Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 15                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

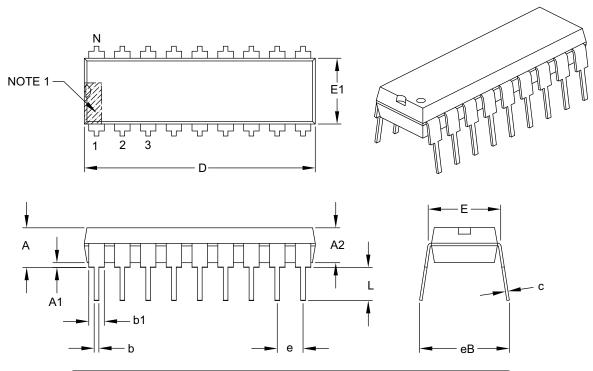

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 20-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc101t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 4.6 Interfacing Program and Data Memory Spaces

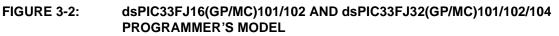

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 architecture uses a 24-bit-wide program space and a 16-bit-wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ16(GP/ MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes, or words, anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for lookups from a large table of static data. The application can only access the lsw of the program word.

#### 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page (TBLPAG) register is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the MSb of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility (PSVPAG) register is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-42 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA.

|                          | Access        | Program Space Address        |           |               |                    |                |  |  |  |

|--------------------------|---------------|------------------------------|-----------|---------------|--------------------|----------------|--|--|--|

| Access Type              | Space         | <23>                         | <22:16>   | <15>          | <14:1>             | <0>            |  |  |  |

| Instruction Access       | User          | 0 PC<22:1>                   |           |               |                    |                |  |  |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |               |                    |                |  |  |  |

| TBLRD/TBLWT              | User          | TB                           | LPAG<7:0> | Data EA<15:0> |                    |                |  |  |  |

| (Byte/Word Read/Write)   |               | 0xxx xxxx xxxx xxxx xxxx     |           |               |                    |                |  |  |  |

|                          | Configuration | TB                           | LPAG<7:0> | Data EA<15:0> |                    |                |  |  |  |

|                          |               | 1                            | xxx xxxx  | xxxx x        | xxxx xxxx xxxx     |                |  |  |  |

| Program Space Visibility | User          | 0 PSVPAG<7:<br>0 xxxx xxxx   |           | :0>           | Data EA<14         | :0> <b>(1)</b> |  |  |  |

| (Block Remap/Read)       |               |                              |           | 2             | xxx xxxx xxxx xxxx |                |  |  |  |

#### TABLE 4-42: PROGRAM SPACE ADDRESS CONSTRUCTION

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

| U-0                            | R/W-1                              | R/W-0                                | R/W-0             | U-0             | R/W-1             | R/W-0           | R/W-0          |  |  |  |  |

|--------------------------------|------------------------------------|--------------------------------------|-------------------|-----------------|-------------------|-----------------|----------------|--|--|--|--|

| —                              | U1RXIP2                            | U1RXIP1                              | U1RXIP0           | —               | SPI1IP2           | SPI1IP1         | SPI1IP0        |  |  |  |  |

| bit 15                         |                                    |                                      |                   |                 |                   |                 | bit            |  |  |  |  |

|                                | D 444                              | DAMA                                 | DAMA              |                 | D 44/ 4           | DAMA            | DAMO           |  |  |  |  |

| U-0                            | R/W-1<br>SPI1EIP2                  | R/W-0<br>SPI1EIP1                    | R/W-0<br>SPI1EIP0 | U-0             | R/W-1<br>T3IP2    | R/W-0<br>T3IP1  | R/W-0<br>T3IP0 |  |  |  |  |

| bit 7                          | OTTEN 2                            | OFFICIENT                            | OFFICIENT         |                 | 10112             | 1011 1          | bit            |  |  |  |  |

|                                |                                    |                                      |                   |                 |                   |                 | _              |  |  |  |  |

| <b>Legend:</b><br>R = Readable | hit.                               |                                      | <b>b</b> :+       |                 | mantad hit raa    |                 |                |  |  |  |  |

|                                |                                    | W = Writable                         |                   | -               | emented bit, read |                 |                |  |  |  |  |

| -n = Value at                  | POR                                | '1' = Bit is set                     |                   | '0' = Bit is cl | eared             | x = Bit is unkı | lown           |  |  |  |  |

| bit 15                         | Unimplemen                         | ted: Read as '                       | 0'                |                 |                   |                 |                |  |  |  |  |

| bit 14-12                      | -                                  | >: UART1 Rec                         |                   | Priority bits   |                   |                 |                |  |  |  |  |

|                                |                                    | pt is Priority 7                     | -                 | -               |                   |                 |                |  |  |  |  |

|                                | •                                  |                                      | 3                 | 5               |                   |                 |                |  |  |  |  |

|                                | •                                  |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •<br>001 = Interrupt is Priority 1 |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                |                                    | pt is Friority 1<br>pt source is dis | abled             |                 |                   |                 |                |  |  |  |  |

| bit 11                         |                                    | ted: Read as '                       |                   |                 |                   |                 |                |  |  |  |  |

| bit 10-8                       | -                                  | : SPI1 Event In                      |                   | v bits          |                   |                 |                |  |  |  |  |

|                                |                                    | pt is Priority 7                     |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                  | pt le 1 lienty 1 l                   | (geet pe          | .,              |                   |                 |                |  |  |  |  |

|                                | •                                  |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                  | nt in Driarity 1                     |                   |                 |                   |                 |                |  |  |  |  |

|                                | 001 = Interru                      | pt is Phonity 1<br>pt source is dis  | abled             |                 |                   |                 |                |  |  |  |  |

| bit 7                          |                                    | ited: Read as '                      |                   |                 |                   |                 |                |  |  |  |  |

| bit 6-4                        | -                                  | >: SPI1 Error I                      |                   | ty hite         |                   |                 |                |  |  |  |  |

|                                |                                    | pt is Priority 7                     | •                 |                 |                   |                 |                |  |  |  |  |

|                                | •                                  | pt lo i nonty i                      | (ingricot priorit | ly interrupty   |                   |                 |                |  |  |  |  |

|                                | •                                  |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                  |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | 001 = Interru                      | pt is Priority 1<br>pt source is dis | abled             |                 |                   |                 |                |  |  |  |  |

| bit 3                          |                                    | ited: Read as '                      |                   |                 |                   |                 |                |  |  |  |  |

| bit 2-0                        | -                                  | imer3 Interrupt                      |                   |                 |                   |                 |                |  |  |  |  |

| Dit 2-0                        |                                    | pt is Priority 7                     | -                 | ty interrupt)   |                   |                 |                |  |  |  |  |

|                                | •                                  | prist nonty /                        | (ingriest priorit | ly interrupt)   |                   |                 |                |  |  |  |  |

|                                | •                                  |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                  |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | 001 = Interru                      | nt in Driarity 1                     |                   |                 |                   |                 |                |  |  |  |  |

|                    | U-0                                                                     | U-0                                                                                                                             | R/W-1           | R/W-1            | R/W-1            | R/W-1           | R/W-1           |  |  |  |  |

|--------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-----------------|--|--|--|--|

| —                  | —                                                                       | —                                                                                                                               | T3CKR4          | T3CKR3           | T3CKR2           | T3CKR1          | T3CKR0          |  |  |  |  |

| bit 15             |                                                                         |                                                                                                                                 |                 |                  |                  |                 | bit 8           |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 | D/M/ 4          |  |  |  |  |

| U-0                | U-0                                                                     | U-0                                                                                                                             | R/W-1<br>T2CKR4 | R/W-1<br>T2CKR3  | R/W-1<br>T2CKR2  | R/W-1<br>T2CKR1 | R/W-1<br>T2CKR0 |  |  |  |  |

| bit 7              |                                                                         |                                                                                                                                 | 1201411         | 1201410          | 1201112          |                 | bit (           |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

| Legend:            |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

| R = Readab         | le bit                                                                  | W = Writable                                                                                                                    | bit             | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |  |

| -n = Value a       | t POR                                                                   | '1' = Bit is se                                                                                                                 | t               | '0' = Bit is cle | ared             | x = Bit is unkr | iown            |  |  |  |  |

|                    |                                                                         |                                                                                                                                 | ( - <b>1</b>    |                  |                  |                 |                 |  |  |  |  |

| bit 15-13          | -                                                                       | ted: Read as                                                                                                                    |                 |                  |                  |                 |                 |  |  |  |  |

| bit 12-8           |                                                                         | -                                                                                                                               | r3 External Clo | ck (T3CK) to t   | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 11111 = Inpu                                                            |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 11110 = Res                                                             | erved                                                                                                                           |                 |                  |                  |                 |                 |  |  |  |  |

|                    | •                                                                       |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | •                                                                       |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 11010 = Reserved                                                        |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 11001 = Inpu                                                            | t tied to RP25                                                                                                                  |                 |                  |                  |                 |                 |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | •                                                                       |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 00001 = Inpu                                                            |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 00000 = Inpu                                                            | t tied to RP0                                                                                                                   |                 |                  |                  |                 |                 |  |  |  |  |

| bit 7-5            | 00000 = Inpu<br>Unimplemen                                              | t tied to RP0<br>ted: Read as                                                                                                   |                 |                  |                  |                 |                 |  |  |  |  |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen                                              | t tied to RP0<br>ted: Read as                                                                                                   |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                                        |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0>                                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                                        |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                                        |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                                        |                 | ck (T2CK) to ti  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Timer<br>It tied to Vss<br>erved<br>erved<br>t tied to RP25<br>tt tied to RP1 | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0          | U-0          | U-0              | U-0            | U-0                                | U-0             | U-0                | U-0    |  |  |

|--------------|--------------|------------------|----------------|------------------------------------|-----------------|--------------------|--------|--|--|

| _            | _            | —                |                |                                    | —               |                    | —      |  |  |

| bit 15       | ·            | •                |                |                                    |                 |                    | bit 8  |  |  |

|              |              |                  |                |                                    |                 |                    |        |  |  |

| U-0          | U-0          | U-0              | R/W-1          | R/W-1                              | R/W-1           | R/W-1              | R/W-1  |  |  |

| _            | —            | —                | OCFAR4         | OCFAR3                             | OCFAR2          | OCFAR1             | OCFAR0 |  |  |

| bit 7        | ·            |                  | •              |                                    |                 |                    | bit 0  |  |  |

|              |              |                  |                |                                    |                 |                    |        |  |  |

| Legend:      |              |                  |                |                                    |                 |                    |        |  |  |

| R = Readab   | ole bit      | W = Writable     | bit            | U = Unimplemented bit, read as '0' |                 |                    |        |  |  |

| -n = Value a | at POR       | '1' = Bit is set |                | '0' = Bit is cle                   | ared            | x = Bit is unknown |        |  |  |

|              |              |                  |                |                                    |                 |                    |        |  |  |

| bit 15-5     | Unimplemen   | ted: Read as '   | 0'             |                                    |                 |                    |        |  |  |

| bit 4-0      | OCFAR<4:0>   | : Assign Outpu   | ut Capture A ( | OCFA) to the 0                     | Corresponding F | RPn Pin bits       |        |  |  |

|              | 11111 = Inpu | t tied to Vss    |                |                                    |                 |                    |        |  |  |

|              | 11110 = Res  | erved            |                |                                    |                 |                    |        |  |  |

|              | •            |                  |                |                                    |                 |                    |        |  |  |

|              |              |                  |                |                                    |                 |                    |        |  |  |

#### REGISTER 10-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

11010 = Reserved 11001 = Input tied to RP25

00001 = Input tied to RP1 00000 = Input tied to RP0

.

| R/W-0              | U-0                                                | R/W-0                                                          | U-0                   | U-0                         | U-0              | U-0                | U-0         |  |  |  |  |

|--------------------|----------------------------------------------------|----------------------------------------------------------------|-----------------------|-----------------------------|------------------|--------------------|-------------|--|--|--|--|

| TON <sup>(2)</sup> |                                                    | TSIDL <sup>(1)</sup>                                           | —                     |                             | —                | —                  | _           |  |  |  |  |

| bit 15             |                                                    |                                                                |                       |                             |                  |                    | bit 8       |  |  |  |  |

|                    |                                                    |                                                                |                       |                             |                  |                    |             |  |  |  |  |

| U-0                | R/W-0                                              | R/W-0                                                          | R/W-0                 | U-0                         | U-0              | R/W-0              | U-0         |  |  |  |  |

| _                  | TGATE <sup>(2)</sup>                               | TCKPS1 <sup>(2)</sup>                                          | TCKPS0 <sup>(2)</sup> | —                           | —                | TCS <sup>(2)</sup> | _           |  |  |  |  |

| bit 7              |                                                    |                                                                |                       |                             |                  |                    | bit         |  |  |  |  |

|                    |                                                    |                                                                |                       |                             |                  |                    |             |  |  |  |  |

| Legend:            | - hit                                              |                                                                | L:4                   |                             |                  |                    |             |  |  |  |  |

| R = Readabl        |                                                    | W = Writable                                                   |                       | •                           | mented bit, rea  |                    |             |  |  |  |  |

| -n = Value at      | POR                                                | '1' = Bit is set                                               |                       | '0' = Bit is cle            | eared            | x = Bit is unkn    | own         |  |  |  |  |

| bit 15             | TON: Timer3                                        | On bit(2)                                                      |                       |                             |                  |                    |             |  |  |  |  |

|                    | 1 = Starts 16-                                     |                                                                |                       |                             |                  |                    |             |  |  |  |  |

|                    | 0 = Stops 16-                                      | bit Timer3                                                     |                       |                             |                  |                    |             |  |  |  |  |

| bit 14             | Unimplemented: Read as '0'                         |                                                                |                       |                             |                  |                    |             |  |  |  |  |

| bit 13             | TSIDL: Timer3 Stop in Idle Mode bit <sup>(1)</sup> |                                                                |                       |                             |                  |                    |             |  |  |  |  |

|                    |                                                    | ues timer opera                                                |                       |                             | e mode           |                    |             |  |  |  |  |

|                    | 0 = Continue                                       | s timer operatio                                               | on in Idle mode       | 9                           |                  |                    |             |  |  |  |  |

| bit 12-7           | •                                                  | ted: Read as '                                                 |                       |                             |                  |                    |             |  |  |  |  |

| bit 6              |                                                    | er3 Gated Time                                                 | Accumulation          | Enable bit <sup>(2)</sup>   |                  |                    |             |  |  |  |  |

|                    | When TCS =<br>This bit is ign                      |                                                                |                       |                             |                  |                    |             |  |  |  |  |

|                    | -                                                  |                                                                |                       |                             |                  |                    |             |  |  |  |  |

|                    |                                                    | <u>When TCS = 0:</u><br>1 = Gated time accumulation is enabled |                       |                             |                  |                    |             |  |  |  |  |

|                    | 0 = Gated tim                                      | ne accumulation                                                | n is disabled         |                             |                  |                    |             |  |  |  |  |

| bit 5-4            | TCKPS<1:0>                                         | : Timer3 Input                                                 | Clock Prescal         | e Select bits <sup>(2</sup> | )                |                    |             |  |  |  |  |

|                    | 11 <b>= 1:256</b> pr                               | rescale value                                                  |                       |                             |                  |                    |             |  |  |  |  |

|                    | 10 = 1:64 pre                                      |                                                                |                       |                             |                  |                    |             |  |  |  |  |

|                    | 01 = 1:8 pres<br>00 = 1:1 pres                     |                                                                |                       |                             |                  |                    |             |  |  |  |  |

| bit 3-2            | •                                                  | ited: Read as '                                                | ∩'                    |                             |                  |                    |             |  |  |  |  |

| bit 1              | •                                                  | Clock Source S                                                 |                       |                             |                  |                    |             |  |  |  |  |

|                    |                                                    | clock from T3C                                                 |                       |                             |                  |                    |             |  |  |  |  |

|                    |                                                    | lock (Fosc/2)                                                  |                       |                             |                  |                    |             |  |  |  |  |

| bit 0              | Unimplemen                                         | ted: Read as '                                                 | 0'                    |                             |                  |                    |             |  |  |  |  |

|                    | /hen 32-bit timer<br>t must be cleared             |                                                                |                       |                             | r2 Control regis | ster (T2CON<3>)    | , the TSIDL |  |  |  |  |

| 0. 14              |                                                    |                                                                |                       |                             |                  | · · / /TOOON       | 0 ) (1      |  |  |  |  |

#### REGISTER 12-2: T3CON: TIMER3 CONTROL REGISTER

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer2 Control register (T2CON<3>), these bits have no effect.

| R/W-0                  | R/W-0 | R/W-0                        | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|------------------------|-------|------------------------------|-------|------------------------------------|-------|-----------------|-------|--|--|--|

| SEVTDIR <sup>(1)</sup> |       | SEVTCMP<14:8> <sup>(2)</sup> |       |                                    |       |                 |       |  |  |  |

| bit 15                 |       |                              |       |                                    |       |                 | bit 8 |  |  |  |

| R/W-0                  | R/W-0 | R/W-0                        | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|                        |       |                              | SEVTC | MP<7:0> <sup>(2)</sup>             |       |                 |       |  |  |  |

| bit 7                  |       |                              |       |                                    |       |                 | bit 0 |  |  |  |

| Legend:                |       |                              |       |                                    |       |                 |       |  |  |  |

| R = Readable           | e bit | W = Writable b               | it    | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |

| -n = Value at POR      |       | '1' = Bit is set             |       | '0' = Bit is cleared               |       | x = Bit is unkr | nown  |  |  |  |

#### REGISTER 15-4: PxSECMP: PWMx SPECIAL EVENT COMPARE REGISTER

0 = A Special Event Trigger will occur when the PWMx time base is counting up

bit 14-0 SEVTCMP<14:0>: Special Event Compare Value bits<sup>(2)</sup>

**Note 1:** SEVTDIR is compared with PTDIR (PxTMR<15>) to generate the Special Event Trigger.

2: PxSECMP<14:0> is compared with PxTMR<14:0> to generate the Special Event Trigger.

| REGISTER      | 20-2: CMxC                                             | ON: COMPA                                                 | RATOR x CO                    | ONTROL REG        | GISTER          |                                      |                |

|---------------|--------------------------------------------------------|-----------------------------------------------------------|-------------------------------|-------------------|-----------------|--------------------------------------|----------------|

| R/W-0         | R/W-0                                                  | R/W-0                                                     | U-0                           | U-0               | U-0             | R/W-0                                | R/W-0          |

| CON           | COE                                                    | CPOL                                                      | _                             | _                 | _               | CEVT                                 | COUT           |

| bit 15        |                                                        |                                                           |                               |                   |                 |                                      | bit 8          |

| R/W-0         | R/W-0                                                  | U-0                                                       | R/W-0                         | U-0               | U-0             | R/W-0                                | R/W-0          |

| EVPOL1        | EVPOL0                                                 | 0-0                                                       | CREF                          |                   |                 | CCH1                                 | CCH0           |

| bit 7         | LVIOLO                                                 |                                                           | GIVEI                         |                   |                 | Com                                  | bit C          |

|               |                                                        |                                                           |                               |                   |                 |                                      |                |

| Legend:       |                                                        |                                                           |                               |                   |                 |                                      |                |

| R = Readable  |                                                        | W = Writable                                              |                               | -                 | nented bit, rea |                                      |                |

| -n = Value at | POR                                                    | '1' = Bit is se                                           | t                             | '0' = Bit is clea | ared            | x = Bit is unkr                      | iown           |

| bit 15        | CON: Compa                                             | arator x Enable                                           | bit                           |                   |                 |                                      |                |

|               | =                                                      | tor x is enable                                           |                               |                   |                 |                                      |                |

|               |                                                        | tor x is disable                                          |                               |                   |                 |                                      |                |

| bit 14        | COE: Compa                                             | arator x Output                                           | Enable bit                    |                   |                 |                                      |                |

|               |                                                        | tor output is pr<br>tor output is in                      | esent on the C<br>ternal only | xOUT pin          |                 |                                      |                |

| bit 13        | CPOL: Comp                                             | parator x Outpu                                           | it Polarity Sele              | ct bit            |                 |                                      |                |

|               |                                                        | tor x output is tor x output is                           |                               |                   |                 |                                      |                |

| bit 12-10     | Unimplemen                                             | ted: Read as                                              | 0'                            |                   |                 |                                      |                |

| bit 9         | CEVT: Comp                                             | arator x Event                                            | bit                           |                   |                 |                                      |                |

|               | interrupts                                             | ator x event ac<br>s until the bit is<br>ator x event did | cleared                       | POL<1:0> set      | ings occurred   | ; disables future                    | e triggers and |

| bit 8         | COUT: Comp                                             | parator x Outpu                                           | ıt bit                        |                   |                 |                                      |                |

|               | 1 = VIN+ > VI                                          |                                                           | ted polarity):                |                   |                 |                                      |                |

|               | 0 = VIN+ < VI                                          |                                                           |                               |                   |                 |                                      |                |

|               | $\frac{\text{When CPOL}}{1 = \text{VIN+} < \text{VI}}$ | = 1 (inverted p                                           | olarity):                     |                   |                 |                                      |                |

|               | 0 = VIN + > VI                                         |                                                           |                               |                   |                 |                                      |                |

| bit 7-6       | EVPOL<1:0>                                             | . Trigger/Ever                                            | t/Interrupt Pola              | arity Select bits |                 |                                      |                |

|               | 10 = Trigger/                                          |                                                           | is generated                  |                   |                 | ator output (whil<br>tion of the pol |                |

|               | If $CPOL = 1$ (                                        | (inverted polari                                          |                               | 1421.14           |                 |                                      |                |

|               | •                                                      | (non-inverted p                                           | •                             | արտ.              |                 |                                      |                |

|               |                                                        |                                                           | comparator ou                 | ıtput.            |                 |                                      |                |

|               |                                                        | event/interrupt/<br>ator output (wh                       |                               | only on low-      | to-high transi  | tion of the pol                      | arity selected |

|               |                                                        | (inverted polari<br>ransition of the                      | t <u>y):</u><br>comparator οι | itput.            |                 |                                      |                |

|               | -                                                      | (non-inverted p                                           | -                             |                   |                 |                                      |                |

|               | Low-to-high t                                          | ransition of the                                          | comparator o                  | -                 |                 |                                      |                |

|               | 00 = Trigger/                                          | event/interrupt                                           | generation is o               | disabled          |                 |                                      |                |

|               |                                                        | ted: Read as                                              |                               |                   |                 |                                      |                |

#### CISTED 20 2 CMACONI COMPADATOD A CONTROL DECISTED

### 21.2 RTCC Control Registers

### REGISTER 21-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                                                                    | U-0                                                                                | R/W-0                       | R-0     | R-0                    | R/W-0          | R/W-0             | R/W-0           |  |  |  |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------|---------|------------------------|----------------|-------------------|-----------------|--|--|--|

| RTCEN <sup>(2)</sup>                                                     |                                                                                    | RTCWREN                     | RTCSYNC | HALFSEC <sup>(3)</sup> | RTCOE          | RTCPTR1           | RTCPTR0         |  |  |  |

| bit 15                                                                   |                                                                                    |                             |         |                        |                |                   | bit 8           |  |  |  |

|                                                                          |                                                                                    |                             |         |                        |                |                   |                 |  |  |  |

| R/W-0                                                                    | R/W-0                                                                              | R/W-0                       | R/W-0   | R/W-0                  | R/W-0          | R/W-0             | R/W-0           |  |  |  |

| CAL7                                                                     | CAL6                                                                               | CAL5                        | CAL4    | CAL3                   | CAL2           | CAL1              | CAL0            |  |  |  |

| bit 7                                                                    |                                                                                    |                             |         |                        |                |                   | bit 0           |  |  |  |

|                                                                          |                                                                                    |                             |         |                        |                |                   |                 |  |  |  |

| Legend:                                                                  |                                                                                    |                             |         |                        |                |                   |                 |  |  |  |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |                                                                                    |                             |         |                        |                |                   |                 |  |  |  |

| -n = Value at P                                                          | OR                                                                                 | '1' = Bit is set            |         | '0' = Bit is clea      | ared           | x = Bit is unkr   | nown            |  |  |  |

|                                                                          |                                                                                    | (2)                         |         |                        |                |                   |                 |  |  |  |

| bit 15                                                                   |                                                                                    | C Enable bit <sup>(2)</sup> |         |                        |                |                   |                 |  |  |  |

|                                                                          | 1 = RTCC module is enabled<br>0 = RTCC module is disabled                          |                             |         |                        |                |                   |                 |  |  |  |

| bit 14                                                                   | 0 = RICC module is disabled<br>Unimplemented: Read as '0'                          |                             |         |                        |                |                   |                 |  |  |  |

| bit 13                                                                   | RTCWREN: RTCC Value Registers Write Enable bit                                     |                             |         |                        |                |                   |                 |  |  |  |

| bit 15                                                                   | 1 = RTCVALH and RTCVALL registers can be written to by the user                    |                             |         |                        |                |                   |                 |  |  |  |

|                                                                          | 0 = RTCVALH and RTCVALL registers are locked out from being written to by the user |                             |         |                        |                |                   |                 |  |  |  |

| bit 12                                                                   | RTCSYNC: RTCC Value Registers Read Synchronization bit                             |                             |         |                        |                |                   |                 |  |  |  |

|                                                                          |                                                                                    |                             |         | •                      | •              | eading, due to a  |                 |  |  |  |

|                                                                          |                                                                                    |                             |         | register is read       | twice and the  | results are the s | same data, the  |  |  |  |

|                                                                          |                                                                                    | be assumed to               |         | registers can b        | e read without | concern over a    | rollover ripple |  |  |  |

| bit 11                                                                   |                                                                                    | lalf-Second Sta             |         | regiotore carro        |                |                   |                 |  |  |  |

|                                                                          |                                                                                    | half period of a            |         |                        |                |                   |                 |  |  |  |

|                                                                          |                                                                                    | period of a sec             |         |                        |                |                   |                 |  |  |  |

| bit 10                                                                   | RTCOE: RTC                                                                         | COutput Enab                | ole bit |                        |                |                   |                 |  |  |  |

|                                                                          |                                                                                    | utput is enabled            |         |                        |                |                   |                 |  |  |  |

|                                                                          |                                                                                    | utput is disabled           |         |                        |                |                   |                 |  |  |  |

| bit 9-8                                                                  |                                                                                    | )>: RTCC Value              | 0       |                        |                |                   |                 |  |  |  |

|                                                                          |                                                                                    |                             |         | U U                    | 0              | ALH and RTCV      |                 |  |  |  |

|                                                                          | RTCVAL<15:                                                                         |                             |         |                        |                |                   | <b>53</b> 00.   |  |  |  |

|                                                                          | 00 = MINUTE                                                                        |                             |         |                        |                |                   |                 |  |  |  |

|                                                                          | 01 = WEEKD                                                                         | AY                          |         |                        |                |                   |                 |  |  |  |

|                                                                          | 10 = MONTH                                                                         | l                           |         |                        |                |                   |                 |  |  |  |

|                                                                          | 11 = Reserve                                                                       | ed                          |         |                        |                |                   |                 |  |  |  |

|                                                                          |                                                                                    | <u>_</u> .                  |         |                        |                |                   |                 |  |  |  |

|                                                                          | RTCVAL<7:0                                                                         |                             |         |                        |                |                   |                 |  |  |  |

|                                                                          | 00 = SECON                                                                         | DS                          |         |                        |                |                   |                 |  |  |  |

|                                                                          |                                                                                    | DS                          |         |                        |                |                   |                 |  |  |  |

Note 1: The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

### 23.0 SPECIAL FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/ MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programming (DS70207) and and Diagnostics" "Device Configuration" (DS70194) in the "dsPIC33/PIC24 Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

#### 23.1 Configuration Bits

The Configuration Shadow register bits can be configured (read as '0') or left unprogrammed (read as '1') to select various device configurations. These read-only bits are mapped starting at program memory location, 0xF80000. A detailed explanation of the various bit functions is provided in Table 23-4.

Note that address, 0xF80000, is beyond the user program memory space and belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using Table Reads.

dsPIC33FJ16(GP/MC)101/102 In and dsPIC33FJ32(GP/MC)101/102/104 devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in the two words at the top of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 23-2. These are packed representations of the actual device Configuration bits, whose actual locations are distributed among several locations in configuration space. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Word for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The upper byte of all Flash Configuration Words in program memory should always be '1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration Words, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

### 25.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 25.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

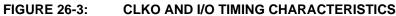

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |                    |     |       |            |

|--------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(2)</sup>     |                                                                                                                                                                                                                                                                                         | Min | Typ <sup>(1)</sup> | Max | Units | Conditions |

| DO31               | TIOR   | Port Output Rise Tim              | е                                                                                                                                                                                                                                                                                       | _   | 10                 | 25  | ns    |            |

| DO32               | TIOF   | Port Output Fall Time             | 9                                                                                                                                                                                                                                                                                       | —   | 10                 | 25  | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) |                                                                                                                                                                                                                                                                                         | 25  | —                  |     | ns    |            |

| DI40               | Trbp   | CNx High or Low Tim               | ne (input)                                                                                                                                                                                                                                                                              | 2   | _                  |     | TCY   |            |

#### TABLE 26-20: I/O TIMING REQUIREMENTS

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: These parameters are characterized, but are not tested in manufacturing.

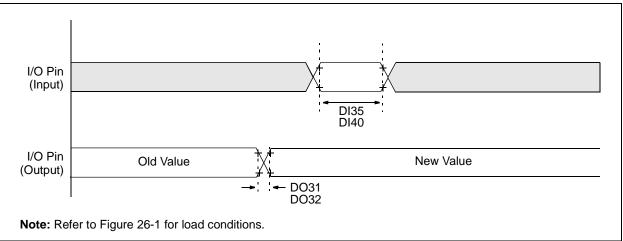

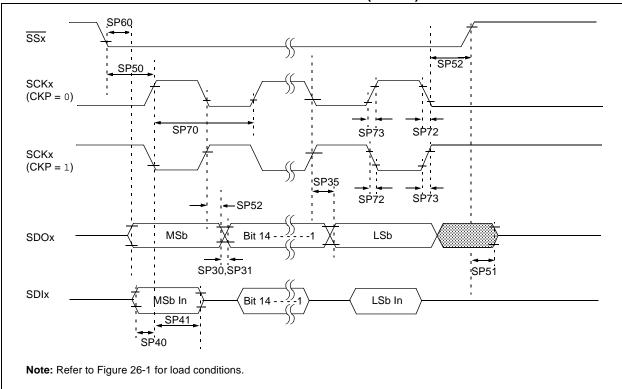

#### FIGURE 26-24: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

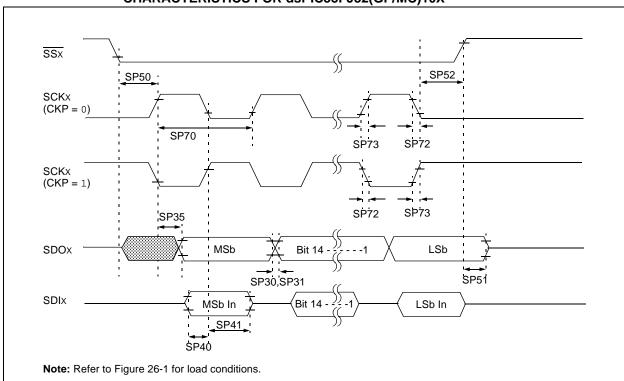

#### FIGURE 26-26: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

#### TABLE 26-50: COMPARATOR TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                       | (unless | otherv | -    | ,     |            |  |

|--------------------|--------|-------------------------------------------------------|---------|--------|------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                                        | Min.    | Тур    | Max. | Units | Conditions |  |

| 300                | TRESP  | Response Time <sup>(1,2)</sup>                        | _       | 150    | 400  | ns    |            |  |

| 301                | TMC20V | Comparator Mode Change to Output Valid <sup>(1)</sup> | —       |        | 10   | μS    |            |  |

| 302                | Ton2ov | Comparator Enabled to<br>Output Valid <sup>(1)</sup>  | —       |        | 10   | μs    |            |  |

Note 1: Parameters are characterized but not tested.

2: Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 26-51: COMPARATOR MODULE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |             |       |            |  |

|--------------------|--------|--------------------------------------------|-------------------------------------------------------|------|-------------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                             | Min.                                                  | Тур  | Max.        | Units | Conditions |  |

| D300               | VIOFF  | Input Offset Voltage <sup>(1)</sup>        | -20                                                   | ±10  | 20          | mV    |            |  |

| D301               | VICM   | Input Common-Mode Voltage <sup>(1)</sup>   | 0                                                     | _    | AVDD – 1.5V | V     |            |  |

| D302               | CMRR   | Common-Mode Rejection Ratio <sup>(1)</sup> | -54                                                   | —    | —           | dB    |            |  |

| D305               | IVREF  | Internal Voltage Reference <sup>(1)</sup>  | 1.116                                                 | 1.24 | 1.364       | V     |            |  |

Note 1: Parameters are characterized but not tested.

#### TABLE 26-52: COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS |        |                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |      |       |            |  |

|--------------------|--------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------|--|