Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 15                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

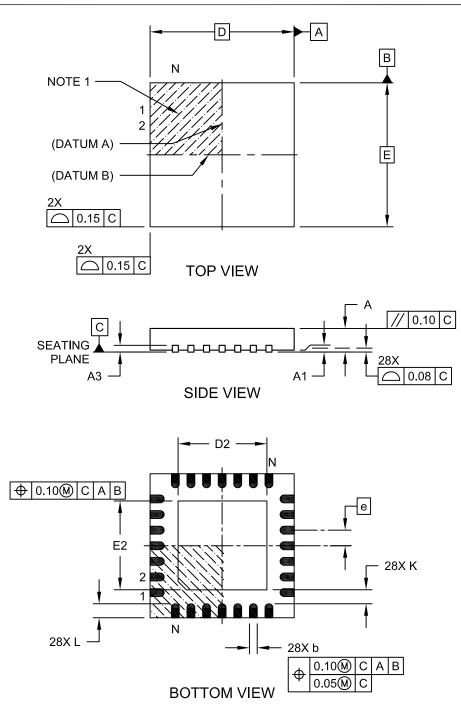

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 20-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc101t-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           |             |        |        |        |        |        |          |                      |         |             |       |       |        |        |          | 1        |         |               |

|-----------|-------------|--------|--------|--------|--------|--------|----------|----------------------|---------|-------------|-------|-------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9                | Bit 8   | Bit 7       | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 0     |       |        |        |          |          |         | xxxx          |

| ADC1BUF1  | 0302        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 1     |       |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 2     |       |        |        |          |          |         | xxxx          |

| ADC1BUF3  | 0306        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 3     |       |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 4     |       |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 5     |       |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 6     |       |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 7     |       |        |        |          |          |         | xxxx          |

| ADC1BUF8  | 0310        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 8     |       |        |        |          |          |         | xxxx          |

| ADC1BUF9  | 0312        |        |        |        |        |        |          |                      | ADC1 D  | Data Buffer | 9     |       |        |        |          |          |         | xxxx          |

| ADC1BUFA  | 0314        |        |        |        |        |        |          |                      | ADC1 D  | ata Buffer  | 10    |       |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |        |        |        |        |        |          |                      | ADC1 D  | ata Buffer  | 11    |       |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318        |        |        |        |        |        |          |                      | ADC1 D  | ata Buffer  | 12    |       |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |        |        |        |        |        |          |                      | ADC1 D  | ata Buffer  | 13    |       |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |        |        |        |        |        |          |                      | ADC1 D  | ata Buffer  | 14    |       |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |        |        |        |        |        |          |                      | ADC1 D  | ata Buffer  | 15    |       |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON   | _      | ADSIDL | _      | _      | _        | FORM1                | FORM0   | SSRC2       | SSRC1 | SSRC0 | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2  | VCFG1  | VCFG0  | _      | _      | CSCNA    | CHPS1                | CHPS0   | BUFS        | _     | SMPI3 | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC   | _      | —      | SAMC4  | SAMC3  | SAMC2    | SAMC1                | SAMC0   | ADCS7       | ADCS6 | ADCS5 | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123 | 0326        |        | _      | —      | _      | _      | CH123NB1 | CH123NB0             | CH123SB | _           | —     | _     | _      | _      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB  | —      | —      | CH0SB4 | CH0SB3 | CH0SB2   | CH0SB1               | CH0SB0  | CH0NA       | —     |       | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | _      | —      | —      | —      |        | PCFG<    | 10:9> <sup>(1)</sup> | —       | _           | —     |       | —      |        | PCF      | G<3:0>   |         | 0000          |

| AD1CSSL   | 0330        | _      | —      | —      | —      |        | CSS<1    | 0:9> <sup>(1)</sup>  | —       | _           | —     |       | —      |        | CSS      | S<3:0>   |         | 0000          |

## TABLE 4-15: ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)101 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)101/102 devices only.

dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| TABLE 4-  | ABLE 4-16: ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES |        |                                                                                            |        |        |        |          |                     |             |           |       |       |        |        |          |          |         |               |

|-----------|----------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------|--------|--------|--------|----------|---------------------|-------------|-----------|-------|-------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr                                                    | Bit 15 | Bit 14                                                                                     | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9               | Bit 8       | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300                                                           |        |                                                                                            |        |        |        |          |                     | ADC1 Data   | Buffer 0  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF1  | 0302                                                           |        |                                                                                            |        |        |        |          |                     | ADC1 Data   | Buffer 1  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304                                                           |        |                                                                                            |        |        |        |          |                     | ADC1 Data   | Buffer 2  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF3  | 0306                                                           |        |                                                                                            |        |        |        |          |                     | ADC1 Data   | Buffer 3  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308                                                           |        |                                                                                            |        |        |        |          |                     | ADC1 Data   | Buffer 4  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A                                                           |        |                                                                                            |        |        |        |          |                     | ADC1 Data   | Buffer 5  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C                                                           |        |                                                                                            |        |        |        |          |                     | ADC1 Data   | Buffer 6  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E                                                           |        |                                                                                            |        |        |        |          |                     |             |           |       |       |        |        | xxxx     |          |         |               |

| ADC1BUF8  | 0310                                                           |        | ADC1 Data Buffer 8 xxx                                                                     |        |        |        |          |                     |             |           |       |       |        |        | xxxx     |          |         |               |

| ADC1BUF9  | 0312                                                           |        |                                                                                            |        |        |        |          |                     | ADC1 Data   | Buffer 9  |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFA  | 0314                                                           |        |                                                                                            |        |        |        |          | A                   | ADC1 Data E | Buffer 10 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316                                                           |        |                                                                                            |        |        |        |          | ŀ                   | ADC1 Data B | Buffer 11 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318                                                           |        |                                                                                            |        |        |        |          | ŀ                   | ADC1 Data E | Buffer 12 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A                                                           |        |                                                                                            |        |        |        |          | ŀ                   | ADC1 Data E | Buffer 13 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C                                                           |        |                                                                                            |        |        |        |          | A                   | ADC1 Data E | Buffer 14 |       |       |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E                                                           |        |                                                                                            |        |        |        |          | A                   | ADC1 Data E | Buffer 15 |       |       |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320                                                           | ADON   | _                                                                                          | ADSIDL | _      | —      | _        | FORM1               | FORM0       | SSRC2     | SSRC1 | SSRC0 | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322                                                           | VCFG2  | VCFG1                                                                                      | VCFG0  | _      | —      | CSCNA    | CHPS1               | CHPS0       | BUFS      |       | SMPI3 | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324                                                           | ADRC   | ADRC — — SAMC4 SAMC3 SAMC2 SAMC1 SAMC0 ADCS7 ADCS6 ADCS5 ADCS4 ADCS3 ADCS2 ADCS1 ADCS0 000 |        |        |        |          |                     |             |           |       |       |        | 0000   |          |          |         |               |

| AD1CHS123 | 0326                                                           | —      | _                                                                                          | _      | _      | —      | CH123NB1 | CH123NB0            | CH123SB     | _         |       |       | _      | _      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328                                                           | CH0NB  | _                                                                                          | _      | CH0SB4 | CH0SB3 | CH0SB2   | CH0SB1              | CH0SB0      | CH0NA     |       |       | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C                                                           | —      | <u> PCFG&lt;10:9&gt;(1)</u> <u> PCFG&lt;5:0&gt;</u> 0000                                   |        |        |        |          |                     |             |           |       |       |        |        |          |          |         |               |

| AD1CSSL   | 0330                                                           | —      | _                                                                                          | —      | —      | _      | CSS<1    | 0:9> <sup>(1)</sup> | —           | _         | —     |       |        | С      | SS<5:0>  |          |         | 0000          |

### TABLE 4-16: ADC1 REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)101/102 devices only.

# DS70000652F-page 66

## TABLE 4-18: CTMU REGISTER MAP

| F | ile Name       | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|---|----------------|-------------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|-------|-------|---------------|

| C | FMUCON1        | 033A        | CTMUEN  | _       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       |          | -        | _        | -        | _     | _     | 0000          |

| C | FMUCON2        | 033C        | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 |       |       | 0000          |

| C | <b>FMUICON</b> | 033E        | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1    | IRNG0    | —       | —       | -        |          | _        |          |       | _     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-19: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14                                                                                                     | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------------|--------|------------------------------------------------------------------------------------------------------------|---------|---------|---------|--------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL   | 0620        |        | Alarm Value Register Window based on ALRMPTR<1:0> xxxx                                                     |         |         |         |        |         |         |       |       |       | xxxx  |       |       |       |       |               |

| ALCFGRPT  | 0622        | ALRMEN | I CHIME AMASK3 AMASK2 AMASK1 AMASK0 ALRMPTR1 ALRMPTR0 ARPT7 ARPT6 ARPT5 ARPT4 ARPT3 ARPT2 ARPT1 ARPT0 0000 |         |         |         |        |         |         |       |       |       |       |       |       |       |       |               |

| RTCVAL    | 0624        |        | RTCC Value Register Window based on RTCPTR<1:0> xxx                                                        |         |         |         |        |         |         |       |       |       | xxxx  |       |       |       |       |               |

| RCFGCAL   | 0626        | RTCEN  | —                                                                                                          | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1 | RTCPTR0 | CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-20: PAD CONFIGURATION REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|-----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------|-------|---------------|

| PADCFG1   | 02FC        | _      |        |        |        | _      | _      | _     | -     | _     |       | _     |       |       |       | RTSECSEL | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | U-0           | U-0                | U-0                         | U-0              | U-0                  | U-0                  | U-0                  |

|--------------|---------------|--------------------|-----------------------------|------------------|----------------------|----------------------|----------------------|

| _            | —             | _                  | —                           | —                | —                    | —                    | —                    |

| bit 15       |               |                    |                             |                  |                      |                      | bit 8                |

|              |               |                    |                             |                  |                      |                      |                      |

| U-0          | R/W-1         | R/W-0              | R/W-0                       | U-0              | R/W-1                | R/W-0                | R/W-0                |

| _            | INT2IP2       | INT2IP1            | INT2IP0                     | —                | T5IP2 <sup>(1)</sup> | T5IP1 <sup>(1)</sup> | T5IP0 <sup>(1)</sup> |

| bit 7        |               |                    |                             |                  |                      |                      | bit 0                |

|              |               |                    |                             |                  |                      |                      |                      |

| Legend:      |               |                    |                             |                  |                      |                      |                      |

| R = Readab   | le bit        | W = Writable       | bit                         | U = Unimple      | mented bit, read     | 1 as '0'             |                      |

| -n = Value a | t POR         | '1' = Bit is set   |                             | '0' = Bit is cle | eared                | x = Bit is unkr      | nown                 |

|              |               |                    |                             |                  |                      |                      |                      |

| bit 15-7     | Unimplemen    | ted: Read as '     | 0'                          |                  |                      |                      |                      |

| bit 6-4      | INT2IP<2:0>:  | External Inter     | rupt 2 Priority             | bits             |                      |                      |                      |

|              | 111 = Interru | pt is Priority 7 ( | highest priorit             | ty interrupt)    |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | 001 = Interru |                    |                             |                  |                      |                      |                      |

|              | 000 = Interru | pt source is dis   | abled                       |                  |                      |                      |                      |

| bit 3        | Unimplemen    | ted: Read as '     | 0'                          |                  |                      |                      |                      |

| bit 2-0      | T5IP<2:0>: ⊺  | ïmer5 Interrupt    | Priority bits <sup>(1</sup> | )                |                      |                      |                      |

|              | 111 = Interru | pt is Priority 7 ( | highest priorit             | ty interrupt)    |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | 001 = Interru | pt is Priority 1   |                             |                  |                      |                      |                      |

|              | 000 = Interru | pt source is dis   | abled                       |                  |                      |                      |                      |

|              | h h :         |                    |                             |                  |                      |                      |                      |

## REGISTER 7-22: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

**Note 1:** These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

## **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | CF: Clock Fail Detect bit (read/clear by application)                                                     |

|-------|-----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = FSCM has detected a clock failure</li><li>0 = FSCM has not detected a clock failure</li></ul> |

| bit 2 | Unimplemented: Read as '0'                                                                                |

| bit 1 | LPOSCEN: Secondary (LP) Oscillator Enable bit                                                             |

|       | <ul><li>1 = Enables secondary oscillator</li><li>0 = Disables secondary oscillator</li></ul>              |

| bit 0 | <b>OSWEN:</b> Oscillator Switch Enable bit                                                                |

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to "Oscillator (Part VI)" (DS70644) in the "dsPIC33/PIC24 Family Reference Manual" for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

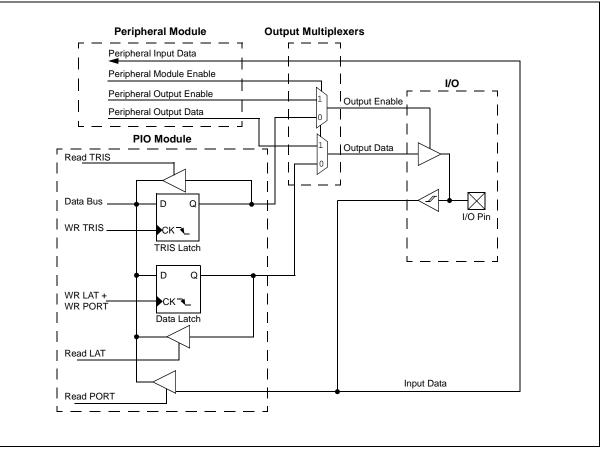

## FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

|               |                    |                  | _              |                  |                  |                 |       |

|---------------|--------------------|------------------|----------------|------------------|------------------|-----------------|-------|

| U-0           | U-0                | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |

| —             | —                  | —                | —              | —                | —                | —               | _     |

| bit 15        |                    |                  |                |                  |                  |                 | bit 8 |

|               |                    |                  |                |                  |                  |                 |       |

| U-0           | U-0                | U-0              | R/W-1          | R/W-1            | R/W-1            | R/W-1           | R/W-1 |

| _             |                    | —                | SS1R4          | SS1R3            | SS1R2            | SS1R1           | SS1R0 |

| bit 7         |                    |                  |                |                  |                  |                 | bit 0 |

|               |                    |                  |                |                  |                  |                 |       |

| Legend:       |                    |                  |                |                  |                  |                 |       |

| R = Readabl   | e bit              | W = Writable     | bit            | U = Unimple      | mented bit, read | l as '0'        |       |

| -n = Value at | POR                | '1' = Bit is set | t              | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               |                    |                  |                |                  |                  |                 |       |

| bit 15-5      | Unimplemer         | nted: Read as '  | 0'             |                  |                  |                 |       |

| bit 4-0       | SS1R<4:0>:         | Assign SPI1 S    | lave Select In | put (SS1IN) to   | the Correspond   | ing RPn Pin bit | S     |

|               |                    | ut tied to Vss   |                |                  |                  |                 |       |

|               | 11110 <b>= Res</b> | served           |                |                  |                  |                 |       |

|               | :                  |                  |                |                  |                  |                 |       |

|               |                    |                  |                |                  |                  |                 |       |

|               | 11010 <b>= Res</b> |                  |                |                  |                  |                 |       |

|               | 11001 <b>= Inp</b> | ut tied to RP25  |                |                  |                  |                 |       |

|               |                    |                  |                |                  |                  |                 |       |

|               |                    |                  |                |                  |                  |                 |       |

|               |                    | ut tied to RP1   |                |                  |                  |                 |       |

|               | 00000 = Inpr       | ut tied to RP0   |                |                  |                  |                 |       |

|               |                    |                  |                |                  |                  |                 |       |

#### REGISTER 10-10: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| R/W-0              | U-0                                    | R/W-0                        | U-0                      | U-0                         | U-0              | U-0                | U-0         |

|--------------------|----------------------------------------|------------------------------|--------------------------|-----------------------------|------------------|--------------------|-------------|

| TON <sup>(2)</sup> |                                        | TSIDL <sup>(1)</sup>         | —                        |                             | —                | —                  | _           |

| bit 15             |                                        |                              |                          |                             |                  |                    | bit 8       |

|                    |                                        |                              |                          |                             |                  |                    |             |

| U-0                | R/W-0                                  | R/W-0                        | R/W-0                    | U-0                         | U-0              | R/W-0              | U-0         |

| _                  | TGATE <sup>(2)</sup>                   | TCKPS1 <sup>(2)</sup>        | TCKPS0 <sup>(2)</sup>    | —                           | —                | TCS <sup>(2)</sup> | _           |

| bit 7              |                                        |                              |                          |                             |                  |                    | bit         |

|                    |                                        |                              |                          |                             |                  |                    |             |

| Legend:            | - hit                                  |                              | L:4                      |                             |                  |                    |             |

| R = Readabl        |                                        | W = Writable                 |                          | •                           | mented bit, rea  |                    |             |

| -n = Value at      | POR                                    | '1' = Bit is set             |                          | '0' = Bit is cle            | eared            | x = Bit is unkn    | own         |

| bit 15             | TON: Timer3                            | On bit(2)                    |                          |                             |                  |                    |             |

|                    | 1 = Starts 16-                         |                              |                          |                             |                  |                    |             |

|                    | 0 = Stops 16-                          | bit Timer3                   |                          |                             |                  |                    |             |

| bit 14             | Unimplemen                             | ted: Read as '               | 0'                       |                             |                  |                    |             |

| bit 13             | TSIDL: Timer                           | r3 Stop in Idle N            | /lode bit <sup>(1)</sup> |                             |                  |                    |             |

|                    |                                        | ues timer opera              |                          |                             | e mode           |                    |             |

|                    | 0 = Continue                           | s timer operatio             | on in Idle mode          | 9                           |                  |                    |             |

| bit 12-7           | •                                      | ted: Read as '               |                          |                             |                  |                    |             |

| bit 6              |                                        | er3 Gated Time               | Accumulation             | Enable bit <sup>(2)</sup>   |                  |                    |             |

|                    | When TCS =<br>This bit is ign          |                              |                          |                             |                  |                    |             |

|                    | When TCS =                             |                              |                          |                             |                  |                    |             |

|                    |                                        | <u>o.</u><br>ne accumulation | n is enabled             |                             |                  |                    |             |

|                    | 0 = Gated tim                          | ne accumulation              | n is disabled            |                             |                  |                    |             |

| bit 5-4            | TCKPS<1:0>                             | : Timer3 Input               | Clock Prescal            | e Select bits <sup>(2</sup> | )                |                    |             |

|                    | 11 <b>= 1:256</b> pr                   | rescale value                |                          |                             |                  |                    |             |

|                    | 10 = 1:64 pre                          |                              |                          |                             |                  |                    |             |

|                    | 01 = 1:8 pres<br>00 = 1:1 pres         |                              |                          |                             |                  |                    |             |

| bit 3-2            | •                                      | ited: Read as '              | ∩'                       |                             |                  |                    |             |

| bit 1              | •                                      | Clock Source S               |                          |                             |                  |                    |             |

|                    |                                        | clock from T3C               |                          |                             |                  |                    |             |

|                    |                                        | lock (Fosc/2)                |                          |                             |                  |                    |             |

| bit 0              | Unimplemen                             | ted: Read as '               | 0'                       |                             |                  |                    |             |

|                    | /hen 32-bit timer<br>t must be cleared |                              |                          |                             | r2 Control regis | ster (T2CON<3>)    | , the TSIDL |

| <b>0</b>           |                                        |                              |                          |                             |                  | · · / /TOOON       | 0 ) (1      |

### REGISTER 12-2: T3CON: TIMER3 CONTROL REGISTER

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer2 Control register (T2CON<3>), these bits have no effect.

| U-0          | U-0               | U-0                     | U-0           | R/W-0                                | R/W-0           | R/W-0           | R/W-0 |

|--------------|-------------------|-------------------------|---------------|--------------------------------------|-----------------|-----------------|-------|

| —            | —                 | —                       |               |                                      | SEVO            | PS<3:0>         |       |

| bit 15       |                   |                         |               |                                      |                 |                 | bit 8 |

|              |                   |                         |               |                                      |                 |                 |       |

| U-0          | U-0               | U-0                     | U-0           | U-0                                  | R/W-0           | R/W-0           | R/W-0 |

| _            | —                 | —                       | _             | —                                    | IUE             | OSYNC           | UDIS  |

| bit 7        | ·                 |                         |               |                                      |                 |                 | bit 0 |

|              |                   |                         |               |                                      |                 |                 |       |

| Legend:      |                   |                         |               |                                      |                 |                 |       |

| R = Readab   | le bit            | W = Writable I          | oit           | U = Unimplen                         | nented bit, rea | d as '0'        |       |

| -n = Value a | t POR             | '1' = Bit is set        |               | '0' = Bit is cle                     | ared            | x = Bit is unkn | own   |

|              |                   |                         |               |                                      |                 |                 |       |

| bit 15-12    | Unimplemen        | ted: Read as '          | )'            |                                      |                 |                 |       |

| bit 11-8     | SEVOPS<3:0        | <b>0&gt;:</b> PWMx Spec | ial Event Tri | gger Output Pos                      | stscale Select  | oits            |       |

|              | 1111 = 1:16       | postscale               |               |                                      |                 |                 |       |

|              | •                 |                         |               |                                      |                 |                 |       |

|              | •                 |                         |               |                                      |                 |                 |       |

|              | •<br>0001 = 1:2 p | netecale                |               |                                      |                 |                 |       |

|              | 0000 = 1.2 p      |                         |               |                                      |                 |                 |       |

| bit 7-3      | •                 | ted: Read as 'd         | )'            |                                      |                 |                 |       |

| bit 2        | IUE: Immedia      | ate Update Enal         | ole bit       |                                      |                 |                 |       |

|              |                   | to the active Px        |               | are immediate                        |                 |                 |       |

|              | 0 = Updates       | to the active Px        | DC registers  | are synchroniz                       | ed to the PWN   | lx time base    |       |

| bit 1        | OSYNC: Out        | put Override Sy         | nchronizatio  | n bit                                |                 |                 |       |

|              |                   |                         |               |                                      |                 | he PWMx time b  | ase   |

|              | •                 |                         |               | register occur o                     | on the next TCN | / boundary      |       |

| bit 0        |                   | Update Disable          |               | <b>5</b> <i>4</i>                    |                 |                 |       |

|              |                   |                         |               | Buffer registers<br>Buffer registers |                 |                 |       |

|              | 0 – Opuales       |                         |               | Duilei registers                     |                 |                 |       |

#### REGISTER 15-6: PWMxCON2: PWMx CONTROL REGISTER 2

|                 | 0 2. 0 0.017                              |                                                                                                         |                            |                                         | OIOTEIX              |       |       |  |  |  |

|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------|----------------------|-------|-------|--|--|--|

| R/W-0           | R/W-0                                     | R/W-0                                                                                                   | U-0                        | R/W-0, HC                               | R/W-0                | R-0   | R-1   |  |  |  |

| UTXISEL1        | UTXINV                                    | UTXISEL0                                                                                                |                            | UTXBRK                                  | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |  |  |  |

| bit 15          |                                           |                                                                                                         |                            |                                         |                      |       | bit 8 |  |  |  |

|                 |                                           |                                                                                                         |                            |                                         |                      |       |       |  |  |  |

| R/W-0           | R/W-0                                     | R/W-0                                                                                                   | R-1                        | R-0                                     | R-0                  | R/C-0 | R-0   |  |  |  |

| URXISEL1        | URXISEL0                                  | ADDEN                                                                                                   | RIDLE                      | PERR                                    | FERR                 | OERR  | URXDA |  |  |  |

| bit 7           |                                           |                                                                                                         |                            |                                         |                      |       | bit C |  |  |  |

|                 |                                           |                                                                                                         |                            |                                         |                      |       |       |  |  |  |

| Legend:         |                                           | C = Clearable b                                                                                         | oit                        | HC = Hardwa                             | are Clearable bi     | t     |       |  |  |  |

| R = Readable    | bit                                       | W = Writable bi                                                                                         | t                          | U = Unimplemented bit, read as '0'      |                      |       |       |  |  |  |

| -n = Value at F | POR                                       | '1' = Bit is set                                                                                        |                            | '0' = Bit is cleared x = Bit is unknown |                      |       |       |  |  |  |

| bit 15,13       | 11 = Reserve<br>10 = Interrup<br>transmit | D>: UARTx Trans<br>ed; do not use<br>t when a charact<br>buffer becomes<br>t when the last ch<br>pleted | ter is transferre<br>empty | ed to the Transr                        | mit Shift Registe    | . ,   |       |  |  |  |

## REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| 00 = Interrupt when a character is transferred to the | Transmit Shift Register (this implies there is at least |

|-------------------------------------------------------|---------------------------------------------------------|

| one character open in the transmit buffer)            |                                                         |

| bit 14  | UTXINV: UARTx Transmit Polarity Inversion bit                                                                                                    |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If IREN = 0:                                                                                                                                     |

|         | 1 = UxTX Idle state is '0'                                                                                                                       |

|         | 0 = UxTX Idle state is '1'                                                                                                                       |

|         | <u>If IREN = 1:</u>                                                                                                                              |

|         | 1 = IrDA encoded, UxTX Idle state is '1'                                                                                                         |

|         | 0 = IrDA encoded, UxTX Idle state is '0'                                                                                                         |

| bit 12  | Unimplemented: Read as '0'                                                                                                                       |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                 |

|         | 1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br>cleared by hardware upon completion |

|         | 0 = Sync Break transmission is disabled or completed                                                                                             |

| bit 10  | UTXEN: UARTx Transmit Enable bit <sup>(1)</sup>                                                                                                  |

|         | 1 = Transmit is enabled, UxTX pin is controlled by UARTx                                                                                         |

|         | <ul> <li>0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by port</li> </ul>        |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                         |

|         | 1 = Transmit buffer is full                                                                                                                      |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                      |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                              |

|         | 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)                                          |

|         | 0 = Transmit Shift Register is not empty, a transmission is in progress or queued                                                                |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                        |

|         | 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)                                            |

|         | 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)                                        |

|         | 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive                                               |

|         | buffer; receive buffer has one or more characters                                                                                                |

| Note 1  | Pater to "ILAPT" (DS70199) in the "doDIC22/DIC24 Family Pateroneo Manual" for information on apphing                                             |

## **Note 1:** Refer to "**UART**" (DS70188) in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UART module for transmit operation.

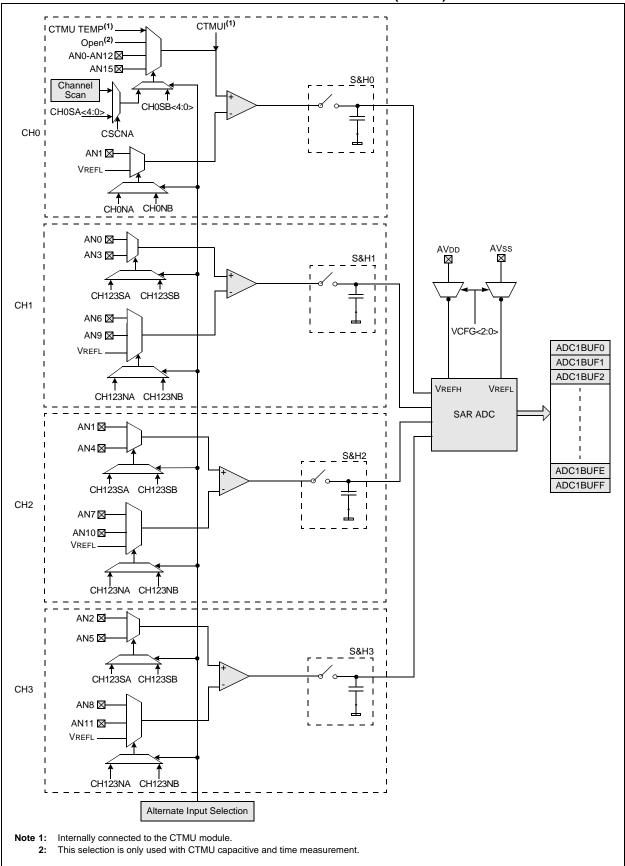

## 19.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Analog-to-Digital Converter (ADC)" (DS70183) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have up to 14 ADC module input channels.

## 19.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 14 analog input pins

- Four Sample-and-Hold (S&H) circuits for simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

- 16-word conversion result buffer

Depending on the particular device pinout, the ADC can have up to 14 analog input pins.

Block diagrams of the ADC module are shown in Figure 19-1 through Figure 19-3.

## 19.2 ADC Initialization

To configure the ADC module:

- 1. Select port pins as analog inputs (AD1PCFGL<15:0>).

- Select the analog conversion clock to match the desired data rate with the processor clock (ADxCON3<7:0>).

- 3. Determine how many Sample-and-Hold channels will be used (ADxCON2<9:8>).

- Select the appropriate sample and conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>).

- 5. Select the way conversion results are presented in the buffer (ADxCON1<9:8>).

- 6. Turn on the ADC module (ADxCON1<15>).

- 7. Configure the ADC interrupt (if required):

- a) Clear the ADxIF bit.

- b) Select the ADC interrupt priority.

|                 | REGI                                       | STER                                                   |                                      | X WASK GA        | ATING CONTI                            | ROL             |       |

|-----------------|--------------------------------------------|--------------------------------------------------------|--------------------------------------|------------------|----------------------------------------|-----------------|-------|

| R/W-0           | U-0                                        | R/W-0                                                  | R/W-0                                | R/W-0            | R/W-0                                  | R/W-0           | R/W-0 |

| HLMS            |                                            | OCEN                                                   | OCNEN                                | OBEN             | OBNEN                                  | OAEN            | OANEN |

| bit 15          |                                            |                                                        |                                      |                  |                                        |                 | bit 8 |

| R/W-0           | R/W-0                                      | R/W-0                                                  | R/W-0                                | R/W-0            | R/W-0                                  | R/W-0           | R/W-0 |

| NAGS            | PAGS                                       | ACEN                                                   | ACNEN                                | ABEN             | ABNEN                                  | AAEN            | AANEN |

| bit 7           | 1                                          | 1                                                      |                                      |                  |                                        |                 | bit 0 |

| Legend:         |                                            |                                                        |                                      |                  |                                        |                 |       |

| R = Readable b  | oit                                        | W = Writable                                           | bit                                  | U = Unimple      | mented bit, read                       | d as '0'        |       |

| -n = Value at P | OR                                         | '1' = Bit is se                                        | t                                    | '0' = Bit is cle | eared                                  | x = Bit is unki | nown  |

| bit 15          | 1 = The mas<br>0 = The mas                 | king (blanking)                                        | function will pr<br>function will pr | event any asse   | erted ('0') compa<br>erted ('1') compa |                 |       |

| bit 14          | -                                          | nted: Read as                                          |                                      | L :4             |                                        |                 |       |

| bit 13          | 1 = MCI is c                               | Gate C Input In<br>connected to OF<br>not connected to | R gate                               | DIT              |                                        |                 |       |

| bit 12          | OCNEN: OR Gate C Input Inverted Enable bit |                                                        |                                      |                  |                                        |                 |       |

|                 |                                            | MCI is connec<br>MCI is not con                        |                                      |                  |                                        |                 |       |

| bit 11          | OBEN: OR                                   | Gate B Input In                                        | verted Enable                        | bit              |                                        |                 |       |

|                 |                                            | onnected to OF<br>ot connected to                      |                                      |                  |                                        |                 |       |

| bit 10          |                                            | R Gate B Input                                         |                                      |                  |                                        |                 |       |

|                 |                                            | MBI is connect<br>MBI is not con                       |                                      |                  |                                        |                 |       |

| bit 9           | OAEN: OR                                   | Gate A Input Er                                        | nable bit                            |                  |                                        |                 |       |

|                 |                                            | onnected to OF<br>ot connected to                      |                                      |                  |                                        |                 |       |

| bit 8           | OANEN: OF                                  | R Gate A Input                                         | Inverted Enabl                       | e bit            |                                        |                 |       |

|                 |                                            | MAI is connect<br>MAI is not con                       | •                                    |                  |                                        |                 |       |

| bit 7           | 1 = Inverted                               | ative AND Gate<br>ANDI is conne<br>ANDI is not co      | cted to OR gat                       | te               |                                        |                 |       |

| bit 6           | 1 = ANDI is                                | tive AND Gate<br>connected to C<br>not connected       | R gate                               |                  |                                        |                 |       |

| bit 5           | 1 = MCI is c                               | O Gate A1 C Inp<br>connected to AN                     |                                      | able bit         |                                        |                 |       |

|                 |                                            | of connected 1-                                        |                                      |                  |                                        |                 |       |

| bit 4           |                                            | ot connected to                                        | -                                    | nabla kit        |                                        |                 |       |

## DECISTED 20-4. CMVMSKCON- COMPADATOR V MASK GATING CONTROL

| R/W-0         | R/W-0                                                                                                                                                                     | R/W-0                                                                                                                                | R/W-0                        | R/W-0                                      | R/W-0            | R/W-0                              | R/W-0         |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------|------------------|------------------------------------|---------------|

| ALRMEN        | CHIME                                                                                                                                                                     | AMASK3                                                                                                                               | AMASK2                       | AMASK1                                     | AMASK0           | ALRMPTR1                           | ALRMPTR0      |

| bit 15        |                                                                                                                                                                           |                                                                                                                                      |                              |                                            |                  |                                    | bit 8         |

| R/W-0         | R/W-0                                                                                                                                                                     | R/W-0                                                                                                                                | R/W-0                        | R/W-0                                      | R/W-0            | R/W-0                              | R/W-0         |

| ARPT7         | ARPT6                                                                                                                                                                     | ARPT5                                                                                                                                | ARPT4                        | ARPT3                                      | ARPT2            | ARPT1                              | ARPT0         |

| bit 7         |                                                                                                                                                                           |                                                                                                                                      |                              |                                            |                  |                                    | bit (         |

| Legend:       |                                                                                                                                                                           |                                                                                                                                      |                              |                                            |                  |                                    |               |

| R = Readable  | e bit                                                                                                                                                                     | W = Writable                                                                                                                         | bit                          | U = Unimpler                               | nented bit, read | d as '0'                           |               |

| -n = Value at | POR                                                                                                                                                                       | '1' = Bit is set                                                                                                                     |                              | '0' = Bit is cle                           | ared             | x = Bit is unkr                    | nown          |

| bit 15        |                                                                                                                                                                           | = 0)                                                                                                                                 | ed automatica                | lly after an ala                           | rm event wher    | never ARPT<7:(                     | 0> = 0x00 and |

| bit 14        |                                                                                                                                                                           | me Enable bit                                                                                                                        |                              |                                            |                  |                                    |               |

| DIL 14        | 1 = Chime is                                                                                                                                                              | s enabled; ARP<br>disabled; ARP                                                                                                      |                              |                                            |                  | 00 to 0xFF                         |               |

| bit 13-10     |                                                                                                                                                                           | >: Alarm Mask                                                                                                                        |                              |                                            |                  |                                    |               |

|               | 0011 = Ever<br>0100 = Ever<br>0101 = Ever<br>0110 = Onco<br>0111 = Onco<br>1000 = Onco<br>1001 = Onco<br>101x = Rese<br>11xx = Rese                                       | y 10 minutes<br>y hour<br>e a day<br>e a week<br>e a month<br>e a year (excep<br>erved – do not u<br>erved – do not u                | ise                          | red for Februa                             | ıry 29th, once e | every 4 years)                     |               |

| hi+ 0 0       | ALRMPTR<                                                                                                                                                                  | 1.05. Alarm Val                                                                                                                      |                              |                                            |                  |                                    |               |

| bit 9-8       |                                                                                                                                                                           |                                                                                                                                      | -                            | indow Pointer                              |                  |                                    |               |

| DIL 9-0       | Points to the                                                                                                                                                             | corresponding /<br>R<1:0> value d<br>5:8>:<br>/IN<br>VD<br>/NTH<br>emented<br>/ <u>:0&gt;:</u><br>SEC<br>IR<br>DAY                   | Alarm Value reg              | gisters when re                            | ading ALRMVA     | ALH and ALRM\<br>ALH until it reac |               |

|               | Points to the<br>the ALRMPT<br>ALRMVAL<1<br>00 = ALRMM<br>01 = ALRMM<br>10 = ALRMM<br>11 = Unimple<br>ALRMVAL<7<br>00 = ALRMS<br>01 = ALRME<br>10 = ALRME<br>11 = Unimple | corresponding /<br>R<1:0> value d<br>5:8>:<br>/IN<br>VD<br>/NTH<br>emented<br>/ <u>:0&gt;:</u><br>SEC<br>IR<br>DAY                   | Alarm Value regerements on e | gisters when re<br>every read or w         | ading ALRMVA     |                                    |               |

|               | Points to the<br>the ALRMPT<br>ALRMVAL<1<br>00 = ALRMM<br>01 = ALRMV<br>10 = ALRMM<br>11 = Unimple<br>ALRMVAL<7<br>00 = ALRME<br>10 = ALRME<br>11 = Unimple<br>ARPT<7:0>: | corresponding /<br>R<1:0> value d<br>5:8>:<br>/IN<br>VD<br>/NTH<br>emented<br>/:0>:<br>SEC<br>IR<br>DAY<br>emented                   | Alarm Value regerements on e | gisters when re<br>every read or w<br>bits | ading ALRMVA     |                                    |               |

|               | Points to the<br>the ALRMPT<br>ALRMVAL<1<br>00 = ALRMM<br>01 = ALRMV<br>10 = ALRMM<br>11 = Unimple<br>ALRMVAL<7<br>00 = ALRME<br>10 = ALRME<br>11 = Unimple<br>ARPT<7:0>: | corresponding /<br>R<1:0> value d<br>5:8>:<br>/IIN<br>VD<br>/INTH<br>emented<br>/:0>:<br>SEC<br>IR<br>DAY<br>emented<br>Alarm Repeat | Alarm Value regerements on e | gisters when re<br>every read or w<br>bits | ading ALRMVA     |                                    |               |

| bit 7-0       | Points to the<br>the ALRMPT<br>ALRMVAL<1<br>00 = ALRMM<br>01 = ALRMV<br>10 = ALRMM<br>11 = Unimple<br>ALRMVAL<7<br>00 = ALRME<br>10 = ALRME<br>11 = Unimple<br>ARPT<7:0>: | corresponding /<br>R<1:0> value d<br>5:8>:<br>/IIN<br>VD<br>/INTH<br>emented<br>/:0>:<br>SEC<br>IR<br>DAY<br>emented<br>Alarm Repeat | Alarm Value regerements on e | gisters when re<br>every read or w<br>bits | ading ALRMVA     |                                    |               |

## REGISTER 21-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

## 26.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                | 40°C to +125°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                            | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 3.0V^{(3)}$  | 0.3V to +5.6V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $< 3.0V^{(3)}$    | 0.3V to (VDD + 0.3V) |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                   | 250 mA               |

| Maximum output current sourced and sunk by any I/O pin excluding OSCO         | 15 mA                |

| Maximum output current sourced and sunk by OSCO                               | 25 mA                |

| Maximum current sunk by all ports                                             | 200 mA               |

| Maximum current sourced by all ports <sup>(2)</sup>                           | 200 mA               |

**Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those, or any other conditions above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of the device maximum power dissipation (see Table 26-2).

- 3: See the "Pin Diagrams" section for 5V tolerant pins.

# TABLE 26-33:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ16(GP/MC)10X

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |

|--------------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|