#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc102-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

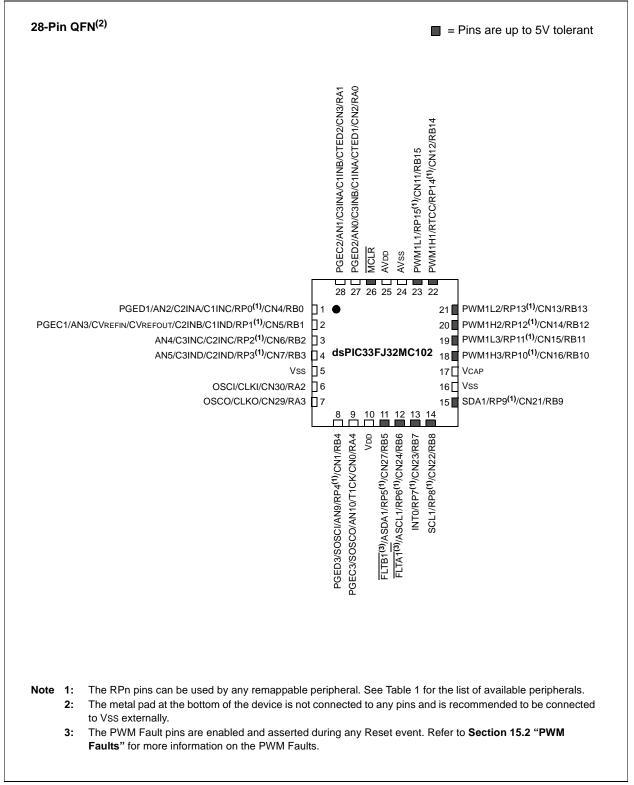

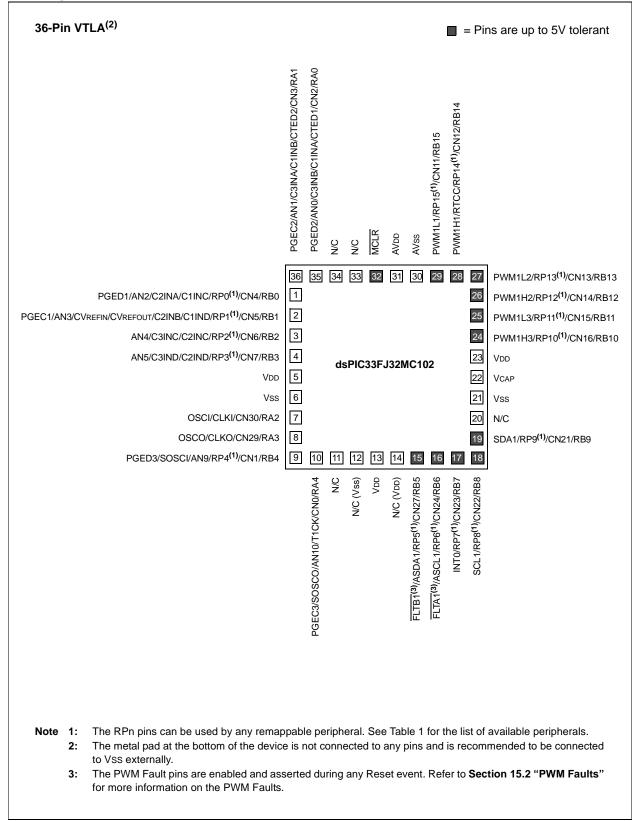

## Pin Diagrams (Continued)

## **Pin Diagrams (Continued)**

### Referenced Sources

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the primary reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33FJ16MC102 product page of the Microchip Web site (www.microchip.com). In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "CPU" (DS70204)

- "Data Memory" (DS70202)

- "Program Memory" (DS70203)

- "Flash Programming" (DS70191)

- "Reset" (DS70192)

- "Watchdog Timer and Power-Saving Modes" (DS70196)

- "Timers" (DS70205)

- "Input Capture" (DS70198)

- "Output Compare" (DS70209)

- "Motor Control PWM" (DS70187)

- "Analog-to-Digital Converter (ADC)" (DS70183)

- "UART" (DS70188)

- "Serial Peripheral Interface (SPI)" (DS70206)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- "CodeGuard Security" (DS70199)

- "Programming and Diagnostics" (DS70207)

- "Device Configuration" (DS70194)

- "I/O Ports with Peripheral Pin Select (PPS)" (DS70190)

- "Real-Time Clock and Calendar (RTCC)" (DS70301)

- "Introduction (Part VI)" (DS70655)

- "Oscillator (Part VI)" (DS70644)

- "Interrupts (Part VI)" (DS70633)

- "Comparator with Blanking" (DS70647)

- "Charge Time Measurement Unit (CTMU)" (DS70635)

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33/PIC24 Family Reference Manual", which are available the Microchip from web site (www.microchip.com).

This data sheet contains device-specific information for dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 Digital Signal Controller (DSC) devices. These devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ16(GP/ MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

| TABLE 1-1              |             |                   |           | RIPTIONS (CONTINUED)                                                                                                                  |

|------------------------|-------------|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name               | Pin<br>Type | Buffer<br>Type    | PPS       | Description                                                                                                                           |

| SCL1                   | I/O         | ST                | No        | Synchronous serial clock input/output for I2C1.                                                                                       |

| SDA1                   | I/O         | ST                | No        | Synchronous serial data input/output for I2C1.                                                                                        |

| ASCL1                  | I/O         | ST                | No        | Alternate synchronous serial clock input/output for I2C1.                                                                             |

| ASDA1                  | I/O         | ST                | No        | Alternate synchronous serial data input/output for I2C1.                                                                              |

| FLTA1(1,2,4)           | 1           | ST                | No        | PWM1 Fault A input.                                                                                                                   |

| FLTB1 <sup>(3,4)</sup> | 1           | ST                | No        | PWM1 Fault B input.                                                                                                                   |

| PWM1L1                 | 0           |                   | No        | PWM1 Low Output 1.                                                                                                                    |

| PWM1H1                 | 0           |                   | No        | PWM1 High Output 1.                                                                                                                   |

| PWM1L2                 | 0           |                   | No        | PWM1 Low Output 2.                                                                                                                    |

| PWM1H2                 | 0           |                   | No        | PWM1 High Output 2.                                                                                                                   |

| PWM1L3                 | 0           |                   | No        | PWM1 Low Output 3.                                                                                                                    |

| PWM1H3                 | Ō           | _                 | No        | PWM1 High Output 3.                                                                                                                   |

| RTCC                   | 0           | Digital           | No        | RTCC Alarm output.                                                                                                                    |

| CTPLS                  | 0           | Digital           | Yes       | CTMU pulse output.                                                                                                                    |

| CTED1                  | I           | Digital           | No        | CTMU External Edge Input 1.                                                                                                           |

| CTED2                  | I           | Digital           | No        | CTMU External Edge Input 2.                                                                                                           |

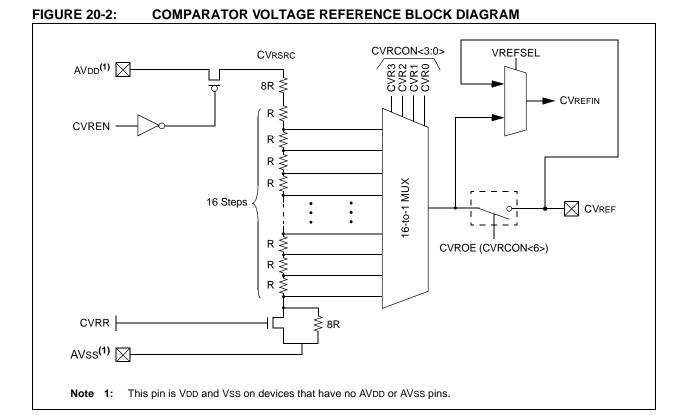

| CVREFIN                | I           | Analog            | No        | Comparator Voltage Positive Reference Input.                                                                                          |

| CVREFOUT               | 0           | Analog            | No        | Comparator Voltage Positive Reference Output.                                                                                         |

| C1INA                  | I           | Analog            | No        | Comparator 1 Positive Input A.                                                                                                        |

| C1INB                  | i           | Analog            | No        | Comparator 1 Negative Input B.                                                                                                        |

| C1INC                  | i           | Analog            | No        | Comparator 1 Negative Input C.                                                                                                        |

| C1IND                  | i           | Analog            | No        | Comparator 1 Negative Input D.                                                                                                        |

| C1OUT                  | Ō           | Digital           | Yes       | Comparator 1 Output.                                                                                                                  |

| C2INA                  | Ĩ           | Analog            | No        | Comparator 2 Positive Input A.                                                                                                        |

| C2INB                  | l i         | Analog            | No        | Comparator 2 Negative Input B.                                                                                                        |

| C2INC                  | i           | Analog            | No        | Comparator 2 Negative Input D.                                                                                                        |

| C2INC<br>C2IND         |             | Analog            | No        | Comparator 2 Negative Input C.                                                                                                        |

| C2OUT                  | 0           | Digital           | Yes       | Comparator 2 Output.                                                                                                                  |

|                        |             | •                 |           |                                                                                                                                       |

| C3INA                  |             | Analog            | No        | Comparator 3 Positive Input A.                                                                                                        |

| C3INB                  |             | Analog            | No        | Comparator 3 Negative Input B.                                                                                                        |

| C3INC                  |             | Analog            | No        | Comparator 3 Negative Input C.                                                                                                        |

| C3IND<br>C3OUT         |             | Analog<br>Digital | No<br>Yes | Comparator 3 Negative Input D.<br>Comparator 3 Output.                                                                                |

|                        |             | ST                |           | Data I/O pin for Programming/Debugging Communication Channel 1.                                                                       |

| PGED1                  | I/O         |                   | No        |                                                                                                                                       |

| PGEC1                  |             | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 1.                                                                    |

| PGED2                  | I/O         | ST                | No        | Data I/O pin for Programming/Debugging Communication Channel 2.                                                                       |

| PGEC2                  | I           | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 2.                                                                    |

| PGED3<br>PGEC3         | I/O         | ST<br>ST          | No<br>No  | Data I/O pin for Programming/Debugging Communication Channel 3.<br>Clock input pin for Programming/Debugging Communication Channel 3. |

|                        | - ·         |                   |           |                                                                                                                                       |

| MCLR                   | I/P         | ST                | No        | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                            |

|                        |             |                   |           | input or output Analog = Analog input P = Power                                                                                       |

| S                      | I = Schr    | nitt Frigger      | input w   | ith CMOS levels O = Output I = Input                                                                                                  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: An external pull-down resistor is required for the FLTA1 pin in dsPIC33FJXXMC101 (20-pin) devices.

- 2: The FLTA1 pin and the PWM1Lx/PWM1Hx pins are available in dsPIC(16/32)MC10X devices only.

- 3: The FLTB1 pin is available in dsPIC(16/32)MC102/104 devices only.

PPS = Peripheral Pin Select

- 4: The PWM Fault pins are enabled during any Reset event. Refer to **Section 15.2 "PWM Faults"** for more information on the PWM Faults.

- 5: Not all pins are available on all devices. Refer to the specific device in the "**Pin Diagrams**" section for availability.

- 6: These pins are available in dsPIC33FJ32(GP/MC)104 (44-pin) devices only.

### 4.6 Interfacing Program and Data Memory Spaces

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 architecture uses a 24-bit-wide program space and a 16-bit-wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ16(GP/ MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes, or words, anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for lookups from a large table of static data. The application can only access the lsw of the program word.

## 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page (TBLPAG) register is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the MSb of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility (PSVPAG) register is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-42 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA.

|                                                | Access        | Program Space Address         |           |                                    |                    |                |  |

|------------------------------------------------|---------------|-------------------------------|-----------|------------------------------------|--------------------|----------------|--|

| Access Type                                    | Space         | <23>                          | <22:16>   | <15>                               | <14:1>             | <0>            |  |

| Instruction Access                             | User          | 0                             | PC<22:1>  |                                    |                    | 0              |  |

| (Code Execution)                               |               | 0xx xxxx xxxx xxxx xxxx xxx0  |           |                                    |                    |                |  |

| TBLRD/TBLWT                                    | User          | TB                            | LPAG<7:0> | Data EA<15:0>                      |                    |                |  |

| (Byte/Word Read/Write)                         |               | 0xxx xxxx xxxx xxxx xxxx      |           |                                    |                    |                |  |

|                                                | Configuration | TB                            | LPAG<7:0> | Data EA<15:0>                      |                    |                |  |

|                                                |               | 1xxx xxxx xxxx xxxx xxxx xxxx |           |                                    |                    |                |  |

| Program Space Visibility<br>(Block Remap/Read) | User          | 0 PSVPAG<                     |           | <7:0> Data EA<14:0> <sup>(1)</sup> |                    | :0> <b>(1)</b> |  |

|                                                |               | 0                             | xxxx xxxx | 2                                  | XXX XXXX XXXX XXXX |                |  |

### TABLE 4-42: PROGRAM SPACE ADDRESS CONSTRUCTION

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

|               |                                                                                                                          |                                                                                                 | 0            |                 |                  |                |        |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------|-----------------|------------------|----------------|--------|--|--|--|--|

| R/W-0         | R-0                                                                                                                      | U-0                                                                                             | U-0          | U-0             | U-0              | U-0            | U-0    |  |  |  |  |

| ALTIVT        | DISI                                                                                                                     | —                                                                                               | —            | —               | —                | —              | —      |  |  |  |  |

| bit 15        |                                                                                                                          |                                                                                                 |              |                 |                  |                | bit 8  |  |  |  |  |

|               |                                                                                                                          |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

| U-0           | U-0                                                                                                                      | U-0                                                                                             | U-0          | U-0             | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |

|               |                                                                                                                          | —                                                                                               | —            | _               | INT2EP           | INT1EP         | INT0EP |  |  |  |  |

| bit 7         |                                                                                                                          |                                                                                                 |              |                 |                  |                | bit (  |  |  |  |  |

|               |                                                                                                                          |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

| Legend:       |                                                                                                                          |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

| R = Readabl   | e bit                                                                                                                    | W = Writable                                                                                    | bit          | U = Unimple     | emented bit, rea | d as '0'       |        |  |  |  |  |

| -n = Value at | POR                                                                                                                      | '1' = Bit is set                                                                                |              | '0' = Bit is cl | eared            | x = Bit is unk | nown   |  |  |  |  |

|               |                                                                                                                          |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

| bit 15        |                                                                                                                          | ALTIVT: Enable Alternate Interrupt Vector Table bit                                             |              |                 |                  |                |        |  |  |  |  |

|               |                                                                                                                          | 1 = Uses Alternate Interrupt Vector Table<br>0 = Uses standard Interrupt Vector Table (default) |              |                 |                  |                |        |  |  |  |  |

| bit 14        |                                                                                                                          | -                                                                                               |              |                 |                  |                |        |  |  |  |  |

|               | DISI: DISI Instruction Status bit                                                                                        |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

|               | 0 = DISI instruction is not active                                                                                       |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

| bit 13-3      | Unimplemen                                                                                                               | nted: Read as '                                                                                 | 0'           |                 |                  |                |        |  |  |  |  |

| bit 2         | INT2EP: Exte                                                                                                             | ernal Interrupt 2                                                                               | 2 Edge Detec | t Polarity Sele | ct bit           |                |        |  |  |  |  |

|               | 1 = Interrupt on negative edge                                                                                           |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

|               | 0 = Interrupt on positive edge                                                                                           |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

| bit 1         |                                                                                                                          | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit                                    |              |                 |                  |                |        |  |  |  |  |

|               | 1 = Interrupt on negative edge                                                                                           |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

| <b>h</b> it 0 | <ul> <li>0 = Interrupt on positive edge</li> <li>INTOEP: External Interrupt 0 Edge Detect Polarity Select bit</li> </ul> |                                                                                                 |              |                 |                  |                |        |  |  |  |  |

| bit 0         |                                                                                                                          |                                                                                                 | 0            | a Polarity Sele |                  |                |        |  |  |  |  |

|               |                                                                                                                          | on negative ed<br>on positive edg                                                               |              |                 |                  |                |        |  |  |  |  |

|               |                                                                                                                          |                                                                                                 | -            |                 |                  |                |        |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

#### REGISTER 10-15: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0           | U-0                                              | U-0                                                                                   | R/W-0                                  | R/W-0                | R/W-0          | R/W-0 | R/W-0              |  |  |  |

|---------------|--------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------|----------------------|----------------|-------|--------------------|--|--|--|

| _             | _                                                | —                                                                                     |                                        |                      | RP9R<4:0>      |       |                    |  |  |  |

| bit 15        | ·                                                |                                                                                       | •                                      |                      |                |       | bit 8              |  |  |  |

| U-0           | U-0                                              | U-0                                                                                   | R/W-0                                  | R/W-0                | R/W-0          | R/W-0 | R/W-0              |  |  |  |

| —             | _                                                | —                                                                                     |                                        |                      | RP8R<4:0>      |       |                    |  |  |  |

| bit 7         |                                                  |                                                                                       |                                        |                      |                |       | bit 0              |  |  |  |

|               |                                                  |                                                                                       |                                        |                      |                |       |                    |  |  |  |

| Legend:       |                                                  |                                                                                       |                                        |                      |                |       |                    |  |  |  |

| R = Readabl   | le bit                                           | W = Writable                                                                          | bit U = Unimplemented bit, read as '0' |                      |                |       |                    |  |  |  |

| -n = Value at | t POR                                            | '1' = Bit is set                                                                      |                                        | '0' = Bit is cleared |                |       | x = Bit is unknown |  |  |  |

|               |                                                  |                                                                                       |                                        |                      |                |       |                    |  |  |  |

| bit 15-13     | Unimplemen                                       | ted: Read as '                                                                        | 0'                                     |                      |                |       |                    |  |  |  |

| bit 12-8      | RP9R<4:0>:                                       | Peripheral Out                                                                        | put Function i                         | s Assigned to F      | RP9 Output Pin | bits  |                    |  |  |  |

|               | (see Table 10-2 for peripheral function numbers) |                                                                                       |                                        |                      |                |       |                    |  |  |  |

| bit 7-5       | Unimplemented: Read as '0'                       |                                                                                       |                                        |                      |                |       |                    |  |  |  |

| bit 4-0       | RP8R<4:0>:                                       | <b>RP8R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP8 Output Pin bits |                                        |                      |                |       |                    |  |  |  |

|               |                                                  | (see Table 10-2 for peripheral function numbers)                                      |                                        |                      |                |       |                    |  |  |  |

|               | (                                                |                                                                                       |                                        | /                    |                |       |                    |  |  |  |

#### REGISTER 10-16: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|--------------------------|-------|-------|

| —      | —   | —   |       |       | RP11R<4:0> <sup>(1</sup> | )     |       |

| bit 15 |     |     |       |       |                          |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0                     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|---------------------------|-------|-------|-------|-------|

| _     | —   | —   | RP10R<4:0> <sup>(1)</sup> |       |       |       |       |

| bit 7 |     |     |                           |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'            |

|-----------|---------------------------------------|

| L:400     | DD44D 4.0. Device and Output Function |

- bit 12-8 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits<sup>(1)</sup> (see Table 10-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits<sup>(1)</sup> (see Table 10-2 for peripheral function numbers)

**Note 1:** These bits are not available in dsPIC33FJXX(GP/MC)101 devices.

## REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Stop bit has been detected last                                                                                       |

|       | 0 = Stop bit was not detected last                                                                                                         |

|       | Hardware sets or clears when Start, Repeated Start or Stop is detected.                                                                    |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware sets or clears when Start, Repeated Start or Stop is detected.                                                                    |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                          |

|       | <ul> <li>1 = Read – Indicates data transfer is output from slave</li> <li>0 = Write – Indicates data transfer is input to slave</li> </ul> |

|       | Hardware sets or clears after reception of an I <sup>2</sup> C device address byte.                                                        |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive is complete, I2CxRCV is full                                                                                                   |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                                                              |

|       | Hardware sets when I2CxRCV is written with received byte. Hardware clears when software reads I2CxRCV.                                     |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty                                                       |

|       | Hardware sets when software writes to I2CxTRN. Hardware clears at completion of data transmission.                                         |

# 18.3 UART Control Registers

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                                                                                                                                                                                                                                        | R/W-0                                  | R/W-0               | R/W-0            | U-0              | R/W-0                                         | R/W-0         |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------|------------------|------------------|-----------------------------------------------|---------------|--|--|

| UARTEN <sup>(1)</sup> |                                                                                                                                                                                                                                            | USIDL                                  | IREN <sup>(2)</sup> | RTSMD            |                  | UEN1                                          | UEN0          |  |  |

| bit 15                |                                                                                                                                                                                                                                            |                                        |                     |                  |                  |                                               | bit 8         |  |  |

|                       |                                                                                                                                                                                                                                            |                                        |                     |                  |                  |                                               |               |  |  |

| R/W-0, HC             | R/W-0                                                                                                                                                                                                                                      | R/W-0, HC                              | R/W-0               | R/W-0            | R/W-0            | R/W-0                                         | R/W-0         |  |  |

| WAKE                  | LPBACK                                                                                                                                                                                                                                     | ABAUD                                  | URXINV              | BRGH             | PDSEL1           | PDSEL0                                        | STSEL         |  |  |

| bit 7                 |                                                                                                                                                                                                                                            |                                        |                     |                  |                  |                                               | bit           |  |  |

| Legend:               |                                                                                                                                                                                                                                            | HC = Hardwa                            | re Clearable b      | nit              |                  |                                               |               |  |  |

| R = Readable          | hit                                                                                                                                                                                                                                        | W = Writable                           |                     |                  | mented bit, read | 1 as '0'                                      |               |  |  |

| -n = Value at F       |                                                                                                                                                                                                                                            | '1' = Bit is set                       |                     | '0' = Bit is cle |                  | x = Bit is unkn                               | own           |  |  |

|                       |                                                                                                                                                                                                                                            | 1 - Dit 13 300                         |                     |                  |                  |                                               | own           |  |  |

| bit 15                | UARTEN: UA                                                                                                                                                                                                                                 | RTx Enable bi                          | t(1)                |                  |                  |                                               |               |  |  |

|                       |                                                                                                                                                                                                                                            |                                        |                     | e controlled by  | UARTx as defi    | ned by the UEN                                | l<1:0> bits   |  |  |

|                       | 0 = UARTx is                                                                                                                                                                                                                               |                                        |                     |                  |                  | JARTx power co                                |               |  |  |

|                       | minimal                                                                                                                                                                                                                                    |                                        |                     |                  |                  |                                               |               |  |  |

| bit 14                | •                                                                                                                                                                                                                                          | ted: Read as '                         |                     |                  |                  |                                               |               |  |  |

| bit 13                |                                                                                                                                                                                                                                            | Tx Stop in Idle                        |                     |                  |                  |                                               |               |  |  |

|                       | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                    |                                        |                     |                  |                  |                                               |               |  |  |

| bit 12                |                                                                                                                                                                                                                                            |                                        |                     |                  |                  |                                               |               |  |  |

| DIL 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup><br>1 = IrDA encoder and decoder are enabled                                                                                                                          |                                        |                     |                  |                  |                                               |               |  |  |

|                       | 1 = IrDA encoder and decoder are enabled $0 = IrDA encoder and decoder are disabled$                                                                                                                                                       |                                        |                     |                  |                  |                                               |               |  |  |

| bit 11                | RTSMD: UAF                                                                                                                                                                                                                                 | RTx Mode Sele                          | ction for UxR1      | S Pin bit        |                  |                                               |               |  |  |

|                       |                                                                                                                                                                                                                                            | oin is in Simple:<br>Sin is in Flow Co |                     |                  |                  |                                               |               |  |  |

| bit 10                | -                                                                                                                                                                                                                                          | ted: Read as '                         |                     |                  |                  |                                               |               |  |  |

| bit 9-8               | -                                                                                                                                                                                                                                          | IARTx Pin Ena                          |                     |                  |                  |                                               |               |  |  |

|                       | 11 = UxTX, UxRX and BCLK pins are enabled and used; $\overline{\text{UxCTS}}$ pin is controlled by port latches                                                                                                                            |                                        |                     |                  |                  |                                               |               |  |  |

|                       | 10 = UxTX, UxRX, $\overline{\text{UxCTS}}$ and $\overline{\text{UxRTS}}$ pins are enabled and used<br>01 = UxTX, UxRX and $\overline{\text{UxRTS}}$ pins are enabled and used; $\overline{\text{UxCTS}}$ pin is controlled by port latches |                                        |                     |                  |                  |                                               |               |  |  |

|                       | 01 = 0x1X, 0xRX and 0xR1S pins are enabled and used; 0xC1S pin is controlled by port latches<br>00 = 0x1X and 0xRX pins are enabled and used; 0xCTS and 0xRTS/BCLK pins are controlled by                                                  |                                        |                     |                  |                  |                                               |               |  |  |

|                       | port latc                                                                                                                                                                                                                                  |                                        |                     |                  |                  | , <b>-                                   </b> |               |  |  |

| bit 7                 | WAKE: Wake                                                                                                                                                                                                                                 | -up on Start bi                        | t Detect During     | g Sleep Mode     | Enable bit       |                                               |               |  |  |

|                       | 1 = UARTx will continue to sample the UxRX pin; interrupt is generated on falling edge, bit is cleared                                                                                                                                     |                                        |                     |                  |                  |                                               |               |  |  |

|                       | in hardware on following rising edge                                                                                                                                                                                                       |                                        |                     |                  |                  |                                               |               |  |  |

|                       |                                                                                                                                                                                                                                            | -up is enabled                         |                     | 1.52             |                  |                                               |               |  |  |

| bit 6                 |                                                                                                                                                                                                                                            | RTx Loopback                           |                     | Dit              |                  |                                               |               |  |  |

|                       |                                                                                                                                                                                                                                            | Loopback mod<br>k mode is disal        |                     |                  |                  |                                               |               |  |  |

| bit 5                 | -                                                                                                                                                                                                                                          | p-Baud Enable                          |                     |                  |                  |                                               |               |  |  |

| ~                     |                                                                                                                                                                                                                                            |                                        |                     | he next charac   | ter – reauires r | eception of a Sy                              | nc field (55h |  |  |

|                       |                                                                                                                                                                                                                                            | her data; clear                        |                     |                  |                  |                                               |               |  |  |

|                       |                                                                                                                                                                                                                                            | e measuremen                           |                     |                  |                  |                                               |               |  |  |

| Note 1: Ref           | er to "UART" (                                                                                                                                                                                                                             | DS70188) in th                         | ne "dsPIC33/F       | PIC24 Family F   | Reference Manu   | al" for information                           | on on         |  |  |

|                       | bling the UART                                                                                                                                                                                                                             |                                        |                     |                  |                  |                                               |               |  |  |

|                       | e foaturo ie ava                                                                                                                                                                                                                           |                                        |                     | -                |                  |                                               |               |  |  |

2: This feature is available for 16x BRG mode (BRGH = 0) only.

# 19.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Analog-to-Digital Converter (ADC)" (DS70183) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have up to 14 ADC module input channels.

# 19.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 14 analog input pins

- Four Sample-and-Hold (S&H) circuits for simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

- 16-word conversion result buffer

Depending on the particular device pinout, the ADC can have up to 14 analog input pins.

Block diagrams of the ADC module are shown in Figure 19-1 through Figure 19-3.

# 19.2 ADC Initialization

To configure the ADC module:

- 1. Select port pins as analog inputs (AD1PCFGL<15:0>).

- Select the analog conversion clock to match the desired data rate with the processor clock (ADxCON3<7:0>).

- 3. Determine how many Sample-and-Hold channels will be used (ADxCON2<9:8>).

- Select the appropriate sample and conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>).

- 5. Select the way conversion results are presented in the buffer (ADxCON1<9:8>).

- 6. Turn on the ADC module (ADxCON1<15>).

- 7. Configure the ADC interrupt (if required):

- a) Clear the ADxIF bit.

- b) Select the ADC interrupt priority.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

#### R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 PCFG15<sup>(4,5)</sup> PCFG<12:0>(4,5,7) \_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 PCFG<7:0>(4,5,6) bit 7 bit 0 Leaend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown PCFG15: ADC1 Port Configuration Control bit<sup>(4,5)</sup> bit 15 1 = Port pin is in Digital mode, port read input is enabled, ADC1 input multiplexer is connected to AVss

#### AD1PCFGL: ADC1 PORT CONFIGURATION REGISTER LOW<sup>(1,2,3)</sup> REGISTER 19-7:

| bit 14-13 | Unimplemented: Read as '0'                                                                               |

|-----------|----------------------------------------------------------------------------------------------------------|

| bit 12-0  | PCFG<12:0>: ADC1 Port Configuration Control bits <sup>(4,5,6,7)</sup>                                    |

|           | 1 = Port pin is in Digital mode, port read input is enabled, ADC1 input multiplexer is connected to AVss |

0 = Port pin is in Analog mode, port read input is disabled, ADC1 samples pin voltage

0 = Port pin is in Analog mode, port read input is disabled, ADC1 samples pin voltage

#### Note 1: On devices without 14 analog inputs, all PCFGx bits are R/W by user. However, PCFGx bits are ignored on ports without a corresponding input on the device.

**2:** PCFGx = ANx, where x = 0 through 12 and 15.

- 3: The PCFGx bits have no effect if the ADC module is disabled by setting the AD1MD bit in the PMD1 register. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

- 4: Pins shared with analog functions (i.e., ANx) are analog by default and therefore, must be set by the user to enable any digital function on that pin. Reading any port pin with the analog function enabled will return a '0', regardless of the signal input level.

- 5: The PCFG<15,12:11,8:6> bits are available in the dsPIC33FJ32(GP/MC)104 devices only and are reserved in all other devices.

- 6: The PCFG<5:4> bits are available on all devices, excluding the dsPIC33FJXX(GP/MC)101 devices, where they are reserved.

- 7: The PCFG<10:9> bits are available on all devices, excluding the dsPIC33FJ16(GP/MC)101/102 devices, where they are reserved.

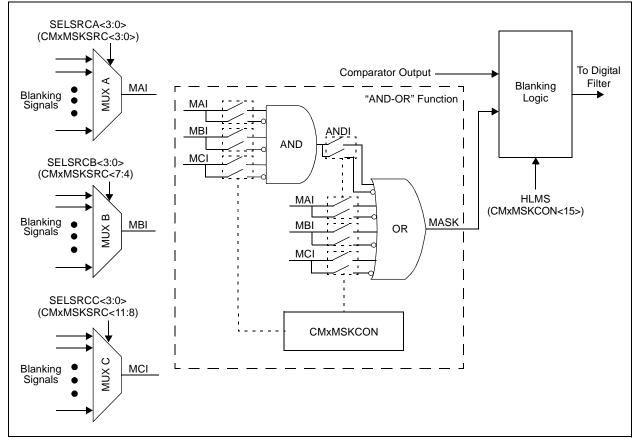

#### FIGURE 20-3: USER-PROGRAMMABLE BLANKING FUNCTION BLOCK DIAGRAM

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER      | 20-2: CMxC                                                                              | ON: COMPA                                                 | RATOR x CO                    | ONTROL REC        | GISTER         |                                      |                |  |  |

|---------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|-------------------|----------------|--------------------------------------|----------------|--|--|

| R/W-0         | R/W-0                                                                                   | R/W-0                                                     | U-0                           | U-0               | U-0            | R/W-0                                | R/W-0          |  |  |

| CON           | COE                                                                                     | CPOL                                                      |                               |                   | _              | CEVT                                 | COUT           |  |  |

| bit 15        |                                                                                         |                                                           |                               |                   |                |                                      | bit 8          |  |  |

| R/W-0         | R/W-0                                                                                   | U-0                                                       | R/W-0                         | U-0               | U-0            | R/W-0                                | R/W-0          |  |  |

| EVPOL1        | EVPOL0                                                                                  | 0-0                                                       | CREF                          |                   |                | CCH1                                 | CCH0           |  |  |

| bit 7         | LVIOLO                                                                                  |                                                           | ONEI                          |                   |                | 00111                                | bit C          |  |  |

|               |                                                                                         |                                                           |                               |                   |                |                                      |                |  |  |

| Legend:       |                                                                                         |                                                           |                               |                   |                |                                      |                |  |  |

| R = Readable  |                                                                                         | W = Writable                                              |                               | U = Unimplem      |                | d as '0'                             |                |  |  |

| -n = Value at | POR                                                                                     | '1' = Bit is se                                           | t                             | '0' = Bit is clea | ared           | x = Bit is unkr                      | nown           |  |  |

| bit 15        | CON: Compa                                                                              | arator x Enable                                           | hit                           |                   |                |                                      |                |  |  |

| bit 15        | -                                                                                       | tor x is enable                                           |                               |                   |                |                                      |                |  |  |

|               |                                                                                         | tor x is disable                                          |                               |                   |                |                                      |                |  |  |

| bit 14        | COE: Compa                                                                              | arator x Output                                           | Enable bit                    |                   |                |                                      |                |  |  |

|               |                                                                                         | tor output is pr<br>tor output is in                      | esent on the C<br>ternal only | xOUT pin          |                |                                      |                |  |  |

| bit 13        | CPOL: Comp                                                                              | parator x Outpu                                           | ut Polarity Sele              | ct bit            |                |                                      |                |  |  |

|               |                                                                                         | tor x output is tor x output is                           |                               |                   |                |                                      |                |  |  |

| bit 12-10     | Unimplemen                                                                              | ted: Read as                                              | ʻ0'                           |                   |                |                                      |                |  |  |

| bit 9         | CEVT: Comp                                                                              | arator x Event                                            | bit                           |                   |                |                                      |                |  |  |

|               | interrupts                                                                              | ator x event ac<br>s until the bit is<br>ator x event did | cleared                       | POL<1:0> seti     | ings occurred  | ; disables future                    | e triggers and |  |  |

| bit 8         | COUT: Comp                                                                              | parator x Outpu                                           | ıt bit                        |                   |                |                                      |                |  |  |

|               | 1 = VIN+ > VI                                                                           |                                                           | ted polarity):                |                   |                |                                      |                |  |  |

|               | 0 = VIN+ < VI                                                                           |                                                           |                               |                   |                |                                      |                |  |  |

|               | $\frac{\text{When CPOL} = 1 \text{ (inverted polarity):}}{1 = \text{VIN} + \text{VIN}}$ |                                                           |                               |                   |                |                                      |                |  |  |

|               | 1 = VIN+ < VIN- $0 = VIN+ > VIN-$                                                       |                                                           |                               |                   |                |                                      |                |  |  |

| bit 7-6       | EVPOL<1:0>                                                                              | -: Trigger/Ever                                           | t/Interrupt Pola              | rity Select bits  |                |                                      |                |  |  |

|               | 10 = Trigger/                                                                           |                                                           | is generated                  |                   |                | ator output (whil<br>tion of the pol |                |  |  |

|               | If $CPOL = 1$ (                                                                         | (inverted polari                                          | -                             | utput.            |                |                                      |                |  |  |

|               |                                                                                         | (non-inverted p<br>ransition of the                       | olarity):<br>comparator ou    | itput.            |                |                                      |                |  |  |

|               |                                                                                         | event/interrupt/<br>ator output (wh                       |                               | only on low-      | to-high transi | tion of the pol                      | arity selected |  |  |

|               |                                                                                         | (inverted polari<br>ransition of the                      | <u>ty):</u><br>comparator ou  | itput.            |                |                                      |                |  |  |

|               |                                                                                         | (non-inverted p<br>ransition of the                       | olarity):<br>comparator ou    | utput.            |                |                                      |                |  |  |

|               | -                                                                                       |                                                           | generation is o               | -                 |                |                                      |                |  |  |

| bit 5         | Unimplemen                                                                              | ted: Read as                                              | ʻ0'                           |                   |                |                                      |                |  |  |

|               |                                                                                         |                                                           |                               |                   |                |                                      |                |  |  |

#### CISTED 20 2 CMACONI COMPADATOD A CONTROL DECISTED

# REGISTER 20-4: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

| bit 3 | ABEN: AND Gate A1 B Input Inverted Enable bit                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------|

|       | 1 = MBI is connected to AND gate                                                                                  |

|       | 0 = MBI is not connected to AND gate                                                                              |

| bit 2 | ABNEN: AND Gate A1 B Input Inverted Enable bit                                                                    |

|       | <ul><li>1 = Inverted MBI is connected to AND gate</li><li>0 = Inverted MBI is not connected to AND gate</li></ul> |

| bit 1 | AAEN: AND Gate A1 A Input Enable bit                                                                              |

|       | <ul><li>1 = MAI is connected to AND gate</li><li>0 = MAI is not connected to AND gate</li></ul>                   |

| bit 0 | AANEN: AND Gate A1 A Input Inverted Enable bit                                                                    |

|       | <ul><li>1 = Inverted MAI is connected to AND gate</li><li>0 = Inverted MAI is not connected to AND gate</li></ul> |

| U-0             | U-0                                                                                                                                          | U-0              | U-0            | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------|------------------|-----------------|--------|--|--|

|                 | _                                                                                                                                            | _                | _              | —                | VREFSEL          | BGSEL1          | BGSEL0 |  |  |

| bit 15          |                                                                                                                                              |                  |                |                  |                  |                 | bit    |  |  |

|                 |                                                                                                                                              |                  |                |                  |                  |                 |        |  |  |

| R/W-0           | R/W-0                                                                                                                                        | R/W-0            | U-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |