Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc102-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

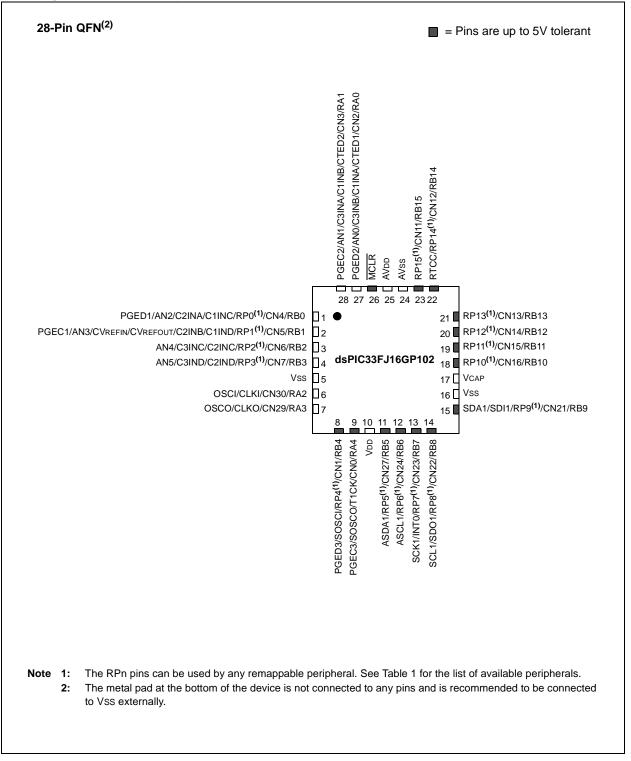

#### Pin Diagrams (Continued)

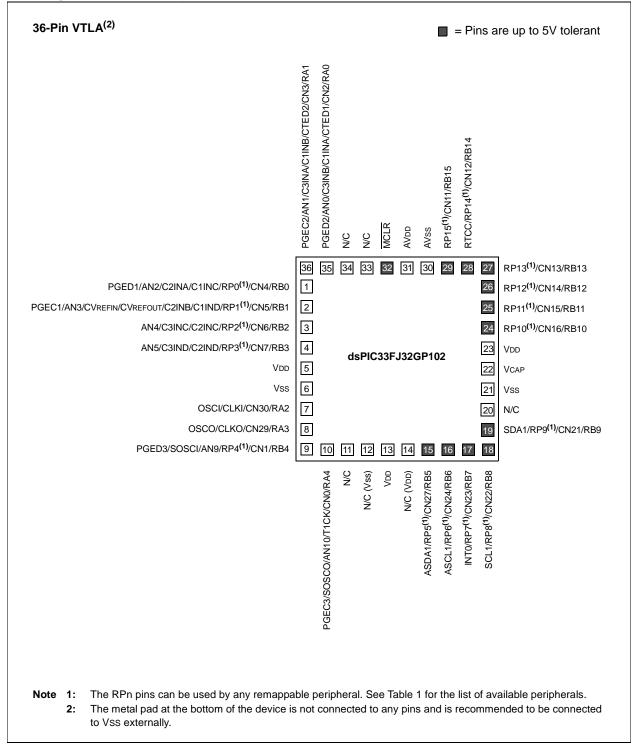

#### Pin Diagrams (Continued)

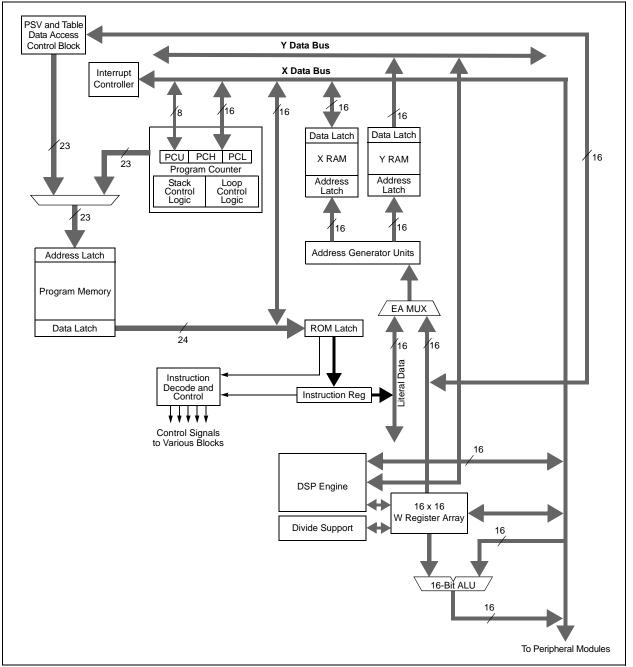

#### 3.3 Special MCU Features

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 features a 17-bit by 17-bit, single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

FIGURE 3-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 CPU CORE BLOCK DIAGRAM

#### TABLE 4-21: COMPARATOR REGISTER MAP

| File Name        | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|------------------|-------------|--------|--------|--------|--------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| CMSTAT           | 0650        | CMSIDL | _      | _      | _      | _        | C3EVT    | C2EVT    | C1EVT    | _        | —        | —        | —        | —        | C3OUT    | C2OUT    | C1OUT    | 0000          |

| CVRCON           | 0652        | —      | _      | _      | _      | _        | VREFSEL  | BGSEL1   | BGSEL0   | CVREN    | CVROE    | CVRR     | _        | CVR3     | CVR2     | CVR1     | CVR0     | 0000          |

| CM1CON           | 0654        | CON    | COE    | CPOL   |        | -        | -        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM1MSKSRC        | 0656        | _      | —      | -      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM1MSKCON        | 0658        | HLMS   | —      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM1FLTR          | 065A        | -      | —      |        |        | -        | -        | _        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM2CON           | 065C        | CON    | COE    | CPOL   |        | -        | -        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM2MSKSRC        | 065E        | -      | —      |        |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM2MSKCON        | 0660        | HLMS   | —      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM2FLTR          | 0662        | -      | —      |        |        | -        | -        | _        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM3CON           | 0664        | CON    | COE    | CPOL   |        | -        | -        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM3MSKSRC        | 0666        | -      | —      |        |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| <b>CM3MSKCON</b> | 0668        | HLMS   | _      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM3FLTR          | 066A        | _      | —      | —      | —      | _        | —        | _        | _        | -        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10                  | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|-------------------------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPINR0       | 0680        | _      | —      | —      |        | I      | NT1R<4:0>               |       |       | —     | —     | —     | _     | —     | —          | —     | _     | 1F00          |

| RPINR1       | 0682        | _      | _      | _      | _      | _      | _                       | _     | _     | _     | _     | _     |       | I     | NT2R<4:0>  |       |       | 001F          |

| RPINR3       | 0686        | _      | _      | _      |        | Т      | 3CKR<4:0>               |       |       | _     | _     | _     |       | Т     | 2CKR<4:0>  | •     |       | 1F1F          |

| RPINR4       | 0688        | —      | _      | _      |        | Τŧ     | 5CKR<4:0>(1             | )     |       | _     | _     | _     |       | T4    | CKR<4:0>   | 1)    |       | 1F1F          |

| RPINR7       | 068E        | —      | _      | _      |        |        | IC2R<4:0>               |       |       | _     | _     | —     |       |       | IC1R<4:0>  |       |       | 1F1F          |

| RPINR8       | 0690        | —      | _      | _      | _      | _      | —                       | —     | _     | _     | _     | —     |       |       | IC3R<4:0>  |       |       | 001F          |

| RPINR11      | 0696        | —      | _      | _      | _      | _      | _                       | —     | _     | _     | _     | —     |       | C     | CFAR<4:0   | >     |       | 001F          |

| RPINR18      | 06A4        | —      | _      | _      |        | U      | 1CTSR<4:0>              |       |       | _     | _     | —     |       | U     | 1RXR<4:0:  | >     |       | 1F1F          |

| RPINR20      | 06A8        | —      | _      | _      |        | S      | CK1R<4:0> <sup>(1</sup> | )     |       | _     | _     | —     |       | SI    | DI1R<4:0>( | 1)    |       | 1F1F          |

| RPINR21      | 06AA        | _      | _      | _      | —      | _      | —                       | _     | _     | _     | —     | _     |       | ;     | SS1R<4:0>  |       |       | 001F          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

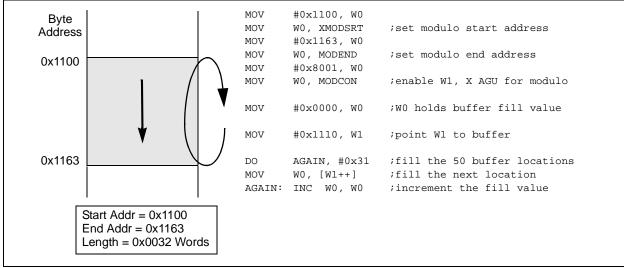

#### 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the circular buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear). The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.4.2 W ADDRESS REGISTER SELECTION

- The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing.

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

#### 5.2 RTSP Operation

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions); and to program one word. Table 26-12 shows typical erase and programming times. The 8-row erase pages are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the operation is finished.

The programming time depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3). Use the following formula to calculate the minimum and maximum values for the Word write time and page erase time (see Parameters D138a and D138b, and Parameters D137a and D137b in Table 26-12, respectively).

#### EQUATION 5-1: PROGRAMMING TIME

$\frac{T}{7.37 \text{ MHz} \times (FRC \text{ Accuracy})\% \times (FRC \text{ Tuning})\%}$

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 8-3) are set to `b000000, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 + 0.02) \times (1 - 0.00375)} = 47.4 \mu s$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 49.3 \mu s$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one word (24 bits) of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

| Note: | Performing a page erase operation on the   |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | last page of program memory will clear the |  |  |  |  |  |  |  |  |

|       | Flash Configuration Words, thereby         |  |  |  |  |  |  |  |  |

|       | enabling code protection as a result.      |  |  |  |  |  |  |  |  |

|       | Therefore, users should avoid performing   |  |  |  |  |  |  |  |  |

|       | page erase operations on the last page of  |  |  |  |  |  |  |  |  |

|       | program memory.                            |  |  |  |  |  |  |  |  |

Refer to **"Flash Programming"** (DS70191) in the *"dsPIC33/PIC24 Family Reference Manual"* for details and codes examples on programming using RTSP.

#### 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

| D / M A       | D 444 A                         | D.4.4. 0                            | DAMA            | DALLA             | DALLA           | DAMA            | D 44/ 6 |

|---------------|---------------------------------|-------------------------------------|-----------------|-------------------|-----------------|-----------------|---------|

| R/W-0         | R/W-0                           | R/W-0                               | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

| NSTDIS        | OVAERR                          | OVBERR                              | COVAERR         | COVBERR           | OVATE           | OVBTE           | COVTE   |

| bit 15        |                                 |                                     |                 |                   |                 |                 | bi      |

| R/W-0         | R/W-0                           | U-0                                 | R/W-0           | R/W-0             | R/W-0           | R/W-0           | U-0     |

| SFTACERR      |                                 | <u> </u>                            | MATHERR         | ADDRERR           | STKERR          | OSCFAIL         |         |

| bit 7         | BIVOLINI                        |                                     |                 | ABBRERR           | OTTLETT         | 00017112        | bi      |

|               |                                 |                                     |                 |                   |                 |                 |         |

| Legend:       |                                 |                                     |                 |                   |                 |                 |         |

| R = Readabl   | e bit                           | W = Writable                        | bit             | U = Unimplem      | ented bit, read | 1 as '0'        |         |

| -n = Value at | POR                             | '1' = Bit is set                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

| 6:4 <i>7</i>  |                                 | www.unt.Nie.otie.ev.F               | Niachla hit     |                   |                 |                 |         |

| bit 15        |                                 | rrupt Nesting E<br>nesting is disat |                 |                   |                 |                 |         |

|               |                                 | nesting is cloat                    |                 |                   |                 |                 |         |

| bit 14        | -                               | cumulator A O                       |                 | lag bit           |                 |                 |         |

|               | 1 = Trap was                    | caused by ove                       | erflow of Accur | nulator A         |                 |                 |         |

|               | 0 = Trap was                    | not caused by                       | overflow of Ad  | ccumulator A      |                 |                 |         |

| bit 13        |                                 | cumulator B O                       | -               | -                 |                 |                 |         |

|               |                                 | caused by ove<br>not caused by      |                 |                   |                 |                 |         |

| bit 12        | -                               | -                                   |                 | Dverflow Trap F   | lag hit         |                 |         |

|               |                                 |                                     | •               | flow of Accumu    | •               |                 |         |

|               | •                               | •                                   | •               | overflow of Accu  |                 |                 |         |

| bit 11        | COVBERR: A                      | Accumulator B                       | Catastrophic C  | Overflow Trap F   | lag bit         |                 |         |

|               |                                 |                                     |                 | flow of Accumu    |                 |                 |         |

|               | -                               | -                                   | -               | overflow of Accu  | umulator B      |                 |         |

| bit 10        |                                 | Imulator A Ove                      |                 | able bit          |                 |                 |         |

|               | ⊥ = Trap over<br>0 = Trap is di | flow of Accum                       | ulator A        |                   |                 |                 |         |

| bit 9         |                                 | umulator B Ove                      | erflow Trap En  | able bit          |                 |                 |         |

|               |                                 | flow of Accum                       |                 |                   |                 |                 |         |

|               | 0 = Trap is di                  | sabled                              |                 |                   |                 |                 |         |

| bit 8         | COVTE: Cata                     | astrophic Overf                     | low Trap Enab   | ole bit           |                 |                 |         |

|               |                                 |                                     | erflow of Accur | mulator A or B i  | s enabled       |                 |         |

| hit 7         | 0 = Trap is dis                 | sabled<br>Shift Accumula            | tor Error State | ia hit            |                 |                 |         |

| bit 7         |                                 |                                     |                 | llid accumulator  | chift           |                 |         |

|               |                                 |                                     |                 | invalid accumul   |                 |                 |         |

| bit 6         |                                 | ithmetic Error :                    | -               |                   |                 |                 |         |

|               |                                 | or trap was cau                     | -               | -                 |                 |                 |         |

|               |                                 | r trap was not                      | -               | ivide-by-zero     |                 |                 |         |

| bit 5         | •                               | ted: Read as '                      |                 |                   |                 |                 |         |

| bit 4         | MATHERR: A                      | Arithmetic Error                    | Status bit      |                   |                 |                 |         |

|               | 1 14-41                         | or trap has occu                    | una al          |                   |                 |                 |         |

#### INTOONA, INTERDURT CONTROL DECISTER A

| U-0           | U-0           | U-0                                  | U-0             | U-0                                | U-0  | U-0             | U-0   |  |  |  |  |

|---------------|---------------|--------------------------------------|-----------------|------------------------------------|------|-----------------|-------|--|--|--|--|

| —             |               | _                                    | —               |                                    | —    |                 |       |  |  |  |  |

| bit 15        |               |                                      |                 |                                    |      |                 | bit 8 |  |  |  |  |

|               |               |                                      |                 |                                    |      |                 |       |  |  |  |  |

| U-0           | R/W-1         | R/W-0                                | R/W-0           | U-0                                | U-0  | U-0             | U-0   |  |  |  |  |

| —             | CTMUIP2       | CTMUIP1                              | CTMUIP0         | —                                  | _    | —               | _     |  |  |  |  |

| bit 7         |               |                                      |                 |                                    |      |                 | bit 0 |  |  |  |  |

|               |               |                                      |                 |                                    |      |                 |       |  |  |  |  |

| Legend:       |               |                                      |                 |                                    |      |                 |       |  |  |  |  |

| R = Readabl   | e bit         | W = Writable                         | bit             | U = Unimplemented bit, read as '0' |      |                 |       |  |  |  |  |

| -n = Value at | POR           | '1' = Bit is set                     |                 | '0' = Bit is cle                   | ared | x = Bit is unkn | iown  |  |  |  |  |

|               |               |                                      |                 |                                    |      |                 |       |  |  |  |  |

| bit 15-7      | Unimplemen    | ted: Read as '                       | 0'              |                                    |      |                 |       |  |  |  |  |

| bit 6-4       | CTMUIP<2:0    | >: CTMU Interr                       | upt Priority bi | ts                                 |      |                 |       |  |  |  |  |

|               | 111 = Interru | pt is Priority 7 (                   | highest priorit | y interrupt)                       |      |                 |       |  |  |  |  |

|               | •             |                                      |                 |                                    |      |                 |       |  |  |  |  |

|               | •             |                                      |                 |                                    |      |                 |       |  |  |  |  |

|               | •             |                                      |                 |                                    |      |                 |       |  |  |  |  |

|               |               | pt is Priority 1<br>pt source is dis | abled           |                                    |      |                 |       |  |  |  |  |

| bit 3-0       | Unimplemen    | ted: Read as '                       | 0'              |                                    |      |                 |       |  |  |  |  |

|               |               |                                      |                 |                                    |      |                 |       |  |  |  |  |

#### REGISTER 7-27: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

| R/W-0        | R/W-0                            | R/W-1                        | R/W-1                                                    | R/W-0                        | R/W-0           | R/W-0             | R/W-0       |

|--------------|----------------------------------|------------------------------|----------------------------------------------------------|------------------------------|-----------------|-------------------|-------------|

| ROI          | DOZE2 <sup>(2,3)</sup>           | DOZE1 <sup>(2,3)</sup>       | DOZE0 <sup>(2,3)</sup>                                   | DOZEN <sup>(1,2,3)</sup>     | FRCDIV2         | FRCDIV1           | FRCDIV0     |

| bit 15       |                                  |                              |                                                          |                              |                 |                   | bit         |

|              |                                  |                              |                                                          |                              |                 |                   |             |

| U-0          | U-0                              | U-0                          | U-0                                                      | U-0                          | U-0             | U-0               | U-0         |

|              | _                                | _                            |                                                          | —                            |                 |                   | —           |

| bit 7        |                                  |                              |                                                          |                              |                 |                   | bit         |

| Legend:      |                                  |                              |                                                          |                              |                 |                   |             |

| R = Readab   | le bit                           | W = Writable                 | bit                                                      | U = Unimpleme                | ented bit, read | as '0'            |             |

| -n = Value a | t POR                            | '1' = Bit is set             |                                                          | '0' = Bit is clear           | ed              | x = Bit is unk    | nown        |

|              |                                  |                              |                                                          |                              |                 |                   |             |

| bit 15       | 1 = Interrupts<br>0 = Interrupts | s have no effec              | DOZEN bit and to the |                              | clock/periphera | al clock ratio is | set to 1:1  |

| bit 14-12    | DOZE<2:0>:                       | Processor Cloo               | ck Reduction S                                           | Select bits <sup>(2,3)</sup> |                 |                   |             |

|              | 111 = FCY/12                     | -                            |                                                          |                              |                 |                   |             |

|              | 110 = FCY/64<br>101 = FCY/32     |                              |                                                          |                              |                 |                   |             |

|              | 101 = FCY/16                     |                              |                                                          |                              |                 |                   |             |

|              | 011 = FCY/8 (                    | default)                     |                                                          |                              |                 |                   |             |

|              | 010 = FCY/4                      |                              |                                                          |                              |                 |                   |             |

|              | 001 = FCY/2<br>000 = FCY/1       |                              |                                                          |                              |                 |                   |             |

| bit 11       |                                  | E Mode Enabl                 | e bit <sup>(1,2,3)</sup>                                 |                              |                 |                   |             |

|              |                                  |                              |                                                          | io between the p             | eripheral clock | s and the proc    | essor clock |

|              | 0 = Processo                     | or clock/periphe             | eral clock ratio                                         | is forced to 1:1             |                 |                   |             |

| bit 10-8     |                                  |                              | RC Oscillator                                            | Postscaler bits              |                 |                   |             |

|              | 111 = FRC di                     |                              |                                                          |                              |                 |                   |             |

|              | 110 = FRC di<br>101 = FRC di     |                              |                                                          |                              |                 |                   |             |

|              | 100 = FRC di                     | •                            |                                                          |                              |                 |                   |             |

|              | 011 = FRC di                     | •                            |                                                          |                              |                 |                   |             |

|              | 010 = FRC di                     |                              |                                                          |                              |                 |                   |             |

|              | 001 = FRC di                     | vide-by-2<br>vide-by-1 (defa |                                                          |                              |                 |                   |             |

|              |                                  | •                            |                                                          |                              |                 |                   |             |

| bit 7-0      | Unimplomon                       | ted: Read as '               | o'                                                       |                              |                 |                   |             |

#### REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER

**Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **2:** If DOZEN = 1, writes to DOZE<2:0> are ignored.

- 3: If DOZE<2:0> = 000, the DOZEN bit cannot be set by the user; writes are ignored.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

#### 15.4 PWM Control Registers

#### R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 PTEN PTSIDL bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 PTOPS3 PTOPS2 PTOPS1 PTOPS0 PTCKPS1 PTCKPS0 PTMOD1 PTMOD0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 PTEN: PWMx Time Base Timer Enable bit 1 = PWMx time base is on 0 = PWMx time base is off bit 14 Unimplemented: Read as '0' bit 13 PTSIDL: PWMx Time Base Stop in Idle Mode bit 1 = PWMx time base halts in CPU Idle mode 0 = PWMx time base runs in CPU Idle mode bit 12-8 Unimplemented: Read as '0' bit 7-4 PTOPS<3:0>: PWMx Time Base Output Postscale Select bits 1111 = 1:16 postscale 0001 = 1:2 postscale 0000 = 1:1 postscale bit 3-2 PTCKPS<1:0>: PWMx Time Base Input Clock Prescale Select bits 11 = PWMx time base input clock period is 64 Tcy (1:64 prescale) 10 = PWMx time base input clock period is 16 Tcy (1:16 prescale) 01 = PWMx time base input clock period is 4 Tcy (1:4 prescale) 00 = PWMx time base input clock period is TCY (1:1 prescale) bit 1-0 PTMOD<1:0>: PWMx Time Base Mode Select bits 11 = PWMx time base operates in a Continuous Up/Down Count mode with interrupts for double **PWM updates** 10 = PWMx time base operates in a Continuous Up/Down Count mode 01 = PWMx time base operates in Single Pulse mode

#### REGISTER 15-1: PxTCON: PWMx TIME BASE CONTROL REGISTER

00 = PWMx time base operates in a Free-Running mode

#### 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit<sup>TM</sup> ( $I^2C^{TM}$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addresses

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addresses

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

#### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7-Bit and 10-Bit Addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-Bit Addressing

- I<sup>2</sup>C slave operation with 10-Bit Addressing

- I<sup>2</sup>C master operation with 7-Bit or 10-Bit Addressing

For details about the communication sequence in each of these modes, refer to the Microchip web site (www.microchip.com) for the latest *"dsPIC33/PIC24 Family Reference Manual"* sections.

## 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CxSTAT are read/write.

- I2CxRSR is the shift register used for shifting data

- I2CxRCV is the receive buffer and the register to which data bytes are written or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- · I2CxADD register holds the slave address

- ADD10 status bit indicates 10-Bit Addressing mode

- I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

#### **REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)**

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                      |

- **Note 1:** Refer to "**UART**" (DS70188) in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UART module for receive or transmit operation.

- **2:** This feature is available for 16x BRG mode (BRGH = 0) only.

### 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70635) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four edge input trigger sources

- · Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · Precise time measurement resolution of 200 ps

- Accurate current source suitable for capacitive measurement

- On-chip temperature measurement using a built-in diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 enables the module, the edge delay generation, sequencing of edges, and controls the current source and the output trigger. CTMUCON2 controls the edge source selection, edge source polarity selection and edge sampling mode. The CTMUICON register controls the selection and trim of the current source.

Figure 22-1 shows the CTMU block diagram.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| DC CHARACI       | TERISTICS                   |           | (unless oth  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |        |                             |  |  |  |

|------------------|-----------------------------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup>      | Max       | Units        | Conditions                                                                                                                                                                                           |        |                             |  |  |  |

| Operating Cur    | rent (IDD) <sup>(2)</sup> – | dsPIC33FJ | 32(GP/MC)10X | Devices                                                                                                                                                                                              |        |                             |  |  |  |

| DC20d            | 1                           | 2         | mA           | -40°C                                                                                                                                                                                                |        |                             |  |  |  |

| DC20a            | 1                           | 2         | mA           | +25°C                                                                                                                                                                                                | - 3.3V | LPRC                        |  |  |  |

| DC20b            | 1.1                         | 2         | mA           | +85°C                                                                                                                                                                                                | 3.3V   | (32.768 kHz) <sup>(3)</sup> |  |  |  |

| DC20c            | 1.3                         | 2         | mA           | +125°C                                                                                                                                                                                               |        |                             |  |  |  |

| DC21d            | 1.7                         | 3         | mA           | -40°C                                                                                                                                                                                                |        |                             |  |  |  |

| DC21a            | 2.3                         | 3         | mA           | +25°C                                                                                                                                                                                                | 2.21/  | 1 MIPS <sup>(3)</sup>       |  |  |  |

| DC21b            | 2.3                         | 3         | mA           | +85°C                                                                                                                                                                                                | 3.3V   | 1 MIPS(*)                   |  |  |  |

| DC21c            | 2.4                         | 3         | mA           | +125°C                                                                                                                                                                                               |        |                             |  |  |  |

| DC22d            | 7                           | 8.5       | mA           | -40°C                                                                                                                                                                                                |        |                             |  |  |  |

| DC22a            | 7                           | 8.5       | mA           | +25°C                                                                                                                                                                                                | - 3.3V | 4 MIPS <sup>(3)</sup>       |  |  |  |

| DC22b            | 7                           | 8.5       | mA           | +85°C                                                                                                                                                                                                | 3.3V   | 4 10119517                  |  |  |  |

| DC22c            | 7                           | 8.5       | mA           | +125°C                                                                                                                                                                                               |        |                             |  |  |  |

| DC23d            | 13.2                        | 17        | mA           | -40°C                                                                                                                                                                                                |        |                             |  |  |  |

| DC23a            | 13.2                        | 17        | mA           | +25°C                                                                                                                                                                                                |        | 10 MIPS <sup>(3)</sup>      |  |  |  |

| DC23b            | 13.2                        | 17        | mA           | +85°C                                                                                                                                                                                                | 3.3V   | 10 MIPS(*)                  |  |  |  |

| DC23c            | 13.2                        | 17        | mA           | +125°C                                                                                                                                                                                               | ]      |                             |  |  |  |

| DC24d            | 17                          | 22        | mA           | -40°C                                                                                                                                                                                                |        |                             |  |  |  |

| DC24a            | 17                          | 22        | mA           | +25°C                                                                                                                                                                                                | 2.21/  |                             |  |  |  |

| DC24b            | 17                          | 22        | mA           | +85°C                                                                                                                                                                                                | - 3.3V | 16 MIPS                     |  |  |  |

| DC24c            | 17                          | 22        | mA           | +125°C                                                                                                                                                                                               | 1      |                             |  |  |  |

#### TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD) (CONTINUED)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- CPU executing while(1) statement

- 3: These parameters are characterized, but not tested in manufacturing.

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

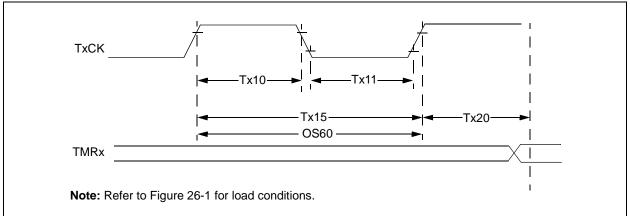

#### FIGURE 26-5: TIMER1/2/3 EXTERNAL CLOCK TIMING CHARACTERISTICS

#### Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) AC CHARACTERISTICS Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial -40°C $\leq$ TA $\leq$ +125°C for Extended Param Characteristic<sup>(2)</sup> Symbol Min Max Units Conditions Тур No. TA10 ТтхН T1CK High Synchronous Greater of: Must also meet ns Time mode 20 or Parameter TA15, (TCY + 20)/N N = prescale value (1, 8, 64, 256) Asynchronous 35 ns \_ \_\_\_\_ TA11 T1CK Low Must also meet TTXL Synchronous Greater of: ns Time mode 20 ns or Parameter TA15, (TCY + 20)/N N = prescale value (1, 8, 64, 256) Asynchronous 10 ns TA15 ΤτχΡ T1CK Input Synchronous Greater of: N = prescale value ns Period mode 40 or (1, 8, 64, 256) (2 TCY + 40)/N **OS60** Ft1 SOSC1/T1CK Oscillator DC 50 kHz \_\_\_\_ Input Frequency Range (oscillator enabled by setting the TCS (T1CON<1>) bit) TA20 TCKEXTMRL Delay from External T1CK 0.75 Tcy + 40 1.75 Tcy + 40 ns Clock Edge to Timer Increment

## TABLE 26-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

Note 1: Timer1 is a Type A.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

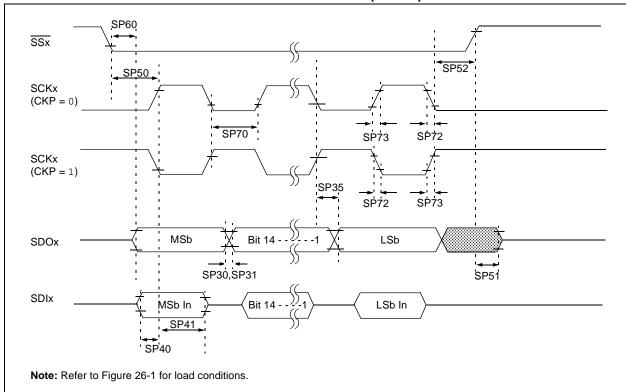

FIGURE 26-23: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

# TABLE 26-43:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X

| AC CH        | ARACTERIS             | TICS                                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |  |  |

|--------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                                 | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |  |

| SP70         | TscP                  | Maximum SCKx Input Frequency                                 | —                                                                                                                                                                                                                                                                                   | -                  | 15  | MHz   | See Note 3                           |  |  |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                                                                                                                   |                    |     | ns    | See Parameter DO32 and <b>Note 4</b> |  |  |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —                                                                                                                                                                                                                                                                                   | _                  | —w  | ns    | See Parameter DO31 and <b>Note 4</b> |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | —                                                                                                                                                                                                                                                                                   |                    |     | ns    | See Parameter DO32 and <b>Note 4</b> |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —                                                                                                                                                                                                                                                                                   |                    |     | ns    | See Parameter DO31 and <b>Note 4</b> |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                                                                                                                                                                   | 6                  | 20  | ns    |                                      |  |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                                                                                                                                                                                                                                                  | _                  | _   | ns    |                                      |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                                                                                                                                                                                                                                                  |                    |     | ns    |                                      |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                                                                                                                                                                                                                                                  |                    |     | ns    |                                      |  |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                                                                                 | _                  | _   | ns    |                                      |  |  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                                                                                                                                                                                                                                                  | _                  | 50  | ns    | See Note 4                           |  |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                                                                                                                                                                                                                                                        | -                  | _   | ns    | See Note 4                           |  |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

#### 27.1 High-Temperature DC Characteristics

#### TABLE 27-1: OPERATING MIPS VS. VOLTAGE

|                | VDD Range                  | Temperature Range | Max MIPS                                                       |

|----------------|----------------------------|-------------------|----------------------------------------------------------------|

| Characteristic | (in Volts)                 | (in °C)           | dsPIC33FJ16(GP/MC)101/102 and<br>dsPIC33FJ32(GP/MC)101/102/104 |

| HDC5           | VBOR – 3.6V <sup>(1)</sup> | -40°C to +150°C   | 5                                                              |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules, such as the ADC, etc., may have degraded performances below VDDMIN.

#### TABLE 27-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| High Temperature Devices                                                                                                                                                               |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40 | —           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40 | —           | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | I   | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (   | TJ — TA)/θJ | IA   | W    |

#### TABLE 27-3: DC CHARACTERISTICS: OPERATING CURRENT (IDD))

| DC CHARACTERISTICS                                      |         |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |      |                   |  |  |

|---------------------------------------------------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|--|--|

| Parameter<br>No.                                        | Typical | Мах | Units                                                                                                                                                  |      | Conditions        |  |  |

| Operating Current (IDD) – dsPIC33FJ16(GP/MC)10X Devices |         |     |                                                                                                                                                        |      |                   |  |  |

| DC20e                                                   | 1.3     | 1.7 | mA                                                                                                                                                     | 3.3V | LPRC (32.768 kHz) |  |  |

| DC22e                                                   | 7.0     | 8.5 | mA                                                                                                                                                     | 3.3V | 5 MIPS            |  |  |

| DC Characteristics                          | <br>282 |

|---------------------------------------------|---------|

| Brown-out Reset (BOR)                       |         |

| Doze Current (IDOZE)                        |         |

| High Temperature                            |         |

| I/O Pin Input Specifications                |         |

| I/O Pin Output Specifications               |         |

| Idle Current (IIDLE)                        |         |

| Operating Current (IDD)                     |         |

| Operating MIPS vs. Voltage                  |         |

| Power-Down Current (IPD)                    |         |

| Program Memory                              |         |

| Temperature and Voltage Specifications      |         |

| Thermal Operating Conditions                |         |

| Thermal Packaging                           |         |

| Development Support                         |         |

| Assembler                                   |         |

| MPASM Assembler                             | <br>278 |

| C Compilers                                 |         |

| MPLAB XC                                    | <br>278 |

| Demonstration/Development Boards            | <br>280 |

| Evaluation and Starter Kits                 |         |

| MPLAB Assembler, Linker, Librarian          |         |

| MPLAB ICD 3 In-Circuit Debugger System      | <br>279 |

| MPLAB PM3 Device Programmer                 | <br>279 |

| MPLAB REAL ICE In-Circuit Emulator System   |         |

| MPLAB X Integrated Development              |         |

| Environment Software                        | <br>277 |

| MPLINK Object Linker/MPLIB Object Librarian | <br>278 |

| PICkit 3 In-Circuit Debugger/Programmer     | <br>279 |

| Software Simulator (MPLAB X SIM)            | <br>279 |

| Third-Party Development Tools               |         |

| Doze Mode                                   | <br>134 |

| dsPIC33FJ16(GP/MC)101/102                   |         |

| Device Features                             | <br>2   |

| dsPIC33FJ32(GP/MC)101/102/104               |         |

| Device Features                             | <br>3   |

| F                                           |         |

| -                                           |         |

| Electrical Characteristics                  | <br>281 |

| 126 |

|-----|

|     |

|     |

|     |

|     |

|     |

|     |

#### F

| Flash Program Memory  |  |

|-----------------------|--|

| Control Registers     |  |

| Operations            |  |

| Programming Algorithm |  |

| RTSP Operation        |  |

| Table Instructions    |  |

|                       |  |

#### G

| Getting Started with 16-Bit DSCs        |    |

|-----------------------------------------|----|

| Analog and Digital Pins Configuration   |    |

| During ICSP                             | 36 |

| Connection Requirements                 | 33 |

| Decoupling Capacitors                   | 33 |

| External Oscillator Pins                | 35 |

| ICSP Pins                               | 35 |

| Master Clear (MCLR) Pin                 | 34 |

| Oscillator Value Conditions on Start-up | 36 |

| Unused I/Os                             | 36 |

#### Н

| High-Temperature Electrical Characteristics            |

|--------------------------------------------------------|

|                                                        |

| VO Dorto 120                                           |

| I/O Ports                                              |

| Configuring Analog Port Pins                           |

| Open-Drain Configuration                               |

| Parallel I/O (PIO)                                     |

| Write/Read Timing 141                                  |

| l <sup>2</sup> C                                       |

| Control Registers                                      |

| Operating Modes                                        |

| Registers                                              |

| In-Circuit Debugger268                                 |

| In-Circuit Serial Programming (ICSP)                   |

| Input Capture 175                                      |

| Control Register 176                                   |

| Input Change Notification (ICN)141                     |

| Instruction Addressing Modes73                         |

| File Register Instructions 73                          |

| Fundamental Modes Supported74                          |

| MAC Instructions74                                     |

| MCU Instructions73                                     |

| Move and Accumulator Instructions74                    |

| Other Instructions74                                   |

| Instruction Set                                        |

|                                                        |

| Summary                                                |

| Overview                                               |

| Symbols Used in Opcode Descriptions                    |

| Instruction-Based Power-Saving Modes                   |

| Idle                                                   |

| Sleep                                                  |

| Internet Address                                       |

| Interrupt Controller                                   |

| Interrupt Registers                                    |

| IECx                                                   |

| IFSx                                                   |

| INTCON1                                                |

| INTCON2                                                |

| INTTREG                                                |

| IPCx                                                   |

| Interrupt Setup Procedures                             |

| Initialization                                         |

| Interrupt Disable                                      |

| Interrupt Disable                                      |

| Trap Service Routine (TSR)                             |

|                                                        |

| Interrupt Vectors                                      |

| Reset Sequence                                         |

| Interrupt Vector Table (IVT)                           |

| Interrupts Coincident with Power Save Instructions 134 |

| L                                                      |

|                                                        |

| LPRC Oscillator                                        |

| Use with WDT267                                        |

| Μ                                                      |

|                                                        |

| Memory Organization                                    |

| Microchip Internet Web Site                            |

|                                                        |

| Momory organization          |     |

|------------------------------|-----|

| Microchip Internet Web Site  | 387 |

| Modulo Addressing            | 75  |

| Applicability                |     |

| Operation Example            |     |

| Start and End Address        | 75  |

| W Address Register Selection | 75  |

|                              |     |

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737