Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc102-i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 |  |

|-------------------------------------------------------------|--|

| NOTES:                                                      |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                                                                                                                                                 |

|----------|-------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVDD     | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times. AVDD is connected to VDD in the 18-pin dsPIC33FJXXGP101 and 20-pin dsPIC33FJXXMC101 devices. In all other devices, AVDD is separated from VDD. |

| AVss     | Р           | Р              | No  | Ground reference for analog modules. AVss is connected to Vss in the 18-pin dsPIC33FJXXGP101 and 20-pin dsPIC33FJXXMC101 devices. In all other devices, AVss is separated from Vss.                                         |

| VDD      | Р           | _              | No  | Positive supply for peripheral logic and I/O pins.                                                                                                                                                                          |

| VCAP     | Р           | _              | No  | CPU logic filter capacitor connection.                                                                                                                                                                                      |

| Vss      | Р           | _              | No  | Ground reference for logic and I/O pins.                                                                                                                                                                                    |

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power ST = Schmitt Trigger input with CMOS levels O = Output I = Input PPS = Peripheral Pin Select

- **Note 1:** An external pull-down resistor is required for the FLTA1 pin in dsPIC33FJXXMC101 (20-pin) devices.

- 2: The FLTA1 pin and the PWM1Lx/PWM1Hx pins are available in dsPIC(16/32)MC10X devices only.

- 3: The FLTB1 pin is available in dsPIC(16/32)MC102/104 devices only.

- 4: The PWM Fault pins are enabled during any Reset event. Refer to **Section 15.2 "PWM Faults"** for more information on the PWM Faults.

- 5: Not all pins are available on all devices. Refer to the specific device in the "Pin Diagrams" section for availability.

- 6: These pins are available in dsPIC33FJ32(GP/MC)104 (44-pin) devices only.

### TABLE 4-37: SYSTEM CONTROL REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6  | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 | All<br>Resets |

|-----------|-------------|--------|--------|--------|--------|--------|---------|---------|---------|---------|--------|----------|-------|-------|-------|---------|-------|---------------|

| RCON      | 0740        | TRAPR  | IOPUWR | 1      | _      | _      | _       | СМ      | VREGS   | EXTR    | SWR    | SWDTEN   | WDTO  | SLEEP | IDLE  | BOR     | POR   | xxxx(1)       |

| OSCCON    | 0742        | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK | IOLOCK | LOCK     | _     | CF    | _     | LPOSCEN | OSWEN | 0300(2)       |

| CLKDIV    | 0744        | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | _       | -      | _        | _     | -     | _     | _       | -     | 3040          |

| OSCTUN    | 0748        | _      | _      | _      | _      | _      | _       | _       | _       | _       | _      | TUN<5:0> |       |       |       | 0000    |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the FOSC Configuration bits and by type of Reset.

### **TABLE 4-38: NVM REGISTER MAP**

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | AII<br>Resets |

|-----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------------|-------|-------|-------|--------|--------|--------|--------|---------------|

| NVMCON    | 0760        | WR     | WREN   | WRERR  | _      | _      | _      | _     | _     | _           | ERASE | _     | _     | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000(1)       |

| NVMKEY    | 0766        | _      | _      | _      | _      | _      | _      | _     | _     | NVMKEY<7:0> |       |       |       |        | 0000   |        |        |               |

dsPlC33FJ16(GP/MC)101/102 AND dsPlC33FJ32(GP/MC)101/102/104

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

### TABLE 4-39: PMD REGISTER MAP

| File Name | SFR<br>Addr | Bit 15              | Bit 14              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------------|---------------------|---------------------|--------|--------|--------|--------|-----------------------|-------|--------|-------|-------|-------|--------|--------|-------|-------|---------------|

| PMD1      | 0770        | T5MD <sup>(2)</sup> | T4MD <sup>(2)</sup> | T3MD   | T2MD   | T1MD   | _      | PWM1MD <sup>(1)</sup> | 1     | I2C1MD | -     | U1MD  | -     | SPI1MD | _      | _     | AD1MD | 0000          |

| PMD2      | 0772        | -                   | _                   | -      | _      | _      | IC3MD  | IC2MD                 | IC1MD | _      | _     | _     | -     | _      | _      | OC2MD | OC1MD | 0000          |

| PMD3      | 0774        | _                   | _                   |        | 1      | _      | CMPMD  | RTCCMD                | _     | _      | _     | _     | _     | _      | _      | _     |       | 0000          |

| PMD4      | 0776        |                     | _                   | _      | _      | _      | _      | _                     | _     | _      | _     | _     | _     | _      | CTMUMD | _     | _     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is available in dsPIC33FJXXMC10X devices only.

2: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

#### **RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20** REGISTER 10-9:

| U-0    | U-0 | U-0 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _      | _   | _   | SCK1R4 <sup>(1)</sup> | SCK1R3 <sup>(1)</sup> | SCK1R2 <sup>(1)</sup> | SCK1R1 <sup>(1)</sup> | SCK1R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | _   | _   | SDI1R4 <sup>(1)</sup> | SDI1R3 <sup>(1)</sup> | SDI1R2 <sup>(1)</sup> | SDI1R1 <sup>(1)</sup> | SDI1R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-8 SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits(1)

11111 = Input tied to Vss

11110 = Reserved

11010 = Reserved

11001 = Input tied to RP25

00001 = Input tied to RP1

00000 = Input tied to RP0

bit 7-5 Unimplemented: Read as '0'

SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits(1) bit 4-0

11111 = Input tied to Vss

11110 = Reserved

11010 = Reserved

11001 = Input tied to RP25

00001 = Input tied to RP1

00000 = Input tied to RP0

Note 1: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

### REGISTER 10-10: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | _   | _   | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1IN) to the Corresponding RPn Pin bits

11111 = Input tied to Vss

11110 = Reserved

11010 = Reserved

11001 = Input tied to RP25

00001 = Input tied to RP1

00000 = Input tied to RP0

### REGISTER 12-3: T4CON: TIMER4 CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-------|-----|-----|-----|-----|-------|

| TON    | _   | TSIDL | _   | _   | _   | _   | _     |

| bit 15 |     |       |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0  | R/W-0  | R/W-0 | U-0 | R/W-0 | U-0   |

|-------|-------|--------|--------|-------|-----|-------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | T32   | _   | TCS   | _     |

| bit 7 |       |        |        |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 TON: Timer4 On bit

When T32 = 1:

1 = Starts 32-bit Timer4/5 0 = Stops 32-bit Timer4/5

When T32 = 0:

1 = Starts 16-bit Timer4 0 = Stops 16-bit Timer4

bit 14 Unimplemented: Read as '0'

bit 13 TSIDL: Timer4 Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 **Unimplemented:** Read as '0'

bit 6 TGATE: Timer4 Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timer4 Input Clock Prescale Select bits

11 = 1:256 10 = 1:64 01 = 1:8 00 = 1:1

bit 3 T32: 32-Bit Timer Mode Select bit

1 = Timer4 and Timer5 form a single 32-bit timer 0 = Timer4 and Timer5 act as two 16-bit timers

bit 2 Unimplemented: Read as '0'

bit 1 TCS: Timer4 Clock Source Select bit

1 = External clock from pin, T4CK (on the rising edge)

0 = Internal clock (FCY)

bit 0 **Unimplemented:** Read as '0'

Note 1: This register is available in dsPIC33FJ32(GP/MC)10X devices only.

# 17.3 I<sup>2</sup>C Control Registers

### REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-1, HC | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|---------|-----------|--------|-------|--------|-------|

| I2CEN  | _   | I2CSIDL | SCLREL    | IPMIEN | A10M  | DISSLW | SMEN  |

| bit 15 |     |         |           |        |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0, HC |

|-------|-------|-------|-----------|-----------|-----------|-----------|-----------|

| GCEN  | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |

| bit 7 |       |       |           |           |           |           | bit 0     |

**Legend:** HC = Hardware Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 I2CEN: I2Cx Enable bit

1 = Enables the I2Cx module, and configures the SDAx and SCLx pins as serial port pins

0 = Disables the I2Cx module; all I<sup>2</sup>C<sup>TM</sup> pins are controlled by port functions

bit 14 Unimplemented: Read as '0'

bit 13 I2CSIDL: I2Cx Stop in Idle Mode bit

1 = Discontinues module operation when device enters an Idle mode

0 = Continues module operation in Idle mode

bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

1 = Releases SCLx clock

0 = Holds SCLx clock low (clock stretch)

If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clears at beginning of every slave data byte transmission. Hardware clears at end of every slave address byte reception. Hardware clears at every slave data byte reception.

If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clears at beginning of every slave data byte transmission. Hardware clears at end of every slave address byte reception.

bit 11 IPMIEN: Intelligent Peripheral Management Interface (IPMI) Enable bit

1 = IPMI mode is enabled; all addresses are Acknowledged

0 = IPMI mode is disabled

bit 10 A10M: I2Cx 10-Bit Slave Address bit

1 = I2CxADD is a 10-bit slave address

0 = I2CxADD is a 7-bit slave address

bit 9 DISSLW: Disable Slew Rate Control bit

1 = Slew rate control is disabled

0 = Slew rate control is enabled

bit 8 SMEN: SMBus Input Levels bit

1 = Enables I/O pin thresholds compliant with SMBus specification

0 = Disables SMBus input thresholds

bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

1 = Enables interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

0 = General call address is disabled

# 19.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Analog-to-Digital Converter (ADC)" (DS70183) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have up to 14 ADC module input channels.

# 19.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- Up to 14 analog input pins

- Four Sample-and-Hold (S&H) circuits for simultaneous sampling of up to four analog input pins

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

- 16-word conversion result buffer

Depending on the particular device pinout, the ADC can have up to 14 analog input pins.

Block diagrams of the ADC module are shown in Figure 19-1 through Figure 19-3.

### 19.2 ADC Initialization

To configure the ADC module:

- 1. Select port pins as analog inputs (AD1PCFGL<15:0>).

- Select the analog conversion clock to match the desired data rate with the processor clock (ADxCON3<7:0>).

- 3. Determine how many Sample-and-Hold channels will be used (ADxCON2<9:8>).

- 4. Select the appropriate sample and conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>).

- Select the way conversion results are presented in the buffer (ADxCON1<9:8>).

- 6. Turn on the ADC module (ADxCON1<15>).

- 7. Configure the ADC interrupt (if required):

- a) Clear the ADxIF bit.

- o) Select the ADC interrupt priority.

# REGISTER 19-7: AD1PCFGL: ADC1 PORT CONFIGURATION REGISTER LOW(1,2,3)

| R/W-0                   | U-0 | U-0 | R/W-0                         | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------------------|-----|-----|-------------------------------|-------|-------|-------|-------|--|

| PCFG15 <sup>(4,5)</sup> | _   | _   | PCFG<12:0> <sup>(4,5,7)</sup> |       |       |       |       |  |

| bit 15                  |     |     | bit 8                         |       |       |       |       |  |

| R/W-0                        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------------------------|-------|-------|-------|-------|-------|-------|-------|

| PCFG<7:0> <sup>(4,5,6)</sup> |       |       |       |       |       |       |       |

| bit 7                        |       |       |       |       |       |       |       |

Leaend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **PCFG15:** ADC1 Port Configuration Control bit<sup>(4,5)</sup>

1 = Port pin is in Digital mode, port read input is enabled, ADC1 input multiplexer is connected to AVss

0 = Port pin is in Analog mode, port read input is disabled, ADC1 samples pin voltage

bit 14-13 Unimplemented: Read as '0'

bit 12-0 **PCFG<12:0>:** ADC1 Port Configuration Control bits<sup>(4,5,6,7)</sup>

1 = Port pin is in Digital mode, port read input is enabled, ADC1 input multiplexer is connected to AVss

0 = Port pin is in Analog mode, port read input is disabled, ADC1 samples pin voltage

**Note 1:** On devices without 14 analog inputs, all PCFGx bits are R/W by user. However, PCFGx bits are ignored on ports without a corresponding input on the device.

- **2:** PCFGx = ANx, where x = 0 through 12 and 15.

- **3:** The PCFGx bits have no effect if the ADC module is disabled by setting the AD1MD bit in the PMD1 register. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

- **4:** Pins shared with analog functions (i.e., ANx) are analog by default and therefore, must be set by the user to enable any digital function on that pin. Reading any port pin with the analog function enabled will return a '0', regardless of the signal input level.

- 5: The PCFG<15,12:11,8:6> bits are available in the dsPIC33FJ32(GP/MC)104 devices only and are reserved in all other devices.

- **6:** The PCFG<5:4> bits are available on all devices, excluding the dsPIC33FJXX(GP/MC)101 devices, where they are reserved.

- 7: The PCFG<10:9> bits are available on all devices, excluding the dsPIC33FJ16(GP/MC)101/102 devices, where they are reserved.

#### REGISTER 20-2: CMxCON: COMPARATOR x CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----|-----|-----|-------|-------|

| CON    | COE   | CPOL  | _   | _   | _   | CEVT  | COUT  |

| bit 15 |       |       |     |     |     |       | bit 8 |

| R/W-0  | R/W-0  | U-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-----|-----|-------|-------|

| EVPOL1 | EVPOL0 | _   | CREF  | _   | _   | CCH1  | CCH0  |

| bit 7  |        |     |       |     |     |       | bit 0 |

Legend:

W = Writable bit R = Readable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **CON:** Comparator x Enable bit

> 1 = Comparator x is enabled 0 = Comparator x is disabled

bit 14 **COE:** Comparator x Output Enable bit

1 = Comparator output is present on the CxOUT pin

0 = Comparator output is internal only

bit 13 **CPOL:** Comparator x Output Polarity Select bit

> 1 = Comparator x output is inverted 0 = Comparator x output is not inverted

Unimplemented: Read as '0'

bit 12-10 bit 9 **CEVT:** Comparator x Event bit

> 1 = Comparator x event according to EVPOL<1:0> settings occurred; disables future triggers and interrupts until the bit is cleared

0 = Comparator x event did not occur

bit 8 **COUT:** Comparator x Output bit

When CPOL = 0 (non-inverted polarity):

1 = VIN+ > VIN-0 = VIN+ < VIN-

When CPOL = 1 (inverted polarity):

1 = VIN+ < VIN-0 = VIN+ > VIN-

bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits

11 = Trigger/event/interrupt is generated on any change of the comparator output (while CEVT = 0)

10 = Trigger/event/interrupt is generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

Low-to-high transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

High-to-low transition of the comparator output.

01 = Trigger/event/interrupt is generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

Low-to-high transition of the comparator output. 00 = Trigger/event/interrupt generation is disabled

bit 5 Unimplemented: Read as '0'

# 21.2 RTCC Control Registers

# REGISTER 21-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0 | R/W-0   | R-0     | R-0                    | R/W-0 | R/W-0   | R/W-0   |

|----------------------|-----|---------|---------|------------------------|-------|---------|---------|

| RTCEN <sup>(2)</sup> | _   | RTCWREN | RTCSYNC | HALFSEC <sup>(3)</sup> | RTCOE | RTCPTR1 | RTCPTR0 |

| bit 15               |     |         |         |                        |       |         | bit 8   |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                                                                 |                      |                    |  |  |

|-------------------|-----------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | eadable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                | '0' = Bit is cleared | x = Bit is unknown |  |  |

RTCEN: RTCC Enable bit(2)

1 = RTCC module is enabled0 = RTCC module is disabled

bit 14 Unimplemented: Read as '0'

bit 15

bit 13 RTCWREN: RTCC Value Registers Write Enable bit

1 = RTCVALH and RTCVALL registers can be written to by the user

0 = RTCVALH and RTCVALL registers are locked out from being written to by the user

bit 12 RTCSYNC: RTCC Value Registers Read Synchronization bit

1 = RTCVALH, RTCVALL and ALCFGRPT registers can change while reading, due to a rollover ripple, resulting in an invalid data read. If the register is read twice and the results are the same data, the data can be assumed to be valid.

0 = RTCVALH, RTCVALL or ALCFGRPT registers can be read without concern over a rollover ripple

bit 11 HALFSEC: Half-Second Status bit (3)

1 = Second half period of a second

0 = First half period of a second

bit 10 RTCOE: RTCC Output Enable bit

1 = RTCC output is enabled

0 = RTCC output is disabled

bit 9-8 RTCPTR<1:0>: RTCC Value Register Window Pointer bits

Points to the corresponding RTCC Value registers when reading RTCVALH and RTCVALL registers; the RTCPTR<1:0> value decrements on every read or write of RTCVALH until it reaches '00'.

RTCVAL<15:8>:

00 = MINUTES

01 = WEEKDAY

10 = MONTH

11 = Reserved

RTCVAL<7:0>:

00 = SECONDS

01 = HOURS

10 = DAY

11 = YEAR

Note 1: The RCFGCAL register is only affected by a POR.

- **2:** A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed

as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note:

For more details on the instruction set, refer to the "16-Bit MCU and DSC Programmer's Reference Manual" (DS70157).

TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                       |

|-----------------|-----------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                   |

| (text)          | Means "content of text"                                                           |

| [text]          | Means "the location addressed by text"                                            |

| { }             | Optional field or operation                                                       |

| <n:m></n:m>     | Register bit field                                                                |

| .b              | Byte mode selection                                                               |

| .d              | Double-Word mode selection                                                        |

| .S              | Shadow register select                                                            |

| .W              | Word mode selection (default)                                                     |

| Acc             | One of two accumulators {A, B}                                                    |

| AWB             | Accumulator write-back destination address register ∈ {W13, [W13]+ = 2}           |

| bit4            | 4-bit bit selection field (used in word addressed instructions) ∈ {015}           |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero              |

| Expr            | Absolute address, label or expression (resolved by the linker)                    |

| f               | File register address ∈ {0x00000x1FFF}                                            |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                    |

| lit4            | 4-bit unsigned literal ∈ {015}                                                    |

| lit5            | 5-bit unsigned literal ∈ {031}                                                    |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                   |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode            |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                             |

| None            | Field does not require an entry, can be blank                                     |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate       |

| PC              | Program Counter                                                                   |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                 |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                             |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                    |

| Wb              | Base W register ∈ {W0W15}                                                         |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                 |

| Wdo             | Destination W register ∈ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm, Wn          | Dividend, Divisor Working register pair (direct addressing)                       |

## 25.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers (MCU) and dsPIC® digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB® X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK™ Object Linker/ MPLIB™ Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 25.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

TABLE 26-12: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHV       | RACTER | ISTICS                               |         | rd Opera<br>otherw |         |                                  | s: 3.0V to 3.6V                                            |  |

|--------------|--------|--------------------------------------|---------|--------------------|---------|----------------------------------|------------------------------------------------------------|--|

| DC CHA       | MACIEN | 131103                               | Operati | ng tempe           | erature |                                  | ≤ Ta ≤ +85°C for Industrial                                |  |

|              | 1      |                                      |         |                    |         | -40°C ≤ TA ≤ +125°C for Extended |                                                            |  |

| Param<br>No. | Symbol | Characteristic <sup>(3)</sup>        | Min     | Typ <sup>(1)</sup> | Max     | Units                            | Conditions                                                 |  |

|              |        | Program Flash Memory                 |         |                    |         |                                  |                                                            |  |

| D130a        | ЕР     | Cell Endurance                       | 10,000  | _                  | _       | E/W                              | -40°C to +125°C                                            |  |

| D131         | VPR    | VDD for Read                         | VMIN    | _                  | 3.6     | V                                | VMIN = Minimum operating voltage                           |  |

| D132b        | VPEW   | VDD for Self-Timed Write             | VMIN    | _                  | 3.6     | V                                | VMIN = Minimum operating voltage                           |  |

| D134         | TRETD  | Characteristic Retention             | 20      | _                  | _       | Year                             | Provided no other specifications are violated              |  |

| D135         | IDDP   | Supply Current during<br>Programming | _       | 10                 | _       | mA                               |                                                            |  |

| D137a        | TPE    | Page Erase Time                      | 20.1    | _                  | 26.5    | ms                               | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>  |  |

| D137b        | TPE    | Page Erase Time                      | 19.5    | _                  | 27.3    | ms                               | TPE = 168517 FRC cycles,<br>TA = +125°C, See <b>Note 2</b> |  |

| D138a        | Tww    | Word Write Cycle Time                | 47.4    | _                  | 49.3    | μs                               | Tww = 355 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>     |  |

| D138b        | Tww    | Word Write Cycle Time                | 47.4    |                    | 49.3    | μs                               | Tww = 355 FRC cycles,<br>TA = +125°C, See <b>Note 2</b>    |  |

- Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b'0111111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

- 3: These parameters are ensured by design, but are not characterized or tested in manufacturing.

### **TABLE 26-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS**

| DC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |     |     |     |       |                                                    |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|----------------------------------------------------|

| Param<br>No.       | Symbol | Characteristics                                                                                                                                                                                                                                  | Min | Тур | Max | Units | Comments                                           |

| _                  | CEFC   | External Filter Capacitor Value <sup>(1)</sup>                                                                                                                                                                                                   | 4.7 | 10  | _   | μF    | Capacitor must be low series resistance (< 5 ohms) |

**Note 1:** Typical VCAP voltage = 2.5V when VDD  $\geq VDDMIN$ .

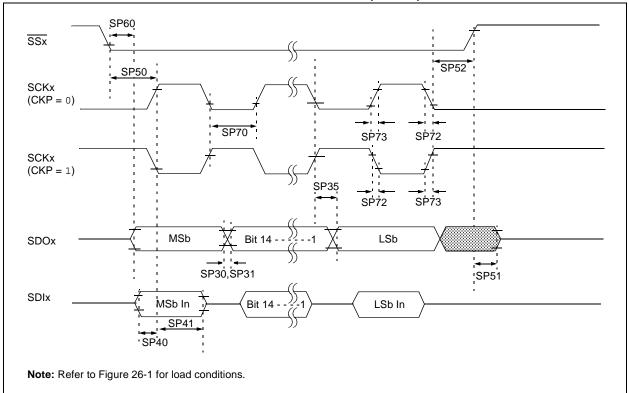

FIGURE 26-15: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ16(GP/MC)10X

TABLE 26-44: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING REQUIREMENTS FOR dsPIC33FJ32(GP/MC)10X

| AC CHA       | ARACTERIST            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |              |                    |     |       |                                      |

|--------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                    | Min          | Typ <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70         | TscP                  | Maximum SCKx Input Frequency                                                                                                                                                                                                                     | _            | _                  | 11  | MHz   | See Note 3                           |

| SP72         | TscF                  | SCKx Input Fall Time                                                                                                                                                                                                                             | _            |                    | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73         | TscR                  | SCKx Input Rise Time                                                                                                                                                                                                                             | _            |                    | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                                                                                                                                                                                                       | _            |                    | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                                                                                                                                                                                                       | _            | _                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge                                                                                                                                                                                                           | _            | 6                  | 20  | ns    |                                      |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to First SCKx Edge                                                                                                                                                                                                        | 30           | _                  | _   | ns    |                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                       | 30           | _                  | _   | ns    |                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                        | 30           |                    | _   | ns    |                                      |

| SP50         | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx Input                                                                                                                                                                                                                    | 120          | _                  | _   | ns    |                                      |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                                                                                                           | 10           | _                  | 50  | ns    | See Note 4                           |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                                                                                                                                                                                              | 1.5 Tcy + 40 |                    |     | ns    | See Note 4                           |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

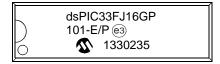

# 28.0 PACKAGING INFORMATION

# 28.1 Package Marking Information

18-Lead PDIP

18-Lead SOIC

20-Lead PDIP

20-Lead SSOP

20-Lead SOIC

Example

Example

Example

Example

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note:** If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information.

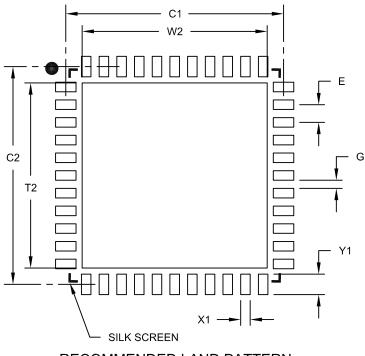

# 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimension Limits           |             | MIN  | NOM      | MAX  |

| Contact Pitch              | E           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 6.80 |

| Optional Center Pad Length | T2          |      |          | 6.80 |

| Contact Pad Spacing        | C1          |      | 8.00     |      |

| Contact Pad Spacing        | C2          |      | 8.00     |      |

| Contact Pad Width (X44)    | X1          |      |          | 0.35 |

| Contact Pad Length (X44)   | Y1          |      |          | 0.80 |

| Distance Between Pads      | G           | 0.25 |          |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

| SPIx Master Transmit Mode (Half-Duplex)         |       |

|-------------------------------------------------|-------|

| for dsPIC33FJ16(GP/MC)10X                       | . 305 |

| SPIx Master Transmit Mode (Half-Duplex)         |       |

| for dsPIC33FJ32(GP/MC)10X                       | .317  |

| SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 0, |       |

| SMP = 0) for $dsPIC33FJ16(GP/MC)10X$            | . 315 |

| SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 0, |       |

| SMP = 0) for $dsPIC33FJ32(GP/MC)10X$            | . 327 |

| SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 1, |       |

| SMP = 0) for $dsPIC33FJ16(GP/MC)10X$            | . 313 |

| SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 1, |       |

| SMP = 0) for $dsPIC33FJ32(GP/MC)10X$            | . 325 |

| SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 0, |       |

| SMP = 0) for $dsPIC33FJ16(GP/MC)10X$            | . 309 |

| SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 0, |       |

| SMP = 0) for dsPIC33FJ32(GP/MC)10X              | . 321 |

| SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 1, |       |

| SMP = 0) for $dsPIC33FJ16(GP/MC)10X$            | . 311 |

| SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 1, |       |

| SMP = 0) for $dsPIC33FJ32(GP/MC)10X$            | . 323 |

| Timer1 External Clock                           | . 299 |

| Timer2/4 External Clock                         | . 300 |

| Timer3/5 External Clock                         | . 300 |

| Timing Specifications                           |       |

| Comparator Module                               | . 336 |

| Comparator Timing                               | . 336 |

| Comparator Voltage Reference                    |       |

| Comparator Voltage Reference Settling Time      | . 336 |

| CTMLI Current Source                            | 337   |

| U                               |     |

|---------------------------------|-----|

| UART                            |     |

| Control Registers               | 213 |

| Helpful Tips                    | 212 |

| Resources                       | 212 |

| Universal Asynchronous Receiver |     |

| Transmitter (UART)              |     |

| Using the RCON Status Bits      | 94  |

| V                               |     |

| Voltage Regulator (On-Chip)     | 266 |

| W                               |     |

| Watchdog Timer (WDT)            | 267 |

| Programming Considerations      | 267 |

| WWW Address                     |     |

| WWW, On-Line Support            | 24  |

|                                 |     |