Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc102t-e-ml |

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33/PIC24 Family Reference Manual" sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSs pins, if present on the device (regardless if ADC module is not used) (see Section 2.2 "Decoupling Capacitors")

- VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1 µF (100 nF), 10V-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within

one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-Bit MCU and DSC Programmer's Reference Manual" (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend.

The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- · Signed or Unsigned DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

TABLE 3-1: DSP INSTRUCTIONS SUMMARY

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

| TABLE 4-7: | TIMERS REGISTER MAP FOR dsPIC33FJ16(GP/MC)10X DEVICES |

|------------|-------------------------------------------------------|

| IADEL T'I. |                                                       |

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8        | Bit 7         | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|-------------|--------------|---------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100        |        |        |        |        |        |        |             | Timer1       | Register      |              |        |        |       |       |       |       | 0000          |

| PR1         | 0102        |        |        |        |        |        |        |             | Period F     | Register 1    |              |        |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON    | 1      | TSIDL  |        | _      | _      | -           | _            | _             | TGATE        | TCKPS1 | TCKPS0 | -     | TSYNC | TCS   | 1     | 0000          |

| TMR2        | 0106        |        |        |        |        |        |        |             | Timer2       | Register      |              |        |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108        |        |        |        |        |        | Tim    | er3 Holding | Register (fo | r 32-bit time | r operations | only)  |        |       |       |       |       | xxxx          |

| TMR3        | 010A        |        |        |        |        |        |        |             | Timer3       | Register      |              |        |        |       |       |       |       | 0000          |

| PR2         | 010C        |        |        |        |        |        |        |             | Period F     | Register 2    |              |        |        |       |       |       |       | FFFF          |

| PR3         | 010E        |        |        |        |        |        |        |             | Period F     | Register 3    |              |        |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON    | -      | TSIDL  |        | _      | _      | -           | _            | _             | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | 1     | 0000          |

| T3CON       | 0112        | TON    |        | TSIDL  | _      | _      | _      |             | _            | _             | TGATE        | TCKPS1 | TCKPS0 | -     | _     | TCS   | -     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-8: TIMERS REGISTER MAP FOR DSPIC33FJ32(GP/MC)10X DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8        | Bit 7          | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|---------------|--------------|----------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100        |        |        |        |        |        |        |               | Timer1       | Register       |              |        |        |       |       |       |       | 0000          |

| PR1         | 0102        |        |        |        |        |        |        |               | Period F     | Register 1     |              |        |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON    | -      | TSIDL  |        | _      | _      | _             | _            | _              | TGATE        | TCKPS1 | TCKPS0 |       | TSYNC | TCS   | -     | 0000          |

| TMR2        | 0106        |        |        |        |        |        |        |               | Timer2       | Register       |              |        |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108        |        |        |        |        |        | Tim    | er3 Holding   | Register (fo | r 32-bit timei | operations   | only)  |        |       |       |       |       | xxxx          |

| TMR3        | 010A        |        |        |        |        |        |        |               | Timer3       | Register       |              |        |        |       |       |       |       | 0000          |

| PR2         | 010C        |        |        |        |        |        |        |               | Period F     | Register 2     |              |        |        |       |       |       |       | FFFF          |

| PR3         | 010E        |        |        |        |        |        |        |               | Period F     | Register 3     |              |        |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON    | _      | TSIDL  | -      |        | _      | _             | _            | _              | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T3CON       | 0112        | TON    | _      | TSIDL  | -      |        | _      | _             | _            | _              | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114        |        |        |        |        |        |        |               | Timer4       | Register       |              |        |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        |        |        |        |        |        | ٦      | Timer5 Holdii | ng Register  | (for 32-bit or | perations on | ly)    |        |       |       |       |       | xxxx          |

| TMR5        | 0118        |        |        |        |        |        |        |               | Timer5       | Register       |              |        |        |       |       |       |       | 0000          |

| PR4         | 011A        |        |        |        |        |        |        |               | Period F     | Register 4     |              |        |        |       |       |       |       | FFFF          |

| PR5         | 011C        |        |        |        |        |        |        |               | Period F     | Register 5     |              |        |        |       |       |       |       | FFFF          |

| T4CON       | 011E        | TON    | _      | TSIDL  | _      | _      | _      | _             | _            | _              | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON    | _      | TSIDL  | _      | _      | _      | _             | _            | _              | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 |  |

|-------------------------------------------------------------|--|

| NOTES:                                                      |  |

|                                                             |  |

#### 8.3 Clock Switching Operation

Applications are free to switch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have a safeguard lock built into the switch process.

Note:

Primary Oscillator mode has three different submodes (MS, HS and EC), which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch among the different primary submodes without reprogramming the device.

#### 8.3.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 23.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 8.3.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires this basic sequence:

- If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSCx control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- Set the OSWEN bit (OSCCON<0>) to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSCx status bits with the new value of the NOSCx control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK and CF (OSCCON<5,3>) status bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bit values are transferred to the COSCx status bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to "Oscillator (Part VI)" (DS70644) in the "dsPIC33/PIC24 Family Reference Manual" for details.

#### 8.4 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a Warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

| dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 |  |

|-------------------------------------------------------------|--|

| NOTES:                                                      |  |

#### REGISTER 10-11: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| _      | _   | _   |       |       | RP1R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| _     | _   | _   |       |       | RP0R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-8 RP1R<4:0>: Peripheral Output Function is Assigned to RP1 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 RP0R<4:0>: Peripheral Output Function is Assigned to RP0 Output Pin bits

(see Table 10-2 for peripheral function numbers)

#### REGISTER 10-12: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|--------------------------|-------|-------|

| _      | _   | _   |       |       | RP3R<4:0> <sup>(1)</sup> |       |       |

| bit 15 |     |     |       |       |                          |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|--------------------------|-------|-------|

| _     | _   | _   |       |       | RP2R<4:0> <sup>(1)</sup> |       |       |

| bit 7 |     |     |       |       |                          |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits<sup>(1)</sup>

(see Table 10-2 for peripheral function numbers)

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 RP2R<4:0>: Peripheral Output Function is Assigned to RP2 Output Pin bits<sup>(1)</sup>

(see Table 10-2 for peripheral function numbers)

Note 1: These bits are not available in dsPIC33FJXX(GP/MC)101 devices.

Note:

#### 12.0 TIMER2/3 AND TIMER4/5

Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Timer2/3 and Timer4/5 have three 2-bit timers that can also be configured as two independent 16-bit timers with selectable operating modes.

**Note 1:** Timer4 and Timer5 are available in dsPIC33FJ32(GP/MC10X) devices only.

As a 32-bit timer, Timer2/3 and Timer4/5 permit operation in three modes:

- Two independent 16-bit timers (e.g., Timer2 and Timer3 or Timer4 and Timer5) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer (Timer2/3 and Timer4/5)

- Single 32-bit synchronous counter (Timer2/3 and Timer4/5)

Timer2/3 and Timer4/5 also support:

- Timer gate operation

- Selectable prescaler settings

- Timer operation during Idle and Sleep modes

- Interrupt on a 32-bit Period register match

- Time base for input capture and output compare modules (Timer2 and Timer3 only)

- ADC1 event trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers (see Register 12-1 through Register 12-4).

For 32-bit timer/counter operation, Timer2/4 is the least significant word (lsw) and Timer3/5 is the most significant word (msw) of the 32-bit timers.

For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are used for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

#### 12.1 32-Bit Operation

To configure Timer2/3 and Timer4/5 for 32-bit operation:

- 1. Set the T32 control bit.

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3/PR5 contains the msw of the value, while PR2/PR4 contains the least significant word (lsw).

- If interrupts are required, set the Timer3 (or Timer5) Interrupt Enable bit, T3IE (or T5IE). Use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. While Timer2/Timer4 controls the timer, the interrupt appears as a Timer3/Timer5 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2 or TMR5:TMR4, which always contains the msw of the count, while TMR2 or TMR4 contains the lsw.

#### 12.2 16-Bit Operation

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the Timerx Interrupt Enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

| sPIC33FJ16(GP/I | WC)101/102 | 2 AND OSPIC | 33FJ32(GP/IVIC | 5)101/10 <i>2/</i> 104 |

|-----------------|------------|-------------|----------------|------------------------|

| OTES:           |            |             |                |                        |

|                 |            |             |                |                        |

|                 |            |             |                |                        |

|                 |            |             |                |                        |

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 U-0 |  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|---------|--|--------|--------|--------|-------|--------------------|

| _      |         |  | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |         |  |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 R/W-0                 |  | R/W-0                | R/W-0                | R/W-0                | R/W-0                                                      | R/W-0 |  |  |  |

|---------------------|-----------------------------|--|----------------------|----------------------|----------------------|------------------------------------------------------------|-------|--|--|--|

| SSEN <sup>(2)</sup> | EN <sup>(2)</sup> CKP MSTEN |  | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | E0 <sup>(3)</sup> PPRE1 <sup>(3)</sup> PPRE0 <sup>(3</sup> |       |  |  |  |

| bit 7               |                             |  |                      |                      |                      |                                                            | bit 0 |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 DISSCK: Disable SCKx pin bit (SPI Master modes only)

1 = Internal SPI clock is disabled, pin functions as I/O

0 = Internal SPI clock is enabled

bit 11 DISSDO: Disable SDOx pin bit

1 = SDOx pin is not used by the module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

Slave mode

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (see bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6)

bit 7 SSEN: SPIx Slave Select Enable bit (Slave mode)(2)

$1 = \overline{SSx}$  pin is used for Slave mode

$0 = \overline{SSx}$  pin is not used by the module, pin is controlled by port function

bit 6 **CKP:** Clock Polarity Select bit

1 = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

**Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

3: Do not set both primary and secondary prescalers to a value of 1:1.

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

```

bit 4-2

SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup>

111 = Secondary prescale 1:1

110 = Secondary prescale 2:1

.

000 = Secondary prescale 8:1

bit 1-0

PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup>

11 = Primary prescale 1:1

10 = Primary prescale 4:1

01 = Primary prescale 4:1

01 = Primary prescale 16:1

00 = Primary prescale 64:1

Note 1: The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes

```

- (FRMEN = 1).2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to a value of 1:1.

#### 19.5 ADC Control Registers

#### REGISTER 19-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|--------|-----|-----|-----|-------|-------|

| ADON   | _   | ADSIDL | _   | _   | _   | FORM1 | FORM0 |

| bit 15 |     | bit 8  |     |     |     |       |       |

| R/W-0 | R/W-0 R/W-0 U-0       |  | R/W-0  | R/W-0 | R/W-0, HC, HS | R/C-0, HC, HS |       |

|-------|-----------------------|--|--------|-------|---------------|---------------|-------|

| SSRC2 | RC2 SSRC1 SSRC0 — SIM |  | SIMSAM | ASAM  | SAMP          | DONE          |       |

| bit 7 |                       |  |        |       |               |               | bit 0 |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit | HC = Hardware Clearable bit |

|-------------------|-------------------|----------------------------|-----------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re  | ead as '0'                  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown          |

bit 15 ADON: ADC1 Operating Mode bit

1 = ADC1 module is operating

0 = ADC1 is off

bit 14 Unimplemented: Read as '0'

bit 13 ADSIDL: ADC1 Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-10 Unimplemented: Read as '0'

bit 9-8 FORM<1:0>: Data Output Format bits

11 = Signed fractional (Dout = sddd dddd dd00 0000, where s = .Not.d<9>)

10 = Fractional (Dout = dddd dddd dd00 0000)

01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NoT.d<9>)

00 = Integer (Dout = 0000 00dd dddd dddd)

bit 7-5 SSRC<2:0>: Sample Clock Source Select bits

111 = Internal counter ends sampling and starts conversion (auto-convert)

110 = CTMU

101 = Reserved

100 = Reserved

011 = Motor control PWM interval ends sampling and starts conversion (1)

010 = GP Timer3 compare ends sampling and starts conversion

001 = Active transition on INTO pin ends sampling and starts conversion

000 = Clearing SAMP bit ends sampling and starts conversion

bit 4 **Unimplemented:** Read as '0'

bit 3 SIMSAM: Simultaneous Sample Select bit (applicable only when CHPS<1:0> = 01 or 1x)

1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS<1:0> = 1x) or samples CH0 and CH1 simultaneously (when CHPS<1:0> = 01)

0 = Samples multiple channels individually in sequence

bit 2 ASAM: ADC1 Sample Auto-Start bit

1 = Sampling begins immediately after last conversion; SAMP bit is auto-set

0 = Sampling begins when the SAMP bit is set

Note 1: This feature is available in dsPIC33FJ(16/32)MC10X devices only.

#### REGISTER 20-5: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      |     |     |     | _   |     | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 R/W-0     |  | R/W-0  | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----------------|--|--------|---------|--------|--------|--------|

| _     | - CFSEL2 CFSEL1 |  | CFSEL0 | CFLTREN | CFDIV2 | CFDIV1 | CFDIV0 |

| bit 7 |                 |  |        |         |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 Unimplemented: Read as '0'

bit 6-4 CFSEL<2:0>: Comparator Filter Input Clock Select bits

111 = Reserved

110 = Reserved

101 = Timer3

100 = Timer2

011 = Reserved

010 = PWM Special Event Trigger

001 = Fosc

000 = FCY

bit 3 CFLTREN: Comparator Filter Enable bit

1 = Digital filter is enabled

0 = Digital filter is disabled

bit 2-0 CFDIV<2:0>: Comparator Filter Clock Divide Select bits

111 = Clock Divide 1:128

110 = Clock Divide 1:64

101 = Clock Divide 1:32

100 = Clock Divide 1:16

011 = Clock Divide 1:8

010 = Clock Divide 1:4

001 = Clock Divide 1:2

000 = Clock Divide 1:1

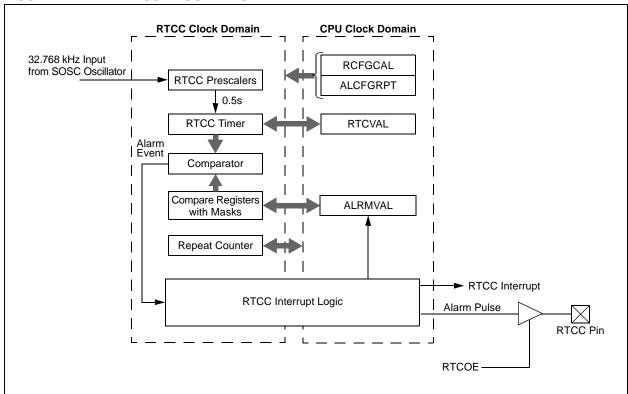

# 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Real-Time Clock and Calendar (RTCC)" (DS70310) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter discusses the Real-Time Clock and Calendar (RTCC) module, available on dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices, and its operation.

Some of the key features of the RTCC module are:

- · Time: hours, minutes and seconds

- · 24-hour format (military time)

- Calendar: weekday, date, month and year

- · Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- · BCD format for compact firmware

- Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for extended periods of time with minimum to no intervention from the CPU. The RTCC module is optimized for low-power usage to provide extended battery lifetime while keeping track of time.

The RTCC module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

The hours are available in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

FIGURE 21-1: RTCC BLOCK DIAGRAM

#### REGISTER 21-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

| R/W-0  | R/W-0 R/W-0       |  | R/W-0  | R/W-0  | R/W-0  | R/W-0             | R/W-0 |  |  |

|--------|-------------------|--|--------|--------|--------|-------------------|-------|--|--|

| ALRMEN | RMEN CHIME AMASK3 |  | AMASK2 | AMASK1 | AMASK0 | ALRMPTR1 ALRMPTR0 |       |  |  |

| bit 15 |                   |  |        |        |        |                   | bit 8 |  |  |

| R/W-0 | R/W-0 R/W-0       |  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------------------|--|-------|-------|-------|-------|-------|

| ARPT7 | ARPT7 ARPT6 ARPT5 |  | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 |

| bit 7 |                   |  |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 ALRMEN: Alarm Enable bit

1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 0x00 and CHIME = 0)

0 = Alarm is disabled

bit 14 CHIME: Chime Enable bit

1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 0x00 to 0xFF

0 = Chime is disabled; ARPT<7:0> bits stop once they reach 0x00

bit 13-10 AMASK<3:0>: Alarm Mask Configuration bits

0000 = Every half second

0001 = Every second

0010 = Every 10 seconds

0011 = Every minute

0100 = Every 10 minutes

0101 = Every hour

0110 = Once a day

0111 = Once a week

1000 = Once a month

1001 = Once a year (except when configured for February 29th, once every 4 years)

101x = Reserved - do not use

11xx = Reserved - do not use

bit 9-8 **ALRMPTR<1:0>:** Alarm Value Register Window Pointer bits

Points to the corresponding Alarm Value registers when reading ALRMVALH and ALRMVALL registers; the ALRMPTR<1:0> value decrements on every read or write of ALRMVALH until it reaches '00'.

ALRMVAL<15:8>:

00 = ALRMMIN

01 = ALRMWD

10 = ALRMMNTH

11 = Unimplemented

ALRMVAL<7:0>:

00 = ALRMSEC

01 = ALRMHR

10 = ALRMDAY

11 = Unimplemented

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits

11111111 = Alarm will repeat 255 more times

•

•

00000000 = Alarm will not repeat

The counter decrements on any alarm event. The counter is prevented from rolling over from 0x00 to 0xFF unless CHIME = 1.

The Configuration Shadow register map is shown in Table 23-1.

#### TABLE 23-1: CONFIGURATION SHADOW REGISTER MAP

| File Name | Addr.  | Bit 7                   | Bit 6                  | Bit 5                   | Bit 4                   | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|-----------|--------|-------------------------|------------------------|-------------------------|-------------------------|----------|----------|----------|----------|

| FGS       | F80004 | _                       | _                      | _                       | _                       | _        | _        | GCP      | GWRP     |

| FOSCSEL   | F80006 | IESO                    | PWMLOCK <sup>(1)</sup> | _                       | WDTWIN1                 | WDTWIN0  | FNOSC2   | FNOSC1   | FNOSC0   |

| FOSC      | F80008 | FCKSM1                  | FCKSM0                 | IOL1WAY                 | _                       | _        | OSCIOFNC | POSCMD1  | POSCMD0  |

| FWDT      | F8000A | FWDTEN                  | WINDIS                 | PLLKEN                  | WDTPRE                  | WDTPOST3 | WDTPOST2 | WDTPOST1 | WDTPOST0 |

| FPOR      | F8000C | PWMPIN <sup>(1)</sup>   | HPOL <sup>(1)</sup>    | LPOL <sup>(1)</sup>     | ALTI2C1                 | _        |          | _        | _        |

| FICD      | F8000E | Reserved <sup>(2)</sup> | _                      | Reserved <sup>(3)</sup> | Reserved <sup>(3)</sup> | _        | _        | ICS1     | ICS0     |

Legend: — = unimplemented, read as '1'.

Note 1: These bits are available in dsPIC33FJ(16/32)MC10X devices only.

2: This bit is reserved for use by development tools.

3: These bits are reserved, program as '0'.

The Configuration Flash Word maps are shown in Table 23-2 and Table 23-3.

# TABLE 23-2: CONFIGURATION FLASH WORDS FOR dsPIC33FJ16(GP/MC)10X DEVICES<sup>(1)</sup>

| File<br>Name | Addr.  | Bits 23-16 | Bit 15                  | Bit 14                  | Bit 13                | Bit 12  | Bit 11                  | Bit 10              | Bit 9  | Bit 8  | Bit 7         | Bit 6  | Bit 5       | Bit 4   | Bit 3               | Bit 2    | Bit 1    | Bit 0    |

|--------------|--------|------------|-------------------------|-------------------------|-----------------------|---------|-------------------------|---------------------|--------|--------|---------------|--------|-------------|---------|---------------------|----------|----------|----------|

| CONFIG2      | 002BFC | _          | IESO                    | PWMLOCK <sup>(2)</sup>  | PWMPIN <sup>(2)</sup> | WDTWIN1 | WDTWIN0                 | FNOSC2              | FNOSC1 | FNOSC0 | FCKSM1        | FCKSM0 | OSCIOFNC(5) | IOL1WAY | LPOL <sup>(2)</sup> | ALTI2C1  | POSCMD1  | POSCMD0  |

| CONFIG1      | 002BFE | _          | Reserved <sup>(3)</sup> | Reserved <sup>(3)</sup> | GCP                   | GWRP    | Reserved <sup>(4)</sup> | HPOL <sup>(2)</sup> | ICS1   | ICS0   | <b>FWDTEN</b> | WINDIS | PLLKEN      | WDTPRE  | WDTPOST3            | WDTPOST2 | WDTPOST1 | WDTPOST0 |

dsPlC33FJ16(GP/MC)101/102 AND dsPlC33FJ32(GP/MC)101/102/104

**Legend:** — = unimplemented, read as '1'.

Note 1: During a Power-on Reset (POR), the contents of these Flash locations are transferred to the Configuration Shadow registers.

2: These bits are reserved in dsPIC33FJ16GP10X devices and read as '1'.

3: These bits are reserved, program as '0'.

4: This bit is reserved for use by development tools and must be programmed as '1'.

5: This bit is programmed to '0' during final tests in the factory.

## TABLE 23-3: CONFIGURATION FLASH WORDS FOR dsPIC33FJ32(GP/MC)10X DEVICES<sup>(1)</sup>

| File<br>Name | Addr.  | Bits 23-16 | Bit 15                  | Bit 14                  | Bit 13                | Bit 12  | Bit 11                  | Bit 10              | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5       | Bit 4   | Bit 3               | Bit 2    | Bit 1    | Bit 0    |

|--------------|--------|------------|-------------------------|-------------------------|-----------------------|---------|-------------------------|---------------------|--------|--------|--------|--------|-------------|---------|---------------------|----------|----------|----------|

| CONFIG2      | 0057FC | -          | IESO                    | PWMLOCK <sup>(2)</sup>  | PWMPIN <sup>(2)</sup> | WDTWIN1 | WDTWIN0                 | FNOSC2              | FNOSC1 | FNOSC0 | FCKSM1 | FCKSM0 | OSCIOFNC(5) | IOL1WAY | LPOL <sup>(2)</sup> | ALTI2C1  | POSCMD1  | POSCMD0  |

| CONFIG1      | 0057FE | -          | Reserved <sup>(3)</sup> | Reserved <sup>(3)</sup> | GCP                   | GWRP    | Reserved <sup>(4)</sup> | HPOL <sup>(2)</sup> | ICS1   | ICS0   | FWDTEN | WINDIS | PLLKEN      | WDTPRE  | WDTPOST3            | WDTPOST2 | WDTPOST1 | WDTPOST0 |

**Legend:** — = unimplemented, read as '1'.

Note 1: During a Power-on Reset (POR), the contents of these Flash locations are transferred to the Configuration Shadow registers.

2: These bits are reserved in dsPIC33FJ32GP10X devices and read as '1'.

3: These bits are reserved, program as '0'.

4: This bit is reserved for use by development tools and must be programmed as '1'.

5: This bit is programmed to '0' during final tests in the factory.

TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                                 |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Wm*Wm | Multiplicand and Multiplier Working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                               |  |  |

| Wm*Wn | Multiplicand and Multiplier Working register pair for DSP instructions ∈ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                  |  |  |

| Wn    | One of 16 Working registers ∈ {W0W15}                                                                                                                                                                                                                       |  |  |

| Wnd   | One of 16 destination Working registers ∈ {W0W15}                                                                                                                                                                                                           |  |  |

| Wns   | One of 16 source Working registers ∈ {W0W15}                                                                                                                                                                                                                |  |  |

| WREG  | W0 (Working register used in file register instructions)                                                                                                                                                                                                    |  |  |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                |  |  |

| Wso   | Source W register ∈ { Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                |  |  |

| Wx    | X data space prefetch address register for DSP instructions ∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2, [W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2, [W9 + W12], none}                |  |  |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                    |  |  |

| Wy    | Y data space prefetch address register for DSP instructions ∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2, [W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2, [W11 + W12], none} |  |  |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                    |  |  |

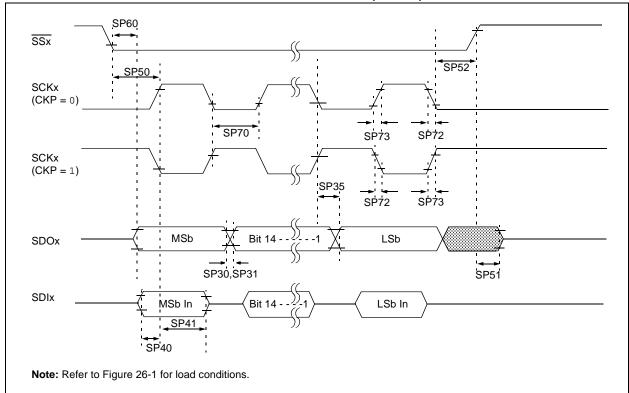

FIGURE 26-23: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

| Resets                                          | 87      | I2Cx Bus Start/Stop Bits (Master Mode)                 | 328  |

|-------------------------------------------------|---------|--------------------------------------------------------|------|

| BOR (Brown-out Reset)                           | 87      | I2Cx Bus Start/Stop Bits (Slave Mode)                  | 330  |

| BOR and Power-up Timer (PWRT)                   | 92      | Input Capture x (ICx)                                  | 301  |

| CM (Configuration Mismatch Reset)               | 87      | Motor Control PWMx                                     | 303  |

| Configuration Mismatch (CM)                     | 93      | Motor Control PWMx Fault                               | 303  |

| External (EXTR)                                 |         | OCx/PWMx                                               |      |

| Illegal Condition                               | 93      | Output Compare x (OCx)                                 | 302  |

| Illegal Opcode                                  | 93      | Output Compare x Operation                             | 178  |

| Security93,                                     |         | Reset, Watchdog Timer, Oscillator Start-up Timer       |      |

| Uninitialized W Register93,                     | 94      | and Power-up Timer                                     | 298  |

| IOPUWR (Illegal Condition Reset)                | 87      | SPIx Master Mode (Full-Duplex, CKE = $0$ , CKP = $x$ , |      |

| Illegal Opcode                                  |         | SMP = 1) for dsPIC33FJ16(GP/MC)10X                     | 307  |

| Security                                        | 87      | SPIx Master Mode (Full-Duplex, CKE = $0$ , CKP = $x$ , |      |

| Uninitialized W Register                        | 87      | SMP = 1) for dsPIC33FJ32(GP/MC)10X                     | 319  |

| MCLR (Master Clear Pin)                         |         | SPIx Master Mode (Full-Duplex, CKE = 1, CKP = $x$ ,    |      |

| Oscillator Delays                               | 90      | SMP = 1) for dsPIC33FJ16(GP/MC)10X                     | 306  |

| POR (Power-on Reset)                            | 87      | SPIx Master Mode (Full-Duplex, CKE = 1, CKP = $x$ ,    |      |

| Power-on Reset (POR)                            | 92      | SMP = 1) for dsPIC33FJ32(GP/MC)10X                     | 318  |

| Software RESET Instruction (SWR)                | 93      | SPIx Master Transmit Mode (Half-Duplex, CKE = 0)       |      |

| SWR (RESET Instruction)                         | 87      | for dsPIC33FJ16(GP/MC)10X                              | 304  |

| System                                          |         | SPIx Master Transmit Mode (Half-Duplex, CKE = 0)       |      |

| Cold Reset                                      | 90      | for dsPIC33FJ32(GP/MC)10X                              | 316  |

| Warm Reset                                      | 90      | SPIx Master Transmit Mode (Half-Duplex, CKE = 1)       |      |

| Trap Conflict                                   | 93      | for dsPIC33FJ16(GP/MC)10X                              | 305  |

| TRAPR (Trap Conflict Reset)                     | 87      | SPIx Master Transmit Mode (Half-Duplex, CKE = 1)       |      |

| Watchdog Timer Time-out (WDTO)                  | 93      | for dsPIC33FJ32(GP/MC)10X                              | 317  |

| WDTO (Watchdog Timer Reset)                     | 87      | SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 0,        |      |

| Revision History 3                              |         | SMP = 0) for $dsPIC33FJ16(GP/MC)10X$                   | 314  |

| RTCC                                            |         | SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 0,        |      |

| Control Registers2                              | 245     | SMP = 0) for $dsPIC33FJ32(GP/MC)10X$                   | 326  |

| Module Registers2                               | 244     | SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 1,        |      |

| Register Mapping2                               |         | SMP = 0) for $dsPIC33FJ16(GP/MC)10X$                   | 312  |

| •                                               |         | SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 1,        |      |

| S                                               |         | SMP = 0) for $dsPIC33FJ32(GP/MC)10X$                   | 324  |

| Serial Peripheral Interface (SPI)1              | 97      | SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 0,        |      |

| Control Registers1                              | 99      | SMP = 0) for $dsPIC33FJ16(GP/MC)10X$                   | 308  |

| Helpful Tips1                                   | 98      | SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 0,        |      |

| Resources1                                      | 98      | SMP = 0) for $dsPIC33FJ32(GP/MC)10X$                   | 320  |

| Software Stack Pointer, Frame Pointer           |         | SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 1,        |      |

| CALL Stack Frame                                | 73      | SMP = 0) for $dsPIC33FJ16(GP/MC)10X$                   | 310  |

| Special Features2                               | 261     | SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 1,        |      |

| Code Protection2                                | 261     | SMP = 0) for $dsPIC33FJ32(GP/MC)10X$                   | 322  |

| Flexible Configuration2                         | 261     | System Reset                                           | . 91 |

| In-Circuit Emulation2                           | 261     | Timer1/2/3 External Clock                              | 299  |

| In-Circuit Serial Programming (ICSP)2           | 261 Tin | ning Requirements                                      |      |

| Watchdog Timer (WDT)2                           | 261     | 10-Bit ADC Conversion                                  | 335  |

| т                                               |         | Capacitive Loading on Output Pins                      | 294  |

| Т                                               |         | CLKO and I/O                                           | 297  |

| Timer1 1                                        | 65      | External Clock                                         | 295  |

| Control Register1                               |         | I2Cx Bus Data (Master Mode)                            | 329  |

| Timer2/3 and Timer4/51                          |         | I2Cx Bus Data (Slave Mode)                             |      |

| 16-Bit Operation1                               | 67      | Input Capture x (ICx)                                  |      |

| 32-Bit Operation1                               | 67      | Motor Control PWMx                                     |      |

| Control Registers1                              | 70      | Output Compare x (OCx)                                 |      |

| Timing Diagrams                                 |         | Reset, Watchdog Timer, Oscillator Start-up Timer,      |      |

| ADC Conversion Characteristics (CHPS<1:0> = 01, |         | Power-up Timer and Brown-out Reset                     | 298  |

| SIMSAM = 0, $ASAM = 0$ ,                        |         | Simple OCx/PWMx Mode                                   | 302  |

| SSRC<2:0> = 000)                                | 334     | SPIx Master Mode (Full-Duplex, CKE = 0, CKP = $x$ ,    |      |

| ADC Conversion Characteristics (CHPS<1:0> = 01, |         | SMP = 1) for dsPIC33FJ16(GP/MC)10X                     | 307  |

| SIMSAM = 0, $ASAM = 1$ , $SSRC < 2:0 > = 111$ , |         | SPIx Master Mode (Full-Duplex, CKE = 0, CKP = x,       |      |

| SAMC<4:0> = 00001)3                             | 334     | SMP = 1) for dsPIC33FJ32(GP/MC)10X                     | 319  |

| Brown-out Reset Situations                      |         | SPIx Master Mode (Full-Duplex, CKE = 1, CKP = x,       | -    |

| CLKO and I/O2                                   | 297     | SMP = 1) for dsPIC33FJ16(GP/MC)10X                     | 306  |

| External Clock2                                 | 295     | SPIx Master Mode (Full-Duplex, CKE = 1, CKP = x,       |      |

| I2Cx Bus Data (Master Mode)3                    |         | SMP = 1) for dsPIC33FJ32(GP/MC)10X                     | 318  |

| I2Cx Bus Data (Slave Mode)                      |         | ,                                                      | -    |