Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

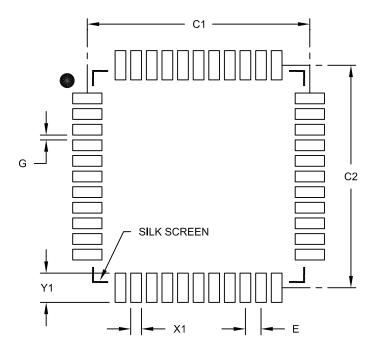

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc102t-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:                                                         | 1                 |                            |                                |                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------|-------------------|----------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                           | Pin<br>Type       | Buffer<br>Type             | PPS                            | Description                                                                                                                                                                                                                                                        |

| AN0-AN12,<br>AN15 <sup>(5)</sup>                                   | I                 | Analog                     | No                             | Analog input channels.                                                                                                                                                                                                                                             |

| CLKI<br>CLKO                                                       | I<br>O            | ST/CMOS<br>—               | No<br>No                       | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always<br>associated with OSC2 pin function. |

| OSC1<br>OSC2                                                       | I<br>I/O          | ST/CMOS<br>—               | No<br>No                       | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                        |

| SOSCI<br>SOSCO                                                     | <br>0             | ST/CMOS                    | No<br>No                       | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.<br>32.768 kHz low-power oscillator crystal output.                                                                                                                                                  |

| CN0-CN30 <sup>(5)</sup>                                            | I                 | ST                         | No                             | Change Notification inputs. Can be software programmable for internal weak pull-ups on all inputs.                                                                                                                                                                 |

| IC1-IC3                                                            | I                 | ST                         | Yes                            | Capture Inputs 1/2/3.                                                                                                                                                                                                                                              |

| OCFA<br>OC1-OC2                                                    | <br>0             | ST<br>—                    | Yes<br>Yes                     | Compare Fault A input (for Compare Channels 1 and 2).<br>Compare Outputs 1/2.                                                                                                                                                                                      |

| INT0<br>INT1<br>INT2<br>RA0-RA4,                                   | <br> <br> <br> /O | ST<br>ST<br>ST<br>ST       | No<br>Yes<br>Yes<br>No         | External Interrupt 0.<br>External Interrupt 1.<br>External Interrupt 2.<br>PORTA is a bidirectional I/O port.                                                                                                                                                      |

| RA7-RA10 <sup>(5)</sup>                                            |                   |                            |                                |                                                                                                                                                                                                                                                                    |

| RB0-RB15 <sup>(5)</sup>                                            | I/O               | ST                         | No                             | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RC0-RC9 <sup>(5)</sup>                                             | I/O               | ST                         | No                             | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| T1CK<br>T2CK<br>T3CK<br>T4CK <sup>(6)</sup><br>T5CK <sup>(6)</sup> |                   | ST<br>ST<br>ST<br>ST<br>ST | No<br>Yes<br>Yes<br>Yes<br>Yes | Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                       |

| U1CTS<br>U1RTS<br>U1RX<br>U1TX                                     | <br>0<br> <br>0   | ST<br>—<br>ST<br>—         | Yes<br>Yes<br>Yes<br>Yes       | UART1 Clear-to-Send.<br>UART1 Ready-to-Send.<br>UART1 receive.<br>UART1 transmit.                                                                                                                                                                                  |

| SCK1<br>SDI1<br>SDO1                                               | I/O<br>I<br>O     | ST<br>ST<br>—              | Yes<br>Yes<br>Yes              | Synchronous serial clock input/output for SPI1.<br>SPI1 data in.<br>SPI1 data out.                                                                                                                                                                                 |

| -                                                                  |                   |                            |                                | input or output Analog = Analog input $P = Power$                                                                                                                                                                                                                  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

PPS = Peripheral Pin Select

O = Output

I = Input

**Note 1:** An external pull-down resistor is required for the FLTA1 pin in dsPIC33FJXXMC101 (20-pin) devices.

2: The FLTA1 pin and the PWM1Lx/PWM1Hx pins are available in dsPIC(16/32)MC10X devices only.

**3:** The FLTB1 pin is available in dsPIC(16/32)MC102/104 devices only.

4: The PWM Fault pins are enabled during any Reset event. Refer to **Section 15.2** "**PWM Faults**" for more information on the PWM Faults.

5: Not all pins are available on all devices. Refer to the specific device in the "**Pin Diagrams**" section for availability.

6: These pins are available in dsPIC33FJ32(GP/MC)104 (44-pin) devices only.

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < FIN < 8 MHz (for MSPLL mode) or 3 MHz < FIN < 8 MHz (for ECPLL mode) to comply with device PLL start-up conditions. HSPLL mode is not supported. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The fixed PLL settings of 4x after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can enable the PLL and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

#### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in the register that correspond to the Analog-to-Digital pins that are initialized by MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain Analog-to-Digital pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all Analog-to-Digital pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

#### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternately, connect a 1k to 10k resistor between Vss and unused pins.

### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXGP101 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0         | All<br>Resets |

|-------------|-------------|--------|---------|---------|---------|---------|--------|-------|-------|---------|---------|---------|--------|--------|--------|--------|---------------|---------------|

| CNEN1       | 0060        | —      | —       | _       | CN12IE  | CN11IE  | _      | —     | _     | —       | —       | CN5IE   | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE         | 0000          |

| CNEN2       | 0062        | _      | CN30IE  | CN29IE  | _       |         |        | _     | _     | CN23IE  | CN22IE  | CN21IE  | _      | _      | _      | _      | _             | 0000          |

| CNPU1       | 0068        | _      | _       | _       | CN12PUE | CN11PUE |        | _     | _     | _       | _       | CN5PUE  | CN4PUE | CN3PUE | CN2PUE | CN1PUE | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | _      | CN30PUE | CN29PUE | —       | _       | _      |       | -     | CN23PUE | CN22PUE | CN21PUE |        | _      | -      |        | -             | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXMC101 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------------|--------|---------|---------|---------|---------|--------|-------|-------|---------|---------|---------|--------|--------|--------|--------|--------|---------------|

| CNEN1       | 0060        | —      | CN14IE  | CN13IE  | CN12IE  | CN11IE  | _      | _     | _     | _       | _       | CN5IE   | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE  | 0000          |

| CNEN2       | 0062        | _      | CN30IE  | CN29IE  | _       | _       | _      | _     | _     | CN23IE  | CN22IE  | CN21IE  |        |        | _      | _      | _      | 0000          |

| CNPU1       | 0068        | _      | CN14PUE | CN13PUE | CN12PUE | CN11PUE | _      | _     | _     | _       | _       | CN5PUE  | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE | 0000          |

| CNPU2       | 006A        | _      | CN30PUE | CN29PUE | _       | _       |        |       | _     | CN23PUE | CN22PUE | CN21PUE |        | _      | _      | _      |        | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXX(GP/MC)102 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3         | Bit 2  | Bit 1  | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|--------|-------|---------|---------|---------|---------|--------|---------------|--------|--------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | _      | _     | —       | CN7IE   | CN6IE   | CN5IE   | CN4IE  | CN3IE         | CN2IE  | CN1IE  | CN0IE         | 0000          |

| CNEN2       | 0062        | _       | CN30IE  | CN29IE  | _       | CN27IE  |        | _     | CN24IE  | CN23IE  | CN22IE  | CN21IE  | _      | _             | _      | _      | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE |        | _     | _       | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE | <b>CN3PUE</b> | CN2PUE | CN1PUE | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE |         | CN27PUE | _      |       | CN24PUE | CN23PUE | CN22PUE | CN21PUE |        |               |        |        | CN16PUE       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-5: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ32(GP/MC)104 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN13IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE   | CN8IE   | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | CN30IE  | CN29IE  | CN28IE  | CN27IE  | CN26IE  | CN25IE  | CN24IE  | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN13PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE  | CN8PUE  | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | —       | CN30PUE | CN29PUE | CN28PUE | CN27PUE | CN26PUE | CN25PUE | CN24PUE | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-40: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing      |

|-------|-----------------------------------------------|

|       | mode specified in the instruction can differ  |

|       | for the source and destination EA. How-       |

|       | ever, the 4-bit Wb (Register Offset) field is |

|       | shared by both source and destination         |

|       | (but typically only used by one).             |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register   | Indirect  | with    | Register    | Offset |

|-------|------------|-----------|---------|-------------|--------|

|       | Addressir  | ng mode i | s ava   | ilable only | for W9 |

|       | (in X spac | ce) and W | /11 (in | Y space).   |        |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.3.5 OTHER INSTRUCTIONS

In addition to the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

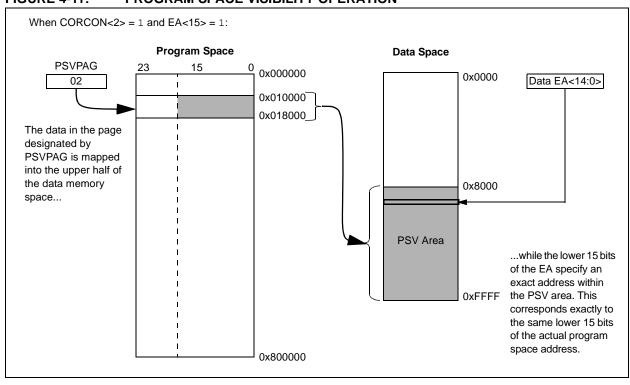

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL and TBLRDH).

Program space access through the data space occurs if the MSb of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | Table Reads/Writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

#### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

| D / M A       | D 444 A                                                                                                                            | D.4.4. 0                       | DAMA            | DALLA             | DALLA           | DAMA            | D 44/ 6 |  |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|--|--|

| R/W-0         | R/W-0                                                                                                                              | R/W-0                          | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |  |  |

| NSTDIS        | OVAERR                                                                                                                             | OVBERR                         | COVAERR         | COVBERR           | OVATE           | OVBTE           | COVTE   |  |  |  |  |  |  |

| bit 15        |                                                                                                                                    |                                |                 |                   |                 |                 | bi      |  |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                              | U-0                            | R/W-0           | R/W-0             | R/W-0           | R/W-0           | U-0     |  |  |  |  |  |  |

| SFTACERR      |                                                                                                                                    | <u> </u>                       | MATHERR         | ADDRERR           | STKERR          | OSCFAIL         |         |  |  |  |  |  |  |

| bit 7         | BIVOLINI                                                                                                                           |                                |                 | ABBRERR           | OTTLETT         | 00017112        | bi      |  |  |  |  |  |  |

|               |                                                                                                                                    |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

| Legend:       |                                                                                                                                    |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                              | W = Writable                   | bit             | U = Unimplem      | ented bit, read | 1 as '0'        |         |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                | '1' = Bit is set               |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |  |  |

| 6:4 <i>7</i>  |                                                                                                                                    | www.unt.Nie.otie.e.F           | Niaahla hit     |                   |                 |                 |         |  |  |  |  |  |  |

| bit 15        |                                                                                                                                    | rrupt Nesting E                |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | <ul> <li>1 = Interrupt nesting is disabled</li> <li>0 = Interrupt nesting is enabled</li> </ul>                                    |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 14        | -                                                                                                                                  | cumulator A O                  |                 | lag bit           |                 |                 |         |  |  |  |  |  |  |

|               | 1 = Trap was                                                                                                                       | caused by ove                  | erflow of Accur | nulator A         |                 |                 |         |  |  |  |  |  |  |

|               | 0 = Trap was                                                                                                                       | not caused by                  | overflow of Ad  | ccumulator A      |                 |                 |         |  |  |  |  |  |  |

| bit 13        | <b>OVBERR:</b> Accumulator B Overflow Trap Flag bit<br>1 = Trap was caused by overflow of Accumulator B                            |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                    | caused by ove<br>not caused by |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 12        | -                                                                                                                                  | -                              |                 |                   | lag hit         |                 |         |  |  |  |  |  |  |

| 51(12)        | <b>COVAERR:</b> Accumulator A Catastrophic Overflow Trap Flag bit<br>1 = Trap was caused by catastrophic overflow of Accumulator A |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | •                                                                                                                                  | •                              | •               | overflow of Accu  |                 |                 |         |  |  |  |  |  |  |

| bit 11        | COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit                                                                         |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                    |                                |                 | flow of Accumu    |                 |                 |         |  |  |  |  |  |  |

|               | 0 = Trap was not caused by catastrophic overflow of Accumulator B                                                                  |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 10        | OVATE: Accumulator A Overflow Trap Enable bit                                                                                      |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | 1 = Trap overflow of Accumulator A<br>0 = Trap is disabled                                                                         |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 9         |                                                                                                                                    | umulator B Ove                 | erflow Trap En  | able bit          |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                    | flow of Accum                  |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | 0 = Trap is di                                                                                                                     | sabled                         |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 8         | COVTE: Cata                                                                                                                        | astrophic Overf                | low Trap Enab   | ole bit           |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                    |                                | erflow of Accur | mulator A or B i  | s enabled       |                 |         |  |  |  |  |  |  |

| hit 7         | 0 = Trap is dis                                                                                                                    | sabled<br>Shift Accumula       | tor Error State | ia hit            |                 |                 |         |  |  |  |  |  |  |

| bit 7         |                                                                                                                                    |                                |                 | llid accumulator  | chift           |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                    |                                |                 | invalid accumul   |                 |                 |         |  |  |  |  |  |  |

| bit 6         |                                                                                                                                    | ithmetic Error :               | -               |                   |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                    | or trap was cau                | -               | -                 |                 |                 |         |  |  |  |  |  |  |

|               |                                                                                                                                    | r trap was not                 | -               | ivide-by-zero     |                 |                 |         |  |  |  |  |  |  |

| bit 5         | Unimplemented: Read as '0'                                                                                                         |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

| bit 4         | <b>MATHERR:</b> Arithmetic Error Status bit<br>1 = Math error trap has occurred                                                    |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

|               | 1 14-41                                                                                                                            |                                |                 |                   |                 |                 |         |  |  |  |  |  |  |

#### INTOONA, INTERDURT CONTROL DECISTER A

#### 8.1 CPU Clocking System

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with 4x PLL

- Primary (MS, HS or EC) Oscillator

- Primary Oscillator with 4x PLL

- Secondary (LP) Oscillator

- Low-Power RC (LPRC) Oscillator

- FRC Oscillator with postscaler

#### 8.1.1 SYSTEM CLOCK SOURCES

#### 8.1.1.1 Fast RC

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The FRC frequency depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3).

#### 8.1.1.2 Primary

The primary oscillator can use one of the following as its clock source:

- MS (Crystal): Crystals and ceramic resonators in the range of 4 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 32 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

#### 8.1.1.3 Secondary

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

#### 8.1.1.4 Low-Power RC

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

#### 8.1.1.5 PLL

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip, 4x Phase Lock Loop (PLL) to provide faster output frequencies for device operation. PLL configuration is described in **Section 8.1.3 "PLL Configuration"**.

#### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 23.1 "Configuration Bits" for further details.) The initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) FOSC is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device, and speeds up to 16 MHz are supported by the dsPIC33FJ16(GP/ MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

#### EQUATION 8-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

#### 8.3 Clock Switching Operation

Applications are free to switch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have a safeguard lock built into the switch process.

| Note: | Primary Oscillator mode has three different |

|-------|---------------------------------------------|

|       | submodes (MS, HS and EC), which are         |

|       | determined by the POSCMD<1:0> Config-       |

|       | uration bits. While an application can      |

|       | switch to and from Primary Oscillator       |

|       | mode in software, it cannot switch among    |

|       | the different primary submodes without      |

|       | reprogramming the device.                   |

#### 8.3.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 23.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 8.3.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit (OSCCON<0>) to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSCx status bits with the new value of the NOSCx control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- 2. If a valid clock switch has been initiated, the LOCK and CF (OSCCON<5,3>) status bits are cleared.

- 3. The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bit values are transferred to the COSCx status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to "Oscillator (Part VI)" (DS70644) in the "dsPIC33/PIC24 Family Reference Manual" for details.

#### 8.4 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a Warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

# 17.3 I<sup>2</sup>C Control Registers

#### REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0      | U-0                                                   | R/W-0                                  | R/W-1, HC         | R/W-0                         | R/W-0                                | R/W-0             | R/W-0            |  |  |  |

|------------|-------------------------------------------------------|----------------------------------------|-------------------|-------------------------------|--------------------------------------|-------------------|------------------|--|--|--|

| I2CEN      | —                                                     | I2CSIDL                                | SCLREL            | IPMIEN                        | A10M                                 | DISSLW            | SMEN             |  |  |  |

| bit 15     |                                                       |                                        |                   |                               | I                                    |                   | bit 8            |  |  |  |

|            |                                                       |                                        |                   |                               |                                      |                   |                  |  |  |  |

| R/W-0      | R/W-0                                                 | R/W-0                                  | R/W-0, HC         | R/W-0, HC                     | R/W-0, HC                            | R/W-0, HC         | R/W-0, HC        |  |  |  |

| GCEN       | STREN                                                 | ACKDT                                  | ACKEN             | RCEN                          | PEN                                  | RSEN              | SEN              |  |  |  |

| bit 7      |                                                       |                                        |                   |                               |                                      |                   | bit (            |  |  |  |

|            |                                                       |                                        |                   |                               |                                      |                   |                  |  |  |  |

| Legend:    |                                                       |                                        | re Clearable bi   |                               |                                      |                   |                  |  |  |  |

| R = Reada  |                                                       | W = Writable                           |                   | -                             | nented bit, read                     |                   |                  |  |  |  |

| -n = Value | at POR                                                | '1' = Bit is set                       |                   | '0' = Bit is cle              | ared                                 | x = Bit is unkno  | own              |  |  |  |

| bit 15     | <b>12CEN:</b> 12Cx                                    | Enable bit                             |                   |                               |                                      |                   |                  |  |  |  |

| DICID      |                                                       |                                        | e and configu     | res the SDAx a                | and SCLx pins a                      | s serial port pin | 2                |  |  |  |

|            |                                                       |                                        |                   |                               | ed by port function                  |                   | 5                |  |  |  |

| bit 14     |                                                       | nted: Read as '                        | -                 |                               |                                      |                   |                  |  |  |  |

| bit 13     | 12CSIDL: 120                                          | Cx Stop in Idle I                      | Node bit          |                               |                                      |                   |                  |  |  |  |

|            |                                                       | nues module op                         |                   | device enters a               | n Idle mode                          |                   |                  |  |  |  |

|            |                                                       | s module opera                         |                   |                               |                                      |                   |                  |  |  |  |

| bit 12     | SCLREL: SC                                            | CLx Release Co                         | ontrol bit (wher  | operating as I                | <sup>2</sup> C slave)                |                   |                  |  |  |  |

|            | 1 = Releases SCLx clock                               |                                        |                   |                               |                                      |                   |                  |  |  |  |

|            |                                                       | CLx clock low (c                       | clock stretch)    |                               |                                      |                   |                  |  |  |  |

|            | $\frac{\text{If STREN} = 1}{\text{Dit is } P(M/(i))}$ |                                        | write (o' to init | tioto otrotob on              | d write (1) to role                  |                   | duara alaara a   |  |  |  |

|            |                                                       |                                        |                   |                               | d write '1' to relevare clears at er |                   |                  |  |  |  |

|            |                                                       | ardware clears                         | -                 |                               |                                      |                   | e daarooo byt    |  |  |  |

|            | If STREN = 0                                          |                                        |                   | 2                             | •                                    |                   |                  |  |  |  |

|            |                                                       |                                        |                   |                               | k). Hardware cle                     |                   | g of every slave |  |  |  |

|            | data byte tra                                         | nsmission. Har                         | dware clears a    | t end of every                | slave address b                      | yte reception.    |                  |  |  |  |

| bit 11     |                                                       | lligent Peripher                       | -                 | -                             |                                      |                   |                  |  |  |  |

|            |                                                       | de is enabled; a<br>de is disabled     | all addresses a   | re Acknowledg                 | jed                                  |                   |                  |  |  |  |

| bit 10     |                                                       | 10-Bit Slave Ac                        | Idress bit        |                               |                                      |                   |                  |  |  |  |

|            |                                                       | ) is a 10-bit slav                     |                   |                               |                                      |                   |                  |  |  |  |

|            |                                                       | ) is a 7-bit slave                     |                   |                               |                                      |                   |                  |  |  |  |

| bit 9      | DISSLW: Dis                                           | sable Slew Rate                        | e Control bit     |                               |                                      |                   |                  |  |  |  |

|            |                                                       | e control is disa<br>e control is enal |                   |                               |                                      |                   |                  |  |  |  |

| bit 8      |                                                       | us Input Levels                        |                   |                               |                                      |                   |                  |  |  |  |

| DILO       |                                                       | I/O pin threshol                       |                   | vith SMBus spe                | ecification                          |                   |                  |  |  |  |

|            |                                                       | SMBus input th                         |                   |                               |                                      |                   |                  |  |  |  |

| bit 7      | GCEN: Gene                                            | eral Call Enable                       | bit (when ope     | erating as I <sup>2</sup> C s | lave)                                |                   |                  |  |  |  |

|            |                                                       | interrupt when                         |                   |                               | ceived in the I2                     | CxRSR (module     | e is enabled fo  |  |  |  |

|            | •                                                     | call address is                        | haldesib          |                               |                                      |                   |                  |  |  |  |

0 = General call address is disabled

| R/W-0      | ) U-0                                                     | U-0                                                                                                                                                                            | R/W-0          | R/W-0                               | R/W-0                     | R/W-0    | R/W-0        |  |

|------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------|---------------------------|----------|--------------|--|

| CSS15      | (4)                                                       | —                                                                                                                                                                              |                |                                     | CSS<12:8> <sup>(4,6</sup> | 5)       |              |  |

| bit 15     |                                                           |                                                                                                                                                                                |                |                                     |                           |          | bit 8        |  |

| R/W-0      | ) R/W-0                                                   | R/W-0                                                                                                                                                                          | R/W-0          | R/W-0                               | R/W-0                     | R/W-0    | R/W-0        |  |

|            |                                                           |                                                                                                                                                                                | CSS<7          | 7:0> <sup>(4,5)</sup>               |                           |          |              |  |

| bit 7      |                                                           |                                                                                                                                                                                |                |                                     |                           |          | bit 0        |  |

| Legend:    |                                                           |                                                                                                                                                                                |                |                                     |                           |          |              |  |

| R = Read   | able bit                                                  | W = Writable b                                                                                                                                                                 | bit            | U = Unimplen                        | nented bit, rea           | d as '0' |              |  |

| -n = Value | at POR                                                    | '1' = Bit is set                                                                                                                                                               |                | 0' = Bit is cleared $x = Bit is un$ |                           |          | nown         |  |

| bit 14-13  | 0 = Skips AN                                              | Nx for input sca<br>‹ for input scan<br><b>ted:</b> Read as '0                                                                                                                 |                |                                     |                           |          |              |  |

| bit 12-0   | <b>CSS&lt;12:0&gt;:</b> /<br>1 = Selects A                | ADC1 Input Sca<br>Nx for input sca                                                                                                                                             | an Selection b | bits <b>(4,5,6)</b>                 |                           |          |              |  |

| Note 1:    | 0 = Skips AN<br>On devices withour<br>inputs selected for |                                                                                                                                                                                |                |                                     |                           |          | on. However, |  |

| 2:         | CSSx = ANx, when                                          |                                                                                                                                                                                |                |                                     |                           | VILLE.   |              |  |

| 3:         |                                                           |                                                                                                                                                                                |                | nned.                               |                           |          |              |  |

| 4:         | •                                                         | CTMU temperature sensor input cannot be scanned.<br>The CSS<15,12:11,8:6> bits are available in the dsPIC33FJ32(GP/MC)104 devices only and are reserved<br>n all other devices |                |                                     |                           |          |              |  |

|            |                                                           |                                                                                                                                                                                |                |                                     |                           |          |              |  |

### REGISTER 19-6: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2,3)</sup>

- they are reserved.

6: The CSS<10:9> bits are available on all devices, excluding the dsPIC33E.116(GP/MC)101/102 devices.

- 6: The CSS<10:9> bits are available on all devices, excluding the dsPIC33FJ16(GP/MC)101/102 devices, where they are reserved.

#### R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 PCFG15<sup>(4,5)</sup> PCFG<12:0>(4,5,7) \_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 PCFG<7:0>(4,5,6) bit 7 bit 0 Leaend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown PCFG15: ADC1 Port Configuration Control bit<sup>(4,5)</sup> bit 15 1 = Port pin is in Digital mode, port read input is enabled, ADC1 input multiplexer is connected to AVss

#### REGISTER 19-7: AD1PCFGL: ADC1 PORT CONFIGURATION REGISTER LOW<sup>(1,2,3)</sup>

| bit 14-13 | Unimplemented: Read as '0'                                                                               |

|-----------|----------------------------------------------------------------------------------------------------------|

| bit 12-0  | PCFG<12:0>: ADC1 Port Configuration Control bits <sup>(4,5,6,7)</sup>                                    |

|           | 1 = Port pin is in Digital mode, port read input is enabled, ADC1 input multiplexer is connected to AVss |

|           | 0 = Port pin is in Analog mode, port read input is disabled. ADC1 samples pin voltage                    |

0 = Port pin is in Analog mode, port read input is disabled. ADC1 samples pin voltage

# **Note 1:** On devices without 14 analog inputs, all PCFGx bits are R/W by user. However, PCFGx bits are ignored on ports without a corresponding input on the device.

- **2:** PCFGx = ANx, where x = 0 through 12 and 15.

- **3:** The PCFGx bits have no effect if the ADC module is disabled by setting the AD1MD bit in the PMD1 register. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

- **4:** Pins shared with analog functions (i.e., ANx) are analog by default and therefore, must be set by the user to enable any digital function on that pin. Reading any port pin with the analog function enabled will return a '0', regardless of the signal input level.

- **5:** The PCFG<15,12:11,8:6> bits are available in the dsPIC33FJ32(GP/MC)104 devices only and are reserved in all other devices.

- 6: The PCFG<5:4> bits are available on all devices, excluding the dsPIC33FJXX(GP/MC)101 devices, where they are reserved.

- 7: The PCFG<10:9> bits are available on all devices, excluding the dsPIC33FJ16(GP/MC)101/102 devices, where they are reserved.

| U-0           | U-0                                                                                                                                                 | U-0                                                                                                 | U-0             | U-0                               | U-0              | U-0             | U-0    |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|-----------------------------------|------------------|-----------------|--------|--|--|--|--|

| _             | -                                                                                                                                                   | _                                                                                                   | _               | _                                 | _                | -               | -      |  |  |  |  |

| bit 15        |                                                                                                                                                     |                                                                                                     |                 |                                   |                  |                 | bit 8  |  |  |  |  |

|               |                                                                                                                                                     |                                                                                                     |                 |                                   |                  |                 |        |  |  |  |  |

| U-0           | R/W-0                                                                                                                                               | R/W-0                                                                                               | R/W-0           | R/W-0                             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| —             | CFSEL2                                                                                                                                              | CFSEL1                                                                                              | CFSEL0          | CFLTREN                           | CFDIV2           | CFDIV1          | CFDIV0 |  |  |  |  |

| bit 7         |                                                                                                                                                     |                                                                                                     |                 |                                   |                  | bit (           |        |  |  |  |  |

| Legend:       |                                                                                                                                                     |                                                                                                     |                 |                                   |                  |                 |        |  |  |  |  |

| R = Readabl   | o hit                                                                                                                                               | W = Writable                                                                                        | hit             | LI – Unimplon                     | nented bit, read | ac 'O'          |        |  |  |  |  |

| -n = Value at |                                                                                                                                                     | '1' = Bit is set                                                                                    |                 | $0^{\circ} = \text{Bit is clear}$ |                  | x = Bit is unki | oown   |  |  |  |  |

|               | FUR                                                                                                                                                 |                                                                                                     |                 |                                   | areu             |                 | IUWII  |  |  |  |  |

| bit 15-7      | Unimplemen                                                                                                                                          | ted: Read as '                                                                                      | 0'              |                                   |                  |                 |        |  |  |  |  |

| bit 6-4       | -                                                                                                                                                   | : Comparator I                                                                                      |                 | ock Select bits                   |                  |                 |        |  |  |  |  |

|               | 111 = Reserved<br>110 = Reserved<br>101 = Timer3<br>100 = Timer2<br>011 = Reserved<br>010 = PWM Special Event Trigger<br>001 = Fosc<br>000 = Fcy    |                                                                                                     |                 |                                   |                  |                 |        |  |  |  |  |

| bit 3         | <b>CFLTREN:</b> C<br>1 = Digital filte<br>0 = Digital filte                                                                                         |                                                                                                     | er Enable bit   |                                   |                  |                 |        |  |  |  |  |

| bit 2-0       | CFDIV<2:0>:<br>111 = Clock I<br>110 = Clock I<br>101 = Clock I<br>100 = Clock I<br>011 = Clock I<br>010 = Clock I<br>001 = Clock I<br>001 = Clock I | Divide 1:128<br>Divide 1:64<br>Divide 1:32<br>Divide 1:16<br>Divide 1:8<br>Divide 1:4<br>Divide 1:2 | ilter Clock Div | ide Select bits                   |                  |                 |        |  |  |  |  |

#### REGISTER 20-5: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

| U-0             | U-0                                                                                                                                | U-0              | U-0 | U-0              | U-0              | U-0                     | U-0   |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|------------------|-------------------------|-------|--|--|

| _               | —                                                                                                                                  | —                | —   | —                |                  | —                       | _     |  |  |

| bit 15          |                                                                                                                                    |                  |     |                  |                  |                         | bit 8 |  |  |

|                 |                                                                                                                                    |                  |     |                  |                  |                         |       |  |  |

| U-0             | U-0                                                                                                                                | U-0              | U-0 | U-0              | U-0              | R/W-0                   | U-0   |  |  |

| —               | —                                                                                                                                  | —                | —   | —                | —                | RTSECSEL <sup>(1)</sup> |       |  |  |

| bit 7           |                                                                                                                                    |                  |     |                  |                  |                         | bit 0 |  |  |

|                 |                                                                                                                                    |                  |     |                  |                  |                         |       |  |  |

| Legend:         |                                                                                                                                    |                  |     |                  |                  |                         |       |  |  |

| R = Readable    | bit                                                                                                                                | W = Writable     | bit | U = Unimpler     | mented bit, read | d as '0'                |       |  |  |

| -n = Value at F | POR                                                                                                                                | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkno        | own   |  |  |

|                 |                                                                                                                                    |                  |     |                  |                  |                         |       |  |  |

| bit 15-2        | Unimplemen                                                                                                                         | ted: Read as '   | 0'  |                  |                  |                         |       |  |  |

| bit 1           | bit 1 RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup>                                                                |                  |     |                  |                  |                         |       |  |  |

|                 | <ul> <li>1 = RTCC seconds clock is selected for the RTCC pin</li> <li>0 = RTCC alarm pulse is selected for the RTCC pin</li> </ul> |                  |     |                  |                  |                         |       |  |  |

|                 |                                                                                                                                    |                  |     |                  |                  |                         |       |  |  |

#### REGISTER 21-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>) bit needs to be set.

Unimplemented: Read as '0'

bit 0

| R/W-0                 | R/W-0                                                                                                                        | R/W-0             | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| ITRIM5                | ITRIM4                                                                                                                       | ITRIM3            | ITRIM2           | ITRIM1            | ITRIM0           | IRNG1           | IRNG0 |  |  |  |  |