Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc102t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7        | Bit 6  | Bit 5     | Bit 4         | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|---------|--------------|--------------|--------|-----------|---------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000        |        |        |        |        |        |        |         | Working Re   | egister 0    |        |           |               |              |              |         |       | xxxx          |

| WREG1    | 0002        |        |        |        |        |        |        |         | Working Re   | egister 1    |        |           |               |              |              |         |       | xxxx          |

| WREG2    | 0004        |        |        |        |        |        |        |         | Working Re   | egister 2    |        |           |               |              |              |         |       | xxxx          |

| WREG3    | 0006        |        |        |        |        |        |        |         | Working Re   | egister 3    |        |           |               |              |              |         |       | xxxx          |

| WREG4    | 0008        |        |        |        |        |        |        |         | Working Re   | egister 4    |        |           |               |              |              |         |       | xxxx          |

| WREG5    | 000A        |        |        |        |        |        |        |         | Working Re   | egister 5    |        |           |               |              |              |         |       | xxxx          |

| WREG6    | 000C        |        |        |        |        |        |        |         | Working Re   | egister 6    |        |           |               |              |              |         |       | xxxx          |

| WREG7    | 000E        |        |        |        |        |        |        |         | Working Re   | egister 7    |        |           |               |              |              |         |       | xxxx          |

| WREG8    | 0010        |        |        |        |        |        |        |         | Working Re   | egister 8    |        |           |               |              |              |         |       | xxxx          |

| WREG9    | 0012        |        |        |        |        |        |        |         | Working Re   | egister 9    |        |           |               |              |              |         |       | xxxx          |

| WREG10   | 0014        |        |        |        |        |        |        |         | Working Re   | gister 10    |        |           |               |              |              |         |       | xxxx          |

| WREG11   | 0016        |        |        |        |        |        |        |         | Working Re   | gister 11    |        |           |               |              |              |         |       | xxxx          |

| WREG12   | 0018        |        |        |        |        |        |        |         | Working Re   | gister 12    |        |           |               |              |              |         |       | xxxx          |

| WREG13   | 001A        |        |        |        |        |        |        |         | Working Re   | gister 13    |        |           |               |              |              |         |       | xxxx          |

| WREG14   | 001C        |        |        |        |        |        |        |         | Working Re   | gister 14    |        |           |               |              |              |         |       | xxxx          |

| WREG15   | 001E        |        |        |        |        |        |        |         | Working Re   | gister 15    |        |           |               |              |              |         |       | 0800          |

| SPLIM    | 0020        |        |        |        |        |        |        | Sta     | ck Pointer L | imit Registe | r      |           |               |              |              |         |       | XXXX          |

| ACCAL    | 0022        |        |        |        |        |        |        | Accum   | ulator A Lov | v Word Reg   | ister  |           |               |              |              |         |       | XXXX          |

| ACCAH    | 0024        |        |        |        |        |        |        | Accum   | ulator A Hig | h Word Reg   | ister  |           |               |              |              |         |       | XXXX          |

| ACCAU    | 0026        |        |        |        |        |        |        | Accumu  | ulator A Upp | er Word Re   | gister |           |               |              |              |         |       | xxxx          |

| ACCBL    | 0028        |        |        |        |        |        |        | Accum   | ulator B Lov | v Word Reg   | ister  |           |               |              |              |         |       | xxxx          |

| ACCBH    | 002A        |        |        |        |        |        |        | Accum   | ulator B Hig | h Word Reg   | ister  |           |               |              |              |         |       | xxxx          |

| ACCBU    | 002C        |        |        |        |        |        |        | Accumu  | ulator B Upp | er Word Re   | gister |           |               |              |              |         |       | xxxx          |

| PCL      | 002E        |        |        |        |        |        |        | Progran | n Counter Lo | w Word Re    | gister |           |               |              |              |         |       | 0000          |

| PCH      | 0030        | —      | —      | —      |        |        |        | —       | —            |              |        | Progra    | m Counter     | High Byte R  | egister      |         |       | 0000          |

| TBLPAG   | 0032        | —      | —      | —      |        |        |        | —       | —            |              |        | Table F   | age Addre     | ss Pointer R | egister      |         |       | 0000          |

| PSVPAG   | 0034        | —      | —      | —      |        |        |        | _       | —            |              | Progra | am Memory | Visibility Pa | age Address  | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036        |        |        |        |        |        |        | Repe    | eat Loop Co  | unter Regist | er     |           |               |              |              |         |       | xxxx          |

| DCOUNT   | 0038        |        |        |        |        |        |        |         | DCOUNT       | <15:0>       |        |           |               |              |              |         |       | xxxx          |

| DOSTARTL | 003A        |        |        |        |        |        |        | DOS     | TARTL<15:    | 1>           |        |           |               |              |              |         | 0     | xxxx          |

| DOSTARTH | 003C        | _      | —      | —      | —      | _      | —      |         | -            | —            | —      |           |               | DOSTAR       | TH<5:0>      |         |       | 00xx          |

| DOENDL   | 003E        |        |        |        |        |        |        | DO      | ENDL<15:1    | >            |        |           |               |              |              |         | 0     | XXXX          |

| DOENDH   | 0040        |        | _      | —      | —      | _      | _      |         | _            | —            | _      |           |               | DOE          | NDH          |         |       | 00xx          |

| SR       | 0042        | OA     | OB     | SA     | SB     | OAB    | SAB    | DA      | DC           | IPL2         | IPL1   | IPL0      | RA            | N            | OV           | Z       | С     | 0000          |

#### . . COLL CODE DECISTED MAD

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

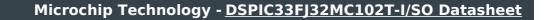

| TABLE 4-  | 17:         | ADC1   | REGIS  | STER M | AP FO  | R dsPIC | 33FJ32(  | GP/MC)1  | 04 DEV  | ICES         |           |                   |        |        |          |          |         |               |

|-----------|-------------|--------|--------|--------|--------|---------|----------|----------|---------|--------------|-----------|-------------------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10   | Bit 9    | Bit 8   | Bit 7        | Bit 6     | Bit 5             | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 0         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF1  | 0302        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 1         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 2         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF3  | 0306        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 3         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 4         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 5         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 6         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 7         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF8  | 0310        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 8         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF9  | 0312        |        |        |        |        |         |          |          | ADC1 Da | ata Buffer   | 9         |                   |        |        |          |          |         | xxxx          |

| ADC1BUFA  | 0314        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer ' | 10        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |        |        |        |        |         |          |          | ADC1 Da | ta Buffer    | 11        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFC  | 0318        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer 1 | 12        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer 1 | 13        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer 1 | 14        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |        |        |        |        |         |          |          | ADC1 Da | ita Buffer 1 | 15        |                   |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON   | —      | ADSIDL | —      | _       |          | FORM1    | FORM0   | SSRC2        | SSRC1     | SSRC0             | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2  | VCFG1  | VCFG0  | —      | _       | CSCNA    | CHPS1    | CHPS0   | BUFS         | —         | SMPI3             | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC   | —      | —      | SAMC4  | SAMC3   | SAMC2    | SAMC1    | SAMC0   | ADCS7        | ADCS6     | ADCS5             | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123 | 0326        | —      | _      | —      | —      | _       | CH123NB1 | CH123NB0 | CH123SB | —            | —         |                   | _      | —      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB  | _      | —      | CH0SB4 | CH0SB3  | CH0SB2   | CH0SB1   | CH0SB0  | CH0NA        | —         |                   | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | PCFG15 | _      | —      |        |         |          |          |         | F            | PCFG<12:0 | )> <sup>(1)</sup> |        |        |          |          |         | 0000          |

| AD1CSSL   | 0330        | CSS15  | _      | _      |        |         |          |          |         |              | CSS12:0>  | (1)               |        |        |          |          |         | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)104 devices only.

### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 2 IDLE: Wake-up from Idle Flag bit

- 1 = Device has been in Idle mode

- 0 = Device has not been in Idle mode

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is set to '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Vector<br>Number         Require           8         9           10         1           12         1           13         1           14         1           15         1           16         1           17         1           18         1           19         20           21         22-23         1           24         25           26         27 | terrupt<br>lest (IRQ)<br>umber<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12 | IVT Address<br>0x000014<br>0x000016<br>0x000018<br>0x00001A<br>0x00001C<br>0x00001E<br>0x000020<br>0x000022<br>0x000024<br>0x000026<br>0x000028 | AIVT Address                                                                                 | Interrupt Source INT0 – External Interrupt 0 IC1 – Input Capture 1 OC1 – Output Compare 1 T1 – Timer1 Reserved IC2 – Input Capture 2 OC2 – Output Compare 2 T2 – Timer2 T3 – Timer3 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9         10         11         12         13         14         15         16         17         18         19         20         21         22-23         24         25         26         27                                                                                                                                                             | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>9<br>10<br>11                                         | 0x000016<br>0x000018<br>0x00001A<br>0x00001C<br>0x00001E<br>0x000020<br>0x000022<br>0x000024<br>0x000026                                        | 0x000116<br>0x000118<br>0x00011A<br>0x00011C<br>0x00011E<br>0x000120<br>0x000122<br>0x000124 | IC1 – Input Capture 1<br>OC1 – Output Compare 1<br>T1 – Timer1<br>Reserved<br>IC2 – Input Capture 2<br>OC2 – Output Compare 2<br>T2 – Timer2                                        |

| 10         11         12         13         14         15         16         17         18         19         20         21         22-23         24         25         26         27                                                                                                                                                                       | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                                                   | 0x000018<br>0x00001A<br>0x00001C<br>0x00001E<br>0x000020<br>0x000022<br>0x000024<br>0x000026                                                    | 0x000118<br>0x00011A<br>0x00011C<br>0x00011E<br>0x000120<br>0x000122<br>0x000124             | OC1 – Output Compare 1<br>T1 – Timer1<br>Reserved<br>IC2 – Input Capture 2<br>OC2 – Output Compare 2<br>T2 – Timer2                                                                 |

| 11         12         13         14         15         16         17         18         19         20         21         22-23         24         25         26         27                                                                                                                                                                                  | 3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                                                        | 0x00001A<br>0x00001C<br>0x00001E<br>0x000020<br>0x000022<br>0x000024<br>0x000026                                                                | 0x00011A<br>0x00011C<br>0x00011E<br>0x000120<br>0x000122<br>0x000124                         | T1 – Timer1<br>Reserved<br>IC2 – Input Capture 2<br>OC2 – Output Compare 2<br>T2 – Timer2                                                                                           |

| 12         13         14         15         16         17         18         19         20         21         22-23         24         25         26         27                                                                                                                                                                                             | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                                                             | 0x00001C<br>0x00001E<br>0x000020<br>0x000022<br>0x000024<br>0x000026                                                                            | 0x00011C<br>0x00011E<br>0x000120<br>0x000122<br>0x000124                                     | Reserved<br>IC2 – Input Capture 2<br>OC2 – Output Compare 2<br>T2 – Timer2                                                                                                          |

| 13         14         15         16         17         18         19         20         21         22-23         24         25         26         27                                                                                                                                                                                                        | 5<br>6<br>7<br>8<br>9<br>10<br>11                                                                  | 0x00001E<br>0x000020<br>0x000022<br>0x000024<br>0x000026                                                                                        | 0x00011E<br>0x000120<br>0x000122<br>0x000124                                                 | IC2 – Input Capture 2<br>OC2 – Output Compare 2<br>T2 – Timer2                                                                                                                      |

| 14         15         16         17         18         19         20         21         22-23         24         25         26         27                                                                                                                                                                                                                   | 6<br>7<br>8<br>9<br>10<br>11                                                                       | 0x000020<br>0x000022<br>0x000024<br>0x000026                                                                                                    | 0x000120<br>0x000122<br>0x000124                                                             | OC2 – Output Compare 2<br>T2 – Timer2                                                                                                                                               |

| 15         16         17         18         19         20         21         22-23         24         25         26         27                                                                                                                                                                                                                              | 7<br>8<br>9<br>10<br>11                                                                            | 0x000022<br>0x000024<br>0x000026                                                                                                                | 0x000122<br>0x000124                                                                         | T2 – Timer2                                                                                                                                                                         |

| 16         17         18         19         20         21         22-23         24         25         26         27                                                                                                                                                                                                                                         | 8<br>9<br>10<br>11                                                                                 | 0x000024<br>0x000026                                                                                                                            | 0x000124                                                                                     |                                                                                                                                                                                     |

| 17       18       19       20       21       22-23       24       25       26       27                                                                                                                                                                                                                                                                      | 9<br>10<br>11                                                                                      | 0x000026                                                                                                                                        |                                                                                              | T3 – Timer3                                                                                                                                                                         |

| 18       19       20       21       22-23       24       25       26       27                                                                                                                                                                                                                                                                               | 10<br>11                                                                                           |                                                                                                                                                 | 0x000106                                                                                     |                                                                                                                                                                                     |

| 19       20       21       22-23       1       24       25       26       27                                                                                                                                                                                                                                                                                | 11                                                                                                 | 0x000028                                                                                                                                        | 0X000120                                                                                     | SPI1E – SPI1 Error                                                                                                                                                                  |

| 20       21       22-23     1       24       25       26       27                                                                                                                                                                                                                                                                                           |                                                                                                    |                                                                                                                                                 | 0x000128                                                                                     | SPI1 – SPI1 Transfer Done                                                                                                                                                           |

| 21       22-23       24       25       26       27                                                                                                                                                                                                                                                                                                          | 12                                                                                                 | 0x00002A                                                                                                                                        | 0x00012A                                                                                     | U1RX – UART1 Receiver                                                                                                                                                               |

| 22-23         1           24         25           26         27                                                                                                                                                                                                                                                                                             |                                                                                                    | 0x00002C                                                                                                                                        | 0x00012C                                                                                     | U1TX – UART1 Transmitter                                                                                                                                                            |

| 24<br>25<br>26<br>27                                                                                                                                                                                                                                                                                                                                        | 13                                                                                                 | 0x00002E                                                                                                                                        | 0x00012E                                                                                     | ADC1 – ADC1                                                                                                                                                                         |

| 25<br>26<br>27                                                                                                                                                                                                                                                                                                                                              | 14-15                                                                                              | 0x000030-0x000032                                                                                                                               | 0x000130-0x000132                                                                            | Reserved                                                                                                                                                                            |

| 26<br>27                                                                                                                                                                                                                                                                                                                                                    | 16                                                                                                 | 0x000034                                                                                                                                        | 0x000134                                                                                     | SI2C1 – I2C1 Slave Events                                                                                                                                                           |

| 27                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                 | 0x000036                                                                                                                                        | 0x000136                                                                                     | MI2C1 – I2C1 Master Events                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                             | 18                                                                                                 | 0x000038                                                                                                                                        | 0x000138                                                                                     | CMP – Comparator Interrupt                                                                                                                                                          |

| 00                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                                 | 0x00003A                                                                                                                                        | 0x00013A                                                                                     | Change Notification Interrupt                                                                                                                                                       |

| 28                                                                                                                                                                                                                                                                                                                                                          | 20                                                                                                 | 0x00003C                                                                                                                                        | 0x00013C                                                                                     | INT1 – External Interrupt 1                                                                                                                                                         |

| 29-34 2                                                                                                                                                                                                                                                                                                                                                     | 21-26                                                                                              | 0x00003E-0x000038                                                                                                                               | 0x00013E-0x000138                                                                            | Reserved                                                                                                                                                                            |

| 35                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                                 | 0x00004A                                                                                                                                        | 0x00014A                                                                                     | T4 – Timer4 <sup>(2)</sup>                                                                                                                                                          |

| 36                                                                                                                                                                                                                                                                                                                                                          | 28                                                                                                 | 0x00004C                                                                                                                                        | 0x00014C                                                                                     | T5 – Timer5 <sup>(2)</sup>                                                                                                                                                          |

| 37                                                                                                                                                                                                                                                                                                                                                          | 29                                                                                                 | 0x00004E                                                                                                                                        | 0x00014E                                                                                     | INT2 – External Interrupt 2                                                                                                                                                         |

| 38-44 3                                                                                                                                                                                                                                                                                                                                                     | 30-36                                                                                              | 0x000050-0x00005C                                                                                                                               | 0x000150-0x00015C                                                                            | Reserved                                                                                                                                                                            |

| 45                                                                                                                                                                                                                                                                                                                                                          | 37                                                                                                 | 0x00005E                                                                                                                                        | 0x00015E                                                                                     | IC3 – Input Capture 3                                                                                                                                                               |

| 46-64 3                                                                                                                                                                                                                                                                                                                                                     | 38-56                                                                                              | 0x000060-0x000084                                                                                                                               | 0x000160-0x000184                                                                            | Reserved                                                                                                                                                                            |

| 65                                                                                                                                                                                                                                                                                                                                                          | 57                                                                                                 | 0x000086                                                                                                                                        | 0x000186                                                                                     | PWM1 – PWM1 Period Match <sup>(1)</sup>                                                                                                                                             |

| 66-69 5                                                                                                                                                                                                                                                                                                                                                     | 58-61                                                                                              | 0x000088-0x00008E                                                                                                                               | 0x000188-0x00018E                                                                            | Reserved                                                                                                                                                                            |

| 70                                                                                                                                                                                                                                                                                                                                                          | 62                                                                                                 | 0x000090                                                                                                                                        | 0x000190                                                                                     | RTCC – Real-Time Clock and Calendar                                                                                                                                                 |

| 71                                                                                                                                                                                                                                                                                                                                                          | 63                                                                                                 | 0x000092                                                                                                                                        | 0x000192                                                                                     | FLTA1 – PWM1 Fault A <sup>(1)</sup>                                                                                                                                                 |

| 72                                                                                                                                                                                                                                                                                                                                                          | 64                                                                                                 | 0x000094                                                                                                                                        | 0x000194                                                                                     | FLTB1 – PWM1 Fault B <sup>(3)</sup>                                                                                                                                                 |

| 73                                                                                                                                                                                                                                                                                                                                                          | 65                                                                                                 | 0x000096                                                                                                                                        | 0x000196                                                                                     | U1E – UART1 Error                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                    | 0x000098-0x0000AC                                                                                                                               | 0x000198-0x0001AC                                                                            | Reserved                                                                                                                                                                            |

| 85                                                                                                                                                                                                                                                                                                                                                          | 66-76                                                                                              | 0x0000AE                                                                                                                                        | 0x0001AE                                                                                     | CTMU – Charge Time Measurement Unit                                                                                                                                                 |

| 86-125 7                                                                                                                                                                                                                                                                                                                                                    | 66-76<br>77                                                                                        | 0x0000B0-0x0000FE                                                                                                                               | 0x0001B0-0x0001FE                                                                            | Reserved                                                                                                                                                                            |

#### TABLE 7-1: INTERRUPT VECTORS

Note 1: This interrupt vector is available in dsPIC33FJ(16/32)MC10X devices only.

2: This interrupt vector is available in dsPIC33FJ32(GP/MC)10X devices only.

**3:** This interrupt vector is available in dsPIC33FJ(16/32)MC102/104 devices only.

| U-0          | U-0          | U-0              | U-0            | U-0              | U-0              | U-0          | U-0    |

|--------------|--------------|------------------|----------------|------------------|------------------|--------------|--------|

| _            | _            | —                |                |                  | —                |              | —      |

| bit 15       | ·            | •                |                |                  |                  |              | bit 8  |

|              |              |                  |                |                  |                  |              |        |

| U-0          | U-0          | U-0              | R/W-1          | R/W-1            | R/W-1            | R/W-1        | R/W-1  |

| _            | —            | —                | OCFAR4         | OCFAR3           | OCFAR2           | OCFAR1       | OCFAR0 |

| bit 7        | ·            |                  | •              |                  |                  |              | bit 0  |

|              |              |                  |                |                  |                  |              |        |

| Legend:      |              |                  |                |                  |                  |              |        |

| R = Readab   | ole bit      | W = Writable     | bit            | U = Unimpler     | mented bit, read | l as '0'     |        |

| -n = Value a | at POR       | '1' = Bit is set |                | '0' = Bit is cle | x = Bit is unkr  | nown         |        |

|              |              |                  |                |                  |                  |              |        |

| bit 15-5     | Unimplemen   | ted: Read as '   | 0'             |                  |                  |              |        |

| bit 4-0      | OCFAR<4:0>   | : Assign Outpu   | ut Capture A ( | OCFA) to the 0   | Corresponding F  | RPn Pin bits |        |

|              | 11111 = Inpu | t tied to Vss    |                |                  |                  |              |        |

|              | 11110 = Res  | erved            |                |                  |                  |              |        |

|              | •            |                  |                |                  |                  |              |        |

|              |              |                  |                |                  |                  |              |        |

#### REGISTER 10-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

11010 = Reserved 11001 = Input tied to RP25

00001 = Input tied to RP1 00000 = Input tied to RP0

.

| U-0           | U-0           | U-0              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|---------------|---------------|------------------|----------------|------------------|-----------------|-----------------|-------|

| —             | —             | —                |                |                  | RP1R<4:0>       |                 |       |

| bit 15        |               |                  |                |                  |                 |                 | bit 8 |

|               |               |                  |                |                  |                 |                 |       |

| U-0           | U-0           | U-0              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| _             | —             | —                |                |                  | RP0R<4:0>       |                 |       |

| bit 7         |               |                  |                |                  |                 |                 | bit 0 |

|               |               |                  |                |                  |                 |                 |       |

| Legend:       |               |                  |                |                  |                 |                 |       |

| R = Readable  | e bit         | W = Writable     | bit            | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|               |               |                  |                |                  |                 |                 |       |

| bit 15-13     | Unimplemen    | ted: Read as '   | 0'             |                  |                 |                 |       |

| bit 12-8      | RP1R<4:0>:    | Peripheral Outp  | out Function   | is Assigned to F | RP1 Output Pir  | n bits          |       |

|               | (see Table 10 | -2 for periphera | al function nu | mbers)           |                 |                 |       |

|               |               |                  |                |                  |                 |                 |       |

#### REGISTER 10-11: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 4-0 | <b>RP0R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP0 Output Pin bits |

|---------|---------------------------------------------------------------------------------------|

|         | (see Table 10-2 for peripheral function numbers)                                      |

Unimplemented: Read as '0'

#### REGISTER 10-12: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0                    | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|--------|-----|-----|--------------------------|-------|--------------------------|-------|-------|

| —      | —   | —   |                          |       | RP3R<4:0> <sup>(1)</sup> | 1     |       |

| bit 15 |     |     |                          |       |                          |       | bit 8 |

|        |     |     |                          |       |                          |       |       |

| U-0    | U-0 | U-0 | R/W-0                    | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|        |     |     | RP2R<4:0> <sup>(1)</sup> |       |                          |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP3R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP3 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

| bit 7-5   | Unimplemented: Read as '0'                                                                           |

| bit 4-0   | <b>RP2R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP2 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

**Note 1:** These bits are not available in dsPIC33FJXX(GP/MC)101 devices.

bit 7-5

bit 7

bit 0

### 11.1 Timer1 Control Register

| R/W-0              | U-0                               | R/W-0                        | U-0           | U-0              | U-0              | U-0                | U-0   |

|--------------------|-----------------------------------|------------------------------|---------------|------------------|------------------|--------------------|-------|

| TON <sup>(1)</sup> | _                                 | TSIDL                        | —             | _                |                  | _                  | _     |

| bit 15             |                                   |                              |               | •                |                  |                    | bit 8 |

|                    |                                   |                              |               |                  |                  |                    |       |

| U-0                | R/W-0                             | R/W-0                        | R/W-0         | U-0              | R/W-0            | R/W-0              | U-0   |

| —                  | TGATE                             | TCKPS1                       | TCKPS0        |                  | TSYNC            | TCS <sup>(1)</sup> | —     |

| bit 7              |                                   |                              |               |                  |                  |                    | bit ( |

|                    |                                   |                              |               |                  |                  |                    |       |

| Legend:            |                                   |                              |               |                  |                  |                    |       |

| R = Readable       |                                   | W = Writable                 |               | -                | mented bit, read |                    |       |

| -n = Value at      | POR                               | '1' = Bit is set             |               | '0' = Bit is cle | ared             | x = Bit is unkno   | own   |

| bit 15             | TON: Timer1                       | On hit(1)                    |               |                  |                  |                    |       |

| DIL 15             | 1 = Starts 16-                    |                              |               |                  |                  |                    |       |

|                    | 0 = Stops 16-                     |                              |               |                  |                  |                    |       |

| bit 14             | Unimplemen                        | ted: Read as '               | 0'            |                  |                  |                    |       |

| bit 13             | TSIDL: Timer                      | 1 Stop in Idle               | Node bit      |                  |                  |                    |       |

|                    |                                   |                              |               | device enters I  | dle mode         |                    |       |

|                    |                                   | s module opera               |               | ode              |                  |                    |       |

| bit 12-7           | -                                 | ted: Read as '               |               |                  |                  |                    |       |

| bit 6              |                                   | er1 Gated Time               | Accumulation  | n Enable bit     |                  |                    |       |

|                    | When TCS =<br>This bit is ign     |                              |               |                  |                  |                    |       |

|                    | When TCS =                        |                              |               |                  |                  |                    |       |

|                    |                                   | e accumulatio                |               |                  |                  |                    |       |

|                    |                                   | e accumulatio                |               |                  |                  |                    |       |

| bit 5-4            |                                   | Timer1 Input (               | Clock Prescal | e Select bits    |                  |                    |       |

|                    | 11 = 1:256<br>10 = 1:64           |                              |               |                  |                  |                    |       |

|                    | 01 = 1:8                          |                              |               |                  |                  |                    |       |

|                    | 00 = 1:1                          |                              |               |                  |                  |                    |       |

| bit 3              | -                                 | ted: Read as '               |               |                  |                  |                    |       |

| bit 2              |                                   |                              | ock Input Syn | chronization Se  | elect bit        |                    |       |

|                    | <u>When TCS =</u><br>1 = Synchron | <u>1:</u><br>izes external c | lock input    |                  |                  |                    |       |

|                    |                                   | synchronize ex               |               | nput             |                  |                    |       |

|                    | When TCS =                        | •                            |               |                  |                  |                    |       |

|                    | This bit is ign                   |                              |               |                  |                  |                    |       |

| bit 1              |                                   | Clock Source                 |               |                  |                  |                    |       |

|                    |                                   | clock from pin,              | T1CK (on the  | rising edge)     |                  |                    |       |

|                    | 0 = Internal c                    |                              |               |                  |                  |                    |       |

| bit 0              | Unimplament                       | ted: Read as '               | o'            |                  |                  |                    |       |

#### REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

NOTES:

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0               | R/W-0           | R/W-0 |

|------------------------|-------|------------------|-------|------------------------|---------------------|-----------------|-------|

| SEVTDIR <sup>(1)</sup> |       |                  | S     | SEVTCMP<14:8           | <sub>&gt;</sub> (2) |                 |       |

| bit 15                 |       |                  |       |                        |                     |                 | bit 8 |

| R/W-0                  | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0               | R/W-0           | R/W-0 |

|                        |       |                  | SEVTC | MP<7:0> <sup>(2)</sup> |                     |                 |       |

| bit 7                  |       |                  |       |                        |                     |                 | bit 0 |

| Legend:                |       |                  |       |                        |                     |                 |       |

| R = Readable           | e bit | W = Writable b   | it    | U = Unimplem           | ented bit, rea      | ıd as '0'       |       |

| -n = Value at          | POR   | '1' = Bit is set |       | '0' = Bit is clea      | ared                | x = Bit is unkr | nown  |

#### REGISTER 15-4: PxSECMP: PWMx SPECIAL EVENT COMPARE REGISTER

0 = A Special Event Trigger will occur when the PWMx time base is counting up

bit 14-0 SEVTCMP<14:0>: Special Event Compare Value bits<sup>(2)</sup>

**Note 1:** SEVTDIR is compared with PTDIR (PxTMR<15>) to generate the Special Event Trigger.

2: PxSECMP<14:0> is compared with PxTMR<14:0> to generate the Special Event Trigger.

| U-0           | U-0          | U-0              | U-0         | U-0               | U-0              | U-0             | U-0   |

|---------------|--------------|------------------|-------------|-------------------|------------------|-----------------|-------|

| _             | —            | —                |             | —                 | _                |                 | —     |

| bit 15        |              |                  |             |                   |                  |                 | bit 8 |

|               |              |                  |             |                   |                  |                 |       |

| U-0           | U-0          | R/W-0            | R/W-0       | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| —             | —            | DTS3A            | DTS3I       | DTS2A             | DTS2I            | DTS1A           | DTS1I |

| bit 7         |              |                  |             |                   |                  |                 | bit ( |

|               |              |                  |             |                   |                  |                 |       |

| Legend:       |              |                  | L :4        |                   |                  |                 |       |

| R = Readab    |              | W = Writable     |             | •                 | nented bit, read |                 |       |

| -n = Value a  | at POR       | '1' = Bit is set |             | '0' = Bit is clea | ared             | x = Bit is unkr | iown  |

| bit 15-6      | Unimplement  | ted: Read as '   | o'          |                   |                  |                 |       |

| bit 5         | •            |                  |             | nal Going Activ   | o hit            |                 |       |

| DIT D         |              | e provided fron  | Ũ           | nai Going Activ   |                  |                 |       |

|               |              | provided from    |             |                   |                  |                 |       |

| bit 4         | DTS3I: Dead- | Time Select fo   | r PWM3 Sign | al Going Inactiv  | ve bit           |                 |       |

|               |              | e provided fron  |             |                   |                  |                 |       |

|               |              | e provided fron  |             |                   |                  |                 |       |

| bit 3         |              |                  | •           | nal Going Activ   | e bit            |                 |       |

|               |              | e provided fron  |             |                   |                  |                 |       |

| <b>h</b> :+ 0 |              | e provided fron  |             |                   | e hit            |                 |       |

| bit 2         |              | e provided fron  | •           | al Going Inactiv  | e dit            |                 |       |

|               |              | e provided from  |             |                   |                  |                 |       |

| bit 1         |              | -                |             | nal Going Activ   | e bit            |                 |       |

|               |              | e provided fron  | •           |                   |                  |                 |       |

|               |              | e provided fron  |             |                   |                  |                 |       |

| bit 0         | DTS1I: Dead- | Time Select for  | r PWM1 Sign | al Going Inactiv  | ve bit           |                 |       |

|               |              | e provided fron  | n Unit B    |                   |                  |                 |       |

|               |              | e provided fron  |             |                   |                  |                 |       |

#### REGISTER 15-8: PxDTCON2: PWMx DEAD-TIME CONTROL REGISTER 2

#### 18.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 18.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en554109          |

#### 18.2.1 KEY RESOURCES

- "UART" (DS70188) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33/PIC24 Family Reference Manual"* sections

- Development Tools

#### REGISTER 20-3: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT REGISTER (CONTINUED)

| bit 3-0 | SELSRCA<3:0>: Mask A Input Select bits |

|---------|----------------------------------------|

| bit 5-0 |                                        |

|         | 1111 = Reserved                        |

|         | 1110 = Reserved                        |

|         | 1101 = Reserved                        |

|         | 1100 = Reserved                        |

|         | 1011 = Reserved                        |

|         | 1010 = Reserved                        |

|         | 1001 = Reserved                        |

|         | 1000 = Reserved                        |

|         | 0111 = Reserved                        |

|         | 0110 = Reserved                        |

|         | 0101 = PWM1H3                          |

|         | 0100 = PWM1L3                          |

|         | 0011 = PWM1H2                          |

|         | 0010 = PWM1L2                          |

|         | 0001 = PWM1H1                          |

|         | 0000 = PWM1L1                          |

|         |                                        |

|         |                                        |

#### 21.2 RTCC Control Registers

## REGISTER 21-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0          | R/W-0                               | R-0          | R-0                    | R/W-0           | R/W-0             | R/W-0           |

|----------------------|--------------|-------------------------------------|--------------|------------------------|-----------------|-------------------|-----------------|

| RTCEN <sup>(2)</sup> |              | RTCWREN                             | RTCSYNC      | HALFSEC <sup>(3)</sup> | RTCOE           | RTCPTR1           | RTCPTR0         |

| bit 15               |              |                                     |              |                        |                 |                   | bit 8           |

|                      |              |                                     |              |                        |                 |                   |                 |

| R/W-0                | R/W-0        | R/W-0                               | R/W-0        | R/W-0                  | R/W-0           | R/W-0             | R/W-0           |

| CAL7                 | CAL6         | CAL5                                | CAL4         | CAL3                   | CAL2            | CAL1              | CAL0            |

| bit 7                |              |                                     |              |                        |                 |                   | bit 0           |

|                      |              |                                     |              |                        |                 |                   |                 |

| Legend:              |              |                                     |              |                        |                 |                   |                 |

| R = Readable I       | bit          | W = Writable                        | bit          | U = Unimplen           | nented bit, rea | d as '0'          |                 |

| -n = Value at P      | OR           | '1' = Bit is set                    |              | '0' = Bit is clea      | ared            | x = Bit is unkr   | nown            |