Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 36-VTLA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc102t-i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33/PIC24 Family Reference Manual" sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSs pins, if present on the device (regardless if ADC module is not used) (see Section 2.2 "Decoupling Capacitors")

- VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1 µF (100 nF), 10V-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within

one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see Section 3.6.3.2 "Data Space Write Saturation"). For the MAC class of instructions, the accumulator write-back operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### 3.6.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF.

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000.

The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 3.6.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts, in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between Bit Positions 16 and 31 for right shifts, and between Bit Positions 0 and 16 for left shifts.

#### 5.2 RTSP Operation

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions); and to program one word. Table 26-12 shows typical erase and programming times. The 8-row erase pages are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the operation is finished.

The programming time depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3). Use the following formula to calculate the minimum and maximum values for the Word write time and page erase time (see Parameters D138a and D138b, and Parameters D137a and D137b in Table 26-12, respectively).

#### **EQUATION 5-1: PROGRAMMING TIME**

$$\frac{T}{7.37~MHz \times (FRC~Accuracy)\% \times (FRC~Tuning)\%}$$

For example, if the device is operating at +125°C, the FRC accuracy will be ±2%. If the TUN<5:0> bits (see Register 8-3) are set to `b000000, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 + 0.02) \times (1 - 0.00375)} = 47.4 \mu s$$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 49.3 \mu s$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

## 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one word (24 bits) of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Performing a page erase operation on the last page of program memory will clear the Flash Configuration Words, thereby enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

Refer to "Flash Programming" (DS70191) in the "dsPIC33/PIC24 Family Reference Manual" for details and codes examples on programming using RTSP.

## 5.4 Control Registers

Note:

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3** "**Programming Operations**" for further details.

#### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0               | R/W-0               | U-0 | U-0 | U-0   |

|--------|-----|--------|---------------------|---------------------|-----|-----|-------|

| _      | _   | INT2IF | T5IF <sup>(1)</sup> | T4IF <sup>(1)</sup> | _   | _   | _     |

| bit 15 |     |        |                     |                     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0   |

|-------|-----|-----|--------|-------|-------|---------|---------|

| _     | _   | _   | INT1IF | CNIF  | CMIF  | MI2C1IF | SI2C1IF |

| bit 7 |     |     |        |       |       |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 INT2IF: External Interrupt 2 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 12 T5IF: Timer5 Interrupt Flag Status bit<sup>(1)</sup>

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 11 **T4IF:** Timer4 Interrupt Flag Status bit<sup>(1)</sup>

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 10-5 Unimplemented: Read as '0'

bit 4 INT1IF: External Interrupt 1 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 2 CMIF: Comparator Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

Note 1: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0               | R/W-0               | U-0 | U-0 | U-0   |

|--------|-----|--------|---------------------|---------------------|-----|-----|-------|

| _      | _   | INT2IE | T5IE <sup>(1)</sup> | T4IE <sup>(1)</sup> | _   | _   | _     |

| bit 15 |     |        |                     |                     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0   |

|-------|-----|-----|--------|-------|-------|---------|---------|

| _     | _   | _   | INT1IE | CNIE  | CMIE  | MI2C1IE | SI2C1IE |

| bit 7 |     |     |        |       |       |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 INT2IE: External Interrupt 2 Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 12 **T5IE:** Timer5 Interrupt Enable bit<sup>(1)</sup>

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 11 **T4IE:** Timer4 Interrupt Enable bit<sup>(1)</sup>

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 10-5 Unimplemented: Read as '0'

bit 4 INT1IE: External Interrupt 1 Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 3 CNIE: Input Change Notification Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 2 CMIE: Comparator Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 1 MI2C1IE: I2C1 Master Events Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

Note 1: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------|-----|--------|-----|-----|-----|-----|-----|--|

| _      | _   | CTMUIE | _   | _   | _   | _   | _   |  |

| bit 15 |     |        |     |     |     |     |     |  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0                  |  |  |

|-------|-----|-----|-----|-----|-----|-------|------------------------|--|--|

| _     | _   | _   | _   | _   | _   | U1EIE | FLTB1IE <sup>(1)</sup> |  |  |

| bit 7 |     |     |     |     |     |       |                        |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 CTMUIE: CTMU Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 12-2 Unimplemented: Read as '0'

bit 1 **U1EIE:** UART1 Error Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 0 FLTB1IE: PWM1 Fault B Interrupt Enable bit<sup>(1)</sup>

1 = Interrupt request has occurred0 = Interrupt request has not occurred

Note 1: This bit is available in dsPIC(16/32)MC102/104 devices only.

#### REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-----|-------|-------|-------|

| _      | CNIP2 | CNIP1 | CNIP0 | _   | CMIP2 | CMIP1 | CMIP0 |

| bit 15 |       |       |       |     |       |       | bit 8 |

| U-0   | R/W-1    | R/W-0    | R/W-0    | U-0 | R/W-1    | R/W-0    | R/W-0    |

|-------|----------|----------|----------|-----|----------|----------|----------|

| _     | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _   | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 |

| bit 7 |          |          |          |     |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 CNIP<2:0>: Change Notification Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **CMIP<2:0>:** Comparator Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

.

\_

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7 Unimplemented: Read as '0'

bit 6-4 MI2C1IP<2:0>: I2C1 Master Events Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 SI2C1IP<2:0>: I2C1 Slave Events Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 7-26: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-0                   | R/W-0                   | R/W-0                   |

|-------|--------|--------|--------|-----|-------------------------|-------------------------|-------------------------|

| _     | U1EIP2 | U1EIP1 | U1EIP0 | _   | FLTB1IP2 <sup>(1)</sup> | FLTB1IP1 <sup>(1)</sup> | FLTB1IP0 <sup>(1)</sup> |

| bit 7 |        |        |        |     |                         |                         | bit 0                   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 Unimplemented: Read as '0'

bit 6-4 **U1EIP<2:0>:** UART1 Error Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 FLTB1IP<2:0>: PWM1 Fault B Interrupt Priority bits<sup>(1)</sup>

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

Note 1: These bits are available in dsPIC(16/32)MC102/104 devices only.

DS70000652F-page 182

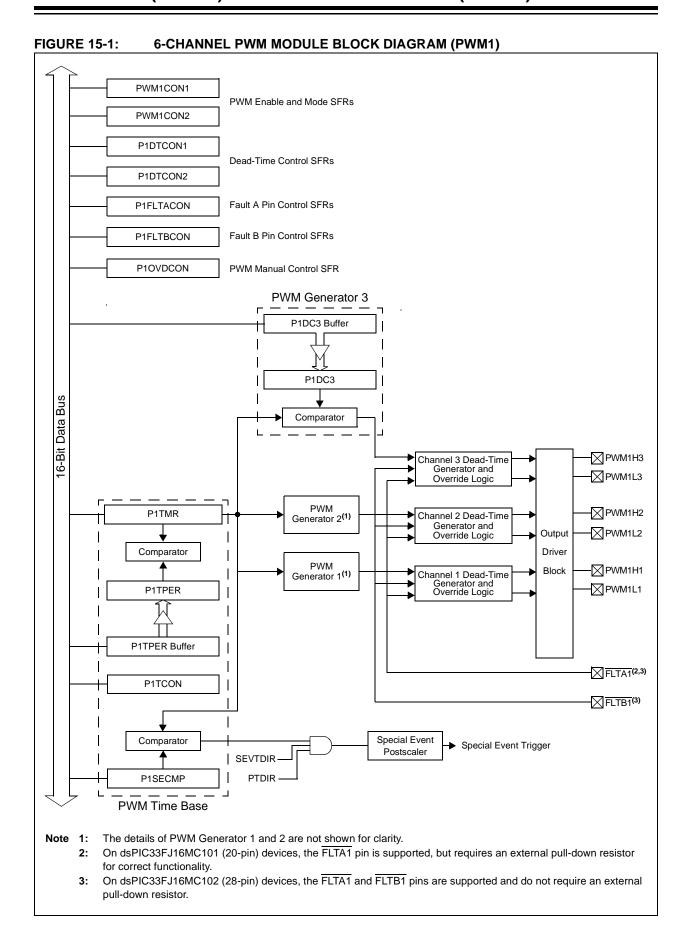

#### 15.4 PWM Control Registers

#### REGISTER 15-1: PXTCON: PWMx TIME BASE CONTROL REGISTER

|   | R/W-0  | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|---|--------|-----|--------|-----|-----|-----|-----|-------|

|   | PTEN   | _   | PTSIDL | _   | _   | _   | _   | _     |

| t | oit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  |

|--------|--------|--------|--------|---------|---------|--------|--------|

| PTOPS3 | PTOPS2 | PTOPS1 | PTOPS0 | PTCKPS1 | PTCKPS0 | PTMOD1 | PTMOD0 |

| bit 7  |        |        |        |         |         |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 PTEN: PWMx Time Base Timer Enable bit

1 = PWMx time base is on

0 = PWMx time base is off

bit 14 **Unimplemented:** Read as '0'

bit 13 PTSIDL: PWMx Time Base Stop in Idle Mode bit

1 = PWMx time base halts in CPU Idle mode

0 = PWMx time base runs in CPU Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7-4 PTOPS<3:0>: PWMx Time Base Output Postscale Select bits

1111 = 1:16 postscale

•

•

0001 = 1:2 postscale

0000 = 1:1 postscale

bit 3-2 PTCKPS<1:0>: PWMx Time Base Input Clock Prescale Select bits

11 = PWMx time base input clock period is 64 Tcy (1:64 prescale)

10 = PWMx time base input clock period is 16 Tcy (1:16 prescale)

01 = PWMx time base input clock period is 4 Tcy (1:4 prescale)

00 = PWMx time base input clock period is Tcy (1:1 prescale)

bit 1-0 PTMOD<1:0>: PWMx Time Base Mode Select bits

11 = PWMx time base operates in a Continuous Up/Down Count mode with interrupts for double PWM updates

10 = PWMx time base operates in a Continuous Up/Down Count mode

01 = PWMx time base operates in Single Pulse mode

00 = PWMx time base operates in a Free-Running mode

#### REGISTER 21-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                   | U-0   |

|-------|-----|-----|-----|-----|-----|-------------------------|-------|

| _     | _   | _   | _   | _   | _   | RTSECSEL <sup>(1)</sup> | _     |

| bit 7 |     |     |     |     |     |                         | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-2 Unimplemented: Read as '0'

bit 1 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(1)</sup>

1 = RTCC seconds clock is selected for the RTCC pin 0 = RTCC alarm pulse is selected for the RTCC pin

bit 0 Unimplemented: Read as '0'

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>) bit needs to be set.

# 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 device families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70635) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four edge input trigger sources

- · Polarity control for each edge source

- · Control of edge sequence

- · Control of response to edges

- Precise time measurement resolution of 200 ps

- Accurate current source suitable for capacitive measurement

- On-chip temperature measurement using a built-in diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 enables the module, the edge delay generation, sequencing of edges, and controls the current source and the output trigger. CTMUCON2 controls the edge source selection, edge source polarity selection and edge sampling mode. The CTMUICON register controls the selection and trim of the current source.

Figure 22-1 shows the CTMU block diagram.

TABLE 26-10: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CH        | ARACTE | RISTICS                                                                     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                    |                       |                     |                                                                                      |

|--------------|--------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|---------------------|--------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                              | Min                                                                                                                                                                                                                                               | Typ <sup>(1)</sup> | -40°C ≤<br><b>Max</b> | T <sub>A</sub> ≤ +1 | 25°C for Extended  Conditions                                                        |

|              | VIL    | Input Low Voltage                                                           |                                                                                                                                                                                                                                                   |                    |                       |                     |                                                                                      |

| DI10         |        | I/O Pins                                                                    | Vss                                                                                                                                                                                                                                               | _                  | 0.2 VDD               | V                   |                                                                                      |

| DI15         |        | MCLR                                                                        | Vss                                                                                                                                                                                                                                               | _                  | 0.2 VDD               | V                   |                                                                                      |

| DI18         |        | I/O Pins with SDAx, SCLx                                                    | Vss                                                                                                                                                                                                                                               | _                  | 0.3 VDD               | V                   | SMBus disabled                                                                       |

| DI19         |        | I/O Pins with SDAx, SCLx                                                    | Vss                                                                                                                                                                                                                                               | _                  | 0.8                   | V                   | SMBus enabled                                                                        |

|              | VIH    | Input High Voltage                                                          |                                                                                                                                                                                                                                                   |                    |                       |                     |                                                                                      |

| DI20         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> I/O Pins 5V Tolerant <sup>(4)</sup> | 0.7 VDD<br>0.7 VDD                                                                                                                                                                                                                                | _                  | VDD<br>5.5            | V<br>V              |                                                                                      |

| DI28         |        | SDAx, SCLx                                                                  | 0.7 VDD                                                                                                                                                                                                                                           | _                  | 5.5                   | V                   | SMBus disabled                                                                       |

| DI29         |        | SDAx, SCLx                                                                  | 2.1                                                                                                                                                                                                                                               | _                  | 5.5                   | V                   | SMBus enabled                                                                        |

|              | ICNPU  | CNx Pull-up Current                                                         |                                                                                                                                                                                                                                                   |                    |                       |                     |                                                                                      |

| DI30         |        |                                                                             | 50                                                                                                                                                                                                                                                | 250                | 450                   | μΑ                  | VDD = 3.3V, VPIN = VSS                                                               |

| DI50         | lıL    | Input Leakage Current <sup>(2,3)</sup> I/O Pins 5V Tolerant <sup>(4)</sup>  | _                                                                                                                                                                                                                                                 | _                  | ±2                    | μА                  | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                                           |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                     | _                                                                                                                                                                                                                                                 | _                  | ±1                    | μА                  | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +85°C                    |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                     | _                                                                                                                                                                                                                                                 | _                  | ±2                    | μΑ                  | Shared with external reference pins, -40°C ≤ TA ≤ +85°C                              |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                     | _                                                                                                                                                                                                                                                 | _                  | ±3.5                  | μΑ                  | VSS ≤ VPIN ≤ VDD,<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                   |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                                     | _                                                                                                                                                                                                                                                 | _                  | ±8                    | μΑ                  | Analog pins shared with external reference pins, -40°C ≤ TA ≤ +125°C                 |

| DI55         |        | MCLR                                                                        | _                                                                                                                                                                                                                                                 | _                  | ±2                    | μΑ                  | $VSS \le VPIN \le VDD$                                                               |

| DI56         |        | OSC1                                                                        | _                                                                                                                                                                                                                                                 | _                  | ±2                    | μА                  | $ \begin{array}{c} VSS \leq VPIN \leq VDD, \\ XT \; and \; HS \; modes \end{array} $ |

- **Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 5: VIL source < (VSS 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins, VIH source > (VDD + 0.3), 5V tolerant pins, VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

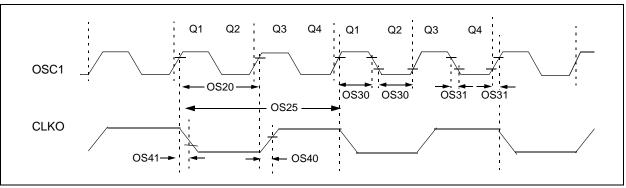

FIGURE 26-2: EXTERNAL CLOCK TIMING

**TABLE 26-16: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHA       | AC CHARACTERISTICS |                                                                                    |                                        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |          |            |                           |  |  |

|--------------|--------------------|------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|---------------------------|--|--|

| Param<br>No. | Symb               | Characteristic                                                                     | Min Typ <sup>(1)</sup> Max Units Condi |                                                                                                                                                                                                                                                  |          |            |                           |  |  |

| OS10         | FIN                | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                     | _                                                                                                                                                                                                                                                | 32       | MHz        | EC                        |  |  |

|              |                    | Oscillator Crystal Frequency                                                       | 3.0<br>10                              |                                                                                                                                                                                                                                                  | 10<br>32 | MHz<br>MHz | MS<br>HS                  |  |  |

|              |                    |                                                                                    | 31                                     | _                                                                                                                                                                                                                                                | 33       | kHz        | SOSC                      |  |  |

| OS20         | Tosc               | Tosc = 1/Fosc                                                                      | 31.25                                  | _                                                                                                                                                                                                                                                | DC       | ns         |                           |  |  |

| OS25         | Tcy                | Instruction Cycle Time <sup>(2,4)</sup>                                            | 62.5                                   | _                                                                                                                                                                                                                                                | DC       | ns         |                           |  |  |

| OS30         | TosL,<br>TosH      | External Clock in (OSC1) <sup>(5)</sup><br>High or Low Time                        | 0.45 x Tosc                            | _                                                                                                                                                                                                                                                | _        | ns         | EC                        |  |  |

| OS31         | TosR,<br>TosF      | External Clock in (OSC1) <sup>(5)</sup><br>Rise or Fall Time                       | _                                      | _                                                                                                                                                                                                                                                | 20       | ns         | EC                        |  |  |

| OS40         | TckR               | CLKO Rise Time <sup>(3,5)</sup>                                                    | _                                      | 6                                                                                                                                                                                                                                                | 10       | ns         |                           |  |  |

| OS41         | TckF               | CLKO Fall Time <sup>(3,5)</sup>                                                    |                                        | 6                                                                                                                                                                                                                                                | 10       | ns         |                           |  |  |

| OS42         | Gм                 | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                     | 16                                                                                                                                                                                                                                               | 18       | mA/V       | VDD = 3.3V,<br>TA = +25°C |  |  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 2: Instruction cycle period (TcY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: These parameters are characterized by similarity, but are tested in manufacturing at FIN = 32 MHz only.

- 5: These parameters are characterized by similarity, but are not tested in manufacturing.

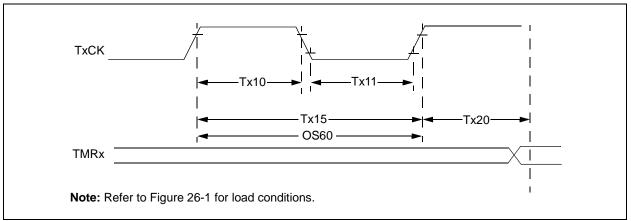

FIGURE 26-5: TIMER1/2/3 EXTERNAL CLOCK TIMING CHARACTERISTICS

TABLE 26-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHARACTERISTICS (unl |                                       |                                                                                                             |                     | nless | d Operating C<br>otherwise sta<br>g temperature | ted)<br>-40° | C ≤ TA ≤ +85°C<br>C ≤ TA ≤ +125°C | for Ind |                                                   |

|-------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------|-------|-------------------------------------------------|--------------|-----------------------------------|---------|---------------------------------------------------|

| Param<br>No.            | Symbol                                | Characteristic <sup>(2)</sup>                                                                               |                     |       | Min                                             | Тур          | Max                               | Units   | Conditions                                        |

| TA10                    | ТтхН                                  | T1CK High<br>Time                                                                                           | Synchronous<br>mode |       | Greater of:<br>20 or<br>(Tcy + 20)/N            | _            | _                                 | ns      | Must also meet Parameter TA15, N = prescale value |

|                         |                                       |                                                                                                             | Asynchronou         | us    | 35                                              | _            |                                   | ns      | (1, 8, 64, 256)                                   |

| TA11                    | 11 TTXL T1CK Low Synchro<br>Time mode |                                                                                                             | Synchronous<br>mode |       | Greater of:<br>20 ns or<br>(Tcy + 20)/N         | _            | _                                 | ns      | Must also meet Parameter TA15, N = prescale value |

|                         |                                       |                                                                                                             | Asynchronou         | us    | 10                                              | _            | _                                 | ns      | (1, 8, 64, 256)                                   |

| TA15                    | ТтхР                                  | T1CK Input<br>Period                                                                                        | Synchronous<br>mode |       | Greater of:<br>40 or<br>2 Tcy + 40)/N           | _            |                                   | ns      | N = prescale value<br>(1, 8, 64, 256)             |

| OS60                    | Ft1                                   | SOSC1/T1CK Oscillator<br>Input Frequency Range<br>(oscillator enabled by setting<br>the TCS (T1CON<1>) bit) |                     | ng    | DC                                              | _            | 50                                | kHz     |                                                   |

| TA20                    | TCKEXTMRL                             | Delay from Ex<br>Clock Edge to                                                                              |                     |       | 0.75 Tcy + 40                                   |              | 1.75 Tcy + 40                     | ns      |                                                   |

Note 1: Timer1 is a Type A.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

TABLE 26-36: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING REQUIREMENTS FOR dsPIC33FJ16(GP/MC)10X

| AC CH        | ARACTERIS             | Standard Operating Conditions: 2.4V to 3.6V (unless otherwise stated) |              |                        |    |       |                                      |

|--------------|-----------------------|-----------------------------------------------------------------------|--------------|------------------------|----|-------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                         | Min          | Min Typ <sup>(2)</sup> |    | Units | Conditions                           |

| SP70         | TscP                  | Maximum SCKx Input Frequency                                          | _            | _                      | 11 | MHz   | See Note 3                           |

| SP72         | TscF                  | SCKx Input Fall Time                                                  | _            | _                      | _  | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73         | TscR                  | SCKx Input Rise Time                                                  | _            | _                      | _  | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                            | _            | _                      | _  | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                            | _            | _                      | _  | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge                                | _            | 6                      | 20 | ns    |                                      |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to First SCKx Edge                             | 30           | _                      | _  | ns    |                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                            | 30           | _                      | _  | ns    |                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                             | 30           | _                      | _  | ns    |                                      |

| SP50         | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx Input                                         | 120          | _                      | _  | ns    |                                      |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                | 10           | _                      | 50 | ns    | See Note 4                           |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                   | 1.5 Tcy + 40 |                        |    | ns    | See Note 4                           |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 3: The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

TABLE 26-49: 10-BIT ADC CONVERSION TIMING REQUIREMENTS

| AC CH        | AC CHARACTERISTICS |                                                                      |         | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |         |       |                                                           |  |  |

|--------------|--------------------|----------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-----------------------------------------------------------|--|--|

| Param<br>No. | Symbol             | Characteristic                                                       | Min.    | Typ <sup>(1)</sup>                                                                                                                                                                                                                               | Max.    | Units | Conditions                                                |  |  |

|              |                    | Clock                                                                | Paramet | ers <sup>(2)</sup>                                                                                                                                                                                                                               |         |       |                                                           |  |  |

| AD50         | TAD                | ADC Clock Period                                                     | 76      | _                                                                                                                                                                                                                                                | _       | ns    |                                                           |  |  |

| AD51         | tRC                | ADC Internal RC Oscillator Period                                    | _       | 250                                                                                                                                                                                                                                              | _       | ns    |                                                           |  |  |

|              | Conversion Rates   |                                                                      |         |                                                                                                                                                                                                                                                  |         |       |                                                           |  |  |

| AD55         | tCONV              | Conversion Time                                                      | _       | 12 TAD                                                                                                                                                                                                                                           | _       | _     |                                                           |  |  |

| AD56         | FCNV               | Throughput Rate                                                      | _       | _                                                                                                                                                                                                                                                | 1.1     | Msps  |                                                           |  |  |

| AD57         | TSAMP              | Sample Time                                                          | 2.0 TAD | _                                                                                                                                                                                                                                                | _       |       |                                                           |  |  |

|              |                    | Timin                                                                | g Param | eters                                                                                                                                                                                                                                            |         |       |                                                           |  |  |

| AD60         | tPCS               | Conversion Start from Sample Trigger <sup>(1)</sup>                  | 2.0 TAD |                                                                                                                                                                                                                                                  | 3.0 TAD | I     | Auto-Convert Trigger<br>(SSRC<2:0> = 111) not<br>selected |  |  |

| AD61         | tPSS               | Sample Start from Setting Sample (SAMP) bit <sup>(1)</sup>           | 2.0 TAD | _                                                                                                                                                                                                                                                | 3.0 TAD |       |                                                           |  |  |

| AD62         | tcss               | Conversion Completion to Sample Start (ASAM = 1) <sup>(1)</sup>      | _       | 0.5 TAD                                                                                                                                                                                                                                          | _       | _     |                                                           |  |  |

| AD63         | tDPU               | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(1)</sup> | _       | _                                                                                                                                                                                                                                                | 20      | μЅ    |                                                           |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

**<sup>2:</sup>** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

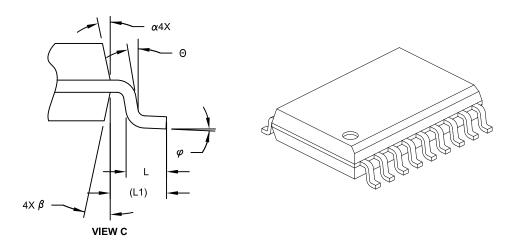

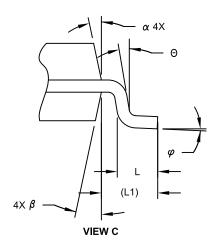

#### 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |           |      |  |  |

|--------------------------|-----------|-------------|-----------|------|--|--|

| Dimension Lin            | nits      | MIN         | NOM       | MAX  |  |  |

| Number of Pins           | N         |             | 18        |      |  |  |

| Pitch                    | е         |             | 1.27 BSC  |      |  |  |

| Overall Height           | Α         | -           | _         | 2.65 |  |  |

| Molded Package Thickness | A2        | 2.05        | -         | -    |  |  |

| Standoff §               | A1        | 0.10        | -         | 0.30 |  |  |

| Overall Width            | E         |             | 10.30 BSC |      |  |  |

| Molded Package Width     | E1        |             | 7.50 BSC  |      |  |  |

| Overall Length           | D         | ,           | 11.55 BSC |      |  |  |

| Chamfer (Optional)       | h         | 0.25        | _         | 0.75 |  |  |

| Foot Length              | L         | 0.40        | -         | 1.27 |  |  |

| Footprint                | L1        |             | 1.40 REF  |      |  |  |

| Lead Angle               | Θ         | 0°          | _         | -    |  |  |

| Foot Angle               | $\varphi$ | 0°          | -         | 8°   |  |  |

| Lead Thickness           | С         | 0.20        | -         | 0.33 |  |  |

| Lead Width               | b         | 0.31        | -         | 0.51 |  |  |

| Mold Draft Angle Top     | α         | 5°          | _         | 15°  |  |  |

| Mold Draft Angle Bottom  | β         | 5°          | -         | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-051C Sheet 2 of 2

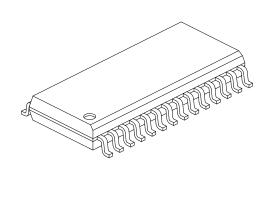

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |           |      |  |  |

|--------------------------|-----------|-------------|-----------|------|--|--|

| Dimension                | Limits    | MIN         | NOM       | MAX  |  |  |

| Number of Pins           | N         |             | 28        |      |  |  |

| Pitch                    | е         |             | 1.27 BSC  |      |  |  |

| Overall Height           | Α         | -           | -         | 2.65 |  |  |

| Molded Package Thickness | A2        | 2.05        | -         | -    |  |  |

| Standoff §               | A1        | 0.10        | -         | 0.30 |  |  |

| Overall Width            | E         |             | 10.30 BSC |      |  |  |

| Molded Package Width     | E1        | 7.50 BSC    |           |      |  |  |

| Overall Length           | D         |             | 17.90 BSC |      |  |  |

| Chamfer (Optional)       | h         | 0.25        | ı         | 0.75 |  |  |

| Foot Length              | L         | 0.40        | -         | 1.27 |  |  |

| Footprint                | L1        | 1.40 REF    |           |      |  |  |

| Lead Angle               | Θ         | 0°          | ı         | 1    |  |  |

| Foot Angle               | $\varphi$ | 0°          | ı         | 8°   |  |  |

| Lead Thickness           | С         | 0.18        | -         | 0.33 |  |  |

| Lead Width               | b         | 0.31        | -         | 0.51 |  |  |

| Mold Draft Angle Top     | α         | 5°          |           | 15°  |  |  |

| Mold Draft Angle Bottom  | β         | 5°          | -         | 15°  |  |  |

#### Notes

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

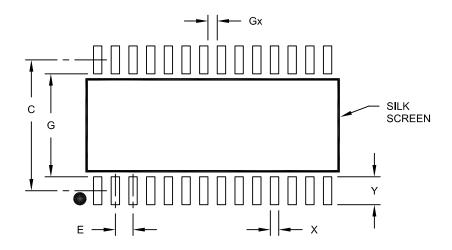

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**lote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | N   | MILLIMETERS |      |      |  |  |  |

|--------------------------|-----|-------------|------|------|--|--|--|

| Dimensior                | MIN | NOM         | MAX  |      |  |  |  |

| Contact Pitch            |     | 1.27 BSC    |      |      |  |  |  |

| Contact Pad Spacing      | С   |             | 9.40 |      |  |  |  |

| Contact Pad Width (X28)  | X   |             |      | 0.60 |  |  |  |

| Contact Pad Length (X28) | Y   |             |      | 2.00 |  |  |  |

| Distance Between Pads    | Gx  | 0.67        |      |      |  |  |  |

| Distance Between Pads    | G   | 7.40        |      |      |  |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A