Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 14x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc104-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

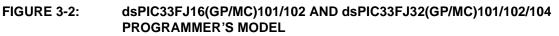

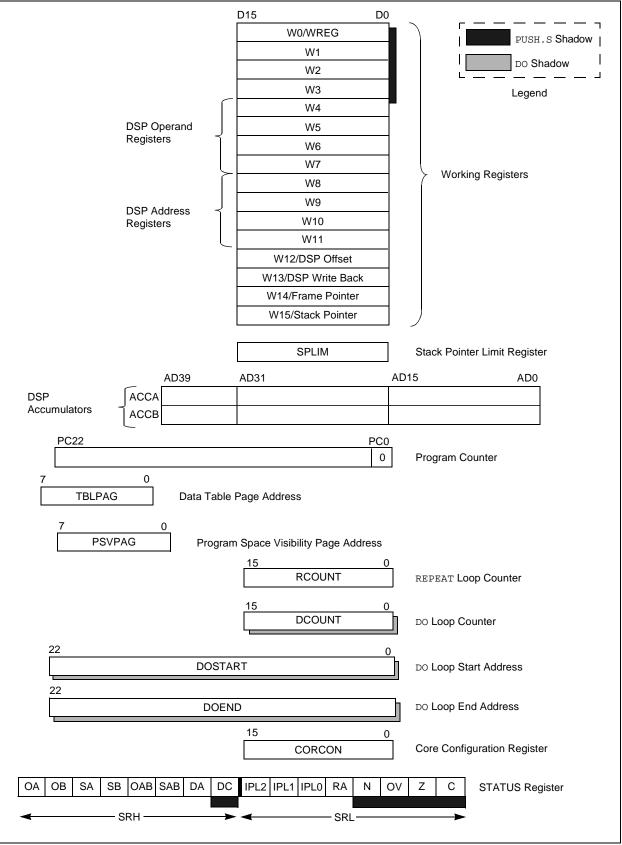

# 3.4 CPU Control Registers

| R-0                 | R-0                 | R/C-0                                  | R/C-0             | R-0                     | R/C-0              | R-0               | R/W-0         |

|---------------------|---------------------|----------------------------------------|-------------------|-------------------------|--------------------|-------------------|---------------|

| OA                  | OB                  | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB                     | SAB                | DA                | DC            |

| bit 15              | ·                   |                                        |                   |                         |                    |                   | bit 8         |

| (2)                 | )) (2)              | (2)                                    |                   |                         |                    |                   |               |

| R/W-0 <sup>(3</sup> |                     | R/W-0 <sup>(3)</sup>                   | R-0               | R/W-0                   | R/W-0              | R/W-0             | R/W-0         |

| IPL2 <sup>(2)</sup> | IPL1 <sup>(2)</sup> | IPL0 <sup>(2)</sup>                    | RA                | N                       | OV                 | Z                 | С             |

| bit 7               |                     |                                        |                   |                         |                    |                   | bit (         |

| Legend:             |                     | C = Clearable                          | bit               |                         |                    |                   |               |

| R = Reada           | able bit            | W = Writable I                         | oit               | U = Unimpler            | mented bit, read   | l as '0'          |               |

| -n = Value          | at POR              | '1' = Bit is set                       |                   | '0' = Bit is cle        | ared               | x = Bit is unkn   | own           |

|                     |                     |                                        |                   |                         |                    |                   |               |

| bit 15              |                     | ator A Overflow                        |                   |                         |                    |                   |               |

|                     |                     | ator A has overf<br>ator A has not o   |                   |                         |                    |                   |               |

| bit 14              |                     | ator B Overflow                        |                   |                         |                    |                   |               |

| DIL 14              |                     | ator B has overf                       |                   |                         |                    |                   |               |

|                     |                     | ator B has not o                       |                   |                         |                    |                   |               |

| bit 13              | SA: Accumul         | ator A Saturatio                       | on 'Sticky' Sta   | itus bit <sup>(1)</sup> |                    |                   |               |

|                     | 1 = Accumula        | ator A is saturat                      | ed or has be      | en saturated at         | some time          |                   |               |

|                     |                     | ator A is not sat                      |                   | (4)                     |                    |                   |               |

| bit 12              |                     | ator B Saturatio                       |                   |                         |                    |                   |               |

|                     |                     | ator B is saturat<br>ator B is not sat |                   | en saturated at         | some time          |                   |               |

| bit 11              | <b>OAB:</b> OA    C | B Combined A                           | ccumulator C      | Verflow Status          | bit                |                   |               |

|                     |                     | ators A or B hav                       |                   |                         |                    |                   |               |

| bit 10              | <b>SAB:</b> SA    S | B Combined Ac                          | cumulator 'S      | ticky' Status bit       |                    |                   |               |

|                     |                     |                                        |                   |                         | urated at some     | time in the past  |               |

|                     |                     | ccumulator A o                         |                   |                         | it will clear SA a | and SB            |               |

| bit 9               | DA: DO LOOP         |                                        |                   | Cleaning this bi        |                    |                   |               |

|                     | 1 = DO loop is      |                                        |                   |                         |                    |                   |               |

|                     |                     | not in progres                         | 5                 |                         |                    |                   |               |

| bit 8               | DC: MCU AL          | U Half Carry/Bo                        | prrow bit         |                         |                    |                   |               |

|                     |                     |                                        | ow-order bit      | (for byte-sized o       | data) or 8th low-  | order bit (for wo | rd-sized data |

|                     |                     | sult occurred                          | h low-order       | hit (for hyte-siz       | ed data) or 8th    | low-order bit (f  | or word-sized |

|                     | •                   | he result occur                        |                   |                         |                    |                   |               |

| Note 1:             | This bit can be rea | nd or cleared (ne                      | ot set).          |                         |                    |                   |               |

|                     | The IPL<2:0> bits   |                                        |                   |                         |                    |                   |               |

|                     | Level. The value in | n parentheses i                        | ndicates the      | IPL if IPL<3> =         | 1. User interru    | ots are disabled  | when          |

|                     | IPL<3> = 1.         |                                        |                   |                         |                    |                   |               |

## REGISTER 3-1: SR: CPU STATUS REGISTER

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

## 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY. N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, although the implemented memory locations vary by device.

# 5.2 RTSP Operation

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions); and to program one word. Table 26-12 shows typical erase and programming times. The 8-row erase pages are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes.

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the operation is finished.

The programming time depends on the FRC accuracy (see Table 26-18) and the value of the FRC Oscillator Tuning register (see Register 8-3). Use the following formula to calculate the minimum and maximum values for the Word write time and page erase time (see Parameters D138a and D138b, and Parameters D137a and D137b in Table 26-12, respectively).

#### EQUATION 5-1: PROGRAMMING TIME

$\frac{T}{7.37 \text{ MHz} \times (FRC \text{ Accuracy})\% \times (FRC \text{ Tuning})\%}$

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 8-3) are set to `b000000, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 + 0.02) \times (1 - 0.00375)} = 47.4 \mu s$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{355 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 49.3 \mu s$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one word (24 bits) of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

| Note: | Performing a page erase operation on the   |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | last page of program memory will clear the |  |  |  |  |  |  |  |

|       | Flash Configuration Words, thereby         |  |  |  |  |  |  |  |

|       | enabling code protection as a result.      |  |  |  |  |  |  |  |

|       | Therefore, users should avoid performing   |  |  |  |  |  |  |  |

|       | page erase operations on the last page of  |  |  |  |  |  |  |  |

|       | program memory.                            |  |  |  |  |  |  |  |

Refer to **"Flash Programming"** (DS70191) in the *"dsPIC33/PIC24 Family Reference Manual"* for details and codes examples on programming using RTSP.

# 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts (Part IV)" (DS70300) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family CPU. It has the following features:

- Up to eight processor exceptions and software traps

- Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

# 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location, 000004h. The IVT contains 126 vectors consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR). Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices implement up to 26 unique interrupts and 4 nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a way to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications to facilitate evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices clear their registers in response to a Reset, forcing the PC to zero. The Digital Signal Controller then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# FIGURE 7-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 INTERRUPT VECTOR TABLE

| 1                                 |                                            | 7                    |                                                        |

|-----------------------------------|--------------------------------------------|----------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction                   | 0x000000             |                                                        |

|                                   | Reset – GOTO Address                       | 0x000002             |                                                        |

|                                   | Reserved                                   | 0x000004             |                                                        |

|                                   | Oscillator Fail Trap Vector                | _                    |                                                        |

|                                   | Address Error Trap Vector                  | _                    |                                                        |

|                                   | Stack Error Trap Vector                    | _                    |                                                        |

|                                   | Math Error Trap Vector                     | _                    |                                                        |

|                                   | Reserved                                   | -                    |                                                        |

|                                   | Reserved                                   | _                    |                                                        |

|                                   | Reserved<br>Interrupt Vector 0             | 0x000014             |                                                        |

|                                   | Interrupt Vector 1                         | 0,000014             |                                                        |

|                                   |                                            | -                    |                                                        |

|                                   | ~                                          |                      |                                                        |

|                                   | ~                                          | _                    |                                                        |

|                                   | Interrupt Vector 52                        | 0x00007C             | (4)                                                    |

|                                   | Interrupt Vector 53                        | 0x00007E             | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                        | 0x000080             |                                                        |

| iori                              | ~                                          |                      |                                                        |

| ā                                 | ~                                          |                      |                                                        |

| der                               | ~                                          |                      |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                       | 0x0000FC             |                                                        |

| ra                                | Interrupt Vector 117                       | 0x0000FE             |                                                        |

| atu                               | Reserved                                   | 0x000100             |                                                        |

| Z                                 | Reserved                                   | 0x000102             |                                                        |

| sing                              | Reserved                                   |                      |                                                        |

| eas                               | Oscillator Fail Trap Vector                |                      |                                                        |

| ecr                               | Address Error Trap Vector                  |                      |                                                        |

| ă                                 | Stack Error Trap Vector                    |                      |                                                        |

|                                   | Math Error Trap Vector                     |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Interrupt Vector 0                         | 0x000114             |                                                        |

|                                   | Interrupt Vector 1                         | _                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~<br>Interrupt Vector 52                   | 0x000470             | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   |                                            | 0x00017C             |                                                        |

|                                   | Interrupt Vector 53<br>Interrupt Vector 54 | 0x00017E<br>0x000180 |                                                        |

|                                   | ~                                          | 0000180              |                                                        |

|                                   | ~                                          | -                    |                                                        |

|                                   | ~                                          | _                    |                                                        |

|                                   | -<br>Interrupt Vector 116                  | -                    |                                                        |

|                                   | Interrupt Vector 117                       | 0x0001FE             |                                                        |

| *                                 | Start of Code                              | 0x000200             | L                                                      |

|                                   |                                            |                      |                                                        |

| Note 1: See                       | e Table 7-1 for the list of impleme        | ented interrupt v    | ectors.                                                |

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>                                                          |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit                                                                                                     |

|       | 1 = Interrupt request has occurred                                                                                                                           |

|       | 0 = Interrupt request has not occurred                                                                                                                       |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit                                                                                                                 |

|       | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                                                                 |

|       | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>INTOIF: External Interrupt 0 Flag Status bit</li> </ul> |

# 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. Devices can manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 9.1 Clock Frequency and Clock Switching

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration**".

## 9.2 Instruction-Based Power-Saving Modes

dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices have two special powersaving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

# 9.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of the these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE; Put the device into SLEEP modePWRSAV #IDLE\_MODE; Put the device into IDLE mode

#### REGISTER 9-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

bit 3 SPI1MD: SPI1 Module Disable bit 1 = SPI1 module is disabled 0 = SPI1 module is enabled

#### bit 2-1 Unimplemented: Read as '0'

- bit 0 AD1MD: ADC1 Module Disable bit<sup>(2)</sup>

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

- **Note 1:** These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

- 2: PCFGx bits have no effect if the ADC module is disabled by setting this bit. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

#### REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | —   | —   | —   | —   | IC3MD | IC2MD | IC1MD |

| bit 15 |     |     |     |     |       |       | bit 8 |

|        |     |     |     |     |       |       |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0   | R/W-0 | R/W-0 |

| —      | —   | —   | —   | —   | —     | OC2MD | OC1MD |

| bit 7  |     |     | •   |     |       |       | bit 0 |

|        |     |     |     |     |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                 |

|-----------|------------------------------------------------------------|

| bit 10    | IC3MD: Input Capture 3 Module Disable bit                  |

|           | 1 = Input Capture 3 module is disabled                     |

|           | 0 = Input Capture 3 module is enabled                      |

| bit 9     | IC2MD: Input Capture 2 Module Disable bit                  |

|           | 1 = Input Capture 2 module is disabled                     |

|           | 0 = Input Capture 2 module is enabled                      |

| bit 8     | IC1MD: Input Capture 1 Module Disable bit                  |

|           | <ol> <li>I = Input Capture 1 module is disabled</li> </ol> |

|           | 0 = Input Capture 1 module is enabled                      |

| bit 7-2   | Unimplemented: Read as '0'                                 |

| bit 1     | OC2MD: Output Compare 2 Module Disable bit                 |

|           | 1 = Output Compare 2 module is disabled                    |

|           | 0 = Output Compare 2 module is enabled                     |

| bit 0     | OC1MD: Output Compare 1 Module Disable bit                 |

|           | 1 = Output Compare 1 module is disabled                    |

|           | 0 = Output Compare 1 module is enabled                     |

|           |                                                            |

# 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70193) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Output Latch (LATx) register read the latch. Writes to the Output Latch register write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that is not valid for a particular device will be disabled. This means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

# 10.4.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 10.4.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language<br>functions for unlocking the OSCCON<br>register: |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                           |  |  |  |  |  |  |  |

|       | See MPLAB IDE Help for more information.                                                               |  |  |  |  |  |  |  |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

### 10.4.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.4.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

|                         | 10-4: RPINF                                                                                                                                |                 | ERAL PIN SE           |                       |                       |                       |                       |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| U-0                     | U-0                                                                                                                                        | U-0             | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 |  |  |  |

| —                       | —                                                                                                                                          | _               | T5CKR4 <sup>(1)</sup> | T5CKR3 <sup>(1)</sup> | T5CKR2 <sup>(1)</sup> | T5CKR1 <sup>(1)</sup> | T5CKR0 <sup>(1)</sup> |  |  |  |

| bit 15                  |                                                                                                                                            |                 |                       |                       |                       |                       | bit 8                 |  |  |  |

| U-0                     | U-0                                                                                                                                        | U-0             | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 | R/W-1                 |  |  |  |

| _                       | _                                                                                                                                          |                 | T4CKR4 <sup>(1)</sup> | T4CKR3 <sup>(1)</sup> | T4CKR2 <sup>(1)</sup> | T4CKR1 <sup>(1)</sup> | T4CKR0 <sup>(1)</sup> |  |  |  |

| bit 7                   |                                                                                                                                            |                 |                       | 1                     |                       |                       | bit (                 |  |  |  |

| Logondi                 |                                                                                                                                            |                 |                       |                       |                       |                       |                       |  |  |  |

| Legend:<br>R = Readable | e hit                                                                                                                                      | W = Writable    | hit                   | II = Unimplen         | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at           |                                                                                                                                            | '1' = Bit is se |                       | '0' = Bit is clea     |                       | x = Bit is unkr       | own                   |  |  |  |

|                         |                                                                                                                                            |                 | -                     |                       |                       |                       |                       |  |  |  |

| bit 15-13               | Unimplemen                                                                                                                                 | nted: Read as   | '0'                   |                       |                       |                       |                       |  |  |  |

| bit 12-8                | -                                                                                                                                          |                 |                       | ck (T5CK) to th       | ne Correspondi        | na RPn Pin hits       | <u>s</u> (1)          |  |  |  |

|                         | <b>T5CKR&lt;4:0&gt;:</b> Assign Timer5 External Clock (T5CK) to the Corresponding RPn Pin bits <sup>(1)</sup><br>11111 = Input tied to Vss |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | 11111 = mpt                                                                                                                                |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | -                                                                                                                                          |                 |                       |                       |                       |                       |                       |  |  |  |

|                         |                                                                                                                                            |                 |                       |                       |                       |                       |                       |  |  |  |

|                         |                                                                                                                                            |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | 11010 = Reserved                                                                                                                           |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | 11001 = Input tied to RP25                                                                                                                 |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | •                                                                                                                                          |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | •                                                                                                                                          |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | 00001 = Input tied to RP1                                                                                                                  |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | 00000 = Inpu                                                                                                                               | ut tied to RP0  |                       |                       |                       |                       |                       |  |  |  |

| bit 7-5                 | Unimplemen                                                                                                                                 | nted: Read as   | '0'                   |                       |                       |                       |                       |  |  |  |

| bit 4-0                 | T4CKR<4:0>                                                                                                                                 | . Assign Time   | r4 External Clo       | ck (T4CK) to th       | ne Correspondi        | ng RPn Pin bits       | <sub>3</sub> (1)      |  |  |  |

|                         | 11111 <b>= I</b> npu                                                                                                                       | ut tied to Vss  |                       |                       |                       |                       |                       |  |  |  |

|                         | 11110 = Res                                                                                                                                | served          |                       |                       |                       |                       |                       |  |  |  |

|                         |                                                                                                                                            |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | •                                                                                                                                          |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | •<br>11010 Dee                                                                                                                             | an cad          |                       |                       |                       |                       |                       |  |  |  |

|                         | 11010 = Res                                                                                                                                | ut tied to RP25 | 1                     |                       |                       |                       |                       |  |  |  |

|                         |                                                                                                                                            |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | 11001 - 1100                                                                                                                               |                 |                       |                       |                       |                       |                       |  |  |  |

|                         | •                                                                                                                                          |                 |                       |                       |                       |                       |                       |  |  |  |

|                         |                                                                                                                                            |                 |                       |                       |                       |                       |                       |  |  |  |

|                         |                                                                                                                                            | ut tied to RP1  |                       |                       |                       |                       |                       |  |  |  |

# REGISTER 10-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

NOTES:

# dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

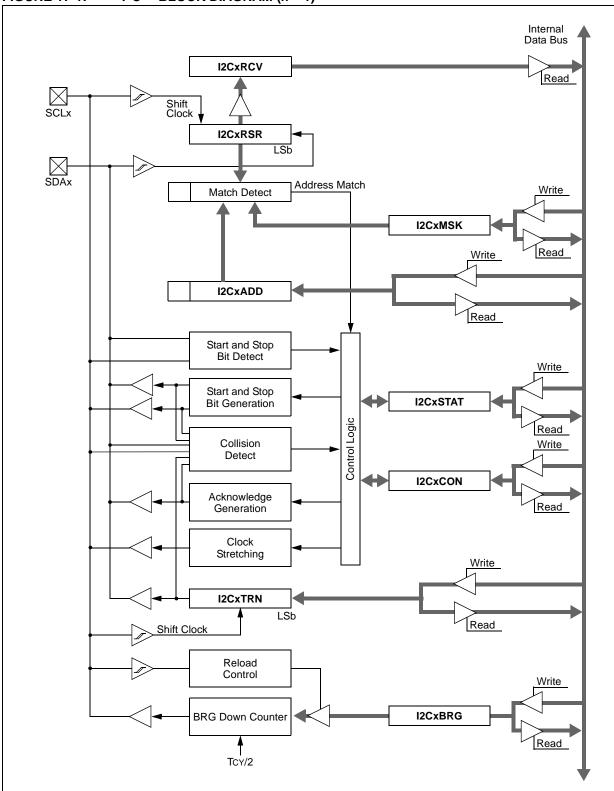

FIGURE 17-1:  $I^2C^{TM}$  BLOCK DIAGRAM (x = 1)

| Bit Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| GCP         | General Segment Code-Protect bit                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|             | <ul><li>1 = User program memory is not code-protected</li><li>0 = Code protection is enabled for the entire program memory space</li></ul>                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| GWRP        | General Segment Write-Protect bit                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|             | <ul><li>1 = User program memory is not write-protected</li><li>0 = User program memory is write-protected</li></ul>                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| IESO        | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator source when ready</li> <li>0 = Starts up device with user-selected oscillator source</li> </ul>                                                                                                                                                               |  |  |  |  |  |  |

| PWMLOCK     | PWM Lock Enable bit                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|             | <ul><li>1 = Certain PWM registers may only be written after a key sequence</li><li>0 = PWM registers may be written without a key sequence</li></ul>                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| WDTWIN<1:0> | Watchdog Timer Window Select bits<br>11 = WDT window is 24% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period                                                                                                                                                                                                                 |  |  |  |  |  |  |

| FNOSC<2:0>  | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Reserved; do not use<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Secondary Oscillator (SOSC)<br>011 = Primary Oscillator with PLL module (MS + PLL, EC + PLL)<br>010 = Primary Oscillator (MS, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N and PLL module (FRCDIVN + PLL)<br>000 = Fast RC Oscillator (FRC) |  |  |  |  |  |  |

| FCKSM<1:0>  | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                   |  |  |  |  |  |  |

| IOL1WAY     | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| OSCIOFNC    | OSC2 Pin Function bit (except in MS and HS modes)<br>1 = OSC2 is a clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| POSCMD<1:0> | Primary Oscillator Mode Select bits         11 = Primary Oscillator is disabled         10 = HS Crystal Oscillator mode (10 MHz-32 MHz)         01 = MS Crystal Oscillator mode (3 MHz-10 MHz)         00 = EC (External Clock) mode (DC-32 MHz)                                                                                                                                                                    |  |  |  |  |  |  |

| FWDTEN      | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN bit in the RCON register will have no effect)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                          |  |  |  |  |  |  |

| WINDIS      | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

## TABLE 23-4: dsPIC33F CONFIGURATION BITS DESCRIPTION

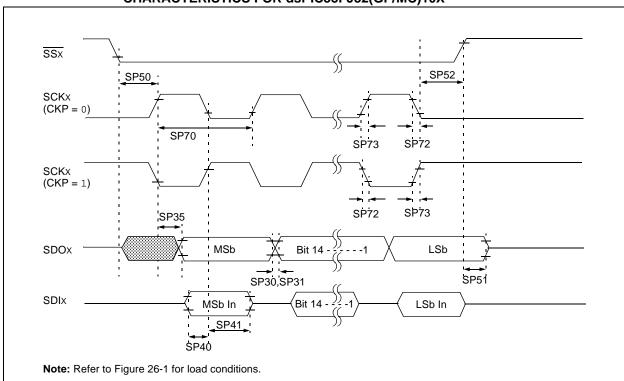

### FIGURE 26-26: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

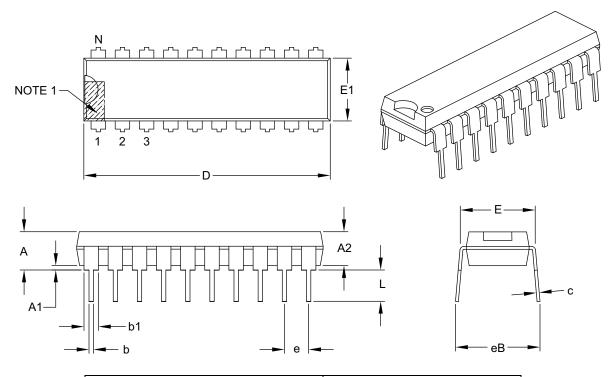

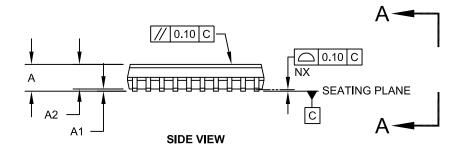

# 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units     |      |          | INCHES |  |  |

|----------------------------|-----------|------|----------|--------|--|--|

| Dimensio                   | on Limits | MIN  | NOM      | MAX    |  |  |

| Number of Pins             | Ν         |      | 20       |        |  |  |

| Pitch                      | е         |      | .100 BSC |        |  |  |

| Top to Seating Plane       | Α         | -    | -        | .210   |  |  |

| Molded Package Thickness   | A2        | .115 | .130     | .195   |  |  |

| Base to Seating Plane      | A1        | .015 | -        | -      |  |  |

| Shoulder to Shoulder Width | Е         | .300 | .310     | .325   |  |  |

| Molded Package Width       | E1        | .240 | .250     | .280   |  |  |

| Overall Length             | D         | .980 | 1.030    | 1.060  |  |  |

| Tip to Seating Plane       | L         | .115 | .130     | .150   |  |  |

| Lead Thickness             | С         | .008 | .010     | .015   |  |  |

| Upper Lead Width           | b1        | .045 | .060     | .070   |  |  |

| Lower Lead Width           | b         | .014 | .018     | .022   |  |  |

| Overall Row Spacing §      | eB        | -    | -        | .430   |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

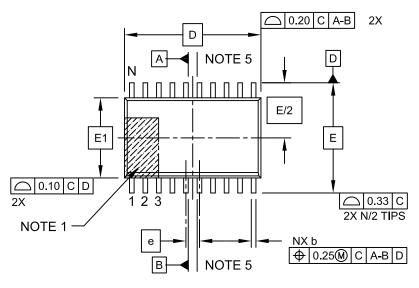

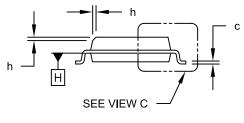

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

NOTES:

| Resets                            | 87     |

|-----------------------------------|--------|

| BOR (Brown-out Reset)             | 87     |

| BOR and Power-up Timer (PWRT)     | 92     |

| CM (Configuration Mismatch Reset) |        |

| Configuration Mismatch (CM)       |        |

| External (EXTR)                   |        |

| Illegal Condition                 |        |

| Illegal Opcode                    |        |

| Security                          | 93, 94 |

| Uninitialized W Register          |        |

| IOPUWR (Illegal Condition Reset)  | 87     |

| Illegal Opcode                    |        |

| Security                          |        |

| Uninitialized W Register          | 87     |

| MCLR (Master Clear Pin)           | 87     |

| Oscillator Delays                 |        |

| POR (Power-on Reset)              | 87     |

| Power-on Reset (POR)              | 92     |

| Software RESET Instruction (SWR)  | 93     |

| SWR (RESET Instruction)           |        |

| System                            |        |

| Cold Reset                        | 90     |

| Warm Reset                        | 90     |

| Trap Conflict                     | 93     |

| TRAPR (Trap Conflict Reset)       | 87     |

| Watchdog Timer Time-out (WDTO)    | 93     |

| WDTO (Watchdog Timer Reset)       | 87     |

| Revision History                  | 373    |

| RTCC                              |        |

| Control Registers                 | 245    |

| Module Registers                  | 244    |

| Register Mapping                  | 244    |

| e                                 |        |

#### S

| Serial Peripheral Interface (SPI)     | 197 |

|---------------------------------------|-----|

| Control Registers                     | 199 |

| Helpful Tips                          | 198 |

| Resources                             | 198 |

| Software Stack Pointer, Frame Pointer |     |

| CALL Stack Frame                      | 73  |

| Special Features                      |     |

| Code Protection                       |     |

| Flexible Configuration                |     |

| In-Circuit Emulation                  |     |

| In-Circuit Serial Programming (ICSP)  |     |

| Watchdog Timer (WDT)                  |     |

# Т

| I2Cx Bus Start/Stop Bits (Master Mode)              |       |

|-----------------------------------------------------|-------|

| I2Cx Bus Start/Stop Bits (Slave Mode)               | . 330 |

| Input Capture x (ICx)                               | . 301 |

| Motor Control PWMx                                  | . 303 |

| Motor Control PWMx Fault                            | . 303 |

| OCx/PWMx                                            | . 302 |

| Output Compare x (OCx)                              | . 302 |

| Output Compare x Operation                          |       |

| Reset, Watchdog Timer, Oscillator Start-up Timer    | -     |

| and Power-up Timer                                  | 298   |

| SPIx Master Mode (Full-Duplex, CKE = 0, CKP = $x_1$ |       |

| SMP = 1) for dsPIC33FJ16(GP/MC)10X                  |       |

| SPIx Master Mode (Full-Duplex, CKE = 0, CKP = $x_i$ |       |

| SMP = 1) for dsPIC33FJ32(GP/MC)10X                  |       |

| SPIx Master Mode (Full-Duplex, CKE = 1, CKP = $x_1$ |       |

| SMP = 1) for dsPIC33FJ16(GP/MC)10X                  |       |

| SPIx Master Mode (Full-Duplex, CKE = 1, CKP = $x_1$ |       |

| SMP = 1) for dsPIC33FJ32(GP/MC)10X                  |       |

| SPIx Master Transmit Mode (Half-Duplex, CKE = 0)    |       |

|                                                     |       |

| for dsPIC33FJ16(GP/MC)10X                           |       |

| SPIx Master Transmit Mode (Half-Duplex, CKE = 0)    |       |

| for dsPIC33FJ32(GP/MC)10X                           |       |

| SPIx Master Transmit Mode (Half-Duplex, CKE = 1)    |       |

| for dsPIC33FJ16(GP/MC)10X                           |       |

| SPIx Master Transmit Mode (Half-Duplex, CKE = 1)    |       |

| for dsPIC33FJ32(GP/MC)10X                           | . 317 |

| SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 0,     |       |

| SMP = 0) for dsPIC33FJ16(GP/MC)10X                  | . 314 |

| SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 0,     |       |

| SMP = 0) for dsPIC33FJ32(GP/MC)10X                  | . 326 |

| SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 1,     |       |

| SMP = 0) for dsPIC33FJ16(GP/MC)10X                  | . 312 |

| SPIx Slave Mode (Full-Duplex, CKE = 0, CKP = 1,     |       |

| SMP = 0) for dsPIC33FJ32(GP/MC)10X                  | . 324 |

| SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 0,     |       |

| SMP = 0) for dsPIC33FJ16(GP/MC)10X                  | . 308 |

| SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 0,     |       |

| SMP = 0) for dsPIC33FJ32(GP/MC)10X                  | . 320 |

| SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 1,     |       |

| SMP = 0) for dsPIC33FJ16(GP/MC)10X                  | . 310 |

| SPIx Slave Mode (Full-Duplex, CKE = 1, CKP = 1,     |       |

| SMP = 0) for dsPIC33FJ32(GP/MC)10X                  | . 322 |

| System Reset                                        | 91    |

| Timer1/2/3 External Clock                           | . 299 |

| Timing Requirements                                 |       |

| 10-Bit ADC Conversion                               | . 335 |

| Capacitive Loading on Output Pins                   | . 294 |

| CLKO and I/O                                        | 297   |

| External Clock                                      |       |

| I2Cx Bus Data (Master Mode)                         | . 329 |

| I2Cx Bus Data (Slave Mode)                          |       |

| Input Capture x (ICx)                               |       |

| Motor Control PWMx                                  |       |

| Output Compare x (OCx)                              |       |

| Reset, Watchdog Timer, Oscillator Start-up Timer,   |       |

| Power-up Timer and Brown-out Reset                  | 298   |

| Simple OCx/PWMx Mode                                |       |

| SPIx Master Mode (Full-Duplex, CKE = 0, CKP = $x_i$ |       |

| SMP = 1) for dsPIC33FJ16(GP/MC)10X                  |       |

| SPIx Master Mode (Full-Duplex, CKE = 0, CKP = $x_1$ |       |

| SMP = 1) for dsPIC33FJ32(GP/MC)10X                  |       |

| SPIx Master Mode (Full-Duplex, CKE = 1, CKP = $x_1$ |       |

| SMP = 1) for dsPIC33FJ16(GP/MC)10X                  |       |

| SPIx Master Mode (Full-Duplex, CKE = 1, CKP = $x_1$ |       |

| SMP = 1) for dsPIC33FJ32(GP/MC)10X                  |       |

|                                                     | . 510 |