Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 14x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc104-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

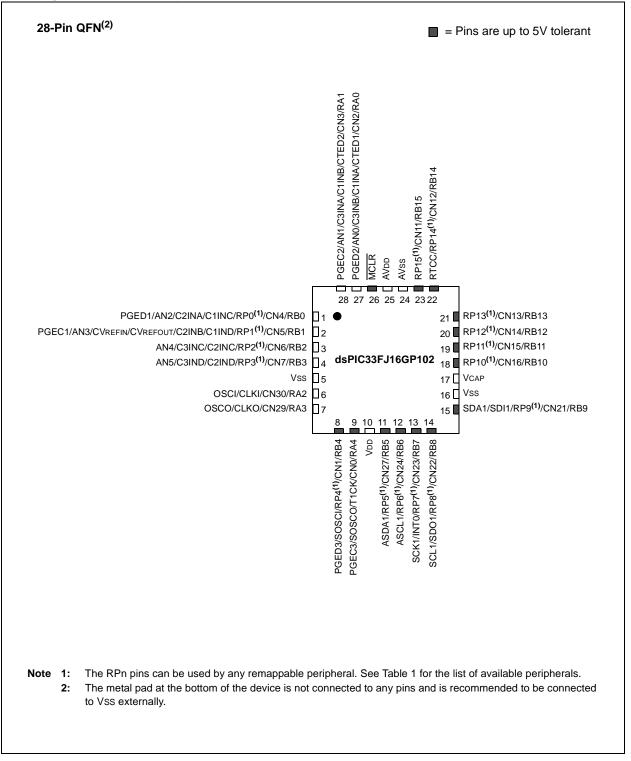

#### Pin Diagrams (Continued)

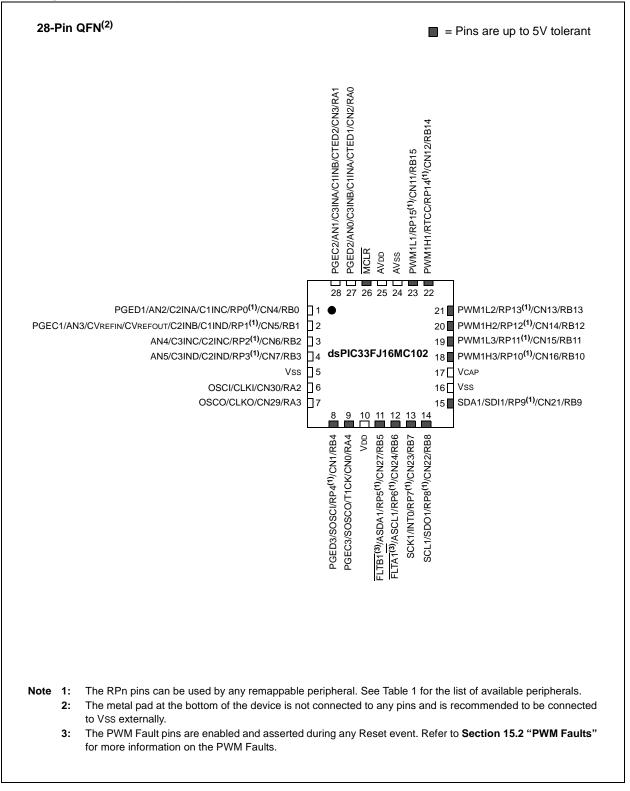

#### Pin Diagrams (Continued)

| U-0             | U-0                            | U-0                                   | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|-----------------|--------------------------------|---------------------------------------|-----------------|---------------------|------------------|------------------|-------|

| —               | —                              | _                                     | US              | EDT <sup>(1)</sup>  | DL2              | DL1              | DL0   |

| bit 15          |                                |                                       |                 |                     |                  |                  | bit   |

| R/W-0           | R/W-0                          | R/W-1                                 | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA            | SATB                           | SATDW                                 | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | R/W-0            | IF    |

| bit 7           | SAID                           | SAIDW                                 | ACCOAT          | IF L3. 7            | F3V              | RND              | bit   |

|                 |                                |                                       |                 |                     |                  |                  | Dit   |

| Legend:         |                                | C = Clearable                         | e bit           |                     |                  |                  |       |

| R = Readabl     | e bit                          | W = Writable                          | bit             | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle | ared                           | 'x = Bit is unk                       | nown            | U = Unimple         | mented bit, read | d as '0'         |       |

| bit 15-13       | Unimplemen                     | ted: Read as '                        | 0'              |                     |                  |                  |       |

| bit 12          | -                              | tiply Unsigned                        |                 | ol bit              |                  |                  |       |

|                 |                                | ne multiplies a                       | •               |                     |                  |                  |       |

|                 | 0 = DSP engi                   | ne multiplies a                       | ire signed      |                     |                  |                  |       |

| bit 11          |                                | Loop Termina                          |                 |                     |                  |                  |       |

|                 | 1 = Terminate<br>0 = No effect | es executing Do                       | o loop at the e | nd of current lo    | oop iteration    |                  |       |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                          | Level Status b  | its                 |                  |                  |       |

|                 | 111 <b>= 7</b> DO <b>lo</b>    | ops are active                        |                 |                     |                  |                  |       |

|                 | •                              |                                       |                 |                     |                  |                  |       |

|                 | •<br>001 = 1 DO lo             | on is activo                          |                 |                     |                  |                  |       |

|                 |                                | ops are active                        |                 |                     |                  |                  |       |

| bit 7           | SATA: ACCA                     | Saturation En                         | able bit        |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

|                 |                                | itor A saturatio                      |                 |                     |                  |                  |       |

| bit 6           |                                | Saturation En                         |                 |                     |                  |                  |       |

|                 |                                | tor B saturatio                       |                 |                     |                  |                  |       |

| bit 5           |                                |                                       |                 | ine Saturation      | Enable bit       |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

|                 |                                | ce write satura                       |                 |                     |                  |                  |       |

| bit 4           | ACCSAT: Acc                    | cumulator Satu                        | uration Mode S  | Select bit          |                  |                  |       |

|                 |                                | ration (super s                       |                 |                     |                  |                  |       |

| L:1 0           |                                | ration (normal                        | ,               | ··· (2)             |                  |                  |       |

| bit 3           |                                | terrupt Priority<br>rrupt Priority Le |                 |                     |                  |                  |       |

|                 |                                | rupt Priority Le                      | •               |                     |                  |                  |       |

| bit 2           |                                |                                       |                 | ace Enable bit      |                  |                  |       |

|                 |                                | space is visible                      |                 |                     |                  |                  |       |

|                 | -                              | space is not vi                       |                 | pace                |                  |                  |       |

| bit 1           |                                | ng Mode Sele                          |                 |                     |                  |                  |       |

|                 |                                | onventional) ro<br>(convergent)       |                 |                     |                  |                  |       |

| bit 0           | IF: Integer or                 | Fractional Mul                        | tiplier Mode S  | elect bit           |                  |                  |       |

|                 | -                              |                                       |                 | iply operations     |                  |                  |       |

|                 | 0 = Fractional                 | l mode is enab                        | led for DSP m   | nultiply operation  | ons              |                  |       |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

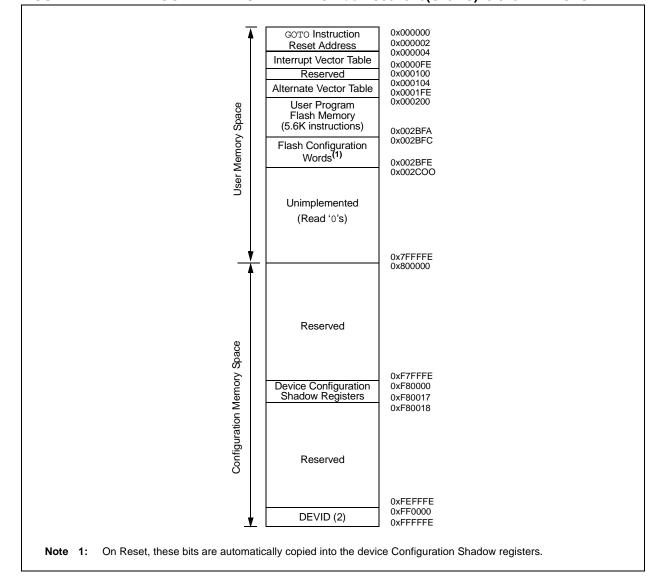

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Data Memory" (DS70202) and "Program Memory" (DS70203) in the "dsPIC33/PIC24 Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

The device architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory maps for the dsPIC33FJ16(GP/MC)101/ 102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices are shown in Figure 4-1 and Figure 4-2.

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJ16(GP/MC)101/102 DEVICES

|               |                                    |                                     | 0            |                 |                  |                |       |  |  |  |

|---------------|------------------------------------|-------------------------------------|--------------|-----------------|------------------|----------------|-------|--|--|--|

| R/W-0         | R-0                                | U-0                                 | U-0          | U-0             | U-0              | U-0            | U-0   |  |  |  |

| ALTIVT        | DISI                               | —                                   | —            | —               | —                | —              | —     |  |  |  |

| bit 15        |                                    |                                     |              |                 |                  |                | bit 8 |  |  |  |

|               |                                    |                                     |              |                 |                  |                |       |  |  |  |

| U-0           | U-0                                | U-0                                 | U-0          | U-0             | R/W-0            | R/W-0          | R/W-0 |  |  |  |

|               | INT2EP INT1EP INT                  |                                     |              |                 |                  |                |       |  |  |  |

| bit 7         |                                    |                                     |              |                 |                  |                | bit ( |  |  |  |

|               |                                    |                                     |              |                 |                  |                |       |  |  |  |

| Legend:       |                                    |                                     |              |                 |                  |                |       |  |  |  |

| R = Readabl   | e bit                              | W = Writable                        | bit          | U = Unimple     | emented bit, rea | d as '0'       |       |  |  |  |

| -n = Value at | POR                                | '1' = Bit is set                    |              | '0' = Bit is cl | eared            | x = Bit is unk | nown  |  |  |  |

|               |                                    |                                     |              |                 |                  |                |       |  |  |  |

| bit 15        |                                    | ble Alternate In                    | •            |                 |                  |                |       |  |  |  |

|               |                                    | ernate Interrupt<br>ndard Interrupt |              |                 |                  |                |       |  |  |  |

| bit 14        |                                    | nuard interrupt                     |              |                 |                  |                |       |  |  |  |

|               |                                    | truction is activ                   |              |                 |                  |                |       |  |  |  |

|               | 0 = DISI instruction is not active |                                     |              |                 |                  |                |       |  |  |  |

| bit 13-3      | Unimplemen                         | nted: Read as '                     | 0'           |                 |                  |                |       |  |  |  |

| bit 2         | INT2EP: Exte                       | ernal Interrupt 2                   | 2 Edge Detec | t Polarity Sele | ct bit           |                |       |  |  |  |

|               | •                                  | on negative ed                      | •            |                 |                  |                |       |  |  |  |

|               | 0 = Interrupt                      | on positive edg                     | e            |                 |                  |                |       |  |  |  |

| bit 1         |                                    | ernal Interrupt 1                   | 0            | t Polarity Sele | ct bit           |                |       |  |  |  |

|               |                                    | on negative ed                      |              |                 |                  |                |       |  |  |  |

| <b>h</b> it 0 | -                                  | on positive edg                     |              | t Delevity Cele | -4 h i4          |                |       |  |  |  |

| bit 0         |                                    | ernal Interrupt (                   | 0            | a Polarity Sele |                  |                |       |  |  |  |

|               |                                    | on negative ed<br>on positive edg   |              |                 |                  |                |       |  |  |  |

|               |                                    | poolato oug                         | -            |                 |                  |                |       |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 |                 |                                        |                   |                  |                  |                 |        |  |  |  |

|------------------------------------------------------|-----------------|----------------------------------------|-------------------|------------------|------------------|-----------------|--------|--|--|--|

| U-0                                                  | U-0             | R/W-0                                  | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| —                                                    | —               | AD1IF                                  | U1TXIF            | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |  |  |  |

| pit 15                                               |                 |                                        |                   |                  |                  |                 | bi     |  |  |  |

| R/W-0                                                | R/W-0           | R/W-0                                  | U-0               | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| T2IF                                                 | OC2IF           | IC2IF                                  | _                 | T1IF             | OC1IF            | IC1IF           | INTOIF |  |  |  |

| bit 7                                                |                 |                                        |                   |                  |                  |                 | bi     |  |  |  |

|                                                      |                 |                                        |                   |                  |                  |                 |        |  |  |  |

| Legend:                                              | - h:4           |                                        | h.:4              |                  |                  |                 |        |  |  |  |

| R = Readable<br>-n = Value at                        |                 | W = Writable<br>'1' = Bit is se        |                   | 0 = Unimplem     | nented bit, read |                 |        |  |  |  |

| -n = value at                                        | POR             | I = DILIS SE                           | l                 |                  | areu             | x = Bit is unkn | own    |  |  |  |

| bit 15-14                                            | Unimplemen      | ted: Read as                           | 'O'               |                  |                  |                 |        |  |  |  |

| bit 13                                               | AD1IF: ADC1     | Conversion (                           | Complete Interi   | rupt Flag Status | s bit            |                 |        |  |  |  |

|                                                      |                 | request has or                         |                   |                  |                  |                 |        |  |  |  |

|                                                      | -               | request has no                         |                   | <b>.</b>         |                  |                 |        |  |  |  |

| bit 12                                               |                 |                                        | er Interrupt Flag | g Status bit     |                  |                 |        |  |  |  |

|                                                      | •               | request has or<br>request has no       |                   |                  |                  |                 |        |  |  |  |

| bit 11                                               | -               | -                                      | nterrupt Flag S   | Status bit       |                  |                 |        |  |  |  |

|                                                      |                 | request has or                         |                   |                  |                  |                 |        |  |  |  |

|                                                      | •               | 0 = Interrupt request has not occurred |                   |                  |                  |                 |        |  |  |  |

| bit 10                                               |                 | -                                      | ot Flag Status k  | bit              |                  |                 |        |  |  |  |

|                                                      | •               | request has oc<br>request has no       |                   |                  |                  |                 |        |  |  |  |

| bit 9                                                | -               | -                                      | pt Flag Status    | bit              |                  |                 |        |  |  |  |

|                                                      |                 | request has or                         |                   |                  |                  |                 |        |  |  |  |

|                                                      | -               | request has no                         |                   |                  |                  |                 |        |  |  |  |

| bit 8                                                |                 | Interrupt Flag                         |                   |                  |                  |                 |        |  |  |  |

|                                                      |                 | request has or<br>request has no       |                   |                  |                  |                 |        |  |  |  |

| bit 7                                                | •               | Interrupt Flag                         |                   |                  |                  |                 |        |  |  |  |

|                                                      |                 | request has oc                         |                   |                  |                  |                 |        |  |  |  |

|                                                      | 0 = Interrupt i | request has no                         | ot occurred       |                  |                  |                 |        |  |  |  |

| bit 6                                                | -               | -                                      |                   | upt Flag Status  | bit              |                 |        |  |  |  |

|                                                      | •               | request has oc<br>request has no       |                   |                  |                  |                 |        |  |  |  |

| bit 5                                                | -               | -                                      | nel 2 Interrupt F | -lag Status bit  |                  |                 |        |  |  |  |

|                                                      | -               | request has or                         | -                 | <u>.</u>         |                  |                 |        |  |  |  |

|                                                      |                 | request has no                         |                   |                  |                  |                 |        |  |  |  |

| bit 4                                                | -               | ted: Read as                           |                   |                  |                  |                 |        |  |  |  |

| bit 3                                                | T1IF: Timer1    | Interrupt Flag                         | Status bit        |                  |                  |                 |        |  |  |  |

|                                                      |                 | request has or                         |                   |                  |                  |                 |        |  |  |  |

#### -י חוור - - -• •

| U-0                            | R/W-1                                                                                                                          | R/W-0                                | R/W-0             | U-0             | R/W-1             | R/W-0           | R/W-0          |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|-----------------|-------------------|-----------------|----------------|--|--|--|--|

| —                              | U1RXIP2                                                                                                                        | U1RXIP1                              | U1RXIP0           | —               | SPI1IP2           | SPI1IP1         | SPI1IP0        |  |  |  |  |

| bit 15                         |                                                                                                                                |                                      |                   |                 |                   |                 | bit            |  |  |  |  |

|                                | D 444                                                                                                                          | DAMA                                 | DAMA              |                 | D 44/ 4           | DAMA            | DAMO           |  |  |  |  |

| U-0                            | R/W-1<br>SPI1EIP2                                                                                                              | R/W-0<br>SPI1EIP1                    | R/W-0<br>SPI1EIP0 | U-0             | R/W-1<br>T3IP2    | R/W-0<br>T3IP1  | R/W-0<br>T3IP0 |  |  |  |  |

| bit 7                          | OTTEN 2                                                                                                                        | OFFICIENT                            | OFFICIENT         |                 | 10112             | 1011 1          | bit            |  |  |  |  |

|                                |                                                                                                                                |                                      |                   |                 |                   |                 | _              |  |  |  |  |

| <b>Legend:</b><br>R = Readable | hit.                                                                                                                           |                                      | <b>b</b> :+       |                 | mantad hit raa    |                 |                |  |  |  |  |

|                                |                                                                                                                                | W = Writable                         |                   | -               | emented bit, read |                 |                |  |  |  |  |

| -n = Value at                  | POR                                                                                                                            | '1' = Bit is set                     |                   | '0' = Bit is cl | eared             | x = Bit is unkı | lown           |  |  |  |  |

| bit 15                         | Unimplemen                                                                                                                     | ted: Read as '                       | 0'                |                 |                   |                 |                |  |  |  |  |

| bit 14-12                      | -                                                                                                                              |                                      |                   | Priority bits   |                   |                 |                |  |  |  |  |

|                                | <b>U1RXIP&lt;2:0&gt;:</b> UART1 Receiver Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              |                                      | 3                 | 5               |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •<br>001 = Interru                                                                                                             | nt in Priority 1                     |                   |                 |                   |                 |                |  |  |  |  |

|                                |                                                                                                                                |                                      | abled             |                 |                   |                 |                |  |  |  |  |

| bit 11                         | 000 = Interrupt source is disabled<br>Unimplemented: Read as '0'                                                               |                                      |                   |                 |                   |                 |                |  |  |  |  |

| bit 10-8                       | SPI1IP<2:0>: SPI1 Event Interrupt Priority bits                                                                                |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                     |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              | pt le 1 lienty 1 l                   | (geet pe          | .,              |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                            |                                      |                   |                 |                   |                 |                |  |  |  |  |

| bit 7                          |                                                                                                                                | ited: Read as '                      |                   |                 |                   |                 |                |  |  |  |  |

| bit 6-4                        | -                                                                                                                              | >: SPI1 Error I                      |                   | ty hite         |                   |                 |                |  |  |  |  |

|                                |                                                                                                                                | pt is Priority 7                     | •                 |                 |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              | pt lo i nonty i                      | (ingricot priorit | ly interrupty   |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | 001 = Interru                                                                                                                  | pt is Priority 1<br>pt source is dis | abled             |                 |                   |                 |                |  |  |  |  |

| bit 3                          |                                                                                                                                | ited: Read as '                      |                   |                 |                   |                 |                |  |  |  |  |

| bit 2-0                        | -                                                                                                                              | imer3 Interrupt                      |                   |                 |                   |                 |                |  |  |  |  |

| Dit 2-0                        |                                                                                                                                | pt is Priority 7                     | -                 | ty interrupt)   |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              | prist nonty /                        | (ingriest priorit | ly interrupt)   |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | •                                                                                                                              |                                      |                   |                 |                   |                 |                |  |  |  |  |

|                                | 001 = Interru                                                                                                                  | nt in Driarity 1                     |                   |                 |                   |                 |                |  |  |  |  |

### **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 3 | CF: Clock Fail Detect bit (read/clear by application)                                                     |

|-------|-----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = FSCM has detected a clock failure</li><li>0 = FSCM has not detected a clock failure</li></ul> |

| bit 2 | Unimplemented: Read as '0'                                                                                |

| bit 1 | LPOSCEN: Secondary (LP) Oscillator Enable bit                                                             |

|       | <ul><li>1 = Enables secondary oscillator</li><li>0 = Disables secondary oscillator</li></ul>              |

| bit 0 | <b>OSWEN:</b> Oscillator Switch Enable bit                                                                |

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to "Oscillator (Part VI)" (DS70644) in the "dsPIC33/PIC24 Family Reference Manual" for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

| REGISTE            | R 12-4: 15CO                         | N: IIMER5 C                                                                 | UNIKOL RE             | GISTER                      |                 |                    |             |  |  |  |  |

|--------------------|--------------------------------------|-----------------------------------------------------------------------------|-----------------------|-----------------------------|-----------------|--------------------|-------------|--|--|--|--|

| R/W-0              | U-0                                  | R/W-0                                                                       | U-0                   | U-0                         | U-0             | U-0                | U-0         |  |  |  |  |

| TON <sup>(3)</sup> | —                                    | TSIDL <sup>(2)</sup>                                                        | —                     | —                           | —               | —                  | —           |  |  |  |  |

| bit 15             |                                      |                                                                             |                       |                             |                 |                    | bit 8       |  |  |  |  |

|                    |                                      |                                                                             |                       |                             |                 |                    |             |  |  |  |  |

| U-0                | R/W-0                                | R/W-0                                                                       | R/W-0                 | U-0                         | U-0             | R/W-0              | U-0         |  |  |  |  |

| —                  | TGATE <sup>(3)</sup>                 | TCKPS1 <sup>(3)</sup>                                                       | TCKPS0 <sup>(3)</sup> | —                           | —               | TCS <sup>(3)</sup> | —           |  |  |  |  |

| bit 7              |                                      |                                                                             |                       |                             |                 |                    | bit 0       |  |  |  |  |

| 1                  |                                      |                                                                             |                       |                             |                 |                    |             |  |  |  |  |

| Legend:            | b.1. b.34                            |                                                                             | L.14                  | II II.                      |                 | -l (Q)             |             |  |  |  |  |

| R = Reada          |                                      | W = Writable                                                                |                       | -                           | mented bit, rea |                    |             |  |  |  |  |

| -n = Value         | at POR                               | '1' = Bit is set                                                            |                       | '0' = Bit is cle            | eared           | x = Bit is unkn    | own         |  |  |  |  |

| bit 15             | TON: Timer5                          | On hit(3)                                                                   |                       |                             |                 |                    |             |  |  |  |  |

| bit 10             | 1 = Starts 16-                       |                                                                             |                       |                             |                 |                    |             |  |  |  |  |

|                    | 0 = Stops 16-                        |                                                                             |                       |                             |                 |                    |             |  |  |  |  |

| bit 14             | Unimplemen                           | Unimplemented: Read as '0'                                                  |                       |                             |                 |                    |             |  |  |  |  |

| bit 13             | TSIDL: Time                          | TSIDL: Timer5 Stop in Idle Mode bit <sup>(2)</sup>                          |                       |                             |                 |                    |             |  |  |  |  |

|                    |                                      | ues timer opera                                                             |                       |                             | e mode          |                    |             |  |  |  |  |

|                    | 0 = Continue                         | s timer operatio                                                            | on in Idle mode       | 9                           |                 |                    |             |  |  |  |  |

| bit 12-7           | Unimplemen                           | nted: Read as '                                                             | 0'                    | (-)                         |                 |                    |             |  |  |  |  |

| bit 6              |                                      | er5 Gated Time                                                              | Accumulation          | n Enable bit <sup>(3)</sup> |                 |                    |             |  |  |  |  |

|                    | <u>When TCS =</u><br>This bit is ign |                                                                             |                       |                             |                 |                    |             |  |  |  |  |

|                    | •                                    |                                                                             |                       |                             |                 |                    |             |  |  |  |  |

|                    |                                      | $\frac{\text{When TCS} = 0}{1 = \text{Gated time accumulation is enabled}}$ |                       |                             |                 |                    |             |  |  |  |  |

|                    | 0 = Gated tim                        | ne accumulatio                                                              | n is disabled         |                             |                 |                    |             |  |  |  |  |

| bit 5-4            | TCKPS<1:0>                           | : Timer5 Input                                                              | Clock Prescal         | e Select bits <sup>(3</sup> | )               |                    |             |  |  |  |  |

|                    |                                      | rescale value                                                               |                       |                             |                 |                    |             |  |  |  |  |

|                    | 10 = 1:64 pre                        |                                                                             |                       |                             |                 |                    |             |  |  |  |  |

|                    | 01 = 1:8 pres<br>00 = 1:1 pres       |                                                                             |                       |                             |                 |                    |             |  |  |  |  |

| bit 3-2            | -                                    | nted: Read as '                                                             | 0'                    |                             |                 |                    |             |  |  |  |  |

| bit 1              | -                                    | Clock Source                                                                |                       |                             |                 |                    |             |  |  |  |  |

|                    |                                      | clock from T5C                                                              |                       |                             |                 |                    |             |  |  |  |  |

|                    |                                      | lock (Fosc/2)                                                               |                       |                             |                 |                    |             |  |  |  |  |

| bit 0              | Unimplemen                           | nted: Read as '                                                             | 0'                    |                             |                 |                    |             |  |  |  |  |

| Note 1:            | This register is ava                 | ailable in dsPIC                                                            | 33FJ32(GP/N           | IC)10X device               | es only.        |                    |             |  |  |  |  |

|                    | When 32-bit timer                    |                                                                             |                       | -                           | -               | ster (T4CON<3>)    | , the TSIDL |  |  |  |  |

|                    | hit must be cleared                  | •                                                                           | •                     | ,                           | Ŭ               | . ,                |             |  |  |  |  |

#### REGISTER 12-4: T5CON: TIMER5 CONTROL REGISTER<sup>(1)</sup>

2: When 32-bit timer operation is enabled (132 = 1) in the Timer4 Control register (14CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

**3:** When the 32-bit timer operation is enabled (T32 = 1) in the Timer4 Control register (T4CON<3>), these bits have no effect.

| U-0          | U-0               | U-0                        | U-0           | R/W-0                                | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|--------------|-------------------|----------------------------|---------------|--------------------------------------|-----------------|-----------------|-------|--|--|--|

| —            | —                 | —                          |               | SEVOPS<3:0>                          |                 |                 |       |  |  |  |

| bit 15       |                   |                            |               |                                      |                 |                 | bit 8 |  |  |  |

|              |                   |                            |               |                                      |                 |                 |       |  |  |  |

| U-0          | U-0               | U-0                        | U-0           | U-0                                  | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| _            | —                 | —                          | _             | —                                    | IUE             | OSYNC           | UDIS  |  |  |  |

| bit 7        | ·                 |                            |               |                                      |                 |                 | bit 0 |  |  |  |

|              |                   |                            |               |                                      |                 |                 |       |  |  |  |

| Legend:      |                   |                            |               |                                      |                 |                 |       |  |  |  |

| R = Readab   | le bit            | W = Writable I             | oit           | U = Unimplen                         | nented bit, rea | d as '0'        |       |  |  |  |

| -n = Value a | t POR             | '1' = Bit is set           |               | '0' = Bit is cle                     | ared            | x = Bit is unkn | own   |  |  |  |

|              |                   |                            |               |                                      |                 |                 |       |  |  |  |

| bit 15-12    | Unimplemen        | Unimplemented: Read as '0' |               |                                      |                 |                 |       |  |  |  |

| bit 11-8     | SEVOPS<3:0        | <b>0&gt;:</b> PWMx Spec    | ial Event Tri | gger Output Pos                      | stscale Select  | oits            |       |  |  |  |

|              | 1111 = 1:16       | postscale                  |               |                                      |                 |                 |       |  |  |  |

|              | •                 |                            |               |                                      |                 |                 |       |  |  |  |

|              | •                 |                            |               |                                      |                 |                 |       |  |  |  |

|              | •<br>0001 = 1:2 p | netecale                   |               |                                      |                 |                 |       |  |  |  |

|              | 0000 = 1.2 p      |                            |               |                                      |                 |                 |       |  |  |  |

| bit 7-3      | •                 | ted: Read as 'd            | )'            |                                      |                 |                 |       |  |  |  |

| bit 2        | IUE: Immedia      | ate Update Enal            | ole bit       |                                      |                 |                 |       |  |  |  |

|              |                   | to the active Px           |               | are immediate                        |                 |                 |       |  |  |  |

|              | 0 = Updates       | to the active Px           | DC registers  | are synchroniz                       | ed to the PWN   | lx time base    |       |  |  |  |

| bit 1        | OSYNC: Out        | put Override Sy            | nchronizatio  | n bit                                |                 |                 |       |  |  |  |

|              |                   |                            |               |                                      |                 | he PWMx time b  | ase   |  |  |  |

|              | •                 |                            |               | register occur o                     | on the next TC  | / boundary      |       |  |  |  |

| bit 0        |                   | Update Disable             |               | <b>5</b> <i>4</i>                    |                 |                 |       |  |  |  |

|              |                   |                            |               | Buffer registers<br>Buffer registers |                 |                 |       |  |  |  |

|              | 0 – Opuales       |                            |               | Duilei registers                     |                 |                 |       |  |  |  |

#### REGISTER 15-6: PWMxCON2: PWMx CONTROL REGISTER 2

| REGISTER            | 16-2: SPIXC                              | ON1: SPIx C                                   | ONTROL RE            | EGISTER 1                              |                      |                                       |                      |  |  |  |

|---------------------|------------------------------------------|-----------------------------------------------|----------------------|----------------------------------------|----------------------|---------------------------------------|----------------------|--|--|--|

| U-0                 | U-0                                      | U-0                                           | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                                 | R/W-0                |  |  |  |

| _                   | —                                        | —                                             | DISSCK               | DISSDO                                 | MODE16               | SMP                                   | CKE <sup>(1)</sup>   |  |  |  |

| bit 15              |                                          |                                               |                      |                                        |                      |                                       | bit 8                |  |  |  |

| R/W-0               | R/W-0                                    | R/W-0                                         | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                                 | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                      | MSTEN                                         | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup>                  | PPRE0 <sup>(3)</sup> |  |  |  |

| bit 7               |                                          | l                                             | 1                    | 1                                      |                      |                                       | bit (                |  |  |  |

| Legend:             |                                          |                                               |                      |                                        |                      |                                       |                      |  |  |  |

| R = Readab          | le bit                                   | W = Writable                                  | bit                  | U = Unimplen                           | nented bit, read     | l as '0'                              |                      |  |  |  |

| -n = Value a        | t POR                                    | '1' = Bit is set                              |                      | '0' = Bit is cle                       | ared                 | x = Bit is unkr                       | nown                 |  |  |  |

| bit 15-13           | Unimplemen                               | ted: Read as '                                | 0'                   |                                        |                      |                                       |                      |  |  |  |

| bit 12              | DISSCK: Disa                             | able SCKx pin                                 | bit (SPI Maste       | r modes only)                          |                      |                                       |                      |  |  |  |

|                     |                                          | PI clock is disa                              | •                    | tions as I/O                           |                      |                                       |                      |  |  |  |

|                     |                                          | PI clock is ena                               |                      |                                        |                      |                                       |                      |  |  |  |

| bit 11              |                                          | able SDOx pin                                 |                      |                                        |                      |                                       |                      |  |  |  |

|                     |                                          | is not used by is controlled b                |                      | oin functions as                       | s I/O                |                                       |                      |  |  |  |

| pit 10              | -                                        | ord/Byte Comm                                 | -                    | ect bit                                |                      |                                       |                      |  |  |  |

|                     | 1 = Communication is word-wide (16 bits) |                                               |                      |                                        |                      |                                       |                      |  |  |  |

|                     | 0 = Communi                              | cation is byte-                               | wide (8 bits)        |                                        |                      |                                       |                      |  |  |  |

| bit 9               | SMP: SPIx D                              | SMP: SPIx Data Input Sample Phase bit         |                      |                                        |                      |                                       |                      |  |  |  |

|                     |                                          | <u>:</u><br>a sampled at er<br>a sampled at m |                      |                                        |                      |                                       |                      |  |  |  |

|                     | Slave mode:                              | -                                             |                      | n Slave mode.                          |                      |                                       |                      |  |  |  |

| bit 8               | CKE: Clock E                             | dge Select bit                                | (1)                  |                                        |                      |                                       |                      |  |  |  |

|                     |                                          |                                               |                      |                                        |                      | lle clock state (<br>ve clock state ( |                      |  |  |  |

| bit 7               | SSEN: SPIX S                             | Slave Select E                                | nable bit (Slav      | e mode) <sup>(2)</sup>                 |                      |                                       |                      |  |  |  |

|                     |                                          | s used for Slav<br>s not used by th           |                      | is controlled b                        | by port function     |                                       |                      |  |  |  |

| oit 6               | CKP: Clock F                             | Polarity Select I                             | oit                  |                                        |                      |                                       |                      |  |  |  |

|                     |                                          |                                               |                      | ve state is a lov<br>e state is a high |                      |                                       |                      |  |  |  |

| bit 5               | MSTEN: Mas                               | ter Mode Enab                                 | ole bit              |                                        |                      |                                       |                      |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo             |                                               |                      |                                        |                      |                                       |                      |  |  |  |

|                     | he CKE bit is not<br>FRMEN = 1).         | used in the Fra                               | amed SPI moo         | des. Program ti                        | his bit to '0' for   | the Framed SP                         | 'l modes             |  |  |  |

|                     | his bit must be cl                       |                                               |                      |                                        |                      |                                       |                      |  |  |  |

| 3: D                | o not set both pri                       | mary and seco                                 | ondary prescal       | ers to a value o                       | of 1:1.              |                                       |                      |  |  |  |

### REGISTER 16-2: SPIxCON1: SPIx CONTROL REGISTER 1

#### REGISTER 20-2: CMxCON: COMPARATOR x CONTROL REGISTER (CONTINUED)

- bit 4 **CREF:** Comparator x Reference Select bit (VIN+ input)

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to CxINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator x Channel Select bits

- 11 = VIN- input of comparator connects to INTREF

- 10 = VIN- input of comparator connects to CXIND pin

- 01 = VIN- input of comparator connects to CxINC pin

- ${\tt 00}$  = VIN- input of comparator connects to CxINB pin

| U-0           | U-0                                                                                                                                                 | U-0                                                                                                 | U-0                  | U-0                                                                          | U-0             | U-0    | U-0    |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------|-----------------|--------|--------|--|--|--|--|--|

| -             |                                                                                                                                                     | _                                                                                                   | _                    | -                                                                            | _               | -      | -      |  |  |  |  |  |

| bit 15        |                                                                                                                                                     |                                                                                                     |                      |                                                                              |                 |        | bit 8  |  |  |  |  |  |

|               |                                                                                                                                                     |                                                                                                     |                      |                                                                              |                 |        |        |  |  |  |  |  |

| U-0           | R/W-0                                                                                                                                               | R/W-0                                                                                               | R/W-0                | R/W-0                                                                        | R/W-0           | R/W-0  | R/W-0  |  |  |  |  |  |

|               | CFSEL2                                                                                                                                              | CFSEL1                                                                                              | CFSEL0               | CFLTREN                                                                      | CFDIV2          | CFDIV1 | CFDIV0 |  |  |  |  |  |

| bit 7         | bit 7 bit 0                                                                                                                                         |                                                                                                     |                      |                                                                              |                 |        |        |  |  |  |  |  |

| Legend:       |                                                                                                                                                     |                                                                                                     |                      |                                                                              |                 |        |        |  |  |  |  |  |

| R = Readabl   | e hit                                                                                                                                               | W = Writable                                                                                        | hit                  | II – I Inimplen                                                              | nented hit read | as 'O' |        |  |  |  |  |  |

| -n = Value at |                                                                                                                                                     | 1' = Bit is set                                                                                     |                      | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unknow |                 |        | าดพท   |  |  |  |  |  |

|               |                                                                                                                                                     |                                                                                                     |                      | 0 2.1.0 0.0.                                                                 |                 |        |        |  |  |  |  |  |

| bit 15-7      | Unimplemen                                                                                                                                          | ted: Read as '                                                                                      | 0'                   |                                                                              |                 |        |        |  |  |  |  |  |

| bit 6-4       | CFSEL<2:0>                                                                                                                                          | : Comparator I                                                                                      | -<br>ilter Input Clo | ock Select bits                                                              |                 |        |        |  |  |  |  |  |

|               | 111 = Reserved<br>110 = Reserved<br>101 = Timer3<br>100 = Timer2<br>011 = Reserved<br>010 = PWM Special Event Trigger<br>001 = Fosc<br>000 = Fcy    |                                                                                                     |                      |                                                                              |                 |        |        |  |  |  |  |  |

| bit 3         | CFLTREN: C<br>1 = Digital filte<br>0 = Digital filte                                                                                                |                                                                                                     | er Enable bit        |                                                                              |                 |        |        |  |  |  |  |  |

| bit 2-0       | CFDIV<2:0>:<br>111 = Clock [<br>110 = Clock [<br>101 = Clock [<br>100 = Clock [<br>011 = Clock [<br>010 = Clock [<br>001 = Clock [<br>000 = Clock [ | Divide 1:128<br>Divide 1:64<br>Divide 1:32<br>Divide 1:16<br>Divide 1:8<br>Divide 1:4<br>Divide 1:2 | ilter Clock Div      | ide Select bits                                                              |                 |        |        |  |  |  |  |  |

#### REGISTER 20-5: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

| REGISTER 2    | 22-2: CTMU                                                                                                          | JCON2: CTM                     | U CONTROL        | REGISTER                          | 2                |                 |          |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|-----------------------------------|------------------|-----------------|----------|--|--|--|

| R/W-0         | R/W-0                                                                                                               | R/W-0                          | R/W-0            | R/W-0                             | R/W-0            | R/W-0           | R/W-0    |  |  |  |

| EDG1MOD       | EDG1POL                                                                                                             | EDG1SEL3                       | EDG1SEL2         | EDG1SEL1                          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |

| bit 15        |                                                                                                                     |                                |                  |                                   |                  |                 | bit 8    |  |  |  |

|               |                                                                                                                     |                                |                  |                                   |                  |                 |          |  |  |  |

| R/W-0         | R/W-0                                                                                                               | R/W-0                          | R/W-0            | R/W-0                             | R/W-0            | U-0             | U-0      |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                             | EDG2SEL3                       | EDG2SEL2         | EDG2SEL1                          | EDG2SEL0         |                 | —        |  |  |  |

| bit 7         |                                                                                                                     |                                |                  |                                   |                  |                 | bit 0    |  |  |  |

| Legend:       |                                                                                                                     |                                |                  |                                   |                  |                 |          |  |  |  |

| R = Readable  | hit                                                                                                                 | W = Writable                   | hit              | II – Unimplem                     | nented bit, read | las 'N'         |          |  |  |  |

| -n = Value at |                                                                                                                     | 1' = Bit is set                | on               | $0^{\circ} = \text{Bit is clear}$ |                  | x = Bit is unkr |          |  |  |  |

|               |                                                                                                                     | 1 – Dit 13 3et                 |                  |                                   |                  |                 | IOWIT    |  |  |  |

| bit 15        | EDG1MOD: E                                                                                                          | Edge 1 Edge Sa                 | ampling Selecti  | ion bit                           |                  |                 |          |  |  |  |

|               |                                                                                                                     | edge-sensitive                 |                  |                                   |                  |                 |          |  |  |  |

|               | 0 = Edge 1 is                                                                                                       | level-sensitive                |                  |                                   |                  |                 |          |  |  |  |

| bit 14        |                                                                                                                     | dge 1 Polarity                 |                  |                                   |                  |                 |          |  |  |  |

|               |                                                                                                                     | programmed f                   |                  |                                   |                  |                 |          |  |  |  |

| bit 13-10     | •                                                                                                                   | programmed f                   | •                | •                                 |                  |                 |          |  |  |  |