Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 14x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

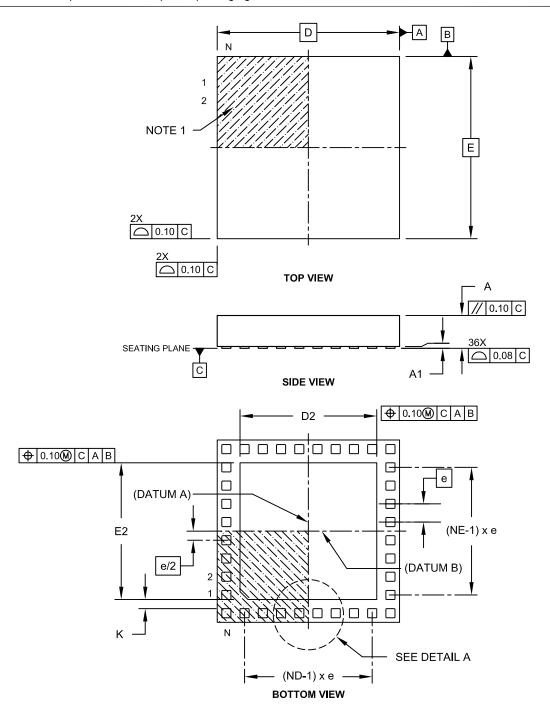

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc104-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-1: | CPU CORE REGISTER MAP (CONTINUE | D) |

|------------|---------------------------------|----|

|------------|---------------------------------|----|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8             | Bit 7        | Bit 6     | Bit 5   | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------------------|--------------|-----------|---------|--------|-------|-------|-------|-------|---------------|

| CORCON   | 0044        | —      | —      | _      | US     | EDT    | DL2    | DL1   | DL0               | SATA         | SATB      | SATDW   | ACCSAT | IPL3  | PSV   | RND   | IF    | 0020          |

| MODCON   | 0046        | XMODEN | YMODEN | _      | _      | BWM3   | BWM2   | BWM1  | BWM0              | YWM3         | YWM2      | YWM1    | YWM0   | XWM3  | XWM2  | XWM1  | XWM0  | 0000          |

| XMODSRT  | 0048        |        |        |        |        |        |        | 2     | (S<15:1>          |              |           |         |        |       |       |       | 0     | xxxx          |

| XMODEND  | 004A        |        |        |        |        |        |        | 2     | <e<15:1></e<15:1> |              |           |         |        |       |       |       | 1     | xxxx          |

| YMODSRT  | 004C        |        |        |        |        |        |        | Ŷ     | ∕S<15:1>          |              |           |         |        |       |       |       | 0     | xxxx          |

| YMODEND  | 004E        |        |        |        |        |        |        | Ŷ     | ΎE<15:1>          |              |           |         |        |       |       |       | 1     | xxxx          |

| XBREV    | 0050        | BREN   |        |        |        |        |        |       |                   | XB<14:0>     |           |         |        |       |       |       |       | xxxx          |

| DISICNT  | 0052        | _      | _      |        |        |        |        |       | Disabl            | e Interrupts | Counter R | egister |        |       |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

## 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM<3:0> bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the bit-reversed address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

**Note:** All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB<14:0> value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing will assume priority when active. For the X WAGU and Y AGU, Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### 6.10.2 UNINITIALIZED W REGISTER RESET

Any attempts to use the Uninitialized W register as an Address Pointer will reset the device. The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to.

### 6.10.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a Security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a Call, Jump, Computed Jump, Return, Return from Subroutine or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an interrupt or trap vector.

## 6.11 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the Reset.

| Note: | The status bits in the RCON register      |

|-------|-------------------------------------------|

|       | should be cleared after they are read so  |

|       | that the next RCON register value after a |

|       | device Reset will be meaningful.          |

Table 6-3 provides a summary of Reset flag bit operation.

### TABLE 6-3: RESET FLAG BIT OPERATION

| Flag Bit         | Set by:                                                                | Cleared by:                                         |

|------------------|------------------------------------------------------------------------|-----------------------------------------------------|

| TRAPR (RCON<15>) | Trap conflict event                                                    | POR, BOR                                            |

| IOPWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access or Security Reset | POR, BOR                                            |

| CM (RCON<9>)     | Configuration Mismatch                                                 | POR, BOR                                            |

| EXTR (RCON<7>)   | MCLR Reset                                                             | POR                                                 |

| SWR (RCON<6>)    | RESET instruction                                                      | POR, BOR                                            |

| WDTO (RCON<4>)   | WDT Time-out                                                           | PWRSAV instruction,<br>CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)  | PWRSAV #SLEEP instruction                                              | POR, BOR                                            |

| IDLE (RCON<2>)   | PWRSAV #IDLE instruction                                               | POR, BOR                                            |

| BOR (RCON<1>)    | POR, BOR                                                               | —                                                   |

| POR (RCON<0>)    | POR                                                                    |                                                     |

Note: All Reset flag bits can be set or cleared by user software.

## FIGURE 7-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 INTERRUPT VECTOR TABLE

| 1                                 |                                            | 7                    |                                                        |

|-----------------------------------|--------------------------------------------|----------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction                   | 0x000000             |                                                        |

|                                   | Reset – GOTO Address                       | 0x000002             |                                                        |

|                                   | Reserved                                   | 0x000004             |                                                        |

|                                   | Oscillator Fail Trap Vector                | _                    |                                                        |

|                                   | Address Error Trap Vector                  | _                    |                                                        |

|                                   | Stack Error Trap Vector                    | _                    |                                                        |

|                                   | Math Error Trap Vector                     | _                    |                                                        |

|                                   | Reserved                                   | -                    |                                                        |

|                                   | Reserved                                   | _                    |                                                        |

|                                   | Reserved<br>Interrupt Vector 0             | 0x000014             |                                                        |

|                                   | Interrupt Vector 1                         | 0,000014             |                                                        |

|                                   |                                            | -                    |                                                        |

|                                   | ~                                          |                      |                                                        |

|                                   | ~                                          | -                    |                                                        |

|                                   | Interrupt Vector 52                        | 0x00007C             | (4)                                                    |

|                                   | Interrupt Vector 53                        | 0x00007E             | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                        | 0x000080             |                                                        |

| iori                              | ~                                          |                      |                                                        |

| ā                                 | ~                                          |                      |                                                        |

| der                               | ~                                          |                      |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                       | 0x0000FC             |                                                        |

| ra                                | Interrupt Vector 117                       | 0x0000FE             |                                                        |

| atu                               | Reserved                                   | 0x000100             |                                                        |

| Z                                 | Reserved                                   | 0x000102             |                                                        |

| sing                              | Reserved                                   |                      |                                                        |

| eas                               | Oscillator Fail Trap Vector                |                      |                                                        |

| ecr                               | Address Error Trap Vector                  |                      |                                                        |

| ă                                 | Stack Error Trap Vector                    |                      |                                                        |

|                                   | Math Error Trap Vector                     |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Interrupt Vector 0                         | 0x000114             |                                                        |

|                                   | Interrupt Vector 1                         | _                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~<br>Interrupt Vector 52                   | 0x000470             | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   |                                            | 0x00017C             |                                                        |

|                                   | Interrupt Vector 53<br>Interrupt Vector 54 | 0x00017E<br>0x000180 |                                                        |

|                                   | ~                                          | 0000180              |                                                        |

|                                   | ~                                          | -                    |                                                        |

|                                   | ~ ~                                        |                      |                                                        |

|                                   | -<br>Interrupt Vector 116                  | -                    |                                                        |

|                                   | Interrupt Vector 117                       | 0x0001FE             |                                                        |

| *                                 | Start of Code                              | 0x000200             | L                                                      |

|                                   |                                            |                      |                                                        |

| Note 1: See                       | e Table 7-1 for the list of impleme        | ented interrupt v    | ectors.                                                |

| U-0               | U-0                                                                                 | R/W-0                                                | U-0                                                                | U-0                                      | U-0 | U-0   | U-0                    |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------|-----|-------|------------------------|--|--|--|--|--|

| —                 | —                                                                                   | CTMUIF                                               | —                                                                  | —                                        | —   | —     | -                      |  |  |  |  |  |

| bit 15            |                                                                                     |                                                      |                                                                    |                                          |     |       | bit 8                  |  |  |  |  |  |

|                   |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |  |  |

| U-0               | U-0                                                                                 | U-0                                                  | U-0                                                                | U-0                                      | U-0 | R/W-0 | R/W-0                  |  |  |  |  |  |

|                   | —                                                                                   | —                                                    | —                                                                  |                                          |     | U1EIF | FLTB1IF <sup>(1)</sup> |  |  |  |  |  |

| bit 7             |                                                                                     |                                                      |                                                                    |                                          |     |       | bit 0                  |  |  |  |  |  |

| [                 |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |  |  |

| Legend:           |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |  |  |

| R = Readab        | le bit                                                                              | W = Writable                                         | bit                                                                | U = Unimplemented bit, read as '0'       |     |       |                        |  |  |  |  |  |

| -n = Value a      | t POR                                                                               | '1' = Bit is set                                     |                                                                    | 0' = Bit is cleared $x = Bit is unknown$ |     |       |                        |  |  |  |  |  |

|                   |                                                                                     |                                                      |                                                                    |                                          |     |       |                        |  |  |  |  |  |

| bit 15-14         | Unimplemen                                                                          | ted: Read as '                                       | o'                                                                 |                                          |     |       |                        |  |  |  |  |  |

| bit 13            | CTMUIF: CTM                                                                         | MU Interrupt Fla                                     | ag Status bit                                                      |                                          |     |       |                        |  |  |  |  |  |

|                   |                                                                                     | equest has occ                                       |                                                                    |                                          |     |       |                        |  |  |  |  |  |

|                   | 0 = Interrupt r                                                                     | equest has not                                       | 0 = Interrupt request has not occurred                             |                                          |     |       |                        |  |  |  |  |  |

|                   | Unimplemented: Read as '0'                                                          |                                                      |                                                                    |                                          |     |       |                        |  |  |  |  |  |

| bit 12-2          | Unimplemen                                                                          | ted: Read as '                                       | כי                                                                 |                                          |     |       |                        |  |  |  |  |  |

| bit 12-2<br>bit 1 | -                                                                                   | t <b>ed:</b> Read as '(<br>1 Error Interru           |                                                                    | bit                                      |     |       |                        |  |  |  |  |  |

|                   | <b>U1EIF:</b> UART<br>1 = Interrupt r                                               | 1 Error Interrup                                     | ot Flag Status<br>curred                                           | bit                                      |     |       |                        |  |  |  |  |  |

|                   | <b>U1EIF:</b> UART<br>1 = Interrupt r<br>0 = Interrupt r                            | 1 Error Interrup<br>equest has occ<br>equest has not | ot Flag Status<br>curred<br>coccurred                              |                                          |     |       |                        |  |  |  |  |  |

|                   | <b>U1EIF:</b> UART<br>1 = Interrupt r<br>0 = Interrupt r                            | 1 Error Interrup                                     | ot Flag Status<br>curred<br>coccurred                              |                                          |     |       |                        |  |  |  |  |  |

| bit 1             | U1EIF: UART<br>1 = Interrupt r<br>0 = Interrupt r<br>FLTB1IF: PW<br>1 = Interrupt r | 1 Error Interrup<br>equest has occ<br>equest has not | ot Flag Status<br>curred<br>coccurred<br>errupt Flag Sta<br>curred |                                          |     |       |                        |  |  |  |  |  |

## REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

Note 1: This bit is available in dsPIC(16/32)MC102/104 devices only.

| U-0          | U-0           | U-0                | U-0                         | U-0              | U-0                  | U-0                  | U-0                  |

|--------------|---------------|--------------------|-----------------------------|------------------|----------------------|----------------------|----------------------|

| _            | —             | _                  | —                           | —                | —                    | —                    | —                    |

| bit 15       |               |                    |                             |                  |                      |                      | bit 8                |

|              |               |                    |                             |                  |                      |                      |                      |

| U-0          | R/W-1         | R/W-0              | R/W-0                       | U-0              | R/W-1                | R/W-0                | R/W-0                |

| _            | INT2IP2       | INT2IP1            | INT2IP0                     | —                | T5IP2 <sup>(1)</sup> | T5IP1 <sup>(1)</sup> | T5IP0 <sup>(1)</sup> |

| bit 7        |               |                    |                             |                  |                      |                      | bit 0                |

|              |               |                    |                             |                  |                      |                      |                      |

| Legend:      |               |                    |                             |                  |                      |                      |                      |

| R = Readab   | le bit        | W = Writable       | bit                         | U = Unimple      | mented bit, read     | 1 as '0'             |                      |

| -n = Value a | t POR         | '1' = Bit is set   |                             | '0' = Bit is cle | eared                | x = Bit is unkr      | nown                 |

|              |               |                    |                             |                  |                      |                      |                      |

| bit 15-7     | Unimplemen    | ted: Read as '     | 0'                          |                  |                      |                      |                      |

| bit 6-4      | INT2IP<2:0>:  | External Inter     | rupt 2 Priority             | bits             |                      |                      |                      |

|              | 111 = Interru | pt is Priority 7 ( | highest priorit             | ty interrupt)    |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | 001 = Interru |                    |                             |                  |                      |                      |                      |

|              | 000 = Interru | pt source is dis   | abled                       |                  |                      |                      |                      |

| bit 3        | Unimplemen    | ted: Read as '     | 0'                          |                  |                      |                      |                      |

| bit 2-0      | T5IP<2:0>: ⊺  | ïmer5 Interrupt    | Priority bits <sup>(1</sup> | )                |                      |                      |                      |

|              | 111 = Interru | pt is Priority 7 ( | highest priorit             | ty interrupt)    |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | •             |                    |                             |                  |                      |                      |                      |

|              | 001 = Interru | pt is Priority 1   |                             |                  |                      |                      |                      |

|              | 000 = Interru | pt source is dis   | abled                       |                  |                      |                      |                      |

|              | h h :         |                    |                             |                  |                      |                      |                      |

## REGISTER 7-22: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

**Note 1:** These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

| REGISTER           | 10-5: RPINK                                                  |                                                                                                 | KAL PIN SE | LECT INPUT       | REGISTER        | 1               |       |

|--------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|------------------|-----------------|-----------------|-------|

| U-0                | U-0                                                          | U-0                                                                                             | R/W-1      | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| —                  | —                                                            | —                                                                                               | IC2R4      | IC2R3            | IC2R2           | IC2R1           | IC2R0 |

| bit 15             |                                                              |                                                                                                 |            |                  |                 |                 | bit 8 |

|                    |                                                              |                                                                                                 |            |                  |                 |                 |       |

| U-0                | U-0                                                          | U-0                                                                                             | R/W-1      | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|                    | —                                                            | —                                                                                               | IC1R4      | IC1R3            | IC1R2           | IC1R1           | IC1R0 |

| bit 7              |                                                              |                                                                                                 |            |                  |                 |                 | bit ( |

| Legend:            |                                                              |                                                                                                 |            |                  |                 |                 |       |

| R = Readabl        | e bit                                                        | W = Writable I                                                                                  | oit        | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at      | POR                                                          | '1' = Bit is set                                                                                |            | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 7-5<br>bit 4-0 | 11111 = Inpu<br>11110 = Reso<br>11010 = Reso<br>11001 = Inpu | erved<br>erved<br>it tied to RP25<br>it tied to RP1<br>it tied to RP0<br><b>ted:</b> Read as '0 | ),         |                  |                 |                 |       |

| Uit 4-V            | 11111 = Inpu<br>11110 = Rese<br>11010 = Rese                 | erved<br>erved<br>it tied to RP25<br>it tied to RP1                                             |            | to the Corresp   | onding KPN PI   |                 |       |

## REGISTER 10-5: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0           | U-0           | U-0              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|---------------|---------------|------------------|----------------|------------------|-----------------|-----------------|-------|

| —             | —             | —                |                |                  | RP1R<4:0>       |                 |       |

| bit 15        |               |                  |                |                  |                 |                 | bit 8 |

|               |               |                  |                |                  |                 |                 |       |

| U-0           | U-0           | U-0              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| _             | —             | —                |                |                  | RP0R<4:0>       |                 |       |

| bit 7         |               |                  |                |                  |                 |                 | bit 0 |

|               |               |                  |                |                  |                 |                 |       |

| Legend:       |               |                  |                |                  |                 |                 |       |

| R = Readable  | e bit         | W = Writable     | bit            | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|               |               |                  |                |                  |                 |                 |       |

| bit 15-13     | Unimplemen    | ted: Read as '   | 0'             |                  |                 |                 |       |

| bit 12-8      | RP1R<4:0>:    | Peripheral Out   | out Function   | is Assigned to F | RP1 Output Pir  | n bits          |       |

|               | (see Table 10 | -2 for periphera | al function nu | mbers)           |                 |                 |       |

|               |               |                  |                |                  |                 |                 |       |

#### REGISTER 10-11: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 4-0 | <b>RP0R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP0 Output Pin bits |

|---------|---------------------------------------------------------------------------------------|

|         | (see Table 10-2 for peripheral function numbers)                                      |

Unimplemented: Read as '0'

### REGISTER 10-12: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|--------------------------|-------|-------|

| —      | —   | —   |       |       | RP3R<4:0> <sup>(1)</sup> | 1     |       |

| bit 15 |     |     |       |       |                          |       | bit 8 |

|        |     |     |       |       |                          |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 |

|        |     |     |       |       | RP2R<4:0> <sup>(1)</sup> |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP3R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP3 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

| bit 7-5   | Unimplemented: Read as '0'                                                                           |

| bit 4-0   | <b>RP2R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP2 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

**Note 1:** These bits are not available in dsPIC33FJXX(GP/MC)101 devices.

bit 7-5

bit 7

bit 0

## 11.1 Timer1 Control Register

| R/W-0              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                        | U-0           | U-0                | U-0              | U-0                | U-0   |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------|--------------------|------------------|--------------------|-------|--|--|--|

| TON <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TSIDL                                                                                                        | —             |                    |                  | —                  |       |  |  |  |

| bit 15             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |               |                    |                  |                    | bit 8 |  |  |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |               |                    |                  |                    |       |  |  |  |

| U-0                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                        | R/W-0         | U-0                | R/W-0            | R/W-0              | U-0   |  |  |  |

| —                  | TGATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TCKPS1                                                                                                       | TCKPS0        | —                  | TSYNC            | TCS <sup>(1)</sup> |       |  |  |  |

| bit 7              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |               |                    |                  |                    | bit ( |  |  |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |               |                    |                  |                    |       |  |  |  |

| Legend:            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |               |                    |                  |                    |       |  |  |  |

| R = Readable       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W = Writable                                                                                                 |               | -                  | mented bit, read |                    |       |  |  |  |

| -n = Value at      | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                             |               | '0' = Bit is cle   | ared             | x = Bit is unkno   | own   |  |  |  |

| bit 15             | TON: Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | On hit(1)                                                                                                    |               |                    |                  |                    |       |  |  |  |