Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                        |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (11K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 14x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc104-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  |      | (e)                   |              |                 | Rem                           | appa          | ble I          | Perip | herals                             | 5   | -                 |            | с                    |      |                   |             |      |          |                                 |

|------------------|------|-----------------------|--------------|-----------------|-------------------------------|---------------|----------------|-------|------------------------------------|-----|-------------------|------------|----------------------|------|-------------------|-------------|------|----------|---------------------------------|

| Device           | Pins | Program Flash (Kbyte) | RAM (Kbytes) | Remappable Pins | 16-bit Timer <sup>(1,2)</sup> | Input Capture | Output Compare | UART  | External Interrupts <sup>(3)</sup> | SPI | Motor Control PWM | PWM Faults | 10-Bit, 1.1 Msps ADC | RTCC | I <sup>2</sup> C™ | Comparators | CTMU | I/O Pins | Packages                        |

| dsPIC33FJ32GP101 | 18   | 32                    | 2            | 8               | 5                             | 3             | 2              | 1     | 3                                  | 1   |                   | -          | 1 ADC,<br>6-ch       | Y    | 1                 | 3           | Y    | 13       | PDIP,<br>SOIC                   |

|                  | 20   | 32                    | 2            | 8               | 5                             | 3             | 2              | 1     | 3                                  | 1   |                   | —          | 1 ADC,<br>6-ch       | Y    | 1                 | 3           | Y    | 15       | SSOP                            |

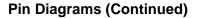

| dsPIC33FJ32GP102 | 28   | 32                    | 2            | 16              | 5                             | 3             | 2              | 1     | 3                                  | 1   |                   |            | 1 ADC,<br>8-ch       | Y    | 1                 | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 32                    | 2            | 16              | 5                             | 3             | 2              | 1     | 3                                  | 1   |                   | _          | 1 ADC,<br>8-ch       | Y    | 1                 | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ32GP104 | 44   | 32                    | 2            | 26              | 5                             | 3             | 2              | 1     | 3                                  | 1   |                   |            | 1 ADC,<br>14-ch      | Y    | 1                 | 3           | Y    | 35       | TQFP,<br>QFN,<br>VTLA           |

| dsPIC33FJ32MC101 | 20   | 32                    | 2            | 10              | 5                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 1          | 1 ADC,<br>6-ch       | Y    | 1                 | 3           | Y    | 15       | PDIP,<br>SOIC,<br>SSOP          |

| dsPIC33FJ32MC102 | 28   | 32                    | 2            | 16              | 5                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>8-ch       | Y    | 1                 | 3           | Y    | 21       | SPDIP,<br>SOIC,<br>SSOP,<br>QFN |

|                  | 36   | 32                    | 2            | 16              | 5                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>8-ch       | Y    | 1                 | 3           | Y    | 21       | VTLA                            |

| dsPIC33FJ32MC104 | 44   | 32                    | 2            | 26              | 5                             | 3             | 2              | 1     | 3                                  | 1   | 6-ch              | 2          | 1 ADC,<br>14-ch      | Y    | 1                 | 3           | Y    | 35       | TQFP,<br>QFN,<br>VTLA           |

### TABLE 2: dsPIC33FJ32(GP/MC)101/102/104 DEVICE FEATURES

**Note 1:** Four out of five timers are remappable.

2: Two pairs can be combined to have up to two 32-bit timers.

**3:** Two out of three interrupts are remappable.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternately, refer to the AC/DC characteristics and timing requirements information in the "dsPIC33F Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70659) for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS51616)

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) (DS51749)

### 2.6 External Oscillator Pins

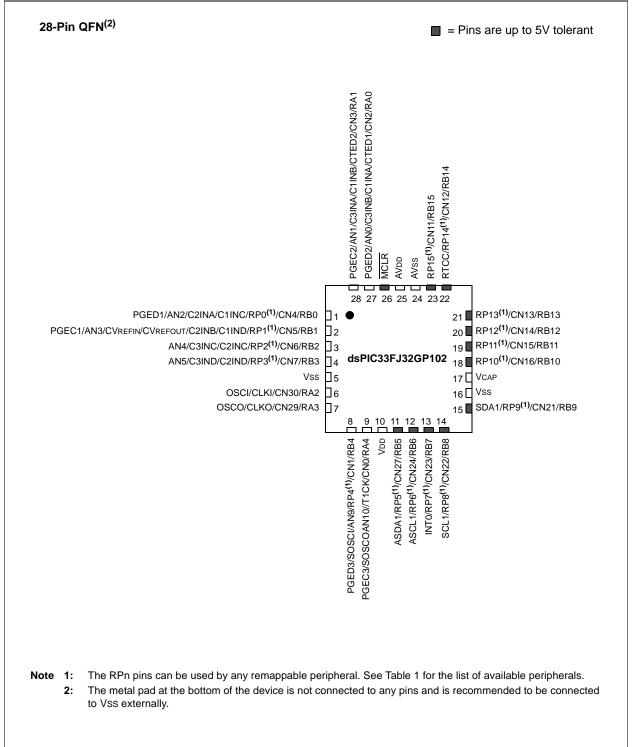

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70204) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ16(GP/MC)101/102 The and dsPIC33FJ32(GP/MC)101/102/104 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can serve as a data, address, or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

There are two classes of instruction in the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices are capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 is shown in Figure 3-2.

### 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data-space mapping feature lets any instruction access program space as if it were data space.

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory, while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain Working registers to each address space.

### 4.2 Data Address Space

The dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family CPU has a separate 16-bit-wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps is shown in Figure 4-4.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15>=0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

Microchip dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices implement up to 2 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decoding but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction in progress is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternately, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

| Note: | The actual set of peripheral features and interrupts varies by the device. Refer to |

|-------|-------------------------------------------------------------------------------------|

|       | the corresponding device tables and                                                 |

|       | pinout diagrams for device-specific information.                                    |

### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using the MOV class of instructions, which support Memory Direct Addressing mode with a 16-bit address field or by using Indirect Addressing mode with a Working register as an Address Pointer.

| TABLE 4-  | 17:         | ADC1   | REGIS  | STER M | AP FO  | R dsPIC             | 33FJ32(  | GP/MC)1  | 04 DEV  | ICES         |           |                   |        |        |          |          |         |               |

|-----------|-------------|--------|--------|--------|--------|---------------------|----------|----------|---------|--------------|-----------|-------------------|--------|--------|----------|----------|---------|---------------|

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11              | Bit 10   | Bit 9    | Bit 8   | Bit 7        | Bit 6     | Bit 5             | Bit 4  | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 0         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF1  | 0302        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 1         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF2  | 0304        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 2         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF3  | 0306        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 3         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF4  | 0308        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 4         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF5  | 030A        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 5         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF6  | 030C        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 6         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF7  | 030E        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 7         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF8  | 0310        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 8         |                   |        |        |          |          |         | xxxx          |

| ADC1BUF9  | 0312        |        |        |        |        |                     |          |          | ADC1 Da | ata Buffer   | 9         |                   |        |        |          |          |         | xxxx          |

| ADC1BUFA  | 0314        |        |        |        |        |                     |          |          | ADC1 Da | ita Buffer ' | 10        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFB  | 0316        |        |        |        |        | ADC1 Data Buffer 11 |          |          |         |              |           |                   |        | xxxx   |          |          |         |               |

| ADC1BUFC  | 0318        |        |        |        |        |                     |          |          | ADC1 Da | ita Buffer 1 | 12        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFD  | 031A        |        |        |        |        |                     |          |          | ADC1 Da | ita Buffer 1 | 13        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFE  | 031C        |        |        |        |        |                     |          |          | ADC1 Da | ita Buffer 1 | 14        |                   |        |        |          |          |         | xxxx          |

| ADC1BUFF  | 031E        |        |        |        |        |                     |          |          | ADC1 Da | ita Buffer 1 | 15        |                   |        |        |          |          |         | xxxx          |

| AD1CON1   | 0320        | ADON   | —      | ADSIDL | —      | _                   |          | FORM1    | FORM0   | SSRC2        | SSRC1     | SSRC0             | _      | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322        | VCFG2  | VCFG1  | VCFG0  | —      | _                   | CSCNA    | CHPS1    | CHPS0   | BUFS         | —         | SMPI3             | SMPI2  | SMPI1  | SMPI0    | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324        | ADRC   | —      | —      | SAMC4  | SAMC3               | SAMC2    | SAMC1    | SAMC0   | ADCS7        | ADCS6     | ADCS5             | ADCS4  | ADCS3  | ADCS2    | ADCS1    | ADCS0   | 0000          |

| AD1CHS123 | 0326        | —      | _      | —      | —      | _                   | CH123NB1 | CH123NB0 | CH123SB | —            | —         |                   | _      | —      | CH123NA1 | CH123NA0 | CH123SA | 0000          |

| AD1CHS0   | 0328        | CH0NB  | _      | —      | CH0SB4 | CH0SB3              | CH0SB2   | CH0SB1   | CH0SB0  | <b>CH0NA</b> | —         |                   | CH0SA4 | CH0SA3 | CH0SA2   | CH0SA1   | CH0SA0  | 0000          |

| AD1PCFGL  | 032C        | PCFG15 | _      | —      |        |                     |          |          |         | F            | PCFG<12:0 | )> <sup>(1)</sup> |        |        |          |          |         | 0000          |

| AD1CSSL   | 0330        | CSS15  | _      | _      |        |                     |          |          |         |              | CSS12:0>  | (1)               |        |        |          |          |         | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PCFG<10:9> and CSS<10:9> bits are available in dsPIC33FJ32(GP/MC)104 devices only.

### FIGURE 7-1: dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104 INTERRUPT VECTOR TABLE

| 1                                 |                                            | 7                    |                                                        |

|-----------------------------------|--------------------------------------------|----------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction                   | 0x000000             |                                                        |

|                                   | Reset – GOTO Address                       | 0x000002             |                                                        |

|                                   | Reserved                                   | 0x000004             |                                                        |

|                                   | Oscillator Fail Trap Vector                | _                    |                                                        |

|                                   | Address Error Trap Vector                  | _                    |                                                        |

|                                   | Stack Error Trap Vector                    | _                    |                                                        |

|                                   | Math Error Trap Vector                     | _                    |                                                        |

|                                   | Reserved                                   | -                    |                                                        |

|                                   | Reserved                                   | _                    |                                                        |

|                                   | Reserved<br>Interrupt Vector 0             | 0x000014             |                                                        |

|                                   | Interrupt Vector 1                         | 0,000014             |                                                        |

|                                   |                                            | -                    |                                                        |

|                                   | ~                                          |                      |                                                        |

|                                   | ~                                          | _                    |                                                        |

|                                   | Interrupt Vector 52                        | 0x00007C             | (4)                                                    |

|                                   | Interrupt Vector 53                        | 0x00007E             | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ity                               | Interrupt Vector 54                        | 0x000080             |                                                        |

| iori                              | ~                                          |                      |                                                        |

| ā                                 | ~                                          |                      |                                                        |

| der                               | ~                                          |                      |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 116                       | 0x0000FC             |                                                        |

| ra                                | Interrupt Vector 117                       | 0x0000FE             |                                                        |

| atu                               | Reserved                                   | 0x000100             |                                                        |

| Z                                 | Reserved                                   | 0x000102             |                                                        |

| sing                              | Reserved                                   |                      |                                                        |

| eas                               | Oscillator Fail Trap Vector                |                      |                                                        |

| ecr                               | Address Error Trap Vector                  |                      |                                                        |

| ă                                 | Stack Error Trap Vector                    |                      |                                                        |

|                                   | Math Error Trap Vector                     |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Reserved                                   |                      |                                                        |

|                                   | Interrupt Vector 0                         | 0x000114             |                                                        |

|                                   | Interrupt Vector 1                         | _                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~                                          | 4                    |                                                        |

|                                   | ~<br>Interrupt Vector 52                   | 0x000470             | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   |                                            | 0x00017C             |                                                        |

|                                   | Interrupt Vector 53<br>Interrupt Vector 54 | 0x00017E<br>0x000180 |                                                        |

|                                   | ~                                          | 0000180              |                                                        |

|                                   | ~                                          | -                    |                                                        |

|                                   | ~ ~                                        | _                    |                                                        |

|                                   | -<br>Interrupt Vector 116                  | -                    |                                                        |

|                                   | Interrupt Vector 117                       | 0x0001FE             |                                                        |

| *                                 | Start of Code                              | 0x000200             | L                                                      |

|                                   |                                            |                      |                                                        |

| Note 1: See                       | e Table 7-1 for the list of impleme        | ented interrupt v    | ectors.                                                |

|                  | R/W-1                                                                                  | R/W-0                                                                          | R/W-0                                              | U-0                | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|--------------------|------------------|-----------------|--------|--|--|--|--|--|--|

| _                | T2IP2                                                                                  | T2IP1                                                                          | T2IP0                                              |                    | OC2IP2           | OC2IP1          | OC2IP0 |  |  |  |  |  |  |

| bit 15           |                                                                                        |                                                                                |                                                    |                    |                  |                 | bit 8  |  |  |  |  |  |  |

|                  |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

| U-0              | R/W-1                                                                                  | R/W-0                                                                          | R/W-0                                              | U-0                | U-0              | U-0             | U-0    |  |  |  |  |  |  |

| _                | IC2IP2                                                                                 | IC2IP1                                                                         | IC2IP0                                             |                    | —                |                 | —      |  |  |  |  |  |  |

| bit 7            |                                                                                        |                                                                                |                                                    |                    |                  |                 | bit    |  |  |  |  |  |  |

| Legend:          |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

| R = Readab       | le bit                                                                                 | W = Writable                                                                   | bit                                                | U = Unimplen       | nented bit, read | l as '0'        |        |  |  |  |  |  |  |

| -n = Value a     | t POR                                                                                  | '1' = Bit is set                                                               |                                                    | '0' = Bit is cle   |                  | x = Bit is unkr | nown   |  |  |  |  |  |  |

|                  |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

| bit 15           | Unimplemer                                                                             | nted: Read as '                                                                | 0'                                                 |                    |                  |                 |        |  |  |  |  |  |  |

| bit 14-12        | T2IP<2:0>: 7                                                                           | Fimer2 Interrupt                                                               | Priority bits                                      |                    |                  |                 |        |  |  |  |  |  |  |

|                  | 111 = Interru                                                                          | 111 = Interrupt is Priority 7 (highest priority interrupt)                     |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  |                                                                                        | ipt is Priority 1<br>ipt source is dis                                         | abled                                              |                    |                  |                 |        |  |  |  |  |  |  |

| bit 11           |                                                                                        | h <b>ted:</b> Read as '                                                        |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

| bit 10-8         | OC2IP<2:0>: Output Compare Channel 2 Interrupt Priority bits                           |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  | 111 = Interrupt is Priority 7 (highest priority interrupt)                             |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  |                                                                                        |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  | •                                                                                      |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  | •<br>001 = Interrupt is Priority 1                                                     |                                                                                |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  | 001 = Interr                                                                           | int is Priority 1                                                              |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  |                                                                                        |                                                                                | abled                                              |                    |                  |                 |        |  |  |  |  |  |  |

| bit 7            | 000 = Interru                                                                          | ipt is Priority 1<br>ipt source is dis<br>nted: Read as '                      |                                                    |                    |                  |                 |        |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemer                                                            | ipt source is dis<br>nted: Read as '                                           | 0'                                                 | errupt Priority bi | its              |                 |        |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '                                           | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•                  | ipt source is dis<br>nted: Read as '<br>Input Capture C<br>ipt is Priority 7 ( | 0'<br>Channel 2 Inte                               |                    | its              |                 |        |  |  |  |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | <sup>0'</sup><br>Channel 2 Inte<br>highest priorit |                    | its              |                 |        |  |  |  |  |  |  |

### REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| Input Name              | Function Name | Register | Configuration<br>Bits     |

|-------------------------|---------------|----------|---------------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>                |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>                |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>                |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>                |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<4:0> <sup>(2)</sup> |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<4:0> <sup>(2)</sup> |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>                 |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>                 |

| Input Capture 3         | IC3           | RPINR8   | IC3R<4:0>                 |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>                |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>                |

| UART1 Clear-to-Send     | U1CTS         | RPINR18  | U1CTSR<4:0>               |

| SDI1 SPI Data Input 1   | SDI1          | RPINR20  | SDI1R<4:0> <sup>(2)</sup> |

| SCK1 SPI Clock Input 1  | SCK1          | RPINR20  | SCK1R<4:0> <sup>(2)</sup> |

| SPI1 Slave Select Input | SS1           | RPINR21  | SS1R<4:0> <sup>(2)</sup>  |

### TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)<sup>(1)</sup>

Note 1: Unless otherwise noted, all inputs use the Schmitt input buffers.

2: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

|                 | 0 2. 0 0.017                              |                                                                                                         |                            |                                    | OIOTEIX              |                |                    |  |  |

|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------|----------------------|----------------|--------------------|--|--|

| R/W-0           | R/W-0                                     | R/W-0                                                                                                   | U-0                        | R/W-0, HC                          | R/W-0                | R-0            | R-1                |  |  |

| UTXISEL1        | UTXINV                                    | UTXISEL0                                                                                                |                            | UTXBRK                             | UTXEN <sup>(1)</sup> | UTXBF          | TRMT               |  |  |

| bit 15          |                                           |                                                                                                         |                            |                                    |                      |                | bit 8              |  |  |

|                 |                                           |                                                                                                         |                            |                                    |                      |                |                    |  |  |

| R/W-0           | R/W-0                                     | R/W-0                                                                                                   | R-1                        | R-0                                | R-0                  | R/C-0          | R-0                |  |  |

| URXISEL1        | URXISEL0                                  | ADDEN                                                                                                   | RIDLE                      | PERR                               | FERR                 | OERR           | URXDA              |  |  |

| bit 7           |                                           |                                                                                                         |                            |                                    |                      |                | bit C              |  |  |

|                 |                                           |                                                                                                         |                            |                                    |                      |                |                    |  |  |

| Legend:         |                                           | C = Clearable b                                                                                         | oit                        | HC = Hardwa                        | are Clearable bi     | t              |                    |  |  |

| R = Readable    | bit                                       | W = Writable bi                                                                                         | t                          | U = Unimplemented bit, read as '0' |                      |                |                    |  |  |

| -n = Value at F | POR                                       | '1' = Bit is set                                                                                        |                            | '0' = Bit is cle                   | ared                 | x = Bit is unk | a = Bit is unknown |  |  |

| bit 15,13       | 11 = Reserve<br>10 = Interrup<br>transmit | D>: UARTx Trans<br>ed; do not use<br>t when a charact<br>buffer becomes<br>t when the last ch<br>pleted | ter is transferre<br>empty | ed to the Transr                   | mit Shift Registe    | . ,            |                    |  |  |

### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| 00 = Interrupt when a character is transferred to the | Transmit Shift Register (this implies there is at least |

|-------------------------------------------------------|---------------------------------------------------------|

| one character open in the transmit buffer)            |                                                         |

| bit 14  | UTXINV: UARTx Transmit Polarity Inversion bit                                                                                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If IREN = 0:                                                                                                                                                          |

|         | 1 = UxTX Idle state is '0'                                                                                                                                            |

|         | 0 = UxTX Idle state is '1'                                                                                                                                            |

|         | <u>If IREN = 1:</u>                                                                                                                                                   |

|         | 1 = IrDA encoded, UxTX Idle state is '1'                                                                                                                              |

|         | 0 = IrDA encoded, UxTX Idle state is '0'                                                                                                                              |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                            |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                      |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul> |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                  |

| bit 10  | UTXEN: UARTx Transmit Enable bit <sup>(1)</sup>                                                                                                                       |

|         | 1 = Transmit is enabled, UxTX pin is controlled by UARTx                                                                                                              |

|         | <ul> <li>0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by port</li> </ul>                             |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                              |

|         | 1 = Transmit buffer is full                                                                                                                                           |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                           |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                   |

|         | 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)                                                               |

|         | 0 = Transmit Shift Register is not empty, a transmission is in progress or queued                                                                                     |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                             |

|         | 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)                                                                 |

|         | 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)                                                             |

|         | 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive                                                                    |

|         | buffer; receive buffer has one or more characters                                                                                                                     |

| Note 1  | Pater to "ILAPT" (DS70199) in the "doDIC22/DIC24 Family Pateroneo Manual" for information on applying                                                                 |

## **Note 1:** Refer to "**UART**" (DS70188) in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UART module for transmit operation.

REGISTER 21-9: ALRMVAL (WHEN ALRMPTR<1:0> = 01): ALARM WEEKDAY AND HOURS

| VALU                                  | E REGISTER           | (1)                                                          |                                                           |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                             |  |

|---------------------------------------|----------------------|--------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| U-0                                   | U-0                  | U-0                                                          | U-0                                                       | R/W-x                                                                                                                                                                                                                                                                   | R/W-x                                                                                                                                                                                                                                                                                                                                 | R/W-x                                                                                                                                                                                                                                                                                                       |  |

|                                       | _                    | _                                                            | —                                                         | WDAY2                                                                                                                                                                                                                                                                   | WDAY1                                                                                                                                                                                                                                                                                                                                 | WDAY0                                                                                                                                                                                                                                                                                                       |  |

|                                       |                      |                                                              |                                                           |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                       | bit 8                                                                                                                                                                                                                                                                                                       |  |

| U-0                                   | R/W-x                | R/W-x                                                        | R/W-x                                                     | R/W-x                                                                                                                                                                                                                                                                   | R/W-x                                                                                                                                                                                                                                                                                                                                 | R/W-x                                                                                                                                                                                                                                                                                                       |  |

| _                                     | HRTEN1               | HRTEN0                                                       | HRONE3                                                    | HRONE2                                                                                                                                                                                                                                                                  | HRONE1                                                                                                                                                                                                                                                                                                                                | HRONE0                                                                                                                                                                                                                                                                                                      |  |

|                                       |                      |                                                              |                                                           |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                       | bit (                                                                                                                                                                                                                                                                                                       |  |

| it                                    | W – Writable         | hit                                                          | II – Unimplen                                             | nented hit read                                                                                                                                                                                                                                                         | l as '0'                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                             |  |

| R = Readable bit<br>-n = Value at POR |                      |                                                              |                                                           |                                                                                                                                                                                                                                                                         | x = Bit is unknown                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                             |  |

|                                       | U-0<br>—<br>U-0<br>— | U-0 U-0<br>— — —<br>U-0 R/W-x<br>— HRTEN1<br>it W = Writable | U-0 R/W-x R/W-x<br>— HRTEN1 HRTEN0<br>it W = Writable bit | U-0         U-0         U-0         U-0           —         —         —         —         —           U-0         R/W-x         R/W-x         R/W-x           —         HRTEN1         HRTEN0         HRONE3           it         W = Writable bit         U = Unimplen | U-0         U-0         U-0         U-0         R/W-x           —         —         —         —         WDAY2           U-0         R/W-x         R/W-x         R/W-x         R/W-x           —         HRTEN1         HRTEN0         HRONE3         HRONE2           it         W = Writable bit         U = Unimplemented bit, read | U-0       U-0       U-0       R/W-x       R/W-x         —       —       —       WDAY2       WDAY1         U-0       R/W-x       R/W-x       R/W-x       R/W-x         HRTEN1       HRTEN0       HRONE3       HRONE2       HRONE1         it       W = Writable bit       U = Unimplemented bit, read as '0' |  |

| Dit 15-11 | Unimplemented: Read as '0'                                       |

|-----------|------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits      |

|           | Contains a value from 0 to 6.                                    |

| bit 7-6   | Unimplemented: Read as '0'                                       |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|           | Contains a value from 0 to 2.                                    |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

|           |                                                                  |

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

© 2011-2014 Microchip Technology Inc.

# REGISTER 21-10: ALRMVAL (WHEN ALRMPTR<1:0> = 00): ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |  |

|--------|---------|---------|---------|---------|---------|---------|---------|--|

| —      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |  |

| bit 15 |         |         |         |         |         |         | bit 8   |  |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

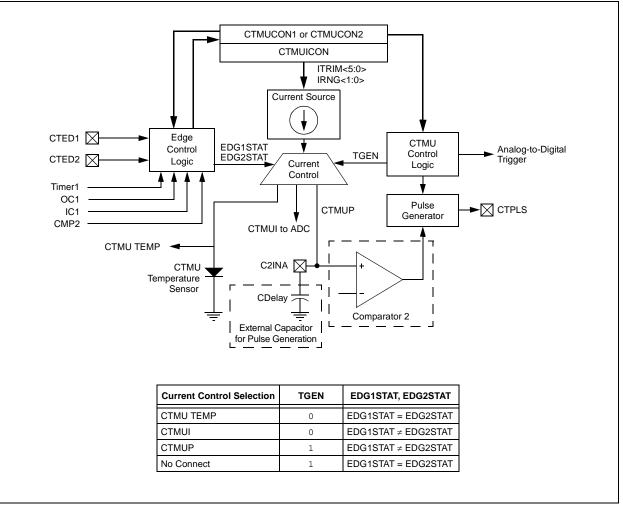

### FIGURE 22-1: CTMU BLOCK DIAGRAM

| DC CHARACI                                                                                           | TERISTICS              |     | (unless oth | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |                             |  |  |  |

|------------------------------------------------------------------------------------------------------|------------------------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------|--|--|--|

| Parameter<br>No.                                                                                     | Typical <sup>(1)</sup> | Max | Units       |                                                                                                                                                                                                                                                                                          | Conditions |                             |  |  |  |

| Idle Current (IIDLE): Core Off, Clock On Base Current <sup>(2)</sup> – dsPIC33FJ16(GP/MC)10X Devices |                        |     |             |                                                                                                                                                                                                                                                                                          |            |                             |  |  |  |

| DC40d                                                                                                | 0.4                    | 1.0 | mA          | -40°C                                                                                                                                                                                                                                                                                    |            |                             |  |  |  |

| DC40a                                                                                                | 0.4                    | 1.0 | mA          | +25°C                                                                                                                                                                                                                                                                                    | 2.21/      | LPRC                        |  |  |  |

| DC40b                                                                                                | 0.4                    | 1.0 | mA          | +85°C                                                                                                                                                                                                                                                                                    | - 3.3V     | (32.768 kHz) <sup>(3)</sup> |  |  |  |

| DC40c                                                                                                | 0.5                    | 1.0 | mA          | +125°C                                                                                                                                                                                                                                                                                   | _          |                             |  |  |  |

| DC41d                                                                                                | 0.5                    | 1.1 | mA          | -40°C                                                                                                                                                                                                                                                                                    |            |                             |  |  |  |

| DC41a                                                                                                | 0.5                    | 1.1 | mA          | +25°C                                                                                                                                                                                                                                                                                    | 2.21/      | 1 MIPS <sup>(3)</sup>       |  |  |  |

| DC41b                                                                                                | 0.5                    | 1.1 | mA          | +85°C                                                                                                                                                                                                                                                                                    | - 3.3V     | T MIPS(*)                   |  |  |  |

| DC41c                                                                                                | 0.8                    | 1.1 | mA          | +125°C                                                                                                                                                                                                                                                                                   | 1          |                             |  |  |  |

| DC42d                                                                                                | 0.9                    | 1.6 | mA          | -40°C                                                                                                                                                                                                                                                                                    |            |                             |  |  |  |

| DC42a                                                                                                | 0.9                    | 1.6 | mA          | +25°C                                                                                                                                                                                                                                                                                    | 2.21/      | 4 MIPS <sup>(3)</sup>       |  |  |  |