Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc104t-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

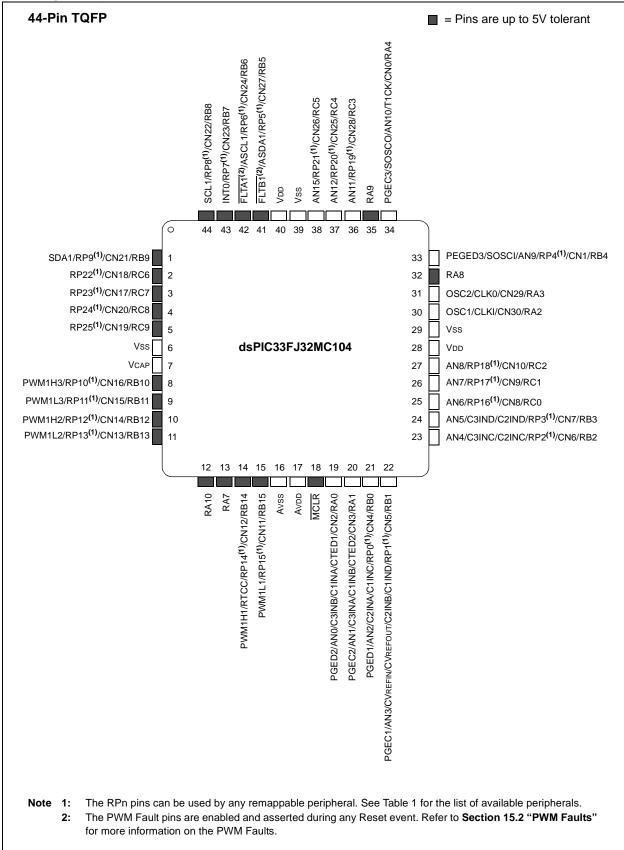

#### Pin Diagrams (Continued)

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. Signed to 40 bits. Integer data is inherently represented as a signed 2's complement value, where the Most Significant bit (MSb) is defined as a sign bit. The range of an N-bit 2's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ .

- For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including 0.

- For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a 2's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit 2's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product that has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiply operations.

The MUL instruction can be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result and word operands will direct a 32-bit result to the specified register(s) in the W array.

## 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled using the barrel shifter prior to accumulation.

## 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side and either true or complement data into the other input.

- In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented).

- In the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented.

The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS Register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block that controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described previously, and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value, to saturate.

Six STATUS Register bits support saturation and overflow:

- OA: ACCA overflowed into guard bits

- OB: ACCB overflowed into guard bits

- SA: ACCA saturated (bit 31 overflow and saturation)

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation)

- SB: ACCB saturated (bit 31 overflow and saturation)

- ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- OAB: Logical OR of OA and OB

- SAB: Logical OR of SA and SB

or

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when OA and OB are set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register are set (refer to **Section 7.0 "Interrupt Controller"**). This allows the user application to take immediate action; for example, to correct system gain.

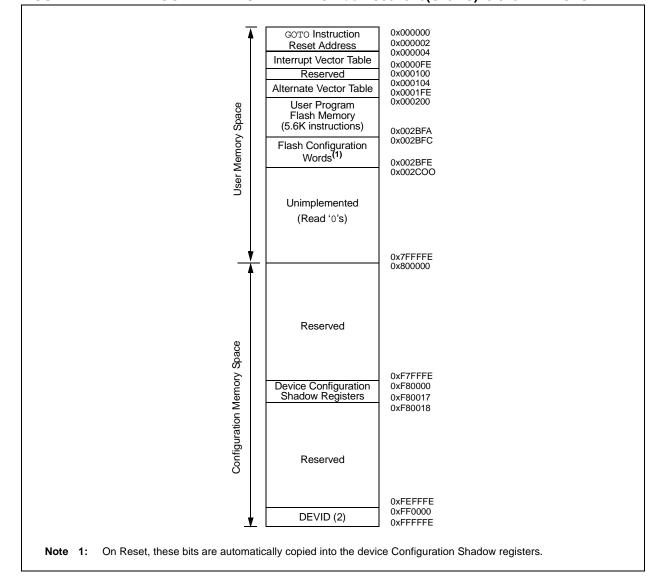

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Data Memory" (DS70202) and "Program Memory" (DS70203) in the "dsPIC33/PIC24 Family Reference Manual", which are available from the Microchip web site (www.microchip.com).

The device architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory maps for the dsPIC33FJ16(GP/MC)101/ 102 and dsPIC33FJ32(GP/MC)101/102/104 family of devices are shown in Figure 4-1 and Figure 4-2.

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJ16(GP/MC)101/102 DEVICES

#### TABLE 4-12: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8                        | Bit 7 | Bit 6 | Bit 5      | Bit 4      | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|-----------------------|------------------------------|-------|-------|------------|------------|--------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      |         | _      |        |        | _                     | _                            |       |       |            | I2C1 Recei | ve Register  |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | —      | _      | _      | _                     | _                            |       |       |            | I2C1 Trans | mit Register | •     |       |       | 00FF          |

| I2C1BRG  | 0204        | _       | _      | _       | —      | _      | _      | _                     | Baud Rate Generator Register |       |       |            |            |              |       |       | 0000  |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN                         | GCEN  | STREN | ACKDT      | ACKEN      | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                | ADD10                        | IWCOL | I2COV | D_A        | Р          | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       |        | _       | _      | _      | _      | I2C1 Address Register |                              |       |       |            |            |              | 0000  |       |       |               |

| I2C1MSK  | 020C        | —       | _      | _       | _      | _      |        |                       |                              |       | 120   | C1 Address | Mask Regis | ter          |       |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                               | Bit 14 | Bit 13   | Bit 12 | Bit 11                                                                     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|--------------------------------------|--------|----------|--------|----------------------------------------------------------------------------|--------|-------|-------|-------|--------|-------|------------|---------|--------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN                               | _      | USIDL    | IREN   | RTSMD                                                                      | —      | UEN1  | UEN0  | WAKE  | LPBACK | ABAUD | URXINV     | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1                             | UTXINV | UTXISEL0 | _      | UTXBRK UTXEN UTXBF TRMT URXISEL1 URXISEL0 ADDEN RIDLE PERR FERR OERR URXDA |        |       |       |       |        |       |            |         |        | 0110   |       |               |

| U1TXREG  | 0224        | _                                    | _      | -        | _      | _                                                                          | _      |       |       |       |        | UART1 | Transmit R | egister |        |        |       | xxxx          |

| U1RXREG  | 0226        | — — — — — — — UART1 Receive Register |        |          |        |                                                                            |        |       |       |       |        | 0000  |            |         |        |        |       |               |

| U1BRG    | 0228        | Baud Rate Generator Prescaler        |        |          |        |                                                                            |        |       |       |       |        |       | 0000       |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: SPI1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                                    | Bit 14                       | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|-------------------------------------------|------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|-------|--------|--------|---------------|

| SPI1STAT | 0240        | SPIEN                                     | _                            | SPISIDL | _      | _      | _      |       |       |       | SPIROV | _     | _     | _     |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _                                         | _                            | _       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2 | 0244        | FRMEN                                     | FRMEN SPIFSD FRMPOL FRMDLY - |         |        |        |        |       |       |       |        |       |       | 0000  |       |        |        |               |

| SPI1BUF  | 0248        | SPI1 Transmit and Receive Buffer Register |                              |         |        |        |        |       |       |       |        |       |       | 0000  |       |        |        |               |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# DS70000652F-page 72

#### TABLE 4-37: SYSTEM CONTROL REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6  | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 | All<br>Resets   |

|-----------|-------------|--------|--------|--------|--------|--------|---------|---------|---------|---------|--------|----------|-------|-------|-------|---------|-------|-----------------|

| RCON      | 0740        | TRAPR  | IOPUWR | _      |        | _      | _       | СМ      | VREGS   | EXTR    | SWR    | SWDTEN   | WDTO  | SLEEP | IDLE  | BOR     | POR   | xxxx(1)         |

| OSCCON    | 0742        | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK | IOLOCK | LOCK     | _     | CF    | _     | LPOSCEN | OSWEN | 0300 <b>(2)</b> |

| CLKDIV    | 0744        | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | _       | -      |          | _     |       |       | _       | _     | 3040            |

| OSCTUN    | 0748        | _      | _      | _      | _      | _      | _       | _       | _       | _       |        | TUN<5:0> |       |       |       |         | 0000  |                 |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the FOSC Configuration bits and by type of Reset.

#### TABLE 4-38: NVM REGISTER MAP

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| NVMCON    | 0760        | WR     | WREN   | WRERR  | _      | -      | _      | -     | _     | _     | ERASE | _     |       | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | <sub>0000</sub> (1) |

| NVMKEY    | 0766        |        | _      | _      |        |        | —      |       | _     |       |       |       | NVMKE | Y<7:0> |        |        |        | 0000                |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-39: PMD REGISTER MAP

| File Name | SFR<br>Addr | Bit 15              | Bit 14              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------------|---------------------|---------------------|--------|--------|--------|--------|-----------------------|-------|--------|-------|-------|-------|--------|--------|-------|-------|---------------|

| PMD1      | 0770        | T5MD <sup>(2)</sup> | T4MD <sup>(2)</sup> | T3MD   | T2MD   | T1MD   | _      | PWM1MD <sup>(1)</sup> | _     | I2C1MD | _     | U1MD  |       | SPI1MD | -      | —     | AD1MD | 0000          |

| PMD2      | 0772        | _                   | _                   | -      |        | _      | IC3MD  | IC2MD                 | IC1MD | -      |       |       | _     | _      | _      | OC2MD | OC1MD | 0000          |

| PMD3      | 0774        | _                   | _                   | -      |        | _      | CMPMD  | RTCCMD                | _     | -      |       |       | _     | _      | _      | _     | _     | 0000          |

| PMD4      | 0776        | —                   | _                   | _      | _      | _      | _      | _                     | _     | _      | _     | _     | _     |        | CTMUMD | _     | _     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is available in dsPIC33FJXXMC10X devices only.

2: These bits are available in dsPIC33FJ32(GP/MC)10X devices only.

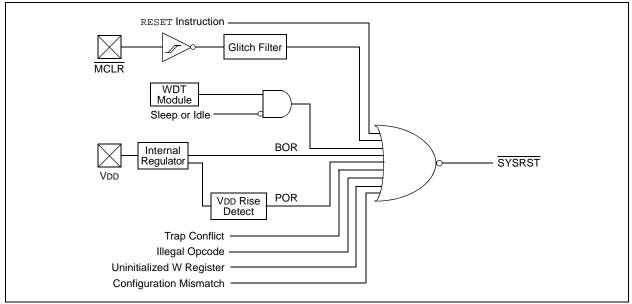

#### 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70192) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

All bits that are set, with the exception of the POR bit (RCON<0>), are cleared during a POR event. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

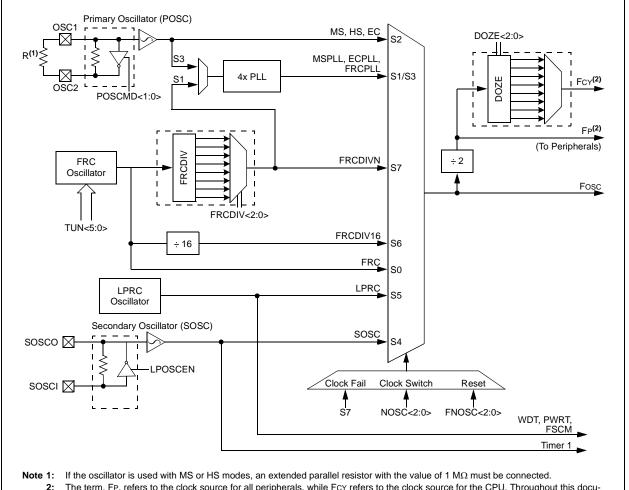

#### 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator (Part VI)" (DS70644) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The oscillator system for dsPIC33FJ16(GP/MC)101/ 102 and dsPIC33FJ32(GP/MC)101/102/104 devices provides:

- External and internal oscillator options as clock sources

- An on-chip, 4x Phase Lock Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

- A simplified diagram of the oscillator system is shown in Figure 8-1.

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a Doze ratio of 1:2 or lower.

#### FIGURE 8-1: OSCILLATOR SYSTEM DIAGRAM

#### 10.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Section 26.0 "Electrical Characteristics". Table 26-11 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD, with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin, (i.e., ANx), are always analog pins by default after any Reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the ADC1 Port Configuration Low (AD1PCFGL) register in the ADC module, by setting the appropriate bit that corresponds to that I/O port pin, to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD – 0.8), not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -6 mA and VDD = 3.3V

The maximum output current sourced by any 6 mA I/O pin = 15 mA.

LED source current < 15 mA is technically permitted. Refer to the VOH/IOH specifications in **Section 26.0 "Electrical Characteristics"** for additional information.

#### 10.6 I/O Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

```

Note: In the event you are not able to access the

product page using the link above, enter

this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en554109

```

#### 10.6.1 KEY RESOURCES

- "I/O Ports" (DS70193) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

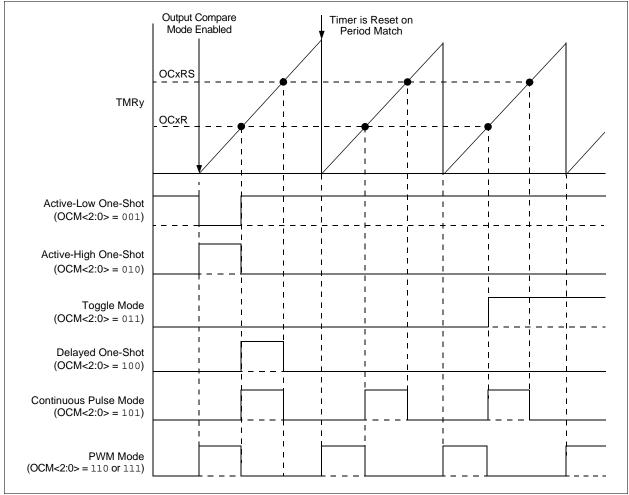

#### 14.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode bits (OCM<2:0>) in the Output Compare x Control (OCxCON<2:0>) register. Table 14-1 lists the different bit settings for the Output Compare modes. Figure 14-2 illustrates the output compare operation for various modes. The user

TABLE 14-1: OUTPUT COMPARE x MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

Note: See "Output Compare" in the "dsPIC33/ PIC24 Family Reference Manual" (DS70209) for OCxR and OCxRS register restrictions.

| OCM<2:0> | Mode                         | OCx Pin Initial State                        | OCx Interrupt Generation         |

|----------|------------------------------|----------------------------------------------|----------------------------------|

| 000      | Module Disabled              | Controlled by GPIO register                  |                                  |

| 001      | Active-Low One-Shot          | 0                                            | OCx Rising Edge                  |

| 010      | Active-High One-Shot         | 1                                            | OCx Falling Edge                 |

| 011      | Toggle                       | Current output is maintained                 | OCx Rising and Falling Edge      |

| 100      | Delayed One-Shot             | 0                                            | OCx Falling Edge                 |

| 101      | Continuous Pulse             | 0                                            | OCx Falling Edge                 |

| 110      | PWM without Fault Protection | 0, if OCxR is zero<br>1, if OCxR is non-zero | No Interrupt                     |

| 111      | PWM with Fault Protection    | 0, if OCxR is zero<br>1, if OCxR is non-zero | OCFA Falling Edge for OC1 to OC4 |

#### FIGURE 14-2: OUTPUT COMPARE x OPERATION

#### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Stop bit has been detected last                                                                                       |

|       | 0 = Stop bit was not detected last                                                                                                         |

|       | Hardware sets or clears when Start, Repeated Start or Stop is detected.                                                                    |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware sets or clears when Start, Repeated Start or Stop is detected.                                                                    |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                          |

|       | <ul> <li>1 = Read – Indicates data transfer is output from slave</li> <li>0 = Write – Indicates data transfer is input to slave</li> </ul> |

|       | Hardware sets or clears after reception of an I <sup>2</sup> C device address byte.                                                        |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive is complete, I2CxRCV is full                                                                                                   |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                                                              |

|       | Hardware sets when I2CxRCV is written with received byte. Hardware clears when software reads I2CxRCV.                                     |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty                                                       |

|       | Hardware sets when software writes to I2CxTRN. Hardware clears at completion of data transmission.                                         |

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| REGISTER      | 20-2: CMxC                                             | ON: COMPA                                                 | RATOR x CO                    | ONTROL REC        | GISTER          |                                      |                |

|---------------|--------------------------------------------------------|-----------------------------------------------------------|-------------------------------|-------------------|-----------------|--------------------------------------|----------------|

| R/W-0         | R/W-0                                                  | R/W-0                                                     | U-0                           | U-0               | U-0             | R/W-0                                | R/W-0          |

| CON           | COE                                                    | CPOL                                                      | _                             | —                 | _               | CEVT                                 | COUT           |

| bit 15        |                                                        |                                                           |                               |                   |                 |                                      | bit 8          |

| R/W-0         | R/W-0                                                  | U-0                                                       | R/W-0                         | U-0               | U-0             | R/W-0                                | R/W-0          |

| EVPOL1        | EVPOL0                                                 | 0-0                                                       | CREF                          |                   |                 | CCH1                                 | CCH0           |

| bit 7         | LVIOLO                                                 |                                                           | GIVEI                         |                   |                 | Com                                  | bit C          |

|               |                                                        |                                                           |                               |                   |                 |                                      |                |

| Legend:       |                                                        |                                                           |                               |                   |                 |                                      |                |

| R = Readable  |                                                        | W = Writable                                              |                               | -                 | nented bit, rea |                                      |                |

| -n = Value at | POR                                                    | '1' = Bit is se                                           | t                             | '0' = Bit is clea | ared            | x = Bit is unkr                      | iown           |

| bit 15        | CON: Compa                                             | arator x Enable                                           | bit                           |                   |                 |                                      |                |

|               | =                                                      | tor x is enable                                           |                               |                   |                 |                                      |                |

|               |                                                        | tor x is disable                                          |                               |                   |                 |                                      |                |

| bit 14        | COE: Compa                                             | arator x Output                                           | Enable bit                    |                   |                 |                                      |                |

|               |                                                        | tor output is pr<br>tor output is in                      | esent on the C<br>ternal only | xOUT pin          |                 |                                      |                |

| bit 13        | CPOL: Comp                                             | parator x Outpu                                           | it Polarity Sele              | ct bit            |                 |                                      |                |

|               |                                                        | tor x output is tor x output is                           |                               |                   |                 |                                      |                |

| bit 12-10     | Unimplemen                                             | ted: Read as                                              | 0'                            |                   |                 |                                      |                |

| bit 9         | CEVT: Comp                                             | arator x Event                                            | bit                           |                   |                 |                                      |                |

|               | interrupts                                             | ator x event ac<br>s until the bit is<br>ator x event dic | cleared                       | POL<1:0> set      | ings occurred   | ; disables future                    | e triggers and |

| bit 8         | COUT: Comp                                             | parator x Outpu                                           | ıt bit                        |                   |                 |                                      |                |

|               | 1 = VIN+ > VI                                          |                                                           | ted polarity):                |                   |                 |                                      |                |

|               | 0 = VIN+ < VI                                          |                                                           |                               |                   |                 |                                      |                |

|               | $\frac{\text{When CPOL}}{1 = \text{VIN+} < \text{VI}}$ | = 1 (inverted p                                           | olarity):                     |                   |                 |                                      |                |

|               | 0 = VIN + > VI                                         |                                                           |                               |                   |                 |                                      |                |

| bit 7-6       | EVPOL<1:0>                                             | . Trigger/Ever                                            | t/Interrupt Pola              | arity Select bits |                 |                                      |                |

|               | 10 = Trigger/                                          |                                                           | is generated                  |                   |                 | ator output (whil<br>tion of the pol |                |

|               | If $CPOL = 1$ (                                        | (inverted polari                                          |                               | 1421.14           |                 |                                      |                |

|               | •                                                      | (non-inverted p                                           | •                             | արտ.              |                 |                                      |                |

|               |                                                        |                                                           | comparator ou                 | ıtput.            |                 |                                      |                |

|               |                                                        | event/interrupt/<br>ator output (wh                       |                               | only on low-      | to-high transi  | tion of the pol                      | arity selected |

|               |                                                        | (inverted polari<br>ransition of the                      | t <u>y):</u><br>comparator οι | itput.            |                 |                                      |                |

|               | -                                                      | (non-inverted p                                           | -                             |                   |                 |                                      |                |

|               | Low-to-high t                                          | ransition of the                                          | comparator o                  | -                 |                 |                                      |                |

|               | 00 = Trigger/                                          | event/interrupt                                           | generation is o               | disabled          |                 |                                      |                |

|               |                                                        | ted: Read as                                              |                               |                   |                 |                                      |                |

#### CIETED 20 2 CMACONI COMPADATOD A CONTROL DECISTED

#### REGISTER 20-2: CMxCON: COMPARATOR x CONTROL REGISTER (CONTINUED)

- bit 4 **CREF:** Comparator x Reference Select bit (VIN+ input)

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to CxINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator x Channel Select bits

- 11 = VIN- input of comparator connects to INTREF

- 10 = VIN- input of comparator connects to CXIND pin

- 01 = VIN- input of comparator connects to CxINC pin

- ${\tt 00}$  = VIN- input of comparator connects to CxINB pin

### 26.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/MC)101/102/104 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

#### Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                | 40°C to +125°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                            | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 3.0V^{(3)}$  | 0.3V to +5.6V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $< 3.0V^{(3)}$    | 0.3V to (VDD + 0.3V) |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                   | 250 mA               |

| Maximum output current sourced and sunk by any I/O pin excluding OSCO         | 15 mA                |

| Maximum output current sourced and sunk by OSCO                               | 25 mA                |

| Maximum current sunk by all ports                                             | 200 mA               |

| Maximum current sourced by all ports <sup>(2)</sup>                           | 200 mA               |

**Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those, or any other conditions above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of the device maximum power dissipation (see Table 26-2).

- 3: See the "Pin Diagrams" section for 5V tolerant pins.

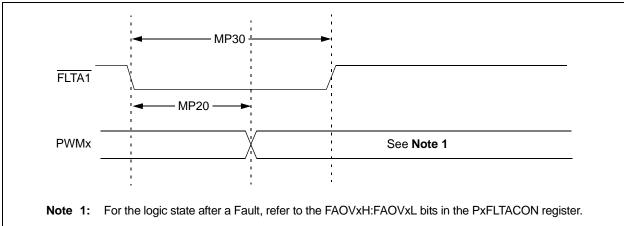

#### FIGURE 26-9: MOTOR CONTROL PWMx MODULE FAULT TIMING CHARACTERISTICS

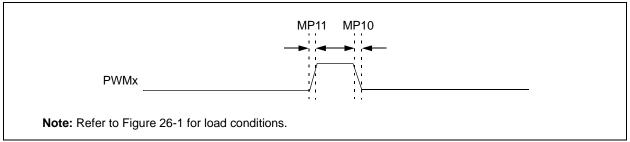

#### FIGURE 26-10: MOTOR CONTROL PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 26-28: MOTOR CONTROL PWMx MODULE TIMING REQUIREMENTS

| АС СНА       | RACTERIS | TICS                               | (unless | rd Opera<br>otherwis<br>ng tempe | se stated<br>rature | <b>d)</b><br>-40°C ≤ T | 3.0V to 3.6V<br>A ≤ +85°C for Industrial<br>A ≤ +125°C for Extended |

|--------------|----------|------------------------------------|---------|----------------------------------|---------------------|------------------------|---------------------------------------------------------------------|

| Param<br>No. | Symbol   | Characteristic <sup>(1)</sup>      | Min     | Тур                              | Max                 | Units                  | Conditions                                                          |

| MP10         | TFPWM    | PWM Output Fall Time               | —       | _                                | —                   | ns                     | See Parameter DO32                                                  |

| MP11         | TRPWM    | PWM Output Rise Time               | —       | —                                | —                   | ns                     | See Parameter DO31                                                  |

| MP20         | Tfd      | Fault Input ↓ to PWM<br>I/O Change | —       |                                  | 50                  | ns                     |                                                                     |

| MP30         | Tfh      | Minimum Pulse Width                | 50      | _                                |                     | ns                     |                                                                     |

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

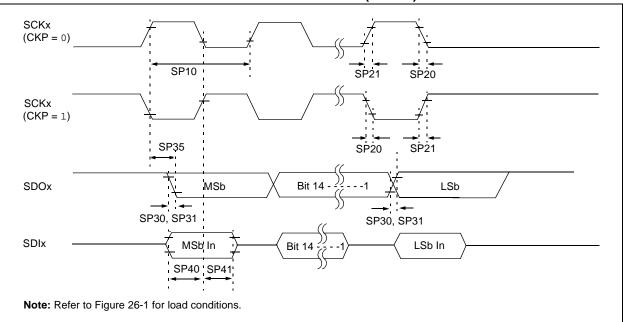

#### FIGURE 26-14: SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS FOR dsPIC33FJ16(GP/MC)10X

## TABLE 26-32:SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ16(GP/MC)10X

| AC CHA       | RACTERIS              | rics                                          | (unless o | I Operatin<br>otherwise<br>g temperat | <b>stated)</b><br>ture -40 | °C ≤ Ta ≤ | V to 3.6V<br>+85°C for Industrial<br>+125°C for Extended |

|--------------|-----------------------|-----------------------------------------------|-----------|---------------------------------------|----------------------------|-----------|----------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min       | Тур <sup>(2)</sup>                    | Max                        | Units     | Conditions                                               |

| SP10         | TscP                  | Maximum SCKx Frequency                        |           | _                                     | 10                         | MHz       | -40°C to +125°C,<br>see <b>Note 3</b>                    |

| SP20         | TscF                  | SCKx Output Fall Time                         | _         | —                                     | _                          | ns        | See Parameter DO32 and <b>Note 4</b>                     |

| SP21         | TscR                  | SCKx Output Rise Time                         | _         | —                                     | _                          | ns        | See Parameter DO31 and <b>Note 4</b>                     |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | _         |                                       | —                          | ns        | See Parameter DO32 and <b>Note 4</b>                     |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | _         |                                       | —                          | ns        | See Parameter DO31 and <b>Note 4</b>                     |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | _         | 6                                     | 20                         | ns        |                                                          |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge  | 30        | —                                     |                            | ns        |                                                          |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30        | _                                     |                            | ns        |                                                          |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge  | 30        | —                                     | —                          | ns        |                                                          |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

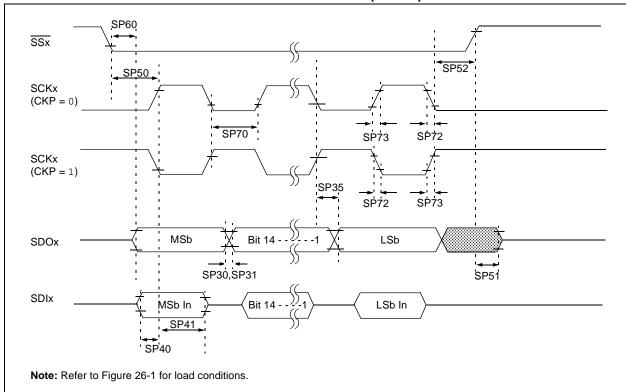

# TABLE 26-36:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS FOR dsPIC33FJ16(GP/MC)10X

| AC CH        | ARACTERIS             | TICS                                                         | Standard Op<br>(unless othe<br>Operating ter | erwise st          | t <b>ated)</b><br>e -40° | C ≤ TA ≤ | IV to 3.6V<br>+85°C for Industrial<br>+125°C for Extended |

|--------------|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|--------------------------|----------|-----------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                          | Тур <sup>(2)</sup> | Max                      | Units    | Conditions                                                |

| SP70         | TscP                  | Maximum SCKx Input Frequency                                 | _                                            |                    | 11                       | MHz      | See Note 3                                                |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —                                            | _                  | _                        | ns       | See Parameter DO32 and <b>Note 4</b>                      |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —                                            |                    |                          | ns       | See Parameter DO31 and <b>Note 4</b>                      |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | —                                            |                    |                          | ns       | See Parameter DO32 and <b>Note 4</b>                      |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —                                            |                    |                          | ns       | See Parameter DO31 and <b>Note 4</b>                      |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                            | 6                  | 20                       | ns       |                                                           |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                           | _                  | _                        | ns       |                                                           |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                           |                    |                          | ns       |                                                           |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                           | _                  | _                        | ns       |                                                           |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                          | —                  | —                        | ns       |                                                           |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                           | _                  | 50                       | ns       | See Note 4                                                |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                 | _                  | —                        | ns       | See Note 4                                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

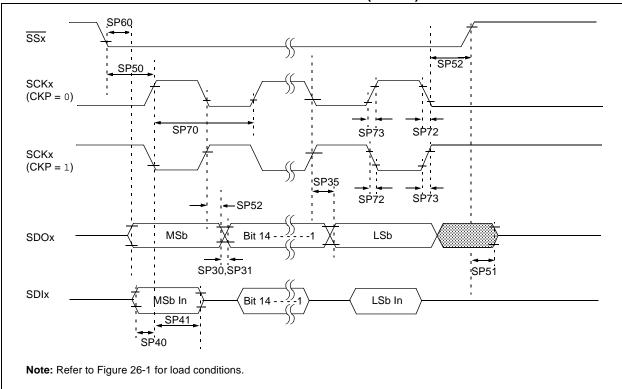

FIGURE 26-23: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

#### FIGURE 26-24: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS FOR dsPIC33FJ32(GP/MC)10X

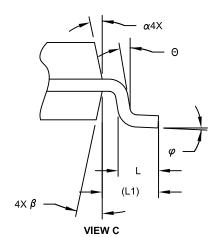

#### 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | Ν        | <b>/ILLIMETER</b> | S    |  |  |

|--------------------------|-------|----------|-------------------|------|--|--|

| Dimension Lin            | nits  | MIN      | NOM               | MAX  |  |  |

| Number of Pins           | N     |          | 18                |      |  |  |

| Pitch                    | е     |          | 1.27 BSC          |      |  |  |

| Overall Height           | Α     | -        | -                 | 2.65 |  |  |

| Molded Package Thickness | A2    | 2.05     | -                 | -    |  |  |

| Standoff §               | A1    | 0.10     | -                 | 0.30 |  |  |

| Overall Width            | E     |          | 10.30 BSC         |      |  |  |

| Molded Package Width     | E1    | 7.50 BSC |                   |      |  |  |

| Overall Length           | D     |          | 11.55 BSC         |      |  |  |

| Chamfer (Optional)       | h     | 0.25     | -                 | 0.75 |  |  |

| Foot Length              | L     | 0.40     | -                 | 1.27 |  |  |

| Footprint                | L1    | 1.40 REF |                   |      |  |  |

| Lead Angle               | Θ     | 0°       | -                 | -    |  |  |

| Foot Angle               | φ     | 0°       | -                 | 8°   |  |  |

| Lead Thickness           | с     | 0.20     | -                 | 0.33 |  |  |

| Lead Width               | b     | 0.31     | -                 | 0.51 |  |  |

| Mold Draft Angle Top     | α     | 5°       | -                 | 15°  |  |  |

| Mold Draft Angle Bottom  | β     | 5°       | -                 | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-051C Sheet 2 of 2

| ALCFGRPT (Alarm Configuration)248                                                |

|----------------------------------------------------------------------------------|

| ALRMVAL (Alarm Minutes and Seconds Value,                                        |

| ALRMPTR Bits = 00)                                                               |

| ALRMVAL (Alarm Month and Day Value,<br>ALRMPTR Bits = 10)252                     |

| ALKING TR DIS = 10)                                                              |

| ALRMPTR Bits = 01)253                                                            |

| CLKDIV (Clock Divisor)130                                                        |

| CMSTAT (Comparator Status)234                                                    |

| CMxCON (Comparator x Control)235                                                 |

| CMxFLTR (Comparator x Filter Control)241<br>CMxMSKCON (Comparator x Mask         |

| Gating Control)                                                                  |

| CMxMSKSRC (Comparator x Mask                                                     |

| Source Select)                                                                   |

| CORCON (Core Control) 42, 99                                                     |

| CTMUCON1 (CTMU Control 1)                                                        |

| CTMUCON2 (CTMU Control 2)                                                        |

| CTMUICON (CTMU Current Control)259<br>CVRCON (Comparator Voltage                 |

| Reference Control)                                                               |

| DEVID (Device ID)                                                                |

| DEVREV (Device Revision)                                                         |

| I2CxCON (I2Cx Control)                                                           |

| I2CxMSK (I2Cx Slave Mode Address Mask)                                           |

| I2CxSTAT (I2Cx Status)                                                           |

| ICxCON (Input Capture x Control)                                                 |

| IEC1 (Interrupt Enable Control 1)                                                |

| IEC2 (Interrupt Enable Control 2)                                                |

| IEC3 (Interrupt Enable Control 3)110                                             |

| IEC4 (Interrupt Enable Control 4)111                                             |

| IFS0 (Interrupt Flag Status 0)                                                   |

| IFS1 (Interrupt Flag Status 1) 105<br>IFS2 (Interrupt Flag Status 2) 106         |

| IFS3 (Interrupt Flag Status 3)                                                   |

| IFS4 (Interrupt Flag Status 4)                                                   |

| INTCON1 (Interrupt Control 1)100                                                 |

| INTCON2 (Interrupt Control 2)102                                                 |

| INTTREG (Interrupt Control and Status)123                                        |

| IPC0 (Interrupt Priority Control 0)                                              |

| IPC1 (Interrupt Priority Control 1)                                              |

| IPC15 (Interrupt Priority Control 15)                                            |

| IPC16 (Interrupt Priority Control 16)                                            |

| IPC19 (Interrupt Priority Control 19)122                                         |

| IPC2 (Interrupt Priority Control 2)114                                           |

| IPC3 (Interrupt Priority Control 3)                                              |

| IPC4 (Interrupt Priority Control 4)116<br>IPC5 (Interrupt Priority Control 5)117 |

| IPC6 (Interrupt Priority Control 6)                                              |

| IPC7 (Interrupt Priority Control 7)                                              |

| IPC9 (Interrupt Priority Control 9)119                                           |

| NVMCON (Flash Memory Control)85                                                  |

| NVMKEY (Nonvolatile Memory Key)85                                                |

| OCxCON (Output Compare x Control)                                                |

| OSCCON (Oscillator Control)                                                      |

| PADCFG1 (Pad Configuration Control)                                              |

| PMD1 (Peripheral Module Disable Control 1)                                       |

| PMD2 (Peripheral Module Disable Control 2)136                                    |

| PMD4 (Peripheral Module Disable Control 4) 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWMxCON1 (PWMx Control 1) 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PWMxCON2 (PWMx Control 2) 189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PWMxKEY (PWMx Unlock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PxDC1 (PWMx Duty Cycle 1) 195                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PxDC2 (PWMx Duty Cycle 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PxDC3 (PWMx Duty Cycle 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PxDTCON1 (PWMx Dead-Time Control 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PxDTCON2 (PWMx Dead-Time Control 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PxFLTACON (PWMx Fault A Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PxFLTBCON (PWMx Fault B Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PxOVDCON (PWMx Override Control) 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PxSECMP (PWMx Special Event Compare)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PxTCON (PWMx Time Base Control) 185                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PxTMR (PWMx Timer Count Value) 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PxTPER (PWMx Time Base Period) 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RCFGCAL (RTCC Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |