Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, POR, PWM, WDT                         |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (11K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 14x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32mc104t-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

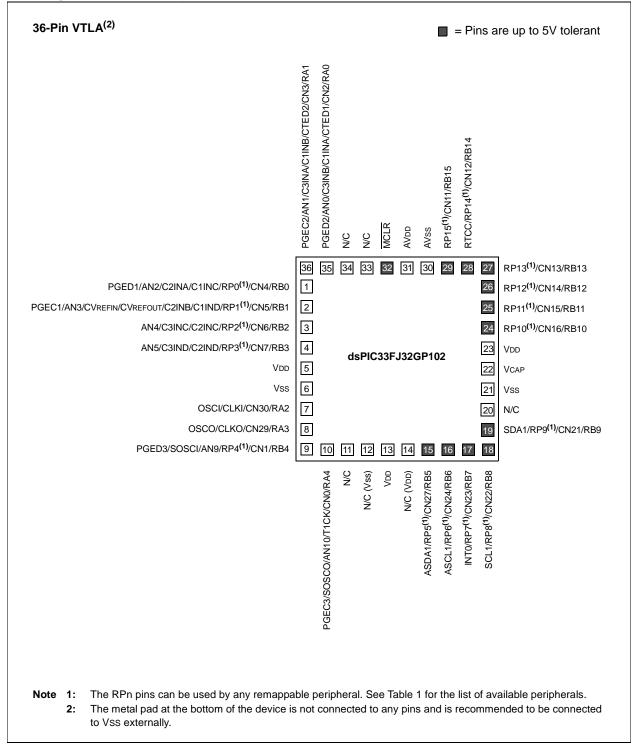

### Pin Diagrams (Continued)

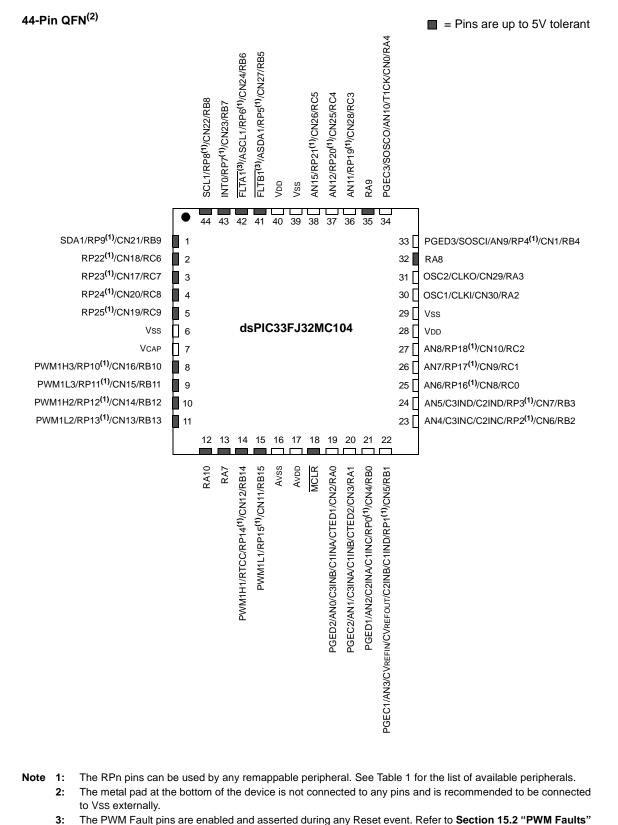

### Pin Diagrams (Continued)

3: The PWM Fault pins are enabled and asserted during any Reset event. Refer to Section 15.2 "PWM Faults" for more information on the PWM Faults.

| TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                   |           |                                                                                                                                       |  |

|------------------------------------------------|-------------|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                       | Pin<br>Type | Buffer<br>Type    | PPS       | Description                                                                                                                           |  |

| SCL1                                           | I/O         | ST                | No        | Synchronous serial clock input/output for I2C1.                                                                                       |  |

| SDA1                                           | I/O         | ST                | No        | Synchronous serial data input/output for I2C1.                                                                                        |  |

| ASCL1                                          | I/O         | ST                | No        | Alternate synchronous serial clock input/output for I2C1.                                                                             |  |

| ASDA1                                          | I/O         | ST                | No        | Alternate synchronous serial data input/output for I2C1.                                                                              |  |

| FLTA1(1,2,4)                                   | 1           | ST                | No        | PWM1 Fault A input.                                                                                                                   |  |

| FLTB1 <sup>(3,4)</sup>                         | 1           | ST                | No        | PWM1 Fault B input.                                                                                                                   |  |

| PWM1L1                                         | 0           |                   | No        | PWM1 Low Output 1.                                                                                                                    |  |

| PWM1H1                                         | 0           |                   | No        | PWM1 High Output 1.                                                                                                                   |  |

| PWM1L2                                         | 0           |                   | No        | PWM1 Low Output 2.                                                                                                                    |  |

| PWM1H2                                         | 0           |                   | No        | PWM1 High Output 2.                                                                                                                   |  |

| PWM1L3                                         | 0           |                   | No        | PWM1 Low Output 3.                                                                                                                    |  |

| PWM1H3                                         | Ō           | _                 | No        | PWM1 High Output 3.                                                                                                                   |  |

| RTCC                                           | 0           | Digital           | No        | RTCC Alarm output.                                                                                                                    |  |

| CTPLS                                          | 0           | Digital           | Yes       | CTMU pulse output.                                                                                                                    |  |

| CTED1                                          | I           | Digital           | No        | CTMU External Edge Input 1.                                                                                                           |  |

| CTED2                                          | I           | Digital           | No        | CTMU External Edge Input 2.                                                                                                           |  |

| CVREFIN                                        | I           | Analog            | No        | Comparator Voltage Positive Reference Input.                                                                                          |  |

| CVREFOUT                                       | 0           | Analog            | No        | Comparator Voltage Positive Reference Output.                                                                                         |  |

| C1INA                                          | I           | Analog            | No        | Comparator 1 Positive Input A.                                                                                                        |  |

| C1INB                                          | i           | Analog            | No        | Comparator 1 Negative Input B.                                                                                                        |  |

| C1INC                                          | i           | Analog            | No        | Comparator 1 Negative Input C.                                                                                                        |  |

| C1IND                                          | i           | Analog            | No        | Comparator 1 Negative Input D.                                                                                                        |  |

| C1OUT                                          | Ō           | Digital           | Yes       | Comparator 1 Output.                                                                                                                  |  |

| C2INA                                          | Ĩ           | Analog            | No        | Comparator 2 Positive Input A.                                                                                                        |  |

| C2INB                                          | l i         | Analog            | No        | Comparator 2 Negative Input B.                                                                                                        |  |

| C2INC                                          | i           | Analog            | No        | Comparator 2 Negative Input D.                                                                                                        |  |

| C2INC<br>C2IND                                 |             | Analog            | No        | Comparator 2 Negative Input C.                                                                                                        |  |

| C2OUT                                          | 0           | Digital           | Yes       | Comparator 2 Output.                                                                                                                  |  |

|                                                |             | •                 |           |                                                                                                                                       |  |

| C3INA                                          |             | Analog            | No        | Comparator 3 Positive Input A.                                                                                                        |  |

| C3INB                                          |             | Analog            | No        | Comparator 3 Negative Input B.                                                                                                        |  |

| C3INC                                          |             | Analog            | No        | Comparator 3 Negative Input C.                                                                                                        |  |

| C3IND<br>C3OUT                                 |             | Analog<br>Digital | No<br>Yes | Comparator 3 Negative Input D.<br>Comparator 3 Output.                                                                                |  |

|                                                |             | ST                |           | Data I/O pin for Programming/Debugging Communication Channel 1.                                                                       |  |

| PGED1                                          | I/O         |                   | No        |                                                                                                                                       |  |

| PGEC1                                          |             | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 1.                                                                    |  |

| PGED2                                          | I/O         | ST                | No        | Data I/O pin for Programming/Debugging Communication Channel 2.                                                                       |  |

| PGEC2                                          | I           | ST                | No        | Clock input pin for Programming/Debugging Communication Channel 2.                                                                    |  |

| PGED3<br>PGEC3                                 | I/O         | ST<br>ST          | No<br>No  | Data I/O pin for Programming/Debugging Communication Channel 3.<br>Clock input pin for Programming/Debugging Communication Channel 3. |  |

|                                                | - ·         |                   |           |                                                                                                                                       |  |

| MCLR                                           | I/P         | ST                | No        | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                            |  |

|                                                |             |                   |           | input or output Analog = Analog input P = Power                                                                                       |  |

| S                                              | I = Schr    | nitt Frigger      | input w   | ith CMOS levels O = Output I = Input                                                                                                  |  |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: An external pull-down resistor is required for the FLTA1 pin in dsPIC33FJXXMC101 (20-pin) devices.

- 2: The FLTA1 pin and the PWM1Lx/PWM1Hx pins are available in dsPIC(16/32)MC10X devices only.

- 3: The FLTB1 pin is available in dsPIC(16/32)MC102/104 devices only.

PPS = Peripheral Pin Select

- 4: The PWM Fault pins are enabled during any Reset event. Refer to **Section 15.2 "PWM Faults"** for more information on the PWM Faults.

- 5: Not all pins are available on all devices. Refer to the specific device in the "**Pin Diagrams**" section for availability.

- 6: These pins are available in dsPIC33FJ32(GP/MC)104 (44-pin) devices only.

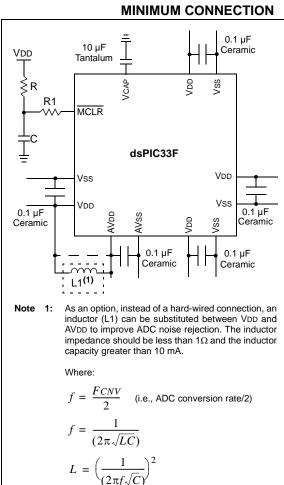

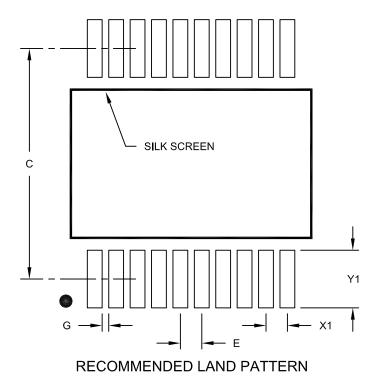

### FIGURE 2-1: RECOMMENDED

#### TANK CAPACITORS 2.2.1

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 µF to 47 µF.

#### 2.3 **CPU Logic Filter Capacitor Connection (VCAP)**

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7 µF and 10 µF, 16V connected to ground. The type can be ceramic or tantalum. Refer to Section 26.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to Section 23.2 "On-Chip Voltage Regulator" for details.

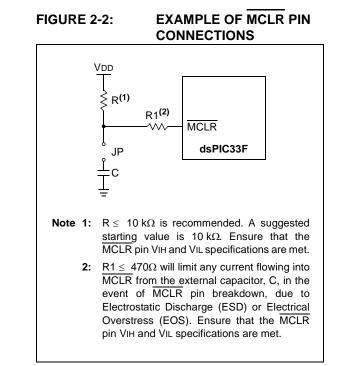

#### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

### 8.2 Oscillator Control Registers

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0           | R-0                                                                                          | R-0                                                                                                                                                       | R-0                                                                                       | U-0              | R/W-y                                | R/W-y                   | R/W-y                |  |  |  |

|---------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|--------------------------------------|-------------------------|----------------------|--|--|--|

| _             | COSC2                                                                                        | COSC1                                                                                                                                                     | COSC0                                                                                     | —                | NOSC2 <sup>(2)</sup>                 | NOSC1 <sup>(2)</sup>    | NOSC0 <sup>(2)</sup> |  |  |  |

| bit 15        |                                                                                              |                                                                                                                                                           |                                                                                           |                  | •                                    |                         | bit 8                |  |  |  |

| DAMA          | DAMO                                                                                         | <b>.</b>                                                                                                                                                  |                                                                                           | D/0 0            |                                      | DAMO                    | DAVA                 |  |  |  |

| R/W-0         | R/W-0                                                                                        | R-0                                                                                                                                                       | U-0                                                                                       | R/C-0            | U-0                                  | R/W-0                   | R/W-0                |  |  |  |

| CLKLOCK       | IOLOCK                                                                                       | LOCK                                                                                                                                                      |                                                                                           | CF               |                                      | LPOSCEN                 | OSWEN                |  |  |  |

| bit 7         |                                                                                              |                                                                                                                                                           |                                                                                           |                  |                                      |                         | bit (                |  |  |  |

| Legend:       |                                                                                              | C = Clearable                                                                                                                                             | e bit                                                                                     | y = Value set    | from Configura                       | tion bits on PO         | R                    |  |  |  |

| R = Readabl   | le bit                                                                                       | W = Writable                                                                                                                                              | bit                                                                                       | U = Unimpler     | mented bit, read                     | l as '0'                |                      |  |  |  |

| -n = Value at | t POR                                                                                        | '1' = Bit is set                                                                                                                                          |                                                                                           | '0' = Bit is cle | ared                                 | x = Bit is unkn         | iown                 |  |  |  |

|               |                                                                                              |                                                                                                                                                           |                                                                                           |                  |                                      |                         |                      |  |  |  |

| bit 15        | Unimplemen                                                                                   | ted: Read as '                                                                                                                                            | 0'                                                                                        |                  |                                      |                         |                      |  |  |  |

| bit 14-12     | COSC<2:0>:                                                                                   | Current Oscilla                                                                                                                                           | ator Selection                                                                            | bits (read-only  | )                                    |                         |                      |  |  |  |

|               | 101 = Low-Po<br>100 = Second<br>011 = Primary<br>010 = Primary<br>001 = Fast R               | C Oscillator (Fl<br>ower RC Oscill<br>dary Oscillator<br>y Oscillator (M<br>y Oscillator (M<br>C Oscillator (Fl<br>C Oscillator (Fl                       | ator (LPRC)<br>(SOSC)<br>S, EC) with PL<br>S, HS, EC)<br>RC) with Divid                   | L                | L (FRCPLL)                           |                         |                      |  |  |  |

| bit 11        | Unimplemen                                                                                   | ted: Read as '                                                                                                                                            | 0'                                                                                        |                  |                                      |                         |                      |  |  |  |

| bit 10-8      | NOSC<2:0>:                                                                                   | New Oscillator                                                                                                                                            | Selection bits                                                                            | <sub>S</sub> (2) |                                      |                         |                      |  |  |  |

|               | 110 = Fast R<br>101 = Low-Po<br>100 = Second<br>011 = Primar<br>010 = Primar<br>001 = Fast R | C Oscillator (FI<br>C Oscillator (FI<br>ower RC Oscill<br>dary Oscillator<br>y Oscillator (Mi<br>y Oscillator (Mi<br>C Oscillator (FI<br>C Oscillator (FI | RC) with Divid<br>ator (LPRC)<br>(SOSC)<br>S, EC) with PL<br>S, HS, EC)<br>RC) with Divid | le-by-16<br>_L   | L (FRCPLL)                           |                         |                      |  |  |  |

| bit 7         | CLKLOCK: C                                                                                   | lock Lock Ena                                                                                                                                             | ble bit                                                                                   |                  |                                      |                         |                      |  |  |  |

|               |                                                                                              | If Clock Switching is Enabled and FSCM is Disabled (FCKSM<1:0> (FOSC<7:6>) = 0b01):<br>1 = Clock switching is disabled, system clock source is locked     |                                                                                           |                  |                                      |                         |                      |  |  |  |

|               |                                                                                              |                                                                                                                                                           |                                                                                           |                  | n be modified by                     | / clock switchin        | a                    |  |  |  |

| bit 6         |                                                                                              | ipheral Pin Sel                                                                                                                                           | -                                                                                         |                  |                                      | ,                       | ~                    |  |  |  |

|               | 1 = Periphera                                                                                | al Pin Select is                                                                                                                                          | locked, a write                                                                           |                  | l Pin Select regi<br>eral Pin Select |                         |                      |  |  |  |

| bit 5         | LOCK: PLL L                                                                                  | ock Status bit                                                                                                                                            | (read-only)                                                                               |                  |                                      |                         |                      |  |  |  |

|               |                                                                                              | that PLL is in that PLL is ou                                                                                                                             |                                                                                           |                  | satisfied<br>progress or PLL         | is disabled             |                      |  |  |  |

| bit 4         | Unimplemen                                                                                   | ted: Read as '                                                                                                                                            | 0'                                                                                        |                  |                                      |                         |                      |  |  |  |

|               | /rites to this regis<br>dsPIC33/PIC24 F                                                      |                                                                                                                                                           |                                                                                           |                  | Oscillator (Part                     | t <b>VI)</b> " (DS7064∠ | 1) in the            |  |  |  |

|               | irect clock switch<br>his applies to cloc                                                    |                                                                                                                                                           |                                                                                           |                  |                                      |                         |                      |  |  |  |

mode as a transitional clock source between the two PLL modes.

# 10.4.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33FJ16(GP/MC)101/102 and dsPIC33FJ32(GP/ MC)101/102/104 devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

### 10.4.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |  |  |  |  |  |  |

|       | See MPLAB IDE Help for more information.                                                         |  |  |  |  |  |  |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

### 10.4.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

### 10.4.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

|                    | U-0                                                                     | U-0                                                                                                                             | R/W-1           | R/W-1            | R/W-1            | R/W-1           | R/W-1           |  |  |  |  |

|--------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-----------------|--|--|--|--|

| —                  | —                                                                       | —                                                                                                                               | T3CKR4          | T3CKR3           | T3CKR2           | T3CKR1          | T3CKR0          |  |  |  |  |

| bit 15             |                                                                         |                                                                                                                                 |                 |                  |                  |                 | bit 8           |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 | D/M/ 4          |  |  |  |  |

| U-0                | U-0                                                                     | U-0                                                                                                                             | R/W-1<br>T2CKR4 | R/W-1<br>T2CKR3  | R/W-1<br>T2CKR2  | R/W-1<br>T2CKR1 | R/W-1<br>T2CKR0 |  |  |  |  |

| bit 7              |                                                                         |                                                                                                                                 | 1201411         | 1201410          | 1201112          |                 | bit (           |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

| Legend:            |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

| R = Readab         | le bit                                                                  | W = Writable                                                                                                                    | bit             | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |  |

| -n = Value a       | t POR                                                                   | '1' = Bit is se                                                                                                                 | t               | '0' = Bit is cle | ared             | x = Bit is unkr | iown            |  |  |  |  |

|                    |                                                                         |                                                                                                                                 | ( - <b>1</b>    |                  |                  |                 |                 |  |  |  |  |

| bit 15-13          | -                                                                       | ted: Read as                                                                                                                    |                 |                  |                  |                 |                 |  |  |  |  |

| bit 12-8           |                                                                         | -                                                                                                                               | r3 External Clo | ck (T3CK) to t   | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | •                                                                       | 11111 = Input tied to Vss                                                                                                       |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 11110 = Res                                                             | erved                                                                                                                           |                 |                  |                  |                 |                 |  |  |  |  |

|                    | •                                                                       |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | •                                                                       |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 11010 = Reserved                                                        |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 11001 = Inpu                                                            | t tied to RP25                                                                                                                  |                 |                  |                  |                 |                 |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    |                                                                         |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | •                                                                       |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 00001 = Inpu                                                            |                                                                                                                                 |                 |                  |                  |                 |                 |  |  |  |  |

|                    | 00000 = Inpu                                                            | t tied to RP0                                                                                                                   |                 |                  |                  |                 |                 |  |  |  |  |

| bit 7-5            | 00000 = Inpu<br>Unimplemen                                              | t tied to RP0<br>ted: Read as                                                                                                   |                 |                  |                  |                 |                 |  |  |  |  |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen                                              | t tied to RP0<br>ted: Read as                                                                                                   |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                                        |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0>                                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                                        |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                                        |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu                | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Time<br>It tied to Vss                                                        |                 | ck (T2CK) to ti  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     |                 | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 3               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br>ted: Read as<br>: Assign Timer<br>It tied to Vss<br>erved                                                     | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

|                    | 00000 = Inpu<br>Unimplemen<br>T2CKR<4:0><br>11111 = Inpu<br>11110 = Res | It tied to RP0<br><b>ted:</b> Read as<br>: Assign Timer<br>It tied to Vss<br>erved<br>erved<br>t tied to RP25<br>tt tied to RP1 | r2 External Clo | ck (T2CK) to tl  | he Correspondi   | ng RPn Pin bits | 5               |  |  |  |  |

### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

NOTES:

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Stop bit has been detected last                                                                                       |

|       | 0 = Stop bit was not detected last                                                                                                         |

|       | Hardware sets or clears when Start, Repeated Start or Stop is detected.                                                                    |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware sets or clears when Start, Repeated Start or Stop is detected.                                                                    |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                          |

|       | <ul> <li>1 = Read – Indicates data transfer is output from slave</li> <li>0 = Write – Indicates data transfer is input to slave</li> </ul> |

|       | Hardware sets or clears after reception of an I <sup>2</sup> C device address byte.                                                        |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive is complete, I2CxRCV is full                                                                                                   |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                                                              |

|       | Hardware sets when I2CxRCV is written with received byte. Hardware clears when software reads I2CxRCV.                                     |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty                                                       |

|       | Hardware sets when software writes to I2CxTRN. Hardware clears at completion of data transmission.                                         |

## dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

| U-0             | U-0        | U-0                               | U-0           | U-0                                    | U-0                                | U-0                     | U-0   |  |  |

|-----------------|------------|-----------------------------------|---------------|----------------------------------------|------------------------------------|-------------------------|-------|--|--|

| _               | —          | _                                 | —             | —                                      | _                                  | —                       | _     |  |  |

| bit 15          |            |                                   |               |                                        |                                    |                         | bit 8 |  |  |

|                 |            |                                   |               |                                        |                                    |                         |       |  |  |

| U-0             | U-0        | U-0                               | U-0           | U-0                                    | U-0                                | R/W-0                   | U-0   |  |  |

| _               | —          | _                                 | —             | —                                      | _                                  | RTSECSEL <sup>(1)</sup> | _     |  |  |

| bit 7           |            |                                   |               |                                        |                                    |                         | bit 0 |  |  |

|                 |            |                                   |               |                                        |                                    |                         |       |  |  |

| Legend:         |            |                                   |               |                                        |                                    |                         |       |  |  |

| R = Readable    | bit        | W = Writable                      | bit           | U = Unimpler                           | U = Unimplemented bit, read as '0' |                         |       |  |  |

| -n = Value at P | POR        | '1' = Bit is set                  |               | '0' = Bit is cleared x = Bit is unknow |                                    |                         | own   |  |  |

|                 |            |                                   |               |                                        |                                    |                         |       |  |  |

| bit 15-2        | Unimplemen | ted: Read as '                    | 0'            |                                        |                                    |                         |       |  |  |

| bit 1           | RTSECSEL:  | RTCC Second                       | s Clock Outpu | ut Select bit <sup>(1)</sup>           |                                    |                         |       |  |  |

|                 |            | conds clock is<br>arm pulse is se |               |                                        |                                    |                         |       |  |  |

### REGISTER 21-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

bit 0 Unimplemented: Read as '0'

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>) bit needs to be set.

|                    | R/W-0                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                               | R/W-0                                                                                                        | R/W-0                                                              | R/W-0                                    | R/W-0           | R/W-0                  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------|-----------------|------------------------|--|--|

| ALRMEN             | CHIME                                                                                                                                                                                                                                                           | AMASK3                                                                                                                                                                                                                                              | AMASK2                                                                                                       | AMASK1                                                             | AMASK0                                   | ALRMPTR1        | ALRMPTR0               |  |  |

| bit 15             |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                     |                                                                                                              |                                                                    |                                          |                 | bit 8                  |  |  |

| R/W-0              | R/W-0                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                               | R/W-0                                                                                                        | R/W-0                                                              | R/W-0                                    | R/W-0           | R/W-0                  |  |  |

| ARPT7              | ARPT6                                                                                                                                                                                                                                                           | ARPT5                                                                                                                                                                                                                                               | ARPT4                                                                                                        | ARPT3                                                              | ARPT2                                    | ARPT1           | ARPT0                  |  |  |

| bit 7              |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                     | 1                                                                                                            |                                                                    |                                          |                 | bit (                  |  |  |

| Legend:            |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                     |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

| R = Readable       | e bit                                                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                        | bit                                                                                                          | U = Unimpler                                                       | mented bit, read                         | d as '0'        |                        |  |  |

| -n = Value at      | POR                                                                                                                                                                                                                                                             | '1' = Bit is set                                                                                                                                                                                                                                    |                                                                                                              | '0' = Bit is cle                                                   | ared                                     | x = Bit is unkr | nown                   |  |  |

| bit 15             |                                                                                                                                                                                                                                                                 | •                                                                                                                                                                                                                                                   | ed automatica                                                                                                | lly after an ala                                                   | irm event wher                           | never ARPT<7:   | 0> = 0x00 and          |  |  |

|                    | 0 = Alarm is                                                                                                                                                                                                                                                    | - /                                                                                                                                                                                                                                                 |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

| bit 14             | CHIME: Chir                                                                                                                                                                                                                                                     | ne Enable bit                                                                                                                                                                                                                                       |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

|                    |                                                                                                                                                                                                                                                                 | s enabled; ARP<br>s disabled; ARP                                                                                                                                                                                                                   |                                                                                                              |                                                                    |                                          | 00 to 0xFF      |                        |  |  |

| bit 13-10          | AMASK<3:0                                                                                                                                                                                                                                                       | >: Alarm Mask                                                                                                                                                                                                                                       | Configuration                                                                                                | bits                                                               |                                          |                 |                        |  |  |

|                    |                                                                                                                                                                                                                                                                 | y half second                                                                                                                                                                                                                                       | 0                                                                                                            |                                                                    |                                          |                 |                        |  |  |

|                    | 0001 = Every second                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                     |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

|                    | 0010 = Every 10 seconds                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                     |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

|                    | 0011 = Every minute                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                     |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

|                    | 0100 = Every 10 minutes<br>0101 = Every hour                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                     |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

|                    | 0110 = Once                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                   |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

|                    | 0111 = Onc                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                     |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

|                    |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                     |                                                                                                              |                                                                    |                                          |                 |                        |  |  |

|                    | 1000 = Once                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                     | twhen configu                                                                                                | rad for Eabrur                                                     | ny 20th anany                            | avery (1 veere) |                        |  |  |

|                    | 1000 = Once<br>1001 = Once                                                                                                                                                                                                                                      | e a year (excep                                                                                                                                                                                                                                     | -                                                                                                            | red for Februa                                                     | ary 29th, once e                         | every 4 years)  |                        |  |  |

|                    | 1000 = Onco<br>1001 = Onco<br>101x = Rese                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                     | ise                                                                                                          | red for Februa                                                     | ary 29th, once e                         | every 4 years)  |                        |  |  |

| bit 9-8            | 1000 = Once<br>1001 = Once<br>101x = Rese<br>11xx = Rese                                                                                                                                                                                                        | e a year (excep<br>erved – do not u<br>erved – do not u                                                                                                                                                                                             | ise                                                                                                          |                                                                    |                                          | every 4 years)  |                        |  |  |

| bit 9-8            | 1000 = Onco<br>1001 = Onco<br>101x = Reso<br>11xx = Reso<br>ALRMPTR<<br>Points to the                                                                                                                                                                           | e a year (excep<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Val<br>corresponding /                                                                                                                                                       | ise<br>ise<br>ue Register W<br>Alarm Value reg                                                               | indow Pointer<br>gisters when re                                   | bits<br>eading ALRMV4                    | LH and ALRM     |                        |  |  |

| bit 9-8            | 1000 = Once<br>1001 = Once<br>101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>the ALRMPT                                                                                                                                                             | e a year (excep<br>erved – do not u<br>erved – do not u<br><b>1:0&gt;:</b> Alarm Val<br>corresponding <i>i</i><br>R<1:0> value d                                                                                                                    | ise<br>ise<br>ue Register W<br>Alarm Value reg                                                               | indow Pointer<br>gisters when re                                   | bits<br>eading ALRMV4                    |                 |                        |  |  |

| bit 9-8            | 1000 = Onco<br>1001 = Onco<br>101x = Reso<br>11xx = Reso<br>ALRMPTR<<br>Points to the                                                                                                                                                                           | e a year (excep<br>erved – do not u<br>erved – do not u<br><b>1:0&gt;:</b> Alarm Val<br>corresponding /<br>R<1:0> value d<br><u>5:8&gt;:</u>                                                                                                        | ise<br>ise<br>ue Register W<br>Alarm Value reg                                                               | indow Pointer<br>gisters when re                                   | bits<br>eading ALRMV4                    | LH and ALRM     |                        |  |  |

| bit 9-8            | 1000 = Onco<br>1001 = Onco<br>101x = Reso<br>11xx = Reso<br>ALRMPTR<<br>Points to the<br>the ALRMPT<br>ALRMVAL<1<br>00 = ALRMM<br>01 = ALRMV                                                                                                                    | e a year (excep<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Val<br>corresponding /<br>R<1:0> value d<br><u>5:8&gt;:</u><br>/IN<br>VD                                                                                                     | ise<br>ise<br>ue Register W<br>Alarm Value reg                                                               | indow Pointer<br>gisters when re                                   | bits<br>eading ALRMV4                    | LH and ALRM     |                        |  |  |

| bit 9-8            | 1000 = Onco<br>1001 = Onco<br>101x = Reso<br><b>ALRMPTR&lt;</b><br>Points to the<br>the ALRMPT<br><u>ALRMVAL&lt;1</u><br>00 = ALRMM<br>01 = ALRMM<br>10 = ALRMM                                                                                                 | e a year (excep<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Val<br>corresponding /<br>R<1:0> value d<br><u>5:8&gt;:</u><br>/IN<br>VD<br>/NTH                                                                                             | ise<br>ise<br>ue Register W<br>Alarm Value reg                                                               | indow Pointer<br>gisters when re                                   | bits<br>eading ALRMV4                    | LH and ALRM     |                        |  |  |