## NXP USA Inc. - KMPC855TZQ80D4 Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 80MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (1), 10/100Mbps (1)                                             |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                      |

| Package / Case                  | 357-BBGA                                                               |

| Supplier Device Package         | 357-PBGA (25x25)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc855tzq80d4 |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

# 1 Overview

The MPC860 power quad integrated communications controller (PowerQUICC<sup>TM</sup>) is a versatile one-chip integrated microprocessor and peripheral combination designed for a variety of controller applications. It particularly excels in communications and networking systems. The PowerQUICC unit is referred to as the MPC860 in this hardware specification.

The MPC860 implements Power Architecture<sup>TM</sup> technology and contains a superset of Freescale's MC68360 quad integrated communications controller (QUICC), referred to here as the QUICC, RISC communications proceessor module (CPM). The CPU on the MPC860 is a 32-bit core built on Power Architecture technology that incorporates memory management units (MMUs) and instruction and data caches.. The CPM from the MC68360 QUICC has been enhanced by the addition of the inter-integrated controller (I<sup>2</sup>C) channel. The memory controller has been enhanced, enabling the MPC860 to support any type of memory, including high-performance memories and new types of DRAMs. A PCMCIA socket controller supports up to two sockets. A real-time clock has also been integrated.

Table 1 shows the functionality supported by the MPC860 family.

|          | Cache (              | Kbytes)    | Ethe    | ernet  |     |     |                        |  |

|----------|----------------------|------------|---------|--------|-----|-----|------------------------|--|

| Part     | Instruction<br>Cache | Data Cache | 10T     | 10/100 | АТМ | SCC | Reference <sup>1</sup> |  |

| MPC860DE | 4                    | 4          | Up to 2 | _      | _   | 2   | 1                      |  |

| MPC860DT | 4                    | 4          | Up to 2 | 1      | Yes | 2   | 1                      |  |

| MPC860DP | 16                   | 8          | Up to 2 | 1      | Yes | 2   | 1                      |  |

| MPC860EN | 4                    | 4          | Up to 4 | _      | _   | 4   | 1                      |  |

| MPC860SR | 4                    | 4          | Up to 4 | —      | Yes | 4   | 1                      |  |

| MPC860T  | 4                    | 4          | Up to 4 | 1      | Yes | 4   | 1                      |  |

| MPC860P  | 16                   | 8          | Up to 4 | 1      | Yes | 4   | 1                      |  |

| MPC855T  | 4                    | 4          | 1       | 1      | Yes | 1   | 2                      |  |

Table 1. MPC860 Family Functionality

Supporting documentation for these devices refers to the following:

1. MPC860 PowerQUICC Family User's Manual (MPC860UM, Rev. 3)

2. MPC855T User's Manual (MPC855TUM, Rev. 1)

Features

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC)

- Reset controller

- IEEE 1149.1<sup>TM</sup> Std. test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- 23 internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- 10/100 Mbps Ethernet support, fully compliant with the IEEE 802.3u® Standard (not available when using ATM over UTOPIA interface)

- ATM support compliant with ATM forum UNI 4.0 specification

- Cell processing up to 50–70 Mbps at 50-MHz system clock

- Cell multiplexing/demultiplexing

- Support of AAL5 and AAL0 protocols on a per-VC basis. AAL0 support enables OAM and software implementation of other protocols.

- ATM pace control (APC) scheduler, providing direct support for constant bit rate (CBR) and unspecified bit rate (UBR) and providing control mechanisms enabling software support of available bit rate (ABR)

- Physical interface support for UTOPIA (10/100-Mbps is not supported with this interface) and byte-aligned serial (for example, T1/E1/ADSL)

- UTOPIA-mode ATM supports level-1 master with cell-level handshake, multi-PHY (up to four physical layer devices), connection to 25-, 51-, or 155-Mbps framers, and UTOPIA/system clock ratios of 1/2 or 1/3.

- Serial-mode ATM connection supports transmission convergence (TC) function for T1/E1/ADSL lines, cell delineation, cell payload scrambling/descrambling, automatic idle/unassigned cell insertion/stripping, header error control (HEC) generation, checking, and statistics.

- Communications processor module (CPM)

- RISC communications processor (CP)

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8 Kbytes of dual-port RAM

- 16 serial DMA (SDMA) channels

- Three parallel I/O registers with open-drain capability

- Four baud-rate generators (BRGs)

- Independent (can be tied to any SCC or SMC)

- Allows changes during operation

- Autobaud support option

- Four serial communications controllers (SCCs)

- Ethernet/IEEE 802.3<sup>®</sup> standard optional on SCC1–4, supporting full 10-Mbps operation (available only on specially programmed devices)

- HDLC/SDLC (all channels supported at 2 Mbps)

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support point-to-point protocol (PPP)

- AppleTalk

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Binary synchronous communication (BISYNC)

- Totally transparent (bit streams)

- Totally transparent (frame-based with optional cyclic redundancy check (CRC))

- Two SMCs (serial management channels)

- UART

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division multiplexed (TDM) channels

- One SPI (serial peripheral interface)

- Supports master and slave modes

- Supports multimaster operation on the same bus

- One I<sup>2</sup>C (inter-integrated circuit) port

- Supports master and slave modes

- Multiple-master environment support

- Time-slot assigner (TSA)

- Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

# 9 Bus Signal Timing

Table 7 provides the bus operation timing for the MPC860 at 33, 40, 50, and 66 MHz.

The maximum bus speed supported by the MPC860 is 66 MHz. Higher-speed parts must be operated in half-speed bus mode (for example, an MPC860 used at 80 MHz must be configured for a 40-MHz bus).

The timing for the MPC860 bus shown assumes a 50-pF load for maximum delays and a 0-pF load for minimum delays.

| Num              | Characteristic                                                                            | 33    | MHz   | 40 MHz |       | 50 I  | MHz   | 66 MHz |       | Unit |

|------------------|-------------------------------------------------------------------------------------------|-------|-------|--------|-------|-------|-------|--------|-------|------|

| Num              | Characteristic                                                                            | Min   | Max   | Min    | Max   | Min   | Max   | Min    | Max   | Unit |

| B1               | CLKOUT period                                                                             | 30.30 | 30.30 | 25.00  | 30.30 | 20.00 | 30.30 | 15.15  | 30.30 | ns   |

| B1a              | EXTCLK to CLKOUT phase skew<br>(EXTCLK > 15 MHz and MF <= 2)                              | -0.90 | 0.90  | -0.90  | 0.90  | -0.90 | 0.90  | -0.90  | 0.90  | ns   |

| B1b              | EXTCLK to CLKOUT phase skew<br>(EXTCLK > 10 MHz and MF < 10)                              | -2.30 | 2.30  | -2.30  | 2.30  | -2.30 | 2.30  | -2.30  | 2.30  | ns   |

| B1c              | CLKOUT phase jitter (EXTCLK > 15 MHz and MF <= $2$ ) <sup>1</sup>                         | -0.60 | 0.60  | -0.60  | 0.60  | -0.60 | 0.60  | -0.60  | 0.60  | ns   |

| B1d              | CLKOUT phase jitter <sup>1</sup>                                                          | -2.00 | 2.00  | -2.00  | 2.00  | -2.00 | 2.00  | -2.00  | 2.00  | ns   |

| B1e              | CLKOUT frequency jitter (MF < 10) <sup>1</sup>                                            | —     | 0.50  | —      | 0.50  | —     | 0.50  | —      | 0.50  | %    |

| B1f              | CLKOUT frequency jitter (10 < MF < 500) <sup>1</sup>                                      | —     | 2.00  | —      | 2.00  | —     | 2.00  | —      | 2.00  | %    |

| B1g              | CLKOUT frequency jitter (MF > 500) <sup>1</sup>                                           | —     | 3.00  | —      | 3.00  | —     | 3.00  | —      | 3.00  | %    |

| B1h              | Frequency jitter on EXTCLK <sup>2</sup>                                                   | _     | 0.50  |        | 0.50  |       | 0.50  |        | 0.50  | %    |

| B2               | CLKOUT pulse width low                                                                    | 12.12 | —     | 10.00  | —     | 8.00  | —     | 6.06   | _     | ns   |

| B3               | CLKOUT width high                                                                         | 12.12 | —     | 10.00  | _     | 8.00  | —     | 6.06   | _     | ns   |

| B4               | CLKOUT rise time <sup>3</sup>                                                             | —     | 4.00  | —      | 4.00  | —     | 4.00  | —      | 4.00  | ns   |

| B5 <sup>33</sup> | CLKOUT fall time <sup>3</sup>                                                             | —     | 4.00  | —      | 4.00  | —     | 4.00  | —      | 4.00  | ns   |

| B7               | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3) invalid                | 7.58  | —     | 6.25   | —     | 5.00  | —     | 3.80   | —     | ns   |

| B7a              | CLKOUT to TSIZ(0:1), REG, RSV, AT(0:3), BDIP, PTR invalid                                 | 7.58  | —     | 6.25   | —     | 5.00  | —     | 3.80   | —     | ns   |

| B7b              | CLKOUT to BR, BG, FRZ, VFLS(0:1),<br>VF(0:2) IWP(0:2), LWP(0:1), STS invalid <sup>4</sup> | 7.58  | —     | 6.25   | —     | 5.00  | —     | 3.80   | —     | ns   |

| B8               | CLKOUT to A(0:31), BADDR(28:30)<br>RD/WR, BURST, D(0:31), DP(0:3) valid                   | 7.58  | 14.33 | 6.25   | 13.00 | 5.00  | 11.75 | 3.80   | 10.04 | ns   |

| B8a              | CLKOUT to TSIZ(0:1), REG, RSV, AT(0:3)<br>BDIP, PTR valid                                 | 7.58  | 14.33 | 6.25   | 13.00 | 5.00  | 11.75 | 3.80   | 10.04 | ns   |

| B8b              | CLKOUT to BR, BG, VFLS(0:1), VF(0:2),<br>IWP(0:2), FRZ, LWP(0:1), STS valid <sup>4</sup>  | 7.58  | 14.33 | 6.25   | 13.00 | 5.00  | 11.75 | 3.80   | 10.04 | ns   |

Table 7. Bus Operation Timings

|      | Characteristic                                                                                                                                  | 33    | MHz   | 40 I  | MHz   | 1Hz 50 MHz |       | 66 MHz |       | 11   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|------------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                  | Min   | Max   | Min   | Max   | Min        | Мах   | Min    | Мах   | Unit |

| B23  | CLKOUT rising edge to $\overline{\text{CS}}$ negated GPCM<br>read access, GPCM write access ACS = 00,<br>TRLX = 0, and CSNT = 0                 | 2.00  | 8.00  | 2.00  | 8.00  | 2.00       | 8.00  | 2.00   | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 10, TRLX = 0                                                                    | 5.58  | —     | 4.25  | _     | 3.00       | —     | 1.79   | _     | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 11, TRLX = 0                                                                    | 13.15 | —     | 10.50 | _     | 8.00       | _     | 5.58   | —     | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}$ (0:3) asserted                                                                          | _     | 9.00  | _     | 9.00  | —          | 9.00  | _      | 9.00  | ns   |

| B26  | CLKOUT rising edge to OE negated                                                                                                                | 2.00  | 9.00  | 2.00  | 9.00  | 2.00       | 9.00  | 2.00   | 9.00  | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 10, TRLX = 1                                                                    | 35.88 | _     | 29.25 | _     | 23.00      | —     | 16.94  | _     | ns   |

| B27a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 11, TRLX = 1                                                                    | 43.45 | —     | 35.50 | —     | 28.00      | —     | 20.73  | —     | ns   |

| B28  | CLKOUT rising edge to $\overline{WE}(0:3)$ negated<br>GPCM write access CSNT = 0                                                                | _     | 9.00  | _     | 9.00  | —          | 9.00  | _      | 9.00  | ns   |

| B28a | CLKOUT falling edge to $\overline{WE}(0:3)$ negated<br>GPCM write access TRLX = 0, 1, CSNT = 1,<br>EBDF = 0                                     | 7.58  | 14.33 | 6.25  | 13.00 | 5.00       | 11.75 | 3.80   | 10.54 | ns   |

| B28b | CLKOUT falling edge to $\overline{CS}$ negated GPCM<br>write access TRLX = 0, 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0                   | _     | 14.33 | _     | 13.00 | _          | 11.75 | —      | 10.54 | ns   |

| B28c | CLKOUT falling edge to $\overline{WE}$ (0:3) negated<br>GPCM write access TRLX = 0, 1, CSNT = 1<br>write access TRLX = 0, CSNT = 1,<br>EBDF = 1 | 10.86 | 17.99 | 8.88  | 16.00 | 7.00       | 14.13 | 5.18   | 12.31 | ns   |

| B28d | CLKOUT falling edge to $\overline{CS}$ negated GPCM<br>write access TRLX = 0, 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                   | _     | 17.99 | —     | 16.00 | —          | 14.13 | —      | 12.31 | ns   |

| B29  | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access CSNT = 0, EBDF = 0                                                 | 5.58  | —     | 4.25  | —     | 3.00       | —     | 1.79   | —     | ns   |

| B29a | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>EBDF = 0                                   | 13.15 | —     | 10.5  | —     | 8.00       | —     | 5.58   |       | ns   |

| B29b | $\overline{CS}$ negated to D(0:31), DP(0:3), High-Z<br>GPCM write access, ACS = 00, TRLX = 0, 1,<br>and CSNT = 0                                | 5.58  |       | 4.25  |       | 3.00       |       | 1.79   |       | ns   |

| B29c | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0          | 13.15 |       | 10.5  |       | 8.00       |       | 5.58   |       | ns   |

# Table 7. Bus Operation Timings (continued)

|      | Charactoristic                                                                                                                        | 33 MHz 40 M |       | MHz 50 MHz |       | MHz   | 66 MHz |      | 11    |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|------------|-------|-------|--------|------|-------|------|

| Num  | Characteristic                                                                                                                        | Min         | Max   | Min        | Max   | Min   | Max    | Min  | Max   | Unit |

| B31a | CLKOUT falling edge to CS valid—as requested by control bit CST1 in the corresponding word in UPM                                     | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid—as requested by control bit CST2 in the corresponding word in UPM                         | 1.50        | 8.00  | 1.50       | 8.00  | 1.50  | 8.00   | 1.50 | 8.00  | ns   |

| B31c | CLKOUT rising edge to $\overline{CS}$ valid—as requested by control bit CST3 in the corresponding word in UPM                         | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.04 | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$ valid—as<br>requested by control bit CST1 in the<br>corresponding word in UPM, EBDF = 1        | 13.26       | 17.99 | 11.28      | 16.00 | 9.40  | 14.13  | 7.58 | 12.31 | ns   |

| B32  | CLKOUT falling edge to BS valid—as<br>requested by control bit BST4 in the<br>corresponding word in UPM                               | 1.50        | 6.00  | 1.50       | 6.00  | 1.50  | 6.00   | 1.50 | 6.00  | ns   |

| B32a | CLKOUT falling edge to $\overline{\text{BS}}$ valid—as<br>requested by control bit BST1 in the<br>corresponding word in UPM, EBDF = 0 | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B32b | CLKOUT rising edge to BS valid—as<br>requested by control bit BST2 in the<br>corresponding word in UPM                                | 1.50        | 8.00  | 1.50       | 8.00  | 1.50  | 8.00   | 1.50 | 8.00  | ns   |

| B32c | CLKOUT rising edge to $\overline{\text{BS}}$ valid—as requested by control bit BST3 in the corresponding word in UPM                  | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B32d | CLKOUT falling edge to $\overline{BS}$ valid—as<br>requested by control bit BST1 in the<br>corresponding word in UPM, EBDF = 1        | 13.26       | 17.99 | 11.28      | 16.00 | 9.40  | 14.13  | 7.58 | 12.31 | ns   |

| B33  | CLKOUT falling edge to GPL valid—as<br>requested by control bit GxT4 in the<br>corresponding word in UPM                              | 1.50        | 6.00  | 1.50       | 6.00  | 1.50  | 6.00   | 1.50 | 6.00  | ns   |

| B33a | CLKOUT rising edge to GPL valid—as<br>requested by control bit GxT3 in the<br>corresponding word in UPM                               | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B34  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST4 in the corresponding word in UPM         | 5.58        |       | 4.25       |       | 3.00  |        | 1.79 | —     | ns   |

| B34a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST1 in the corresponding word in UPM         | 13.15       |       | 10.50      |       | 8.00  |        | 5.58 | _     | ns   |

| B34b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST2 in the corresponding word in UPM         | 20.73       | _     | 16.75      |       | 13.00 |        | 9.36 | _     | ns   |

# Table 7. Bus Operation Timings (continued)

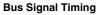

Figure 3 is the control timing diagram.

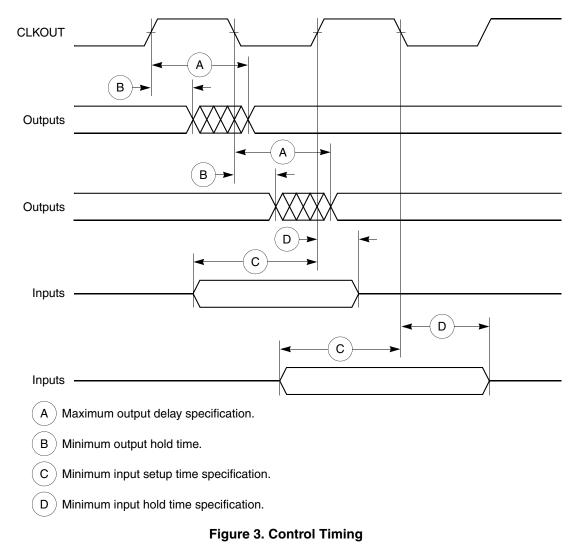

Figure 4 provides the timing for the external clock.

Figure 4. External Clock Timing

#### Bus Signal Timing

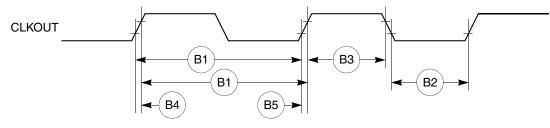

Figure 9 provides the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

Figure 9. Input Data Timing when Controlled by UPM in the Memory Controller and DLT3 = 1

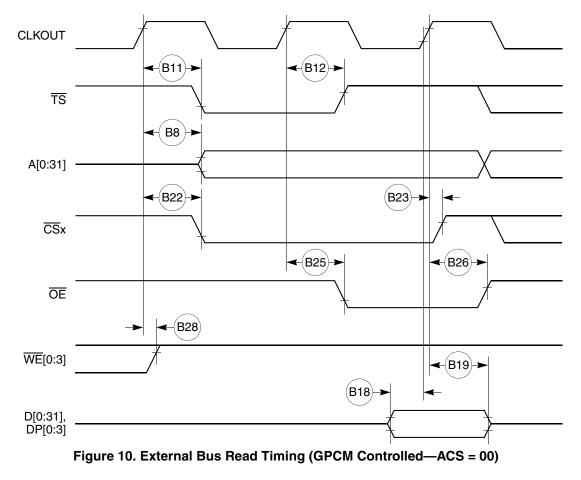

Figure 10 through Figure 13 provide the timing for the external bus read controlled by various GPCM factors.

1

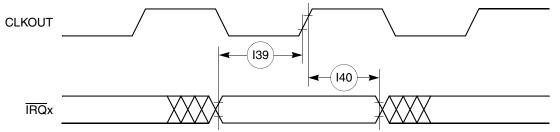

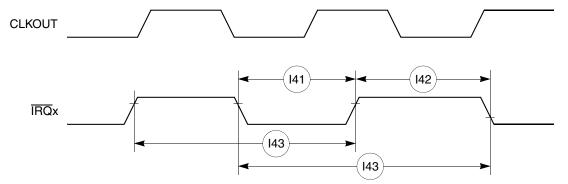

Table 8 provides interrupt timing for the MPC860.

### Table 8. Interrupt Timing

| Num | Characteristic <sup>1</sup>                   | All Freq                | Unit |      |

|-----|-----------------------------------------------|-------------------------|------|------|

| Num | Characteristic                                | Min                     | Мах  | Unit |

| 139 | IRQx valid to CLKOUT rising edge (setup time) | 6.00                    | —    | ns   |

| 140 | IRQx hold time after CLKOUT                   | 2.00                    | —    | ns   |

| 141 | IRQx pulse width low                          | 3.00                    | —    | ns   |

| 142 | IRQx pulse width high                         | 3.00                    | —    | ns   |

| 143 | IRQx edge-to-edge time                        | $4 \times T_{CLOCKOUT}$ | —    | —    |

The timings I39 and I40 describe the testing conditions under which the IRQ lines are tested when being defined as level-sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT.

The timings I41, I42, and I43 are specified to allow the correct function of the IRQ lines detection circuitry and have no direct relation with the total system interrupt latency that the MPC860 is able to support.

Figure 23 provides the interrupt detection timing for the external level-sensitive lines.

Figure 23. Interrupt Detection Timing for External Level Sensitive Lines

Figure 24 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 24. Interrupt Detection Timing for External Edge Sensitive Lines

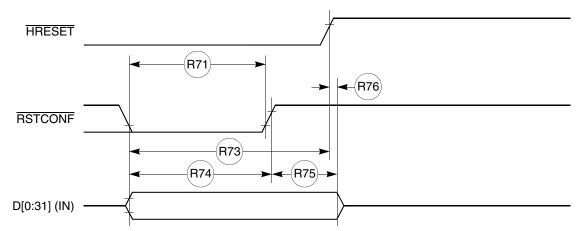

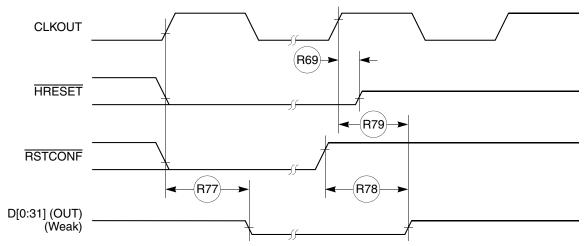

Table 12 shows the reset timing for the MPC860.

Table 12. Reset Timing

| Num | Characteristic                                                                             | 33 N   | /Hz   | 40 N   | ЛНz   | 50 MHz |       | 66 MHz |       | Unit |

|-----|--------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| NUM | Characteristic                                                                             | Min    | Мах   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| R69 | CLKOUT to HRESET high impedance                                                            | —      | 20.00 | —      | 20.00 | _      | 20.00 | —      | 20.00 | ns   |

| R70 | CLKOUT to SRESET high impedance                                                            | —      | 20.00 | —      | 20.00 | —      | 20.00 | —      | 20.00 | ns   |

| R71 | RSTCONF pulse width                                                                        | 515.15 | _     | 425.00 |       | 340.00 | _     | 257.58 | —     | ns   |

| R72 | _                                                                                          | —      | _     | —      | _     | —      | _     | —      | —     |      |

| R73 | Configuration data to HRESET rising edge setup time                                        | 504.55 | —     | 425.00 | —     | 350.00 | _     | 277.27 | —     | ns   |

| R74 | Configuration data to RSTCONF rising edge setup time                                       | 350.00 | —     | 350.00 | —     | 350.00 | _     | 350.00 | —     | ns   |

| R75 | Configuration data hold time after<br>RSTCONF negation                                     | 0.00   | —     | 0.00   | —     | 0.00   | _     | 0.00   | —     | ns   |

| R76 | Configuration data hold time after<br>HRESET negation                                      | 0.00   | —     | 0.00   | —     | 0.00   | _     | 0.00   | —     | ns   |

| R77 | HRESET and RSTCONF asserted to data out drive                                              | —      | 25.00 |        | 25.00 | —      | 25.00 | —      | 25.00 | ns   |

| R78 | RSTCONF negated to data out high impedance                                                 | —      | 25.00 | —      | 25.00 | —      | 25.00 | —      | 25.00 | ns   |

| R79 | CLKOUT of last rising edge before chip<br>three-state HRESET to data out high<br>impedance | —      | 25.00 | —      | 25.00 | —      | 25.00 | —      | 25.00 | ns   |

| R80 | DSDI, DSCK setup                                                                           | 90.91  | _     | 75.00  | _     | 60.00  |       | 45.45  | —     | ns   |

| R81 | DSDI, DSCK hold time                                                                       | 0.00   | _     | 0.00   |       | 0.00   |       | 0.00   | —     | ns   |

| R82 | SRESET negated to CLKOUT rising edge for DSDI and DSCK sample                              | 242.42 | —     | 200.00 | —     | 160.00 | _     | 121.21 | —     | ns   |

#### **Bus Signal Timing**

Figure 32 shows the reset timing for the data bus configuration.

Figure 32. Reset Timing—Configuration from Data Bus

Figure 33 provides the reset timing for the data bus weak drive during configuration.

Figure 33. Reset Timing—Data Bus Weak Drive During Configuration

**CPM Electrical Characteristics**

# **11 CPM Electrical Characteristics**

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC860.

# 11.1 PIP/PIO AC Electrical Specifications

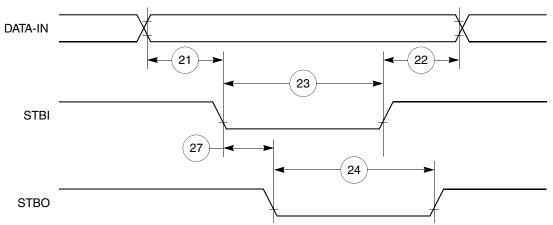

Table 14 provides the PIP/PIO AC timings as shown in Figure 39 through Figure 43.

# Table 14. PIP/PIO Timing

| Num | Characteristic                                                       | All Freq              | uencies | Unit |

|-----|----------------------------------------------------------------------|-----------------------|---------|------|

| Num | Characteristic                                                       | Min                   | Max     | onin |

| 21  | Data-in setup time to STBI low                                       | 0                     | _       | ns   |

| 22  | Data-in hold time to STBI high                                       | 2.5 - t3 <sup>1</sup> | —       | CLK  |

| 23  | STBI pulse width                                                     | 1.5                   | _       | CLK  |

| 24  | STBO pulse width                                                     | 1 CLK – 5 ns          | _       | ns   |

| 25  | Data-out setup time to STBO low                                      | 2                     | _       | CLK  |

| 26  | Data-out hold time from STBO high                                    | 5                     | _       | CLK  |

| 27  | STBI low to STBO low (Rx interlock)                                  | —                     | 2       | CLK  |

| 28  | STBI low to STBO high (Tx interlock)                                 | 2                     | _       | CLK  |

| 29  | Data-in setup time to clock high                                     | 15                    | _       | ns   |

| 30  | Data-in hold time from clock high                                    | 7.5                   | _       | ns   |

| 31  | Clock low to data-out valid (CPU writes data, control, or direction) | —                     | 25      | ns   |

<sup>1</sup> t3 = Specification 23.

Figure 39. PIP Rx (Interlock Mode) Timing Diagram

**CPM Electrical Characteristics**

**CPM Electrical Characteristics**

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

**CPM Electrical Characteristics**

**CPM Electrical Characteristics**

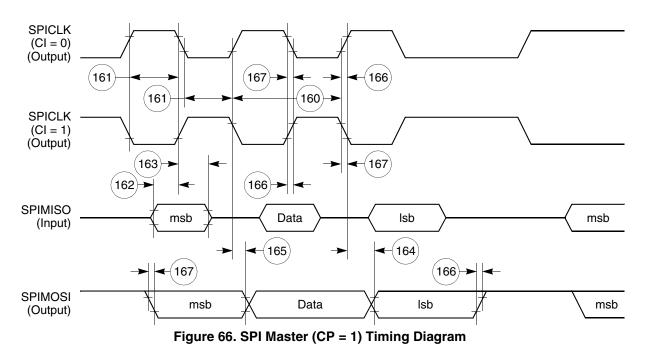

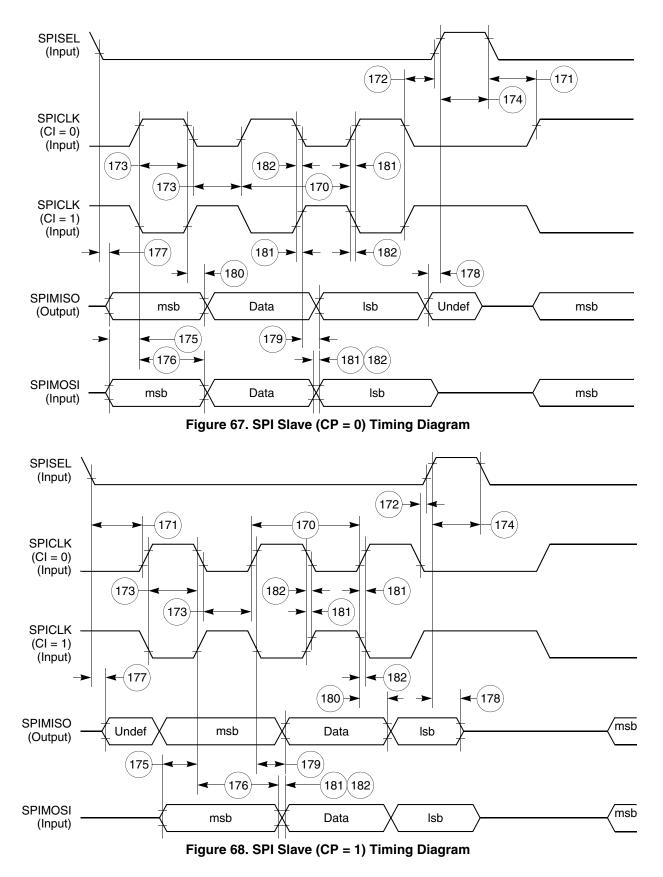

# **11.11 SPI Slave AC Electrical Specifications**

Table 25 provides the SPI slave timings as shown in Figure 67 and Figure 68.

# Table 25. SPI Slave Timing

| Num | Characteristic                                              | All Freq | uencies | Unit             |

|-----|-------------------------------------------------------------|----------|---------|------------------|

| Num | Characteristic                                              | Min      | Мах     | Omi              |

| 170 | Slave cycle time                                            | 2        | —       | t <sub>cyc</sub> |

| 171 | Slave enable lead time                                      | 15       | —       | ns               |

| 172 | Slave enable lag time                                       | 15       | —       | ns               |

| 173 | Slave clock (SPICLK) high or low time                       | 1        | —       | t <sub>cyc</sub> |

| 174 | Slave sequential transfer delay (does not require deselect) | 1        | —       | t <sub>cyc</sub> |

| 175 | Slave data setup time (inputs)                              | 20       | —       | ns               |

| 176 | Slave data hold time (inputs)                               | 20       | —       | ns               |

| 177 | Slave access time                                           | _        | 50      | ns               |

**CPM Electrical Characteristics**

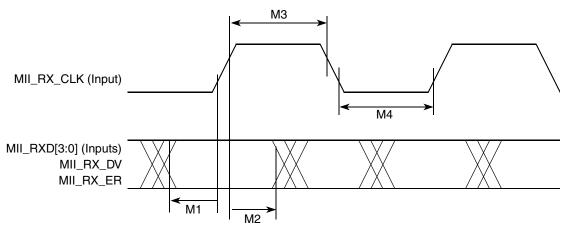

# **13 FEC Electrical Characteristics**

This section provides the AC electrical specifications for the Fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 V or 3.3 V.

# 13.1 MII Receive Signal Timing (MII\_RXD[3:0], MII\_RX\_DV, MII\_RX\_ER, MII\_RX\_CLK)

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency - 1%.

Table 29 provides information on the MII receive signal timing.

| Num | Characteristic                                         | Min | Max | Unit                 |

|-----|--------------------------------------------------------|-----|-----|----------------------|

| M1  | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup | 5   | _   | ns                   |

| M2  | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold  | 5   | _   | ns                   |

| М3  | MII_RX_CLK pulse width high                            | 35% | 65% | MII_RX_CLK<br>period |

| M4  | MII_RX_CLK pulse width low                             | 35% | 65% | MII_RX_CLK<br>period |

# Table 29. Mll Receive Signal Timing

Figure 72 shows MII receive signal timing.

Figure 72. MII Receive Signal Timing Diagram

#### Mechanical Data and Ordering Information

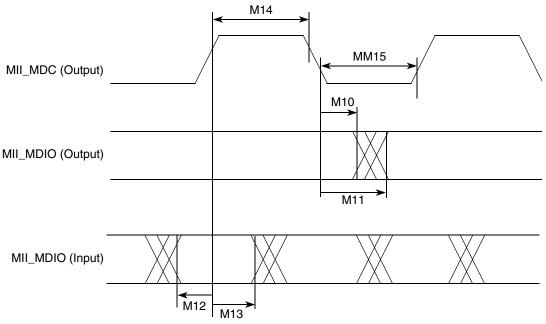

Figure 75 shows the MII serial management channel timing diagram.

Figure 75. MII Serial Management Channel Timing Diagram

# 14 Mechanical Data and Ordering Information

# 14.1 Ordering Information

Table 33 provides information on the MPC860 Revision D.4 derivative devices.

| Device   | Number of<br>SCCs <sup>1</sup> | Ethernet Support <sup>2</sup><br>(Mbps) | Multichannel<br>HDLC Support | ATM<br>Support |

|----------|--------------------------------|-----------------------------------------|------------------------------|----------------|

| MPC855T  | 1                              | 10/100                                  | Yes                          | Yes            |

| MPC860DE | 2                              | 10                                      | N/A                          | N/A            |

| MPC860DT |                                | 10/100                                  | Yes                          | Yes            |

| MPC860DP |                                | 10/100                                  | Yes                          | Yes            |

| MPC860EN | 4                              | 10                                      | N/A                          | N/A            |

| MPC860SR |                                | 10                                      | Yes                          | Yes            |

| MPC860T  |                                | 10/100                                  | Yes                          | Yes            |

| MPC860P  |                                | 10/100                                  | Yes                          | Yes            |

Table 33. MPC860 Family Revision D.4 Derivatives

<sup>1</sup> Serial communications controller (SCC)

<sup>2</sup> Up to 4 channels at 40 MHz or 2 channels at 25 MHz

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC, QorlQ, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. CoreNet, QorlQ Qonverge, QUICC Engine, and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2007-2015 Freescale Semiconductor, Inc.

Power

Document Number: MPC860EC Rev. 10 09/2015