#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                 |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 50MHz                                                                    |

| Co-Processors/DSP               | Communications; CPM                                                      |

| RAM Controllers                 | DRAM                                                                     |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers |                                                                          |

| Ethernet                        | 10Mbps (2)                                                               |

| SATA                            | -                                                                        |

| USB                             | -                                                                        |

| Voltage - I/O                   | 3.3V                                                                     |

| Operating Temperature           | -40°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                        |

| Package / Case                  | 357-BBGA                                                                 |

| Supplier Device Package         | 357-PBGA (25x25)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc860deczq50d4 |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC)

- Reset controller

- IEEE 1149.1<sup>TM</sup> Std. test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- 23 internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- 10/100 Mbps Ethernet support, fully compliant with the IEEE 802.3u® Standard (not available when using ATM over UTOPIA interface)

- ATM support compliant with ATM forum UNI 4.0 specification

- Cell processing up to 50–70 Mbps at 50-MHz system clock

- Cell multiplexing/demultiplexing

- Support of AAL5 and AAL0 protocols on a per-VC basis. AAL0 support enables OAM and software implementation of other protocols.

- ATM pace control (APC) scheduler, providing direct support for constant bit rate (CBR) and unspecified bit rate (UBR) and providing control mechanisms enabling software support of available bit rate (ABR)

- Physical interface support for UTOPIA (10/100-Mbps is not supported with this interface) and byte-aligned serial (for example, T1/E1/ADSL)

- UTOPIA-mode ATM supports level-1 master with cell-level handshake, multi-PHY (up to four physical layer devices), connection to 25-, 51-, or 155-Mbps framers, and UTOPIA/system clock ratios of 1/2 or 1/3.

- Serial-mode ATM connection supports transmission convergence (TC) function for T1/E1/ADSL lines, cell delineation, cell payload scrambling/descrambling, automatic idle/unassigned cell insertion/stripping, header error control (HEC) generation, checking, and statistics.

- Communications processor module (CPM)

- RISC communications processor (CP)

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8 Kbytes of dual-port RAM

- 16 serial DMA (SDMA) channels

- Three parallel I/O registers with open-drain capability

- Four baud-rate generators (BRGs)

- Independent (can be tied to any SCC or SMC)

- Allows changes during operation

- Autobaud support option

- Four serial communications controllers (SCCs)

- Ethernet/IEEE 802.3<sup>®</sup> standard optional on SCC1–4, supporting full 10-Mbps operation (available only on specially programmed devices)

- HDLC/SDLC (all channels supported at 2 Mbps)

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support point-to-point protocol (PPP)

- AppleTalk

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Binary synchronous communication (BISYNC)

- Totally transparent (bit streams)

- Totally transparent (frame-based with optional cyclic redundancy check (CRC))

- Two SMCs (serial management channels)

- UART

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division multiplexed (TDM) channels

- One SPI (serial peripheral interface)

- Supports master and slave modes

- Supports multimaster operation on the same bus

- One I<sup>2</sup>C (inter-integrated circuit) port

- Supports master and slave modes

- Multiple-master environment support

- Time-slot assigner (TSA)

- Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

### Table 4 shows the thermal characteristics for the MPC860.

### Table 4. MPC860 Thermal Resistance Data

| Rating                           | Environment          |                         | Symbol              | ZP<br>MPC860P | ZQ / VR<br>MPC860P | Unit |

|----------------------------------|----------------------|-------------------------|---------------------|---------------|--------------------|------|

| Mold Compound Thicknes           | 0.85                 | 1.15                    | mm                  |               |                    |      |

| Junction-to-ambient <sup>1</sup> | Natural convection   | Single-layer board (1s) | $R_{\theta JA}^2$   | 34            | 34                 | °C/W |

|                                  |                      | Four-layer board (2s2p) | $R_{\thetaJMA}{}^3$ | 22            | 22                 |      |

|                                  | Airflow (200 ft/min) | Single-layer board (1s) | $R_{\thetaJMA}{}^3$ | 27            | 27                 |      |

|                                  |                      | Four-layer board (2s2p) | $R_{\thetaJMA}{}^3$ | 18            | 18                 |      |

| Junction-to-board <sup>4</sup>   |                      |                         | $R_{\theta J B}$    | 14            | 13                 |      |

| Junction-to-case <sup>5</sup>    |                      |                         | $R_{	ext{	heta}JC}$ | 6             | 8                  |      |

| Junction-to-package top 6        | Natural convection   |                         | $\Psi_{JT}$         | 2             | 2                  |      |

<sup>1</sup> Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>4</sup> Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated value from the junction to the exposed pad without contact resistance.

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

**Thermal Calculation and Measurement**

# 7 Thermal Calculation and Measurement

For the following discussions,  $P_D = (V_{DD} \times I_{DD}) + PI/O$ , where PI/O is the power dissipation of the I/O drivers.

## 7.1 Estimation with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, in °C can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_A$  = ambient temperature (°C)

$R_{\theta JA}$  = package junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in package

The junction-to-ambient thermal resistance is an industry standard value which provides a quick and easy estimation of thermal performance. However, the answer is only an estimate; test cases have demonstrated that errors of a factor of two (in the quantity  $T_J - T_A$ ) are possible.

## 7.2 Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the airflow around the device, add a heat sink, change the mounting arrangement on the printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

# 7.3 Estimation with Junction-to-Board Thermal Resistance

A simple package thermal model which has demonstrated reasonable accuracy (about 20%) is a two-resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case thermal resistance covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed-circuit board. It has been observed that the thermal performance of most plastic packages, especially PBGA packages, is strongly dependent on the board temperature; see Figure 2.

**Bus Signal Timing**

| NI   | Characteristic                                                                                                                       | 33    | MHz | 40 MHz |     | 50 MHz |     | 66 MHz |     | - Unit |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------|-----|--------|-----|--------|-----|--------|

| Num  |                                                                                                                                      | Min   | Мах | Min    | Мах | Min    | Max | Min    | Мах | Unit   |

| B35  | A(0:31), BADDR(28:30) to CS valid—as<br>requested by control bit BST4 in the<br>corresponding word in UPM                            | 5.58  |     | 4.25   |     | 3.00   | _   | 1.79   |     | ns     |

| B35a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{BS}}$ valid—as requested by control bit BST1 in the corresponding word in UPM | 13.15 |     | 10.50  |     | 8.00   | _   | 5.58   |     | ns     |

| B35b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{BS}}$ valid—as requested by control bit BST2 in the corresponding word in UPM | 20.73 |     | 16.75  |     | 13.00  | _   | 9.36   |     | ns     |

| B36  | A(0:31), BADDR(28:30), and D(0:31) to<br>GPL valid—as requested by control bit GxT4<br>in the corresponding word in UPM              | 5.58  |     | 4.25   |     | 3.00   | _   | 1.79   |     | ns     |

| B37  | UPWAIT valid to CLKOUT falling edge9                                                                                                 | 6.00  |     | 6.00   |     | 6.00   | _   | 6.00   |     | ns     |

| B38  | CLKOUT falling edge to UPWAIT valid <sup>9</sup>                                                                                     | 1.00  | _   | 1.00   | _   | 1.00   |     | 1.00   |     | ns     |

| B39  | AS valid to CLKOUT rising edge <sup>10</sup>                                                                                         | 7.00  |     | 7.00   |     | 7.00   | _   | 7.00   |     | ns     |

| B40  | A(0:31), TSIZ(0:1), RD/WR, BURST, valid to CLKOUT rising edge                                                                        | 7.00  |     | 7.00   | _   | 7.00   |     | 7.00   | —   | ns     |

| B41  | $\overline{\text{TS}}$ valid to CLKOUT rising edge (setup time)                                                                      | 7.00  |     | 7.00   |     | 7.00   | _   | 7.00   |     | ns     |

| B42  | CLKOUT rising edge to $\overline{TS}$ valid (hold time)                                                                              | 2.00  | _   | 2.00   | _   | 2.00   | _   | 2.00   | _   | ns     |

| B43  | AS negation to memory controller signals negation                                                                                    | _     | TBD | _      | TBD | —      | TBD | _      | TBD | ns     |

| Table 7 | Bus O | neration | Timinas | (continued) |

|---------|-------|----------|---------|-------------|

|         | Du3 0 | peration | rinnigs | (continucu) |

<sup>1</sup> Phase and frequency jitter performance results are only valid if the input jitter is less than the prescribed value.

<sup>2</sup> If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time) then the maximum allowed jitter on EXTAL can be up to 2%.

<sup>3</sup> The timings specified in B4 and B5 are based on full strength clock.

<sup>4</sup> The timing for BR output is relevant when the MPC860 is selected to work with external bus arbiter. The timing for BG output is relevant when the MPC860 is selected to work with internal bus arbiter.

<sup>5</sup> The timing required for BR input is relevant when the MPC860 is selected to work with internal bus arbiter. The timing for BG input is relevant when the MPC860 is selected to work with external bus arbiter.

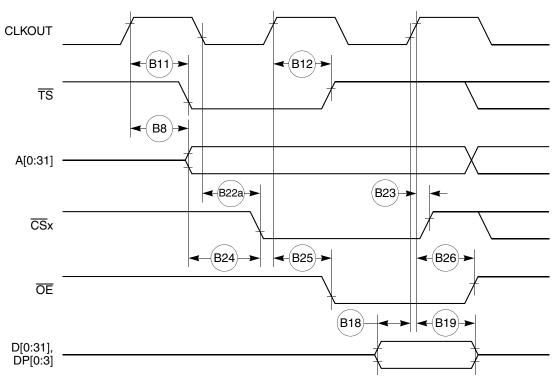

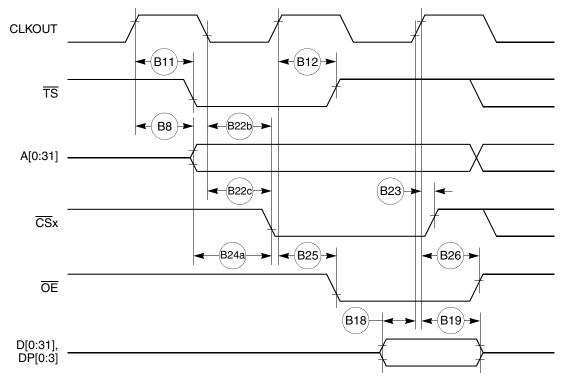

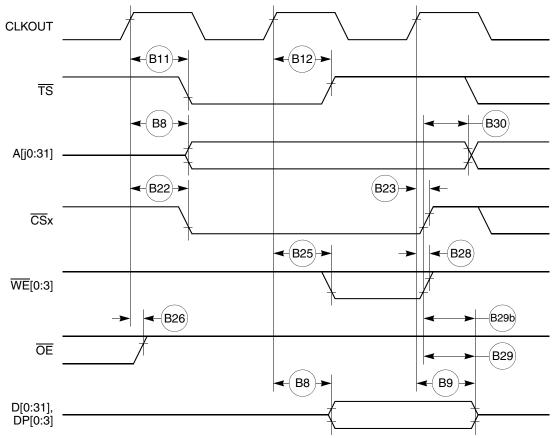

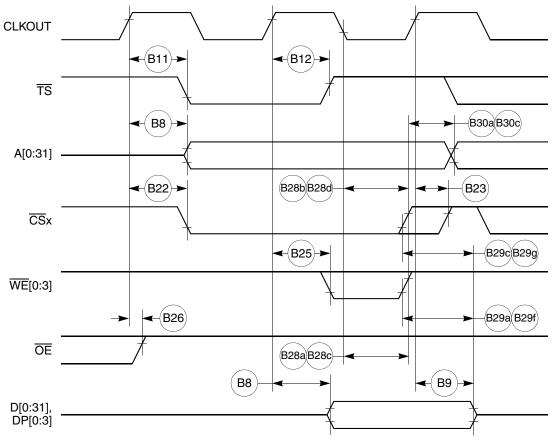

<sup>6</sup> The D(0:31) and DP(0:3) input timings B18 and B19 refer to the rising edge of the CLKOUT in which the TA input signal is asserted.

<sup>7</sup> The D(0:31) and DP(0:3) input timings B20 and B21 refer to the falling edge of the CLKOUT. This timing is valid only for read accesses controlled by chip-selects under control of the UPM in the memory controller, for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

<sup>8</sup> The timing B30 refers to  $\overline{CS}$  when ACS = 00 and to  $\overline{WE}(0:3)$  when CSNT = 0.

<sup>9</sup> The signal UPWAIT is considered asynchronous to the CLKOUT and synchronized internally. The timings specified in B37 and B38 are specified to enable the freeze of the UPM output signals as described in Figure 18.

<sup>10</sup> The AS signal is considered asynchronous to the CLKOUT. The timing B39 is specified in order to allow the behavior specified in Figure 21.

Figure 12. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 11)

Figure 14 through Figure 16 provide the timing for the external bus write controlled by various GPCM factors.

Figure 14. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 0)

**Bus Signal Timing**

Figure 15. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

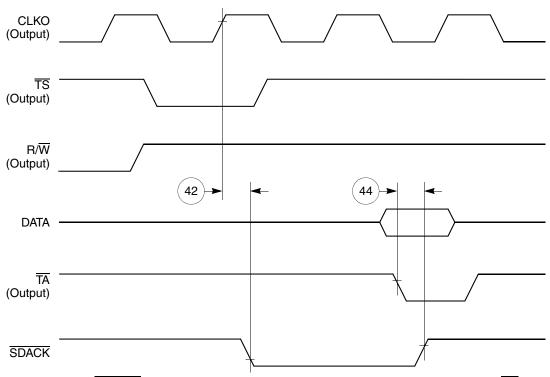

Figure 47. SDACK Timing Diagram—Peripheral Write, Internally-Generated TA

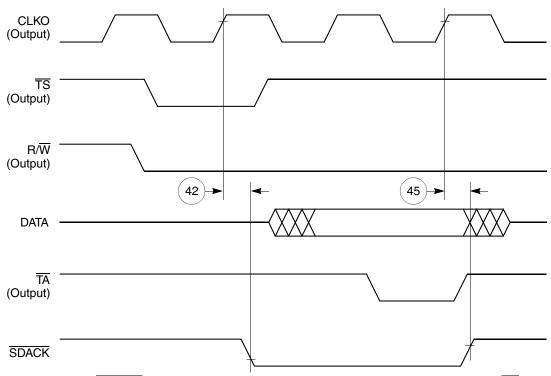

Figure 48. SDACK Timing Diagram—Peripheral Read, Internally-Generated TA

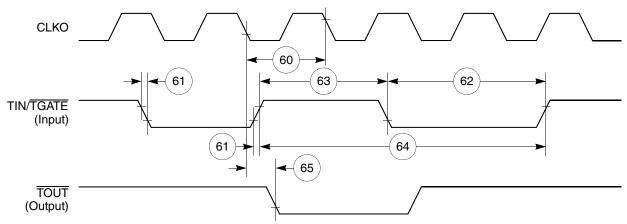

Figure 50. CPM General-Purpose Timers Timing Diagram

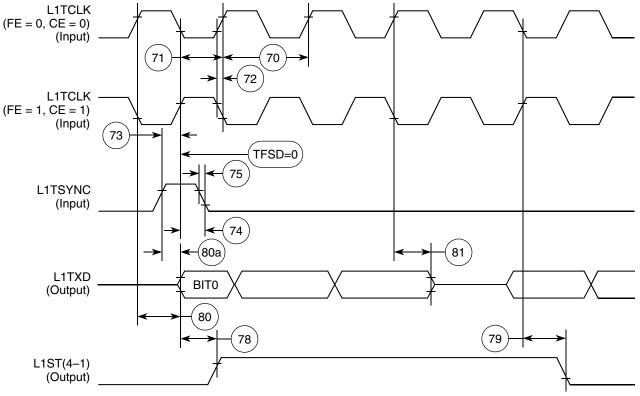

## **11.6 Serial Interface AC Electrical Specifications**

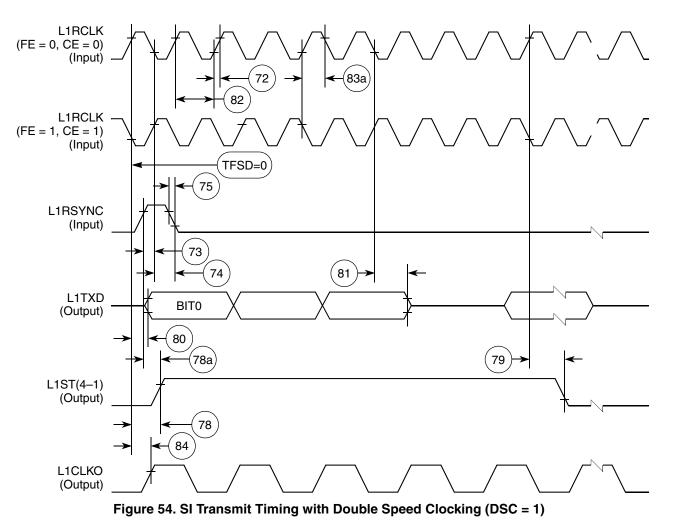

Table 19 provides the serial interface timings as shown in Figure 51 through Figure 55.

| N   | Oh ava ataviatia                                         | All Fred | quencies              | 11   |

|-----|----------------------------------------------------------|----------|-----------------------|------|

| Num | Characteristic                                           | Min      | Max                   | Unit |

| 70  | L1RCLK, L1TCLK frequency (DSC = 0) <sup>1, 2</sup>       | _        | SYNCCLK/2.5           | MHz  |

| 71  | L1RCLK, L1TCLK width low $(DSC = 0)^2$                   | P + 10   | _                     | ns   |

| 71a | L1RCLK, L1TCLK width high (DSC = $0$ ) <sup>3</sup>      | P + 10   | _                     | ns   |

| 72  | L1TXD, L1ST(1–4), L1RQ, L1CLKO rise/fall time            | _        | 15.00                 | ns   |

| 73  | L1RSYNC, L1TSYNC valid to L1CLK edge (SYNC setup time)   | 20.00    | —                     | ns   |

| 74  | L1CLK edge to L1RSYNC, L1TSYNC, invalid (SYNC hold time) | 35.00    | —                     | ns   |

| 75  | L1RSYNC, L1TSYNC rise/fall time                          | _        | 15.00                 | ns   |

| 76  | L1RXD valid to L1CLK edge (L1RXD setup time)             | 17.00    | —                     | ns   |

| 77  | L1CLK edge to L1RXD invalid (L1RXD hold time)            | 13.00    | —                     | ns   |

| 78  | L1CLK edge to L1ST(1-4) valid <sup>4</sup>               | 10.00    | 45.00                 | ns   |

| 78A | L1SYNC valid to L1ST(1-4) valid                          | 10.00    | 45.00                 | ns   |

| 79  | L1CLK edge to L1ST(1-4) invalid                          | 10.00    | 45.00                 | ns   |

| 80  | L1CLK edge to L1TXD valid                                | 10.00    | 55.00                 | ns   |

| 80A | L1TSYNC valid to L1TXD valid <sup>4</sup>                | 10.00    | 55.00                 | ns   |

| 81  | L1CLK edge to L1TXD high impedance                       | 0.00     | 42.00                 | ns   |

| 82  | L1RCLK, L1TCLK frequency (DSC =1)                        | _        | 16.00 or<br>SYNCCLK/2 | MHz  |

| 83  | L1RCLK, L1TCLK width low (DSC = 1)                       | P + 10   | —                     | ns   |

| 83a | L1RCLK, L1TCLK width high (DSC = $1$ ) <sup>3</sup>      | P + 10   | —                     | ns   |

### Table 19. SI Timing

**CPM Electrical Characteristics**

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

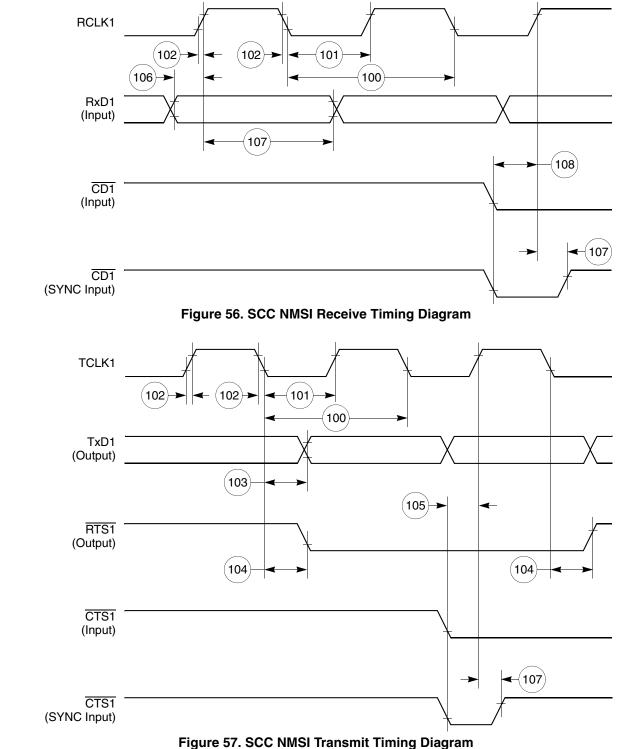

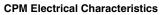

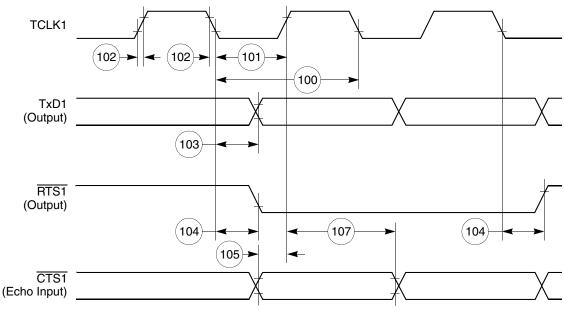

Figure 56 through Figure 58 show the NMSI timings.

rigure 57. See NMSF franslint finning Diagram

Figure 58. HDLC Bus Timing Diagram

# **11.8 Ethernet Electrical Specifications**

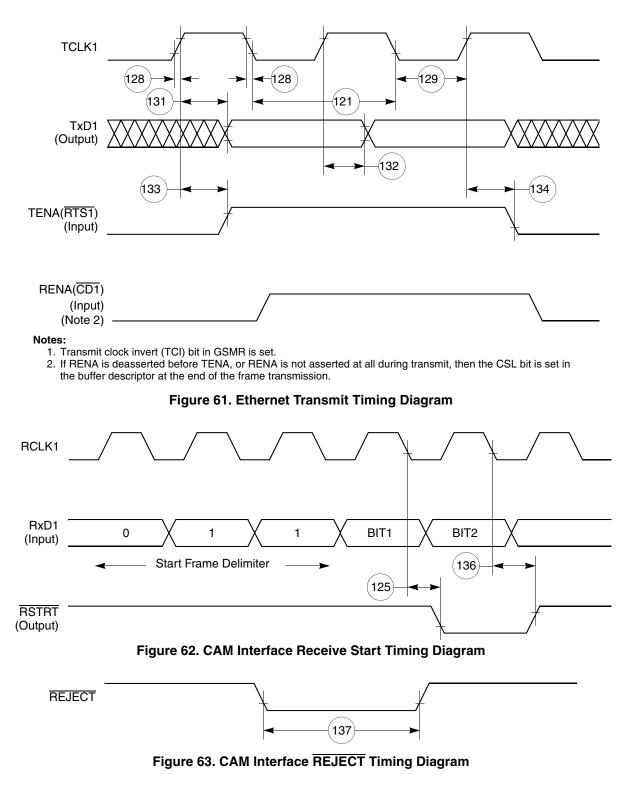

Table 22 provides the Ethernet timings as shown in Figure 59 through Figure 63.

| Num | Characteristic                                                  | All Freq | uencies | Unit |

|-----|-----------------------------------------------------------------|----------|---------|------|

| Num | Characteristic                                                  | Min      | Max     | Unit |

| 120 | CLSN width high                                                 | 40       | _       | ns   |

| 121 | RCLK1 rise/fall time                                            | —        | 15      | ns   |

| 122 | RCLK1 width low                                                 | 40       | —       | ns   |

| 123 | RCLK1 clock period <sup>1</sup>                                 | 80       | 120     | ns   |

| 124 | RXD1 setup time                                                 | 20       | —       | ns   |

| 125 | RXD1 hold time                                                  | 5        | —       | ns   |

| 126 | RENA active delay (from RCLK1 rising edge of the last data bit) | 10       | —       | ns   |

| 127 | RENA width low                                                  | 100      | —       | ns   |

| 128 | TCLK1 rise/fall time                                            | —        | 15      | ns   |

| 129 | TCLK1 width low                                                 | 40       | —       | ns   |

| 130 | TCLK1 clock period <sup>1</sup>                                 | 99       | 101     | ns   |

| 131 | TXD1 active delay (from TCLK1 rising edge)                      | 10       | 50      | ns   |

| 132 | TXD1 inactive delay (from TCLK1 rising edge)                    | 10       | 50      | ns   |

| 133 | TENA active delay (from TCLK1 rising edge)                      | 10       | 50      | ns   |

| 134 | TENA inactive delay (from TCLK1 rising edge)                    | 10       | 50      | ns   |

**CPM Electrical Characteristics**

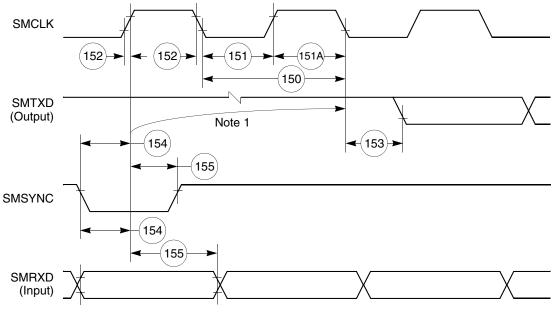

#### **SMC Transparent AC Electrical Specifications** 11.9

Table 23 provides the SMC transparent timings as shown in Figure 64.

### Table 23. SMC Transparent Timing

| Num  | Characteristic                               |     | All Frequencies |      |  |

|------|----------------------------------------------|-----|-----------------|------|--|

| Num  | Characteristic                               | Min | Мах             | Unit |  |

| 150  | SMCLK clock period <sup>1</sup>              | 100 | —               | ns   |  |

| 151  | SMCLK width low                              | 50  | —               | ns   |  |

| 151A | SMCLK width high                             | 50  | —               | ns   |  |

| 152  | SMCLK rise/fall time                         | _   | 15              | ns   |  |

| 153  | SMTXD active delay (from SMCLK falling edge) | 10  | 50              | ns   |  |

| 154  | 54 SMRXD/SMSYNC setup time                   |     | —               | ns   |  |

| 155  | RXD1/SMSYNC hold time                        | 5   | —               | ns   |  |

<sup>1</sup> SYNCCLK must be at least twice as fast as SMCLK.

Note: 1. This delay is equal to an integer number of character-length clocks.

# 11.12 I<sup>2</sup>C AC Electrical Specifications

Table 26 provides the  $I^2C$  (SCL < 100 kHz) timings.

## Table 26. I<sup>2</sup>C Timing (SCL < 100 kHz)

| Num | Characteristic                            | All Freq | uencies | Unit |

|-----|-------------------------------------------|----------|---------|------|

| Num | Characteristic                            | Min      | Max     | Onit |

| 200 | SCL clock frequency (slave)               | 0        | 100     | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100     | kHz  |

| 202 | Bus free time between transmissions       | 4.7      | _       | μS   |

| 203 | Low period of SCL                         | 4.7      | —       | μS   |

| 204 | High period of SCL                        | 4.0      | —       | μS   |

| 205 | Start condition setup time                | 4.7      | —       | μS   |

| 206 | Start condition hold time                 | 4.0      | —       | μS   |

| 207 | Data hold time                            | 0        | —       | μS   |

| 208 | Data setup time                           | 250      | —       | ns   |

| 209 | SDL/SCL rise time                         | —        | 1       | μS   |

| 210 | SDL/SCL fall time                         | —        | 300     | ns   |

| 211 | Stop condition setup time                 | 4.7      | —       | μS   |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3 × pre\_scaler × 2). The ratio SYNCCLK/(BRGCLK/pre\_scaler) must be greater than or equal to 4/1.

## Table 27 provides the $I^2C$ (SCL > 100 kHz) timings.

### Table 27. . I<sup>2</sup>C Timing (SCL > 100 kHz)

| Num | Characteristic                            | Expression | All Freq        | Unit          |      |

|-----|-------------------------------------------|------------|-----------------|---------------|------|

| Num | Gharacteristic                            | Expression | Min             | Мах           | Onit |

| 200 | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48     | Hz   |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48     | Hz   |

| 202 | Bus free time between transmissions       |            | 1/(2.2 * fSCL)  | —             | s    |

| 203 | Low period of SCL                         |            | 1/(2.2 * fSCL)  | —             | s    |

| 204 | High period of SCL                        |            | 1/(2.2 * fSCL)  | _             | S    |

| 205 | Start condition setup time                |            | 1/(2.2 * fSCL)  | —             | S    |

| 206 | Start condition hold time                 |            | 1/(2.2 * fSCL)  | —             | S    |

| 207 | Data hold time                            |            | 0               | _             | S    |

| 208 | Data setup time                           |            | 1/(40 * fSCL)   | _             | S    |

| 209 | SDL/SCL rise time                         |            | —               | 1/(10 * fSCL) | s    |

| 210 | SDL/SCL fall time                         |            | —               | 1/(33 * fSCL) | S    |

| 211 | Stop condition setup time                 |            | 1/2(2.2 * fSCL) |               | S    |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) × pre\_scaler × 2). The ratio SYNCCLK/(BRGCLK / pre\_scaler) must be greater than or equal to 4/1.

### Table 34 identifies the packages and operating frequencies available for the MPC860.

| Package Type                                                                   | Freq. (MHz) /<br>Temp. (Tj) | Package            | Order Number                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------|-----------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball grid array<br>ZP suffix—leaded<br>ZQ suffix—leaded<br>VR suffix—lead-free | 50<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ50D4<br>MPC860DEZQ50D4<br>MPC860DTZQ50D4<br>MPC860ENZQ50D4<br>MPC860SRZQ50D4<br>MPC860TZQ50D4<br>MPC860DPZQ50D4<br>MPC860PZQ50D4                                                                          |

|                                                                                |                             | Tape and Reel      | MPC855TZQ50D4R2<br>MPC860DEZQ50D4R2<br>MPC860ENZQ50D4R2<br>MPC860SRZQ50D4R2<br>MPC860TZQ50D4R2<br>MPC860TZQ50D4R2<br>MPC860TZQ50D4R2<br>MPC855TVR50D4R2<br>MPC860ENVR50D4R2<br>MPC860SRVR50D4R2<br>MPC860TVR50D4R2 |

|                                                                                |                             | VR                 | MPC855TVR50D4<br>MPC860DEVR50D4<br>MPC860DPVR50D4<br>MPC860DTVR50D4<br>MPC860ENVR50D4<br>MPC860PVR50D4<br>MPC860SRVR50D4<br>MPC860SRVR50D4                                                                         |

|                                                                                | 66<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ66D4<br>MPC860DEZQ66D4<br>MPC860DTZQ66D4<br>MPC860ENZQ66D4<br>MPC860SRZQ66D4<br>MPC860TZQ66D4<br>MPC860DPZQ66D4<br>MPC860PZQ66D4                                                                          |

|                                                                                |                             | Tape and Reel      | MPC860SRZQ66D4R2<br>MPC860PZQ66D4R2                                                                                                                                                                                |

|                                                                                |                             | VR                 | MPC855TVR66D4<br>MPC860DEVR66D4<br>MPC860DPVR66D4<br>MPC860DTVR66D4<br>MPC860ENVR66D4<br>MPC860PVR66D4<br>MPC860SRVR66D4<br>MPC860TVR66D4                                                                          |

### Table 34. MPC860 Family Package/Frequency Availability

#### Mechanical Data and Ordering Information

| Package Type                                                                                      | Freq. (MHz) /<br>Temp. (Tj) | Package            | Order Number                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball grid array <i>(continued)</i><br>ZP suffix—leaded<br>ZQ suffix—leaded<br>VR suffix—lead-free | 80<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ80D4<br>MPC860DEZQ80D4<br>MPC860DTZQ80D4<br>MPC860ENZQ80D4<br>MPC860SRZQ80D4<br>MPC860TZQ80D4<br>MPC860DPZQ80D4<br>MPC860PZQ80D4                            |

|                                                                                                   |                             | Tape and Reel      | MPC860PZQ80D4R2<br>MPC860PVR80D4R2                                                                                                                                   |

|                                                                                                   |                             | VR                 | MPC855TVR80D4<br>MPC860DEVR80D4<br>MPC860DPVR80D4<br>MPC860ENVR80D4<br>MPC860PVR80D4<br>MPC860SRVR80D4<br>MPC860SRVR80D4<br>MPC860TVR80D4                            |

| Ball grid array (CZP suffix)<br>CZP suffix—leaded<br>CZQ suffix—leaded<br>CVR suffix—lead-free    | 50<br>–40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ50D4<br>MPC855TCVR50D4<br>MPC860DECZQ50D4<br>MPC860DTCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860SRCZQ50D4<br>MPC860DPCZQ50D4<br>MPC860PCZQ50D4 |

|                                                                                                   |                             | Tape and Reel      | MPC855TCZQ50D4R2<br>MC860ENCVR50D4R2                                                                                                                                 |

|                                                                                                   |                             | CVR                | MPC860DECVR50D4<br>MPC860DTCVR50D4<br>MPC860ENCVR50D4<br>MPC860PCVR50D4<br>MPC860SRCVR50D4<br>MPC860SRCVR50D4<br>MPC860TCVR50D4                                      |

|                                                                                                   | 66<br>–40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ66D4<br>MPC855TCVR66D4<br>MPC860ENCZQ66D4<br>MPC860SRCZQ66D4<br>MPC860TCZQ66D4<br>MPC860DPCZQ66D4<br>MPC860PCZQ66D4                                        |

|                                                                                                   |                             | CVR                | MPC860DTCVR66D4<br>MPC860ENCVR66D4<br>MPC860PCVR66D4<br>MPC860SRCVR66D4<br>MPC860TCVR66D4                                                                            |

### Table 34. MPC860 Family Package/Frequency Availability (continued)

<sup>1</sup> The ZP package is no longer recommended for use. The ZQ package replaces the ZP package.

Mechanical Data and Ordering Information

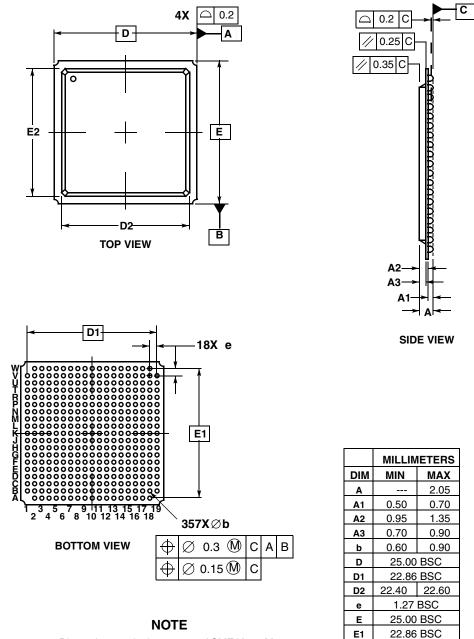

## 14.3 Mechanical Dimensions of the PBGA Package

Figure 77 shows the mechanical dimensions of the ZP PBGA package.

- 1. Dimensions and tolerance per ASME Y14.5M, 1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is the maximum solder ball diameter measured parallel to data C.

22.40

E2

22.60