Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                          |

|---------------------------------|--------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                 |

| Core Processor                  | MPC8xx                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 50MHz                                                                    |

| Co-Processors/DSP               | Communications; CPM                                                      |

| RAM Controllers                 | DRAM                                                                     |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10Mbps (4)                                                               |

| SATA                            | -                                                                        |

| USB                             | -                                                                        |

| Voltage - I/O                   | 3.3V                                                                     |

| Operating Temperature           | -40°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                        |

| Package / Case                  | 357-BBGA                                                                 |

| Supplier Device Package         | 357-PBGA (25x25)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc860srcvr50d4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

## 1 Overview

The MPC860 power quad integrated communications controller (PowerQUICC<sup>TM</sup>) is a versatile one-chip integrated microprocessor and peripheral combination designed for a variety of controller applications. It particularly excels in communications and networking systems. The PowerQUICC unit is referred to as the MPC860 in this hardware specification.

The MPC860 implements Power Architecture<sup>TM</sup> technology and contains a superset of Freescale's MC68360 quad integrated communications controller (QUICC), referred to here as the QUICC, RISC communications processor module (CPM). The CPU on the MPC860 is a 32-bit core built on Power Architecture technology that incorporates memory management units (MMUs) and instruction and data caches.. The CPM from the MC68360 QUICC has been enhanced by the addition of the inter-integrated controller (I<sup>2</sup>C) channel. The memory controller has been enhanced, enabling the MPC860 to support any type of memory, including high-performance memories and new types of DRAMs. A PCMCIA socket controller supports up to two sockets. A real-time clock has also been integrated.

Table 1 shows the functionality supported by the MPC860 family.

|          | Cache (              | Cache (Kbytes) |         | ernet  |     |     |                        |

|----------|----------------------|----------------|---------|--------|-----|-----|------------------------|

| Part     | Instruction<br>Cache | Data Cache     | 10T     | 10/100 | ATM | scc | Reference <sup>1</sup> |

| MPC860DE | 4                    | 4              | Up to 2 | _      | _   | 2   | 1                      |

| MPC860DT | 4                    | 4              | Up to 2 | 1      | Yes | 2   | 1                      |

| MPC860DP | 16                   | 8              | Up to 2 | 1      | Yes | 2   | 1                      |

| MPC860EN | 4                    | 4              | Up to 4 | _      | _   | 4   | 1                      |

| MPC860SR | 4                    | 4              | Up to 4 | _      | Yes | 4   | 1                      |

| MPC860T  | 4                    | 4              | Up to 4 | 1      | Yes | 4   | 1                      |

| MPC860P  | 16                   | 8              | Up to 4 | 1      | Yes | 4   | 1                      |

| MPC855T  | 4                    | 4              | 1       | 1      | Yes | 1   | 2                      |

|          |                      |                |         |        |     |     |                        |

**Table 1. MPC860 Family Functionality**

Supporting documentation for these devices refers to the following:

<sup>1.</sup> MPC860 PowerQUICC Family User's Manual (MPC860UM, Rev. 3)

<sup>2.</sup> MPC855T User's Manual (MPC855TUM, Rev. 1)

#### **Thermal Characteristics**

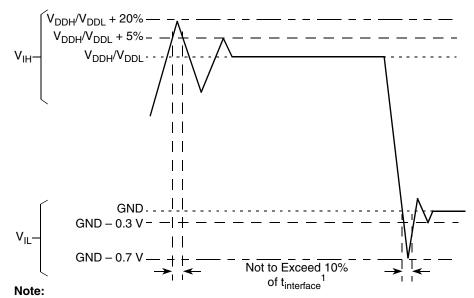

Figure 1 shows the undershoot and overshoot voltages at the interface of the MPC860.

<sup>1.</sup>  $t_{\text{interface}}$  refers to the clock period associated with the bus clock interface.

Figure 1. Undershoot/Overshoot Voltage for V<sub>DDH</sub> and V<sub>DDL</sub>

# 4 Thermal Characteristics

**Table 3. Package Description**

| Package Designator | Package Code (Case No.) | Package Description     |

|--------------------|-------------------------|-------------------------|

| ZP                 | 5050 (1103-01)          | PBGA 357 25*25*0.9P1.27 |

| ZQ/VR              | 5058 (1103D-02)         | PBGA 357 25*25*1.2P1.27 |

#### Table 4 shows the thermal characteristics for the MPC860.

Table 4. MPC860 Thermal Resistance Data

| Rating                           | Environment          |                         | Symbol             | ZP<br>MPC860P | ZQ / VR<br>MPC860P | Unit |

|----------------------------------|----------------------|-------------------------|--------------------|---------------|--------------------|------|

| Mold Compound Thickness          | SS                   |                         |                    | 0.85          | 1.15               | mm   |

| Junction-to-ambient <sup>1</sup> | Natural convection   | Single-layer board (1s) | $R_{\theta JA}^2$  | 34            | 34                 | °C/W |

|                                  |                      | Four-layer board (2s2p) | $R_{\theta JMA}^3$ | 22            | 22                 |      |

|                                  | Airflow (200 ft/min) | Single-layer board (1s) | $R_{\theta JMA}^3$ | 27            | 27                 |      |

|                                  |                      | Four-layer board (2s2p) | $R_{\theta JMA}^3$ | 18            | 18                 |      |

| Junction-to-board 4              |                      | •                       | $R_{\theta JB}$    | 14            | 13                 |      |

| Junction-to-case <sup>5</sup>    |                      |                         | $R_{\theta JC}$    | 6             | 8                  |      |

| Junction-to-package top 6        | Natural convection   |                         | $\Psi_{JT}$        | 2             | 2                  |      |

Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance

<sup>&</sup>lt;sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>&</sup>lt;sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>&</sup>lt;sup>4</sup> Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated value from the junction to the exposed pad without contact resistance.

<sup>&</sup>lt;sup>6</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

#### **Table 6. DC Electrical Specifications (continued)**

| Characteristic                                                                                                                                                                            | Symbol          | Min | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|

| Input leakage current, $V_{in}$ = 3.6 V (except TMS, $\overline{TRST}$ , DSCK, and DSDI pins)                                                                                             | I <sub>In</sub> | _   | 10  | μΑ   |

| Input leakage current, V <sub>in</sub> = 0 V (except TMS, TRST, DSCK, and DSDI pins)                                                                                                      | I <sub>In</sub> | _   | 10  | μΑ   |

| Input capacitance <sup>2</sup>                                                                                                                                                            | C <sub>in</sub> | _   | 20  | pF   |

| Output high voltage, $I_{OH} = -2.0$ mA, $V_{DDH} = 3.0$ V (except XTAL, XFC, and open-drain pins)                                                                                        | V <sub>OH</sub> | 2.4 | _   | V    |

| Output low voltage $I_{OL}$ = 2.0 mA, CLKOUT $I_{OL}$ = 3.2 mA $^3$ $I_{OL}$ = 5.3 mA $^4$ $I_{OL}$ = 7.0 mA, TXD1/PA14, TXD2/PA12 $I_{OL}$ = 8.9 mA, TS, TA, TEA, BI, BB, HRESET, SRESET | V <sub>OL</sub> | _   | 0.5 | V    |

<sup>&</sup>lt;sup>1</sup> V<sub>II</sub> (max) for the I<sup>2</sup>C interface is 0.8 V rather than the 1.5 V as specified in the I<sup>2</sup>C standard.

<sup>&</sup>lt;sup>2</sup> Input capacitance is periodically sampled.

<sup>3</sup> A(0:31), TSIZ0/REG, TSIZ1, D(0:31), DP(0:3)/IRQ(3:6), RD/WR, BURST, RSV/IRQ2, IP\_B(0:1)/IWP(0:1)/VFLS(0:1), IP\_B2/IOIS16\_B/AT2, IP\_B3/IWP2/VF2, IP\_B4/LWP0/VF0, IP\_B5/LWP1/VF1, IP\_B6/DSDI/AT0, IP\_B7/PTR/AT3, RXD1/PA15, RXD2/PA13, L1TXDB/PA11, L1RXDB/PA10, L1TXDA/PA9, L1RXDA/PA8, TIN1/L1RCLKA/BRGO1/CLK1/PA7, BRGCLK1/TOUT1/CLK2/PA6, TIN2/L1TCLKA/BRGO2/CLK3/PA5, TOUT2/CLK4/PA4, TIN3/BRGO3/CLK5/PA3, BRGCLK2/L1RCLKB/TOUT3/CLK6/PA2, TIN4/BRGO4/CLK7/PA1, L1TCLKB/TOUT4/CLK8/PA0, REJCT1/SPISEL/PB31, SPICLK/PB30,SPIMOSI/PB29, BRGO4/SPIMISO/PB28, BRGO1/I2CSDA/PB27, BRGO2/I2CSCL/PB26, SMTXD1/PB25, SMRXD1/PB24, SMSYN1/SDACK1/PB23, SMSYN2/SDACK2/PB22, SMTXD2/L1CLKOB/PB21, SMRXD2/L1CLKOA/PB20, L1ST1/RTS1/PB19, L1ST2/RTS2/PB18, L1ST3/L1RQB/PB17, L1ST4/L1RQA/PB16, BRGO3/PB15, RSTRT1/PB14, L1ST1/RTS1/DREQ0/PC15, L1ST2/RTS2/DREQ1/PC14, L1ST3/L1RQB/PC13, L1ST4/L1RQA/PC12, CTS1/PC11, TGATE1/CD1/PC10, CTS2/PC9, TGATE2/CD2/PC8, SDACK2/L1TSYNCB/PC7, L1RSYNCB/PC6, SDACK1/L1TSYNCA/PC5, L1RSYNCA/PC4, PD15, PD14, PD13, PD12, PD11, PD10, PD9, PD8, PD5, PD6, PD7, PD4, PD3, MII\_MDC, MII\_TX\_ER, MII\_EN, MII\_MDIO, and MII\_TXD[0:3]

<sup>4</sup> BDIP/GPL\_B(5), BR, BG, FRZ/IRQ6, CS(0:5), CS(6)/CE(1)\_B, CS(7)/CE(2)\_B, WE0/BS\_B0/IORD, WE1/BS\_B1/IOWR, WE2/BS\_B2/PCOE, WE3/BS\_B3/PCWE, BS\_A(0:3), GPL\_A0/GPL\_B0, OE/GPL\_A1/GPL\_B1, GPL\_A(2:3)/GPL\_B(2:3)/CS(2:3), UPWAITA/GPL\_A4, UPWAITB/GPL\_B4, GPL\_A5, ALE\_A, CE1\_A, CE2\_A, ALE\_B/DSCK/AT1, OP(0:1), OP2/MODCK1/STS, OP3/MODCK2/DSDO, and BADDR(28:30)

## **Bus Signal Timing**

## **Table 7. Bus Operation Timings (continued)**

| Norma | Observatoristis                                                                                                                                                                                               | 33 1  | ИНz  | 40 [  | MHz  | 50 I  | ИНz  | 66 I  | ИНz  | 11!4 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|-------|------|-------|------|------|

| Num   | Characteristic                                                                                                                                                                                                | Min   | Max  | Min   | Max  | Min   | Max  | Min   | Max  | Unit |

| B29d  | WE(0:3) negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>EBDF = 0                                                                                                              | 43.45 | _    | 35.5  | _    | 28.00 | _    | 20.73 | _    | ns   |

| B29e  | CS negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0                                                                                            | 43.45 |      | 35.5  | _    | 28.00 |      | 29.73 | _    | ns   |

| B29f  | WE(0:3) negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>EBDF = 1                                                                                                              | 8.86  | _    | 6.88  | _    | 5.00  | _    | 3.18  | _    | ns   |

| B29g  | CS negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                            | 8.86  |      | 6.88  |      | 5.00  |      | 3.18  |      | ns   |

| B29h  | WE(0:3) negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>EBDF = 1                                                                                                              | 38.67 | _    | 31.38 | _    | 24.50 | _    | 17.83 | _    | ns   |

| B29i  | CS negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                            | 38.67 |      | 31.38 | _    | 24.50 |      | 17.83 | _    | ns   |

| B30   | CS, WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM write access <sup>8</sup>                                                                                                                           | 5.58  | _    | 4.25  | _    | 3.00  | _    | 1.79  | _    | ns   |

| B30a  | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM, write access, TRLX = 0, CSNT = 1, CS negated to A(0:31) invalid GPCM write access, TRLX = 0, CSNT = 1 ACS = 10, or ACS = 11, EBDF = 0                  | 13.15 | _    | 10.50 | _    | 8.00  | _    | 5.58  | _    | ns   |

| B30b  | WE(0:3) negated to A(0:31), invalid GPCM BADDR(28:30) invalid GPCM write access, TRLX = 1, CSNT = 1. CS negated to A(0:31), Invalid GPCM, write access, TRLX = 1, CSNT = 1, ACS = 10, or ACS = 11, EBDF = 0   | 43.45 | _    | 35.50 | _    | 28.00 | _    | 20.73 | _    | ns   |

| B30c  | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM write access, TRLX = 0, CSNT = 1. $\overline{\text{CS}}$ negated to A(0:31) invalid GPCM write access, TRLX = 0, CSNT = 1, ACS = 10, ACS = 11, EBDF = 1 | 8.36  |      | 6.38  | _    | 4.50  |      | 2.68  | _    | ns   |

| B30d  | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM write access, TRLX = 1, CSNT =1. $\overline{CS}$ negated to A(0:31) invalid GPCM write access TRLX = 1, CSNT = 1, ACS = 10, or ACS = 11, EBDF = 1       | 38.67 | _    | 31.38 | _    | 24.50 | _    | 17.83 | _    | ns   |

| B31   | CLKOUT falling edge to CS valid—as requested by control bit CST4 in the corresponding word in UPM                                                                                                             | 1.50  | 6.00 | 1.50  | 6.00 | 1.50  | 6.00 | 1.50  | 6.00 | ns   |

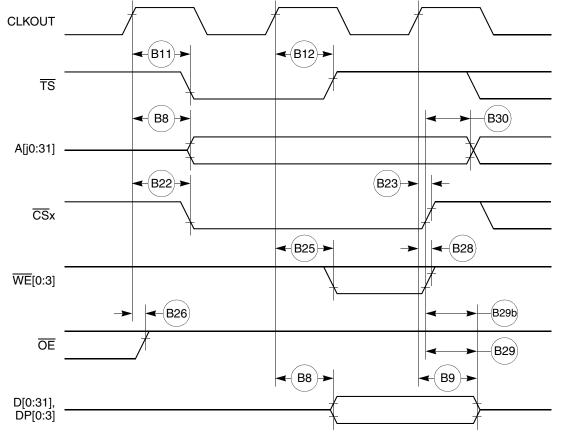

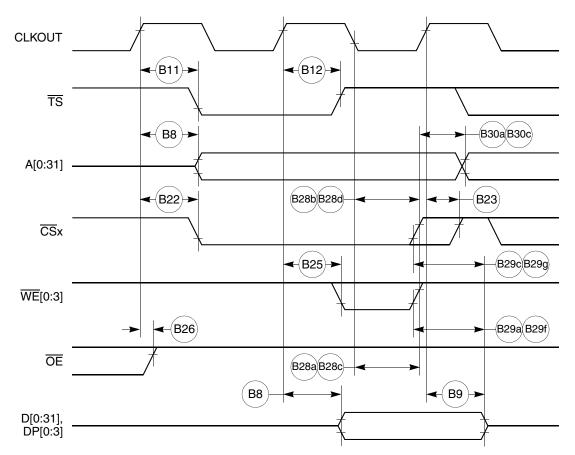

Figure 14 through Figure 16 provide the timing for the external bus write controlled by various GPCM factors.

Figure 14. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 0)

## **Bus Signal Timing**

Figure 15. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

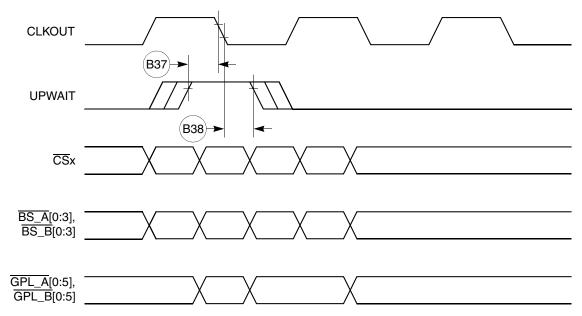

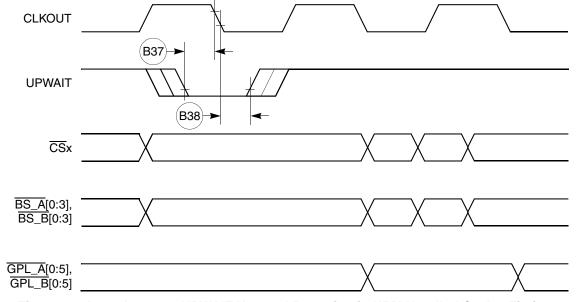

Figure 18 provides the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Figure 18. Asynchronous UPWAIT Asserted Detection in UPM Handled Cycles Timing

Figure 19 provides the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

Figure 19. Asynchronous UPWAIT Negated Detection in UPM Handled Cycles Timing

#### **Bus Signal Timing**

Table 9 shows the PCMCIA timing for the MPC860.

## **Table 9. PCMCIA Timing**

| Norma | Characteristic                                             | 33 I  | ИНz   | 40 I  | ИНz   | 50 I  | ИНz   | 66 I  | ИНz   | l l m i t |

|-------|------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|

| Num   | Characteristic                                             | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit      |

| P44   | A(0:31), REG valid to PCMCIA Strobe asserted <sup>1</sup>  | 20.73 | _     | 16.75 | _     | 13.00 | _     | 9.36  | _     | ns        |

| P45   | A(0:31), REG valid to ALE negation <sup>1</sup>            | 28.30 | _     | 23.00 | _     | 18.00 | _     | 13.15 | _     | ns        |

| P46   | CLKOUT to REG valid                                        | 7.58  | 15.58 | 6.25  | 14.25 | 5.00  | 13.00 | 3.79  | 11.84 | ns        |

| P47   | CLKOUT to REG invalid                                      | 8.58  | _     | 7.25  | _     | 6.00  | _     | 4.84  | _     | ns        |

| P48   | CLKOUT to CE1, CE2 asserted                                | 7.58  | 15.58 | 6.25  | 14.25 | 5.00  | 13.00 | 3.79  | 11.84 | ns        |

| P49   | CLKOUT to CE1, CE2 negated                                 | 7.58  | 15.58 | 6.25  | 14.25 | 5.00  | 13.00 | 3.79  | 11.84 | ns        |

| P50   | CLKOUT to PCOE, IORD, PCWE, IOWR assert time               | _     | 11.00 |       | 11.00 | _     | 11.00 | _     | 11.00 | ns        |

| P51   | CLKOUT to PCOE, IORD, PCWE, IOWR negate time               | 2.00  | 11.00 | 2.00  | 11.00 | 2.00  | 11.00 | 2.00  | 11.00 | ns        |

| P52   | CLKOUT to ALE assert time                                  | 7.58  | 15.58 | 6.25  | 14.25 | 5.00  | 13.00 | 3.79  | 10.04 | ns        |

| P53   | CLKOUT to ALE negate time                                  | _     | 15.58 |       | 14.25 | _     | 13.00 | _     | 11.84 | ns        |

| P54   | PCWE, IOWR negated to D(0:31) invalid <sup>1</sup>         | 5.58  | _     | 4.25  | _     | 3.00  | _     | 1.79  | _     | ns        |

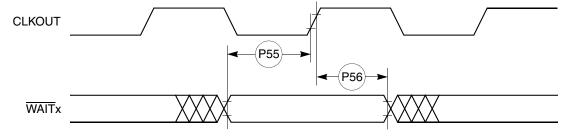

| P55   | WAITA and WAITB valid to CLKOUT rising edge <sup>1</sup>   | 8.00  | _     | 8.00  | _     | 8.00  | _     | 8.00  | _     | ns        |

| P56   | CLKOUT rising edge to WAITA and WAITB invalid <sup>1</sup> | 2.00  | _     | 2.00  | _     | 2.00  | _     | 2.00  | _     | ns        |

<sup>1</sup> PSST = 1. Otherwise add PSST times cycle time. PSHT = 0. Otherwise add PSHT times cycle time.

These synchronous timings define when the  $\overline{WAITx}$  signals are detected in order to freeze (or relieve) the PCMCIA current cycle. The  $\overline{\text{WAITx}}$  assertion will be effective only if it is detected 2 cycles before the PSL timer expiration. See Chapter 16, "PCMCIA Interface," in the MPC860 PowerQUICC<sup>TM</sup> Family User's Manual.

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10 34 Freescale Semiconductor

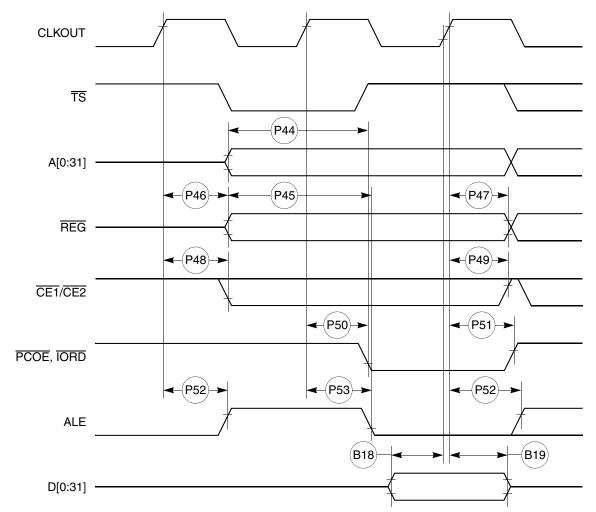

Figure 25 provides the PCMCIA access cycle timing for the external bus read.

Figure 25. PCMCIA Access Cycle Timing External Bus Read

#### **Bus Signal Timing**

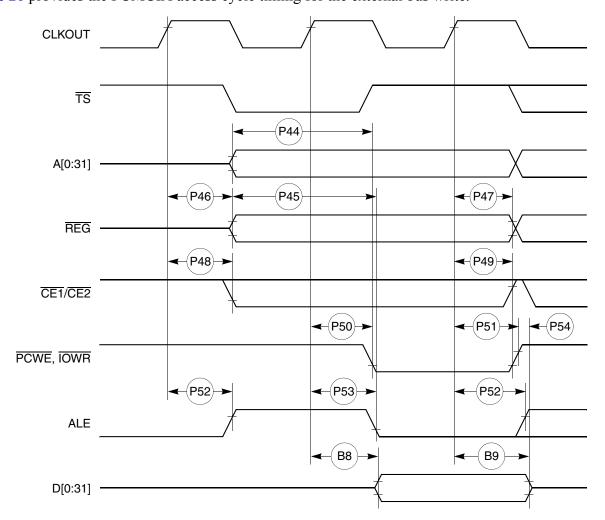

Figure 26 provides the PCMCIA access cycle timing for the external bus write.

Figure 26. PCMCIA Access Cycle Timing External Bus Write

Figure 27 provides the PCMCIA WAIT signal detection timing.

Figure 27. PCMCIA WAIT Signal Detection Timing

36 Freescale Semiconductor

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

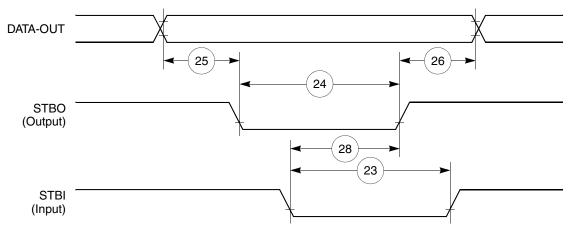

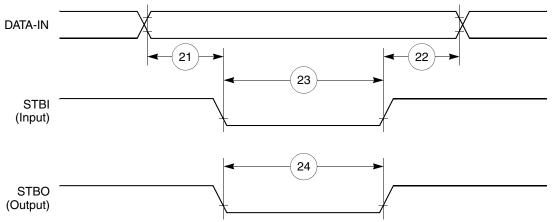

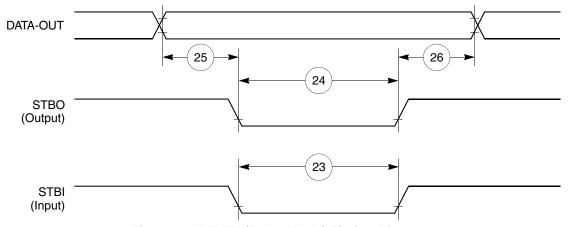

Figure 40. PIP Tx (Interlock Mode) Timing Diagram

Figure 41. PIP Rx (Pulse Mode) Timing Diagram

Figure 42. PIP TX (Pulse Mode) Timing Diagram

## **Table 16. IDMA Controller Timing (continued)**

| N   | Observatoristis                                                                                                       | All Freq | Unit |      |

|-----|-----------------------------------------------------------------------------------------------------------------------|----------|------|------|

| Num | Characteristic                                                                                                        | Min Max  |      | Unit |

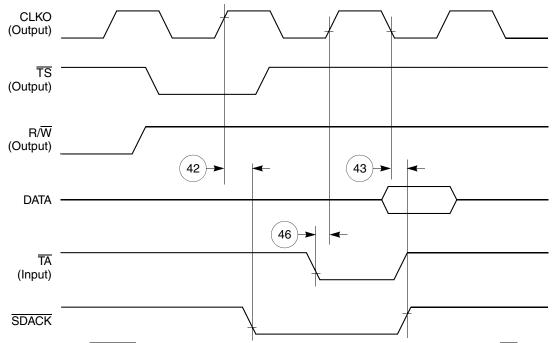

| 42  | SDACK assertion delay from clock high                                                                                 | _        | 12   | ns   |

| 43  | SDACK negation delay from clock low                                                                                   | _        | 12   | ns   |

| 44  | SDACK negation delay from TA low                                                                                      | _        | 20   | ns   |

| 45  | SDACK negation delay from clock high                                                                                  | _        | 15   | ns   |

| 46  | $\overline{\text{TA}}$ assertion to rising edge of the clock setup time (applies to external $\overline{\text{TA}}$ ) | 7        | _    | ns   |

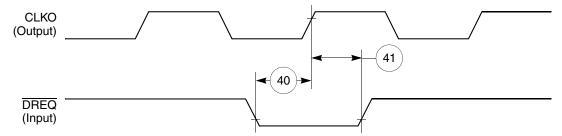

Figure 45. IDMA External Requests Timing Diagram

Figure 46. SDACK Timing Diagram—Peripheral Write, Externally-Generated TA

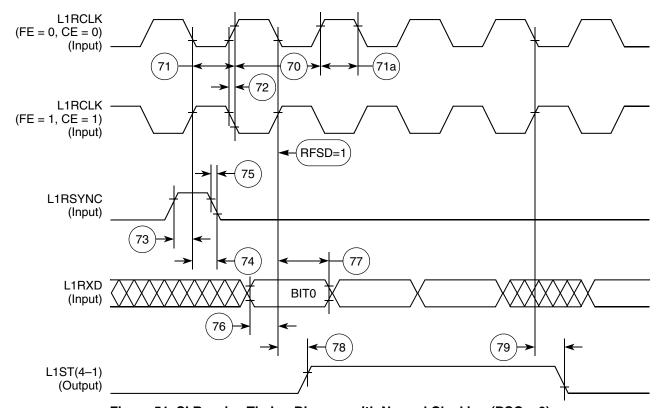

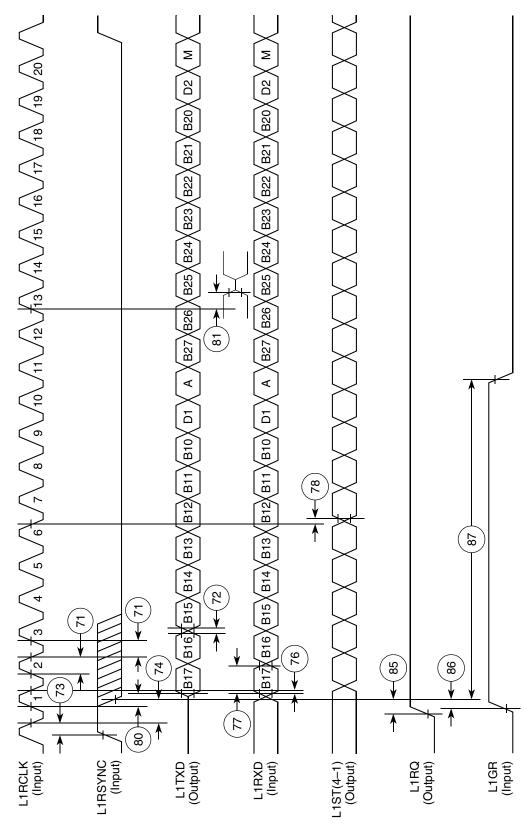

## **Table 19. SI Timing (continued)**

| Num | Characteristic                                                      | All Freq | I I m i t |            |  |

|-----|---------------------------------------------------------------------|----------|-----------|------------|--|

| Num | Characteristic                                                      | Min Max  |           | - Unit     |  |

| 84  | L1CLK edge to L1CLKO valid (DSC = 1)                                | _        | 30.00     | ns         |  |

| 85  | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>              | 1.00     | _         | L1TCL<br>K |  |

| 86  | L1GR setup time <sup>2</sup>                                        | 42.00    | _         | ns         |  |

| 87  | L1GR hold time                                                      | 42.00    | _         | ns         |  |

| 88  | L1CLK edge to L1SYNC valid (FSD = 00) CNT = 0000, BYT = 0, DSC = 0) | _        | 0.00      | ns         |  |

<sup>&</sup>lt;sup>1</sup> The ratio SYNCCLK/L1RCLK must be greater than 2.5/1.

<sup>&</sup>lt;sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever comes later.

Figure 51. SI Receive Timing Diagram with Normal Clocking (DSC = 0)

<sup>&</sup>lt;sup>2</sup> These specs are valid for IDL mode only.

$<sup>^3</sup>$  Where P = 1/CLKOUT. Thus, for a 25-MHz CLKO1 rate, P = 40 ns.

Figure 55. IDL Timing

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

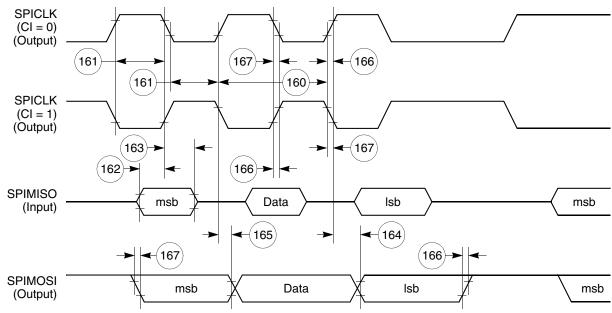

Figure 66. SPI Master (CP = 1) Timing Diagram

# 11.11 SPI Slave AC Electrical Specifications

Table 25 provides the SPI slave timings as shown in Figure 67 and Figure 68.

**Table 25. SPI Slave Timing**

| Num   | Characteristic                                              | All Freq | uencies | Unit             |

|-------|-------------------------------------------------------------|----------|---------|------------------|

| Nulli | Characteristic                                              | Min      | Max     | Oille            |

| 170   | Slave cycle time                                            | 2        | _       | t <sub>cyc</sub> |

| 171   | Slave enable lead time                                      | 15       | _       | ns               |

| 172   | Slave enable lag time                                       | 15       | _       | ns               |

| 173   | Slave clock (SPICLK) high or low time                       | 1        | _       | t <sub>cyc</sub> |

| 174   | Slave sequential transfer delay (does not require deselect) | 1        | _       | t <sub>cyc</sub> |

| 175   | Slave data setup time (inputs)                              | 20       | _       | ns               |

| 176   | Slave data hold time (inputs)                               | 20       | _       | ns               |

| 177   | Slave access time                                           | _        | 50      | ns               |

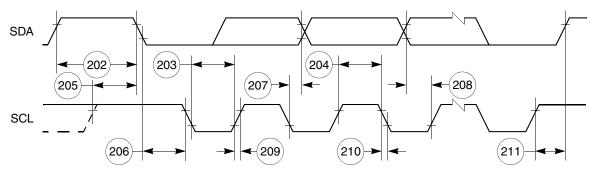

Figure 69 shows the I<sup>2</sup>C bus timing.

Figure 69. I<sup>2</sup>C Bus Timing Diagram

# 12 UTOPIA AC Electrical Specifications

Table 28 shows the AC electrical specifications for the UTOPIA interface.

Table 28. UTOPIA AC Electrical Specifications

| Num | Signal Characteristic                                                  | Direction | Min | Max | Unit |

|-----|------------------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (Internal clock option)                          | Output    | _   | 3.5 | ns   |

|     | Duty cycle                                                             |           | 50  | 50  | %    |

|     | Frequency                                                              |           | _   | 50  | MHz  |

| U1a | UtpClk rise/fall time (external clock option)                          | Input     | _   | 3.5 | ns   |

|     | Duty cycle                                                             |           | 40  | 60  | %    |

|     | Frequency                                                              |           | _   | 50  | MHz  |

| U2  | RxEnb and TxEnb active delay                                           | Output    | 2   | 16  | ns   |

| U3  | UTPB, SOC, Rxclav and Txclav setup time                                | Input     | 8   | _   | ns   |

| U4  | UTPB, SOC, Rxclav and Txclav hold time                                 | Input     | 1   | _   | ns   |

| U5  | UTPB, SOC active delay (and PHREQ and PHSEL active delay in MPHY mode) | Output    | 2   | 16  | ns   |

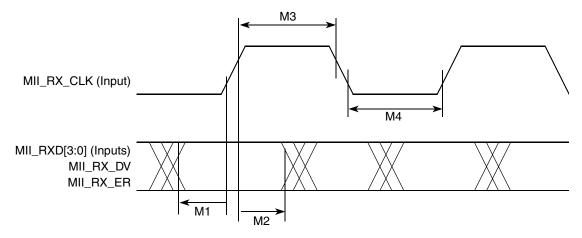

This section provides the AC electrical specifications for the Fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 V or 3.3 V.

#### MII Receive Signal Timing (MII\_RXD[3:0], MII\_RX\_DV, MII\_RX\_ER, 13.1 MII RX CLK)

The receiver functions correctly up to a MII RX CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII RX CLK frequency – 1%.

Table 29 provides information on the MII receive signal timing.

| Num | Characteristic                                         | Min | Max | Unit              |

|-----|--------------------------------------------------------|-----|-----|-------------------|

| M1  | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup | 5   | _   | ns                |

| M2  | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold  | 5   | _   | ns                |

| МЗ  | MII_RX_CLK pulse width high                            | 35% | 65% | MII_RX_CLK period |

| M4  | MII_RX_CLK pulse width low                             | 35% | 65% | MII_RX_CLK period |

**Table 29. MII Receive Signal Timing**

Figure 72 shows MII receive signal timing.

Figure 72. MII Receive Signal Timing Diagram

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10 Freescale Semiconductor 67

## **Mechanical Data and Ordering Information**

Table 34. MPC860 Family Package/Frequency Availability (continued)

| Package Type                                                                      | Freq. (MHz) /<br>Temp. (Tj) | Package            | Order Number                                                                                                                                |

|-----------------------------------------------------------------------------------|-----------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Ball grid array (continued) ZP suffix—leaded ZQ suffix—leaded VR suffix—lead-free | 80<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ80D4 MPC860DEZQ80D4 MPC860DTZQ80D4 MPC860ENZQ80D4 MPC860SRZQ80D4 MPC860TZQ80D4 MPC860DPZQ80D4 MPC860PZQ80D4                        |

|                                                                                   |                             | Tape and Reel      | MPC860PZQ80D4R2<br>MPC860PVR80D4R2                                                                                                          |

|                                                                                   |                             | VR                 | MPC855TVR80D4 MPC860DEVR80D4 MPC860DPVR80D4 MPC860ENVR80D4 MPC860PVR80D4 MPC860SRVR80D4 MPC860TVR80D4                                       |

| Ball grid array (CZP suffix) CZP suffix—leaded CZQ suffix—lead-free               | 50<br>-40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ50D4 MPC855TCVR50D4 MPC860DECZQ50D4 MPC860DTCZQ50D4 MPC860ENCZQ50D4 MPC860SRCZQ50D4 MPC860TCZQ50D4 MPC860DPCZQ50D4 MPC860PCZQ50D4 |

|                                                                                   |                             | Tape and Reel      | MPC855TCZQ50D4R2<br>MC860ENCVR50D4R2                                                                                                        |

|                                                                                   |                             | CVR                | MPC860DECVR50D4 MPC860DTCVR50D4 MPC860ENCVR50D4 MPC860PCVR50D4 MPC860SRCVR50D4 MPC860TCVR50D4                                               |

|                                                                                   | 66<br>-40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ66D4 MPC855TCVR66D4 MPC860ENCZQ66D4 MPC860SRCZQ66D4 MPC860TCZQ66D4 MPC860DPCZQ66D4 MPC860PCZQ66D4                                 |

|                                                                                   |                             | CVR                | MPC860DTCVR66D4<br>MPC860ENCVR66D4<br>MPC860PCVR66D4<br>MPC860SRCVR66D4<br>MPC860TCVR66D4                                                   |

<sup>1</sup> The ZP package is no longer recommended for use. The ZQ package replaces the ZP package.

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC, QorlQ, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. CoreNet, QorlQ Qonverge, QUICC Engine, and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2007-2015 Freescale Semiconductor, Inc.

Document Number: MPC860EC

Rev. 10 09/2015