Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                          |

|---------------------------------|--------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                 |

| Core Processor                  | MPC8xx                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 66MHz                                                                    |

| Co-Processors/DSP               | Communications; CPM                                                      |

| RAM Controllers                 | DRAM                                                                     |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10Mbps (4)                                                               |

| SATA                            | -                                                                        |

| USB                             | -                                                                        |

| Voltage - I/O                   | 3.3V                                                                     |

| Operating Temperature           | -40°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                        |

| Package / Case                  | 357-BBGA                                                                 |

| Supplier Device Package         | 357-PBGA (25x25)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc860srcvr66d4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

## 1 Overview

The MPC860 power quad integrated communications controller (PowerQUICC<sup>TM</sup>) is a versatile one-chip integrated microprocessor and peripheral combination designed for a variety of controller applications. It particularly excels in communications and networking systems. The PowerQUICC unit is referred to as the MPC860 in this hardware specification.

The MPC860 implements Power Architecture<sup>TM</sup> technology and contains a superset of Freescale's MC68360 quad integrated communications controller (QUICC), referred to here as the QUICC, RISC communications processor module (CPM). The CPU on the MPC860 is a 32-bit core built on Power Architecture technology that incorporates memory management units (MMUs) and instruction and data caches.. The CPM from the MC68360 QUICC has been enhanced by the addition of the inter-integrated controller (I<sup>2</sup>C) channel. The memory controller has been enhanced, enabling the MPC860 to support any type of memory, including high-performance memories and new types of DRAMs. A PCMCIA socket controller supports up to two sockets. A real-time clock has also been integrated.

Table 1 shows the functionality supported by the MPC860 family.

|          | Cache (Kbytes)       |            | Ethernet |        |     |     |                        |

|----------|----------------------|------------|----------|--------|-----|-----|------------------------|

| Part     | Instruction<br>Cache | Data Cache | 10T      | 10/100 | ATM | scc | Reference <sup>1</sup> |

| MPC860DE | 4                    | 4          | Up to 2  | _      | _   | 2   | 1                      |

| MPC860DT | 4                    | 4          | Up to 2  | 1      | Yes | 2   | 1                      |

| MPC860DP | 16                   | 8          | Up to 2  | 1      | Yes | 2   | 1                      |

| MPC860EN | 4                    | 4          | Up to 4  | _      | _   | 4   | 1                      |

| MPC860SR | 4                    | 4          | Up to 4  | _      | Yes | 4   | 1                      |

| MPC860T  | 4                    | 4          | Up to 4  | 1      | Yes | 4   | 1                      |

| MPC860P  | 16                   | 8          | Up to 4  | 1      | Yes | 4   | 1                      |

| MPC855T  | 4                    | 4          | 1        | 1      | Yes | 1   | 2                      |

|          |                      |            |          |        |     |     |                        |

**Table 1. MPC860 Family Functionality**

Supporting documentation for these devices refers to the following:

<sup>1.</sup> MPC860 PowerQUICC Family User's Manual (MPC860UM, Rev. 3)

<sup>2.</sup> MPC855T User's Manual (MPC855TUM, Rev. 1)

## 2 Features

The following list summarizes the key MPC860 features:

- Embedded single-issue, 32-bit core (implementing the Power Architecture technology) with thirty-two 32-bit general-purpose registers (GPRs)

- The core performs branch prediction with conditional prefetch without conditional execution.

- 4- or 8-Kbyte data cache and 4- or 16-Kbyte instruction cache (see Table 1)

- 16-Kbyte instruction caches are four-way, set-associative with 256 sets; 4-Kbyte instruction caches are two-way, set-associative with 128 sets.

- 8-Kbyte data caches are two-way, set-associative with 256 sets; 4-Kbyte data caches are two-way, set-associative with 128 sets.

- Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache blocks.

- Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and are lockable on a cache block basis.

- MMUs with 32-entry TLB, fully-associative instruction, and data TLBs

- MMUs support multiple page sizes of 4-, 16-, and 512-Kbytes, and 8-Mbytes; 16 virtual address spaces and 16 protection groups

- Advanced on-chip-emulation debug mode

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- 32 address lines

- Operates at up to 80 MHz

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or RAS to support a DRAM bank.

- Up to 15 wait states programmable per memory bank

- Glueless interface to DRAM, SIMMS, SRAM, EPROM, Flash EPROM, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes to 256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture.

#### **Thermal Characteristics**

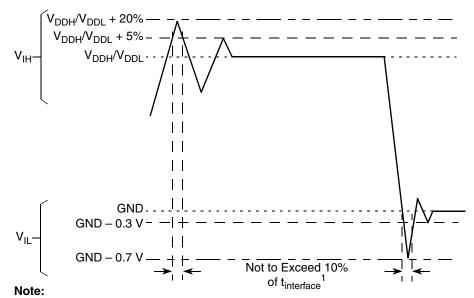

Figure 1 shows the undershoot and overshoot voltages at the interface of the MPC860.

<sup>1.</sup>  $t_{\text{interface}}$  refers to the clock period associated with the bus clock interface.

Figure 1. Undershoot/Overshoot Voltage for V<sub>DDH</sub> and V<sub>DDL</sub>

# 4 Thermal Characteristics

**Table 3. Package Description**

| Package Designator | Package Code (Case No.) | Package Description     |

|--------------------|-------------------------|-------------------------|

| ZP                 | 5050 (1103-01)          | PBGA 357 25*25*0.9P1.27 |

| ZQ/VR              | 5058 (1103D-02)         | PBGA 357 25*25*1.2P1.27 |

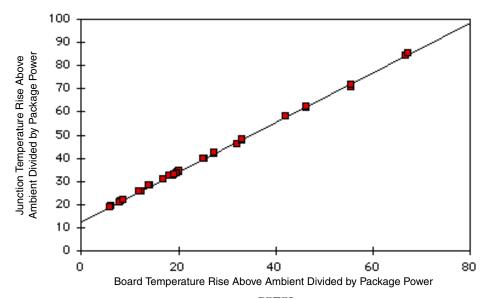

Figure 2. Effect of Board Temperature Rise on Thermal Behavior

If the board temperature is known, an estimate of the junction temperature in the environment can be made using the following equation:

$$T_I = T_B + (R_{\theta IB} \times P_D)$$

where:

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W)

$T_B$  = board temperature (°C)

$P_D$  = power dissipation in package

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. For this method to work, the board and board mounting must be similar to the test board used to determine the junction-to-board thermal resistance, namely a 2s2p (board with a power and a ground plane) and by attaching the thermal balls to the ground plane.

## 7.4 Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple two-resistor model can be used with the thermal simulation of the application [2], or a more accurate and complex model of the package can be used in the thermal simulation.

## 7.5 Experimental Determination

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D})$$

#### **Layout Practices**

where:

$\Psi_{IT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per JEDEC JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

## 7.6 References

Semiconductor Equipment and Materials International (415) 964-5111

805 East Middlefield Rd. Mountain View, CA 94043

MIL-SPEC and EIA/JESD (JEDEC) Specifications 800-854-7179 or (Available from Global Engineering Documents) 303-397-7956

JEDEC Specifications http://www.jedec.org

- 1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 8 Layout Practices

Each  $V_{DD}$  pin on the MPC860 should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on the chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1  $\mu$ F-bypass capacitors located as close as possible to the four sides of the package. The capacitor leads and associated printed circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than half an inch per capacitor lead. A four-layer board employing two inner layers as  $V_{CC}$  and GND planes is recommended.

All output pins on the MPC860 have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of 6 inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{CC}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

## **Table 7. Bus Operation Timings (continued)**

| N    | Observatoristis                                                                                                                      | 33    | MHz   | 40 I  | MHz   | 50 1  | MHz   | 66   | MHz   | 11!4 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|-------|------|

| Num  | Characteristic                                                                                                                       | Min   | Max   | Min   | Max   | Min   | Max   | Min  | Max   | Unit |

| B31a | CLKOUT falling edge to CS valid—as requested by control bit CST1 in the corresponding word in UPM                                    | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B31b | CLKOUT rising edge to CS valid—as requested by control bit CST2 in the corresponding word in UPM                                     | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50 | 8.00  | ns   |

| B31c | CLKOUT rising edge to CS valid—as requested by control bit CST3 in the corresponding word in UPM                                     | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.04 | ns   |

| B31d | CLKOUT falling edge to $\overline{\text{CS}}$ valid—as requested by control bit CST1 in the corresponding word in UPM, EBDF = 1      | 13.26 | 17.99 | 11.28 | 16.00 | 9.40  | 14.13 | 7.58 | 12.31 | ns   |

| B32  | CLKOUT falling edge to BS valid—as requested by control bit BST4 in the corresponding word in UPM                                    | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50 | 6.00  | ns   |

| B32a | CLKOUT falling edge to $\overline{\text{BS}}$ valid—as requested by control bit BST1 in the corresponding word in UPM, EBDF = 0      | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B32b | CLKOUT rising edge to BS valid—as requested by control bit BST2 in the corresponding word in UPM                                     | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50 | 8.00  | ns   |

| B32c | CLKOUT rising edge to BS valid—as requested by control bit BST3 in the corresponding word in UPM                                     | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B32d | CLKOUT falling edge to BS valid—as requested by control bit BST1 in the corresponding word in UPM, EBDF = 1                          | 13.26 | 17.99 | 11.28 | 16.00 | 9.40  | 14.13 | 7.58 | 12.31 | ns   |

| B33  | CLKOUT falling edge to GPL valid—as requested by control bit GxT4 in the corresponding word in UPM                                   | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50 | 6.00  | ns   |

| B33a | CLKOUT rising edge to GPL valid—as requested by control bit GxT3 in the corresponding word in UPM                                    | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B34  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST4 in the corresponding word in UPM | 5.58  | _     | 4.25  | _     | 3.00  | _     | 1.79 | _     | ns   |

| B34a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST1 in the corresponding word in UPM | 13.15 | _     | 10.50 | _     | 8.00  | _     | 5.58 | _     | ns   |

| B34b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST2 in the corresponding word in UPM | 20.73 | _     | 16.75 | _     | 13.00 | _     | 9.36 | _     | ns   |

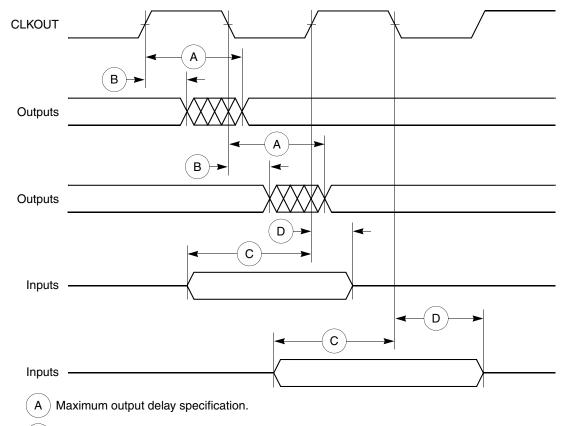

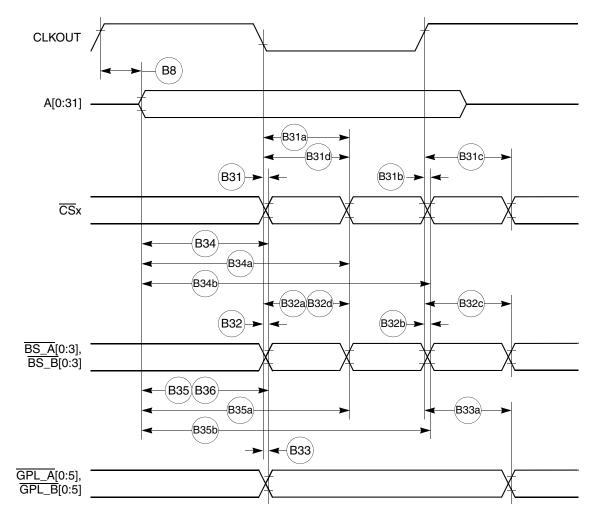

Figure 3 is the control timing diagram.

- (B) Minimum output hold time.

- C Minimum input setup time specification.

- (D) Minimum input hold time specification.

Figure 3. Control Timing

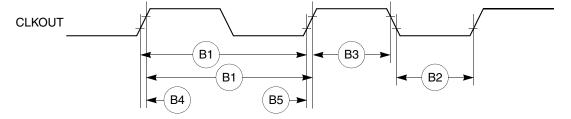

Figure 4 provides the timing for the external clock.

Figure 4. External Clock Timing

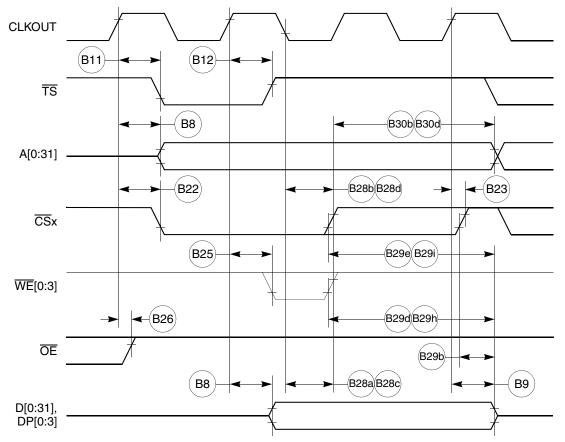

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

## **Bus Signal Timing**

Figure 17 provides the timing for the external bus controlled by the UPM.

Figure 17. External Bus Timing (UPM Controlled Signals)

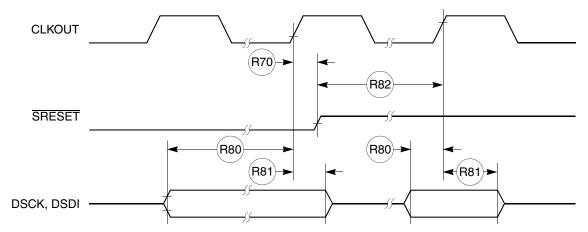

Figure 34 provides the reset timing for the debug port configuration.

Figure 34. Reset Timing—Debug Port Configuration

# 10 IEEE 1149.1 Electrical Specifications

Table 13 provides the JTAG timings for the MPC860 shown in Figure 35 through Figure 38.

| Table | 13. ւ | JTAG | Tim | ing |

|-------|-------|------|-----|-----|

|-------|-------|------|-----|-----|

| Num | Characteristic                                         | All Freq | uencies | Unit |

|-----|--------------------------------------------------------|----------|---------|------|

|     |                                                        | Min      | Max     | Unit |

| J82 | TCK cycle time                                         | 100.00   | _       | ns   |

| J83 | TCK clock pulse width measured at 1.5 V                | 40.00    | _       | ns   |

| J84 | TCK rise and fall times                                | 0.00     | 10.00   | ns   |

| J85 | TMS, TDI data setup time                               | 5.00     | _       | ns   |

| J86 | TMS, TDI data hold time                                | 25.00    | _       | ns   |

| J87 | TCK low to TDO data valid                              | _        | 27.00   | ns   |

| J88 | TCK low to TDO data invalid                            | 0.00     | _       | ns   |

| J89 | TCK low to TDO high impedance                          | _        | 20.00   | ns   |

| J90 | TRST assert time                                       | 100.00   | _       | ns   |

| J91 | TRST setup time to TCK low                             | 40.00    | _       | ns   |

| J92 | TCK falling edge to output valid                       | _        | 50.00   | ns   |

| J93 | TCK falling edge to output valid out of high impedance | _        | 50.00   | ns   |

| J94 | TCK falling edge to output high impedance              | _        | 50.00   | ns   |

| J95 | Boundary scan input valid to TCK rising edge           | 50.00    | _       | ns   |

| J96 | TCK rising edge to boundary scan input invalid         | 50.00    | _       | ns   |

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC860.

## 11.1 PIP/PIO AC Electrical Specifications

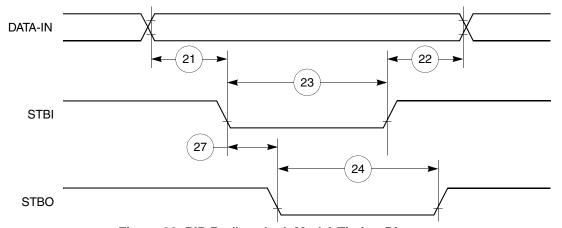

Table 14 provides the PIP/PIO AC timings as shown in Figure 39 through Figure 43.

Table 14. PIP/PIO Timing

| Num   | Characteristic                                                       | All Frequencies       |     | Unit  |

|-------|----------------------------------------------------------------------|-----------------------|-----|-------|

| Nulli | Characteristic                                                       | Min                   | Max | Oille |

| 21    | Data-in setup time to STBI low                                       | 0                     | _   | ns    |

| 22    | Data-in hold time to STBI high                                       | 2.5 – t3 <sup>1</sup> | _   | CLK   |

| 23    | STBI pulse width                                                     | 1.5                   | _   | CLK   |

| 24    | STBO pulse width                                                     | 1 CLK – 5 ns          | _   | ns    |

| 25    | Data-out setup time to STBO low                                      | 2                     | _   | CLK   |

| 26    | Data-out hold time from STBO high                                    | 5                     | _   | CLK   |

| 27    | STBI low to STBO low (Rx interlock)                                  | _                     | 2   | CLK   |

| 28    | STBI low to STBO high (Tx interlock)                                 | 2                     | _   | CLK   |

| 29    | Data-in setup time to clock high                                     | 15                    | _   | ns    |

| 30    | Data-in hold time from clock high                                    | 7.5                   | _   | ns    |

| 31    | Clock low to data-out valid (CPU writes data, control, or direction) | _                     | 25  | ns    |

<sup>1</sup> t3 = Specification 23.

Figure 39. PIP Rx (Interlock Mode) Timing Diagram

# 11.4 Baud Rate Generator AC Electrical Specifications

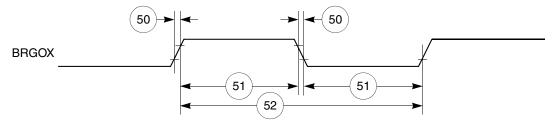

Table 17 provides the baud rate generator timings as shown in Figure 49.

**Table 17. Baud Rate Generator Timing**

| Num | Characteristic          | All Freq | Unit |      |

|-----|-------------------------|----------|------|------|

| Num | Characteristic          | Min      | Max  | Unit |

| 50  | BRGO rise and fall time | _        | 10   | ns   |

| 51  | BRGO duty cycle         | 40       | 60   | %    |

| 52  | BRGO cycle              | 40       | _    | ns   |

Figure 49. Baud Rate Generator Timing Diagram

# 11.5 Timer AC Electrical Specifications

Table 18 provides the general-purpose timer timings as shown in Figure 50.

**Table 18. Timer Timing**

| Num   | Characteristic               | All Freq | Unit |       |

|-------|------------------------------|----------|------|-------|

| Nulli | Characteristic               | Min      | Max  | Oilit |

| 61    | TIN/TGATE rise and fall time | 10       | _    | ns    |

| 62    | TIN/TGATE low time           |          | _    | CLK   |

| 63    | TIN/TGATE high time          |          | _    | CLK   |

| 64    | TIN/TGATE cycle time         | 3        | _    | CLK   |

| 65    | CLKO low to TOUT valid       | 3        | 25   | ns    |

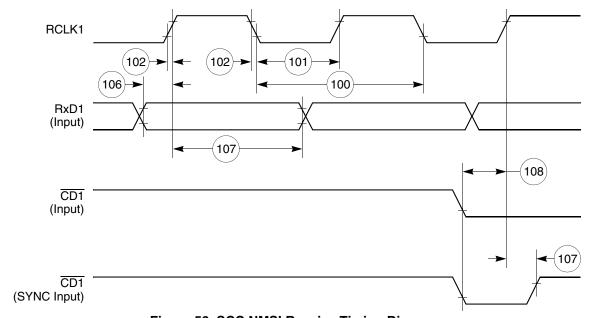

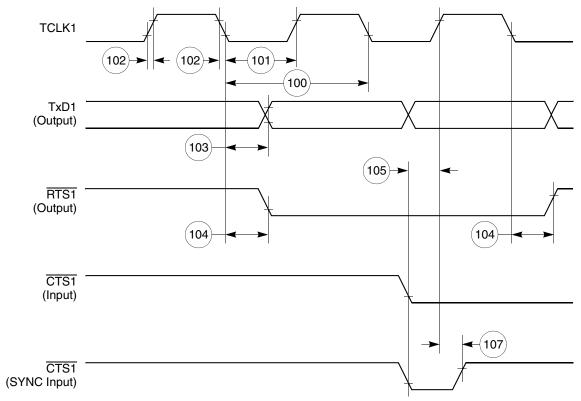

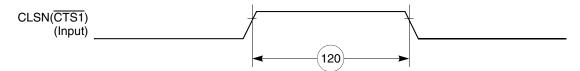

Figure 56 through Figure 58 show the NMSI timings.

Figure 56. SCC NMSI Receive Timing Diagram

Figure 57. SCC NMSI Transmit Timing Diagram

**Table 22. Ethernet Timing (continued)**

| Num | Characteristic                                 | All Freq | Unit |      |

|-----|------------------------------------------------|----------|------|------|

| Num | Characteristic                                 |          | Max  | Unit |

| 135 | RSTRT active delay (from TCLK1 falling edge)   | 10       | 50   | ns   |

| 136 | RSTRT inactive delay (from TCLK1 falling edge) | 10       | 50   | ns   |

| 137 | REJECT width low                               | 1        | _    | CLK  |

| 138 | CLKO1 low to SDACK asserted <sup>2</sup>       | _        | 20   | ns   |

| 139 | CLKO1 low to SDACK negated <sup>2</sup>        | _        | 20   | ns   |

<sup>&</sup>lt;sup>1</sup> The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 2/1.

<sup>&</sup>lt;sup>2</sup> SDACK is asserted whenever the SDMA writes the incoming frame DA into memory.

Figure 59. Ethernet Collision Timing Diagram

Figure 60. Ethernet Receive Timing Diagram

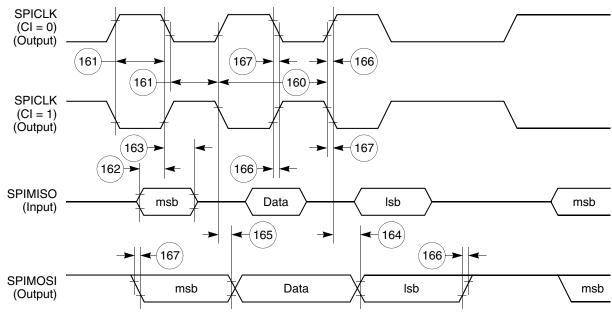

Figure 66. SPI Master (CP = 1) Timing Diagram

# 11.11 SPI Slave AC Electrical Specifications

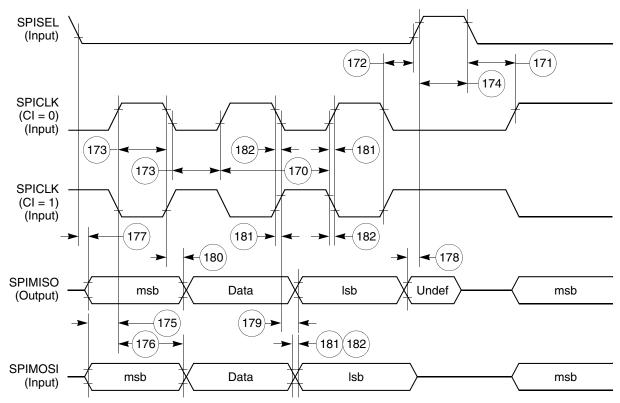

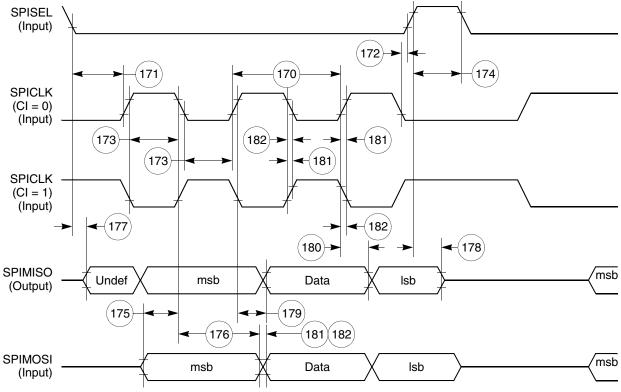

Table 25 provides the SPI slave timings as shown in Figure 67 and Figure 68.

**Table 25. SPI Slave Timing**

| Num   | Characteristic                                              | All Freq | Unit |                  |

|-------|-------------------------------------------------------------|----------|------|------------------|

| Nulli | Ondracteristic                                              |          | Max  | Oille            |

| 170   | Slave cycle time                                            | 2        | _    | t <sub>cyc</sub> |

| 171   | Slave enable lead time                                      | 15       | _    | ns               |

| 172   | Slave enable lag time                                       | 15       | _    | ns               |

| 173   | Slave clock (SPICLK) high or low time                       | 1        | _    | t <sub>cyc</sub> |

| 174   | Slave sequential transfer delay (does not require deselect) | 1        | _    | t <sub>cyc</sub> |

| 175   | Slave data setup time (inputs)                              | 20       | _    | ns               |

| 176   | Slave data hold time (inputs)                               | 20       | _    | ns               |

| 177   | Slave access time                                           | _        | 50   | ns               |

Figure 67. SPI Slave (CP = 0) Timing Diagram

Figure 68. SPI Slave (CP = 1) Timing Diagram

**Mechanical Data and Ordering Information**

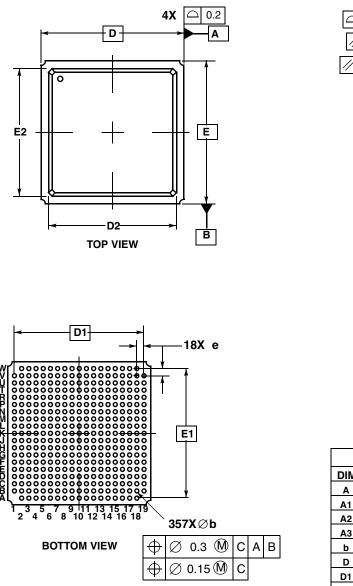

# 14.3 Mechanical Dimensions of the PBGA Package

Figure 77 shows the mechanical dimensions of the ZP PBGA package.

### NOTE

- 1. Dimensions and tolerance per ASME Y14.5M, 1994.

- 2. Dimensions in millimeters.

- Dimension b is the maximum solder ball diameter measured parallel to data C.

|            | MILLIMETERS |       |  |

|------------|-------------|-------|--|

| DIM        | MIN MAX     |       |  |

| Α          |             | 2.05  |  |

| <b>A</b> 1 | 0.50        | 0.70  |  |

| A2         | 0.95        | 1.35  |  |

| А3         | 0.70        | 0.90  |  |

| b          | 0.60        | 0.90  |  |

| D          | 25.00       | BSC   |  |

| D1         | 22.86       | BSC   |  |

| D2         | 22.40       | 22.60 |  |

| е          | 1.27 BSC    |       |  |

| Е          | 25.00 BSC   |       |  |

| E1         | 22.86 BSC   |       |  |

| E2         | 22.40       | 22.60 |  |

SIDE VIEW

0.2 C

Figure 77. Mechanical Dimensions and Bottom Surface Nomenclature of the ZP PBGA Package

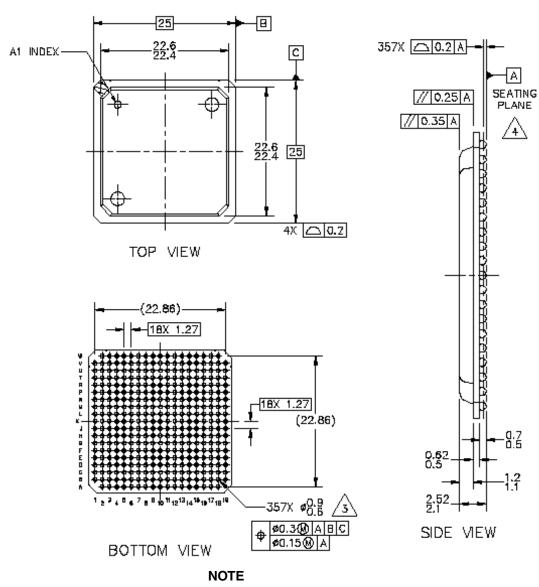

Figure 78 shows the mechanical dimensions of the ZQ PBGA package.

- 1. All Dimensions in millimeters.

- 2. Dimensions and tolerance per ASME Y14.5M, 1994.

- 3. Maximum Solder Ball Diameter measured parallel to Datum A.

- 4. Datum A, the seating plane, is defined by the spherical crowns of the solder balls.

Figure 78. Mechanical Dimensions and Bottom Surface Nomenclature of the ZQ PBGA Package

**Document Revision History**

# 15 Document Revision History

Table 35 lists significant changes between revisions of this hardware specification.

**Table 35. Document Revision History**

| Revision | Date    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10       | 09/2015 | In Table 34, moved MPC855TCVR50D4 and MPC855TCVR66D4 under the extended temperature (–40° to 95°C) and removed MC860ENCVR50D4R2 from the normal temperature Tape and Reel.                                                                                                                                                                                                                                                                                                                               |

| 9        | 10/2011 | Updated orderable part numbers in Table 34, "MPC860 Family Package/Frequency Availability."                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8        | 08/2007 | <ul> <li>Updated template.</li> <li>On page 1, added a second paragraph.</li> <li>After Table 2, inserted a new figure showing the undershoot/overshoot voltage (Figure 1) and renumbered the rest of the figures.</li> <li>In Figure 3, changed all reference voltage measurement points from 0.2 and 0.8 V to 50% level.</li> <li>In Table 16, changed num 46 description to read, "TA assertion to rising edge"</li> <li>In Figure 46, changed TA to reflect the rising edge of the clock.</li> </ul> |

| 7.0      | 9/2004  | <ul> <li>Added a tablefootnote to Table 6 DC Electrical Specifications about meeting the VIL Max of the I2C Standard</li> <li>Replaced the thermal characteristics in Table 4 by the ZQ package</li> <li>Add the new parts to the Ordering and Availablity Chart in Table 34</li> <li>Added the mechanical spec of the ZQ package in Figure 78</li> <li>Removed all of the old revisions from Table 5</li> </ul>                                                                                         |

| 6.3      | 9/2003  | Added Section 11.2 on the Port C interrupt pins     Nontechnical reformatting                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2      | 8/2003  | Changed B28a through B28d and B29d to show that TRLX can be 0 or 1     Changed reference documentation to reflect the Rev 2 MPC860 PowerQUICC Family Users Manual     Nontechnical reformatting                                                                                                                                                                                                                                                                                                          |

| 6.1      | 11/2002 | <ul> <li>Corrected UTOPIA RXenb* and TXenb* timing values</li> <li>Changed incorrect usage of Vcc to Vdd</li> <li>Corrected dual port RAM to 8 Kbytes</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

| 6        | 10/2002 | Added the MPC855T. Corrected Figure 26 on page -36.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.1      | 11/2001 | Revised template format, removed references to MAC functionality, changed Table 7 B23 max value @ 66 MHz from 2ns to 8ns, added this revision history table                                                                                                                                                                                                                                                                                                                                              |

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC, QorlQ, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. CoreNet, QorlQ Qonverge, QUICC Engine, and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2007-2015 Freescale Semiconductor, Inc.

Document Number: MPC860EC

Rev. 10 09/2015