#### NXP USA Inc. - MPC855TCZQ66D4 Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 66MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (1), 10/100Mbps (1)                                             |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | -40°C ~ 95°C (TA)                                                      |

| Security Features               | -                                                                      |

| Package / Case                  | 357-BBGA                                                               |

| Supplier Device Package         | 357-PBGA (25x25)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc855tczq66d4 |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC860. Table 2 provides the maximum ratings.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

(GND = 0 V)

#### Table 2. Maximum Tolerated Ratings

| Rating                              | Symbol              | Value                         | Unit |

|-------------------------------------|---------------------|-------------------------------|------|

| Supply voltage <sup>1</sup>         | V <sub>DDH</sub>    | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDL</sub>    | -0.3 to 4.0                   | V    |

|                                     | KAPWR               | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDSYN</sub>  | -0.3 to 4.0                   | V    |

| Input voltage <sup>2</sup>          | V <sub>in</sub>     | GND – 0.3 to V <sub>DDH</sub> | V    |

| Temperature <sup>3</sup> (standard) | T <sub>A(min)</sub> | 0                             | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Temperature <sup>3</sup> (extended) | T <sub>A(min)</sub> | -40                           | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Storage temperature range           | T <sub>stg</sub>    | –55 to 150                    | °C   |

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC860 is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>i</sub>.

#### Table 4 shows the thermal characteristics for the MPC860.

#### Table 4. MPC860 Thermal Resistance Data

| Rating                           | Env                  | vironment               | Symbol              | ZP<br>MPC860P | ZQ / VR<br>MPC860P | Unit |

|----------------------------------|----------------------|-------------------------|---------------------|---------------|--------------------|------|

| Mold Compound Thicknes           | •                    | 0.85                    | 1.15                | mm            |                    |      |

| Junction-to-ambient <sup>1</sup> | Natural convection   | Single-layer board (1s) | $R_{\theta JA}^2$   | 34            | 34                 | °C/W |

|                                  |                      | Four-layer board (2s2p) | $R_{\thetaJMA}{}^3$ | 22            | 22                 |      |

|                                  | Airflow (200 ft/min) | Single-layer board (1s) | $R_{\thetaJMA}{}^3$ | 27            | 27                 |      |

|                                  |                      | Four-layer board (2s2p) | $R_{\thetaJMA}{}^3$ | 18            | 18                 |      |

| Junction-to-board <sup>4</sup>   |                      |                         | $R_{\theta J B}$    | 14            | 13                 |      |

| Junction-to-case <sup>5</sup>    |                      |                         | $R_{	ext{	heta}JC}$ | 6             | 8                  |      |

| Junction-to-package top 6        | Natural convection   |                         | $\Psi_{JT}$         | 2             | 2                  |      |

<sup>1</sup> Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>4</sup> Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated value from the junction to the exposed pad without contact resistance.

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

**Power Dissipation**

# 5 **Power Dissipation**

Table 5 provides power dissipation information. The modes are 1:1, where CPU and bus speeds are equal, and 2:1, where CPU frequency is twice the bus speed.

| Die Revision | Frequency (MHz) | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|--------------|-----------------|----------------------|----------------------|------|

| D.4          | 50              | 656                  | 735                  | mW   |

| (1:1 mode)   | 66              | TBD                  | TBD                  | mW   |

| D.4          | 66              | 722                  | 762                  | mW   |

| (2:1 mode)   | 80              | 851                  | 909                  | mW   |

#### Table 5. Power Dissipation (PD)

<sup>1</sup> Typical power dissipation is measured at 3.3 V.

<sup>2</sup> Maximum power dissipation is measured at 3.5 V.

NOTE

Values in Table 5 represent  $V_{DDL}$ -based power dissipation and do not include I/O power dissipation over  $V_{DDH}$ . I/O power dissipation varies widely by application due to buffer current, depending on external circuitry.

# 6 DC Characteristics

Table 6 provides the DC electrical characteristics for the MPC860.

Table 6. DC Electrical Specifications

| Characteristic                                                                          | Symbol                                                             | Min                    | Мах                    | Unit |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|------------------------|------|

| Operating voltage at 40 MHz or less                                                     | V <sub>DDH</sub> , V <sub>DDL</sub> , V <sub>DDSYN</sub>           | 3.0                    | 3.6                    | V    |

|                                                                                         | KAPWR<br>(power-down mode)                                         | 2.0                    | 3.6                    | V    |

|                                                                                         | KAPWR<br>(all other operating modes)                               | V <sub>DDH</sub> – 0.4 | V <sub>DDH</sub>       | V    |

| Operating voltage greater than 40 MHz                                                   | V <sub>DDH</sub> , V <sub>DDL</sub> , KAPWR,<br>V <sub>DDSYN</sub> | 3.135                  | 3.465                  | V    |

|                                                                                         | KAPWR<br>(power-down mode)                                         | 2.0                    | 3.6                    | V    |

|                                                                                         | KAPWR<br>(all other operating modes)                               | V <sub>DDH</sub> – 0.4 | V <sub>DDH</sub>       | V    |

| Input high voltage (all inputs except EXTAL and EXTCLK)                                 | V <sub>IH</sub>                                                    | 2.0                    | 5.5                    | V    |

| Input low voltage <sup>1</sup>                                                          | V <sub>IL</sub>                                                    | GND                    | 0.8                    | V    |

| EXTAL, EXTCLK input high voltage                                                        | V <sub>IHC</sub>                                                   | $0.7 	imes (V_{DDH})$  | V <sub>DDH</sub> + 0.3 | V    |

| Input leakage current, $V_{in} = 5.5 \text{ V}$ (except TMS, TRST, DSCK, and DSDI pins) | l <sub>in</sub>                                                    | _                      | 100                    | μA   |

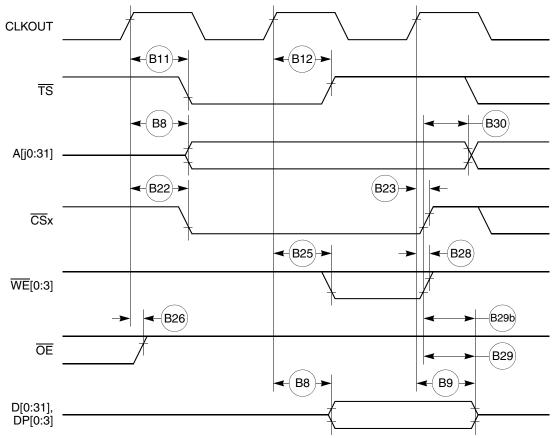

**Bus Signal Timing**

| NI   | Characteristic                                                                                                   | 33 MHz 40 MHz |       | MHz   | 50    | MHz   | 66 MHz |      |       |      |

|------|------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|-------|--------|------|-------|------|

| Num  |                                                                                                                  | Min           | Max   | Min   | Max   | Min   | Max    | Min  | Max   | Unit |

| B9   | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3),<br>TSIZ(0:1), REG, RSV, AT(0:3), PTR High-Z  | 7.58          | 14.33 | 6.25  | 13.00 | 5.00  | 11.75  | 3.80 | 10.04 | ns   |

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion                                                            | 7.58          | 13.58 | 6.25  | 12.25 | 5.00  | 11.00  | 3.80 | 11.29 | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion (when driven by the memory controller or PCMCIA interface) | 2.50          | 9.25  | 2.50  | 9.25  | 2.50  | 9.25   | 2.50 | 9.75  | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation                                                             | 7.58          | 14.33 | 6.25  | 13.00 | 5.00  | 11.75  | 3.80 | 8.54  | ns   |

| B12a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ negation (when driven by the memory controller or PCMCIA interface)  | 2.50          | 11.00 | 2.50  | 11.00 | 2.50  | 11.00  | 2.50 | 9.00  | ns   |

| B13  | CLKOUT to TS, BB High-Z                                                                                          | 7.58          | 21.58 | 6.25  | 20.25 | 5.00  | 19.00  | 3.80 | 14.04 | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ High-Z (when driven by the memory controller or PCMCIA interface)    | 2.50          | 15.00 | 2.50  | 15.00 | 2.50  | 15.00  | 2.50 | 15.00 | ns   |

| B14  | CLKOUT to TEA assertion                                                                                          | 2.50          | 10.00 | 2.50  | 10.00 | 2.50  | 10.00  | 2.50 | 9.00  | ns   |

| B15  | CLKOUT to TEA High-Z                                                                                             | 2.50          | 15.00 | 2.50  | 15.00 | 2.50  | 15.00  | 2.50 | 15.00 | ns   |

| B16  | TA, BI valid to CLKOUT (setup time)                                                                              | 9.75          | _     | 9.75  | —     | 9.75  | —      | 6.00 | —     | ns   |

| B16a | TEA, KR, RETRY, CR valid to CLKOUT (setup time)                                                                  | 10.00         | —     | 10.00 | —     | 10.00 | —      | 4.50 | —     | ns   |

| B16b | $\overline{\text{BB}}, \overline{\text{BG}}, \overline{\text{BR}}, \text{ valid to CLKOUT (setup time)}^5$       | 8.50          |       | 8.50  | _     | 8.50  |        | 4.00 | _     | ns   |

| B17  | CLKOUT to TA, TEA, BI, BB, BG, BR valid (hold time)                                                              | 1.00          | _     | 1.00  | _     | 1.00  | _      | 2.00 | _     | ns   |

| B17a | CLKOUT to KR, RETRY, CR valid (hold time)                                                                        | 2.00          | _     | 2.00  | _     | 2.00  | _      | 2.00 | _     | ns   |

| B18  | D(0:31), DP(0:3) valid to CLKOUT rising edge (setup time) <sup>6</sup>                                           | 6.00          | —     | 6.00  | —     | 6.00  | _      | 6.00 | _     | ns   |

| B19  | CLKOUT rising edge to D(0:31), DP(0:3) valid (hold time) <sup>6</sup>                                            | 1.00          | —     | 1.00  | _     | 1.00  | _      | 2.00 | _     | ns   |

| B20  | D(0:31), DP(0:3) valid to CLKOUT falling edge (setup time) <sup>7</sup>                                          | 4.00          | —     | 4.00  | _     | 4.00  | _      | 4.00 | _     | ns   |

| B21  | CLKOUT falling edge to D(0:31), DP(0:3) valid (hold time) <sup>7</sup>                                           | 2.00          | —     | 2.00  | —     | 2.00  | —      | 2.00 | —     | ns   |

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted GPCM ACS = 00                                                     | 7.58          | 14.33 | 6.25  | 13.00 | 5.00  | 11.75  | 3.80 | 10.04 | ns   |

| B22a | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 10, TRLX = 0                                       | _             | 8.00  |       | 8.00  |       | 8.00   |      | 8.00  | ns   |

| B22b | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = 0, EBDF = 0                             | 7.58          | 14.33 | 6.25  | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B22c | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = 0, EBDF = 1                             | 10.86         | 17.99 | 8.88  | 16.00 | 7.00  | 14.13  | 5.18 | 12.31 | ns   |

## Table 7. Bus Operation Timings (continued)

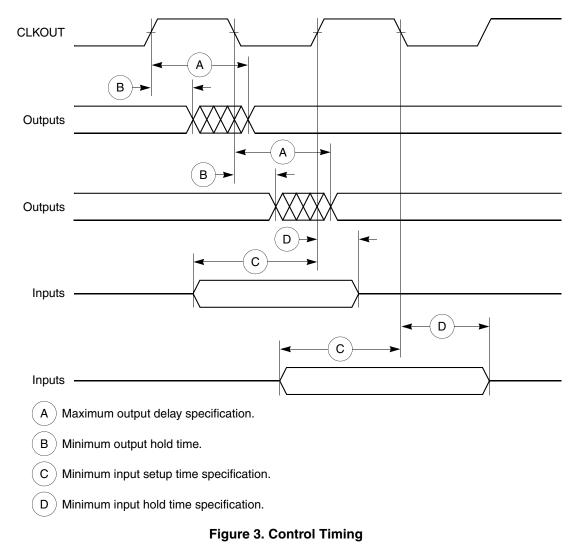

Figure 3 is the control timing diagram.

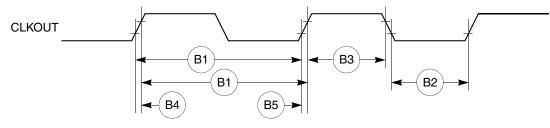

Figure 4 provides the timing for the external clock.

Figure 4. External Clock Timing

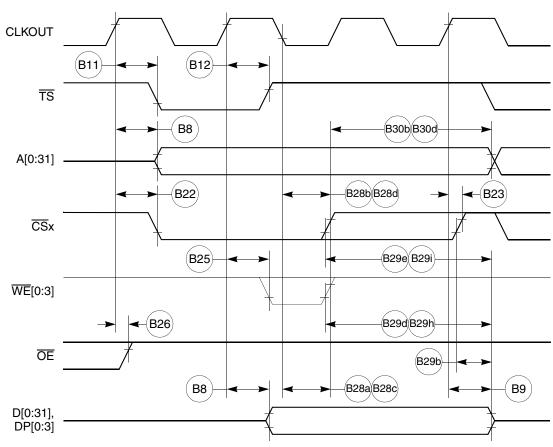

Figure 14 through Figure 16 provide the timing for the external bus write controlled by various GPCM factors.

Figure 14. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 0)

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

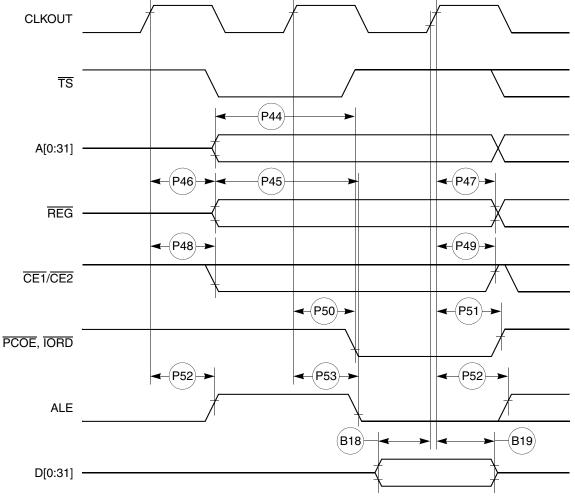

Figure 25 provides the PCMCIA access cycle timing for the external bus read.

Figure 25. PCMCIA Access Cycle Timing External Bus Read

**Bus Signal Timing**

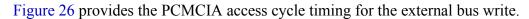

Figure 26. PCMCIA Access Cycle Timing External Bus Write

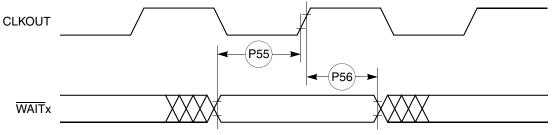

Figure 27 provides the PCMCIA  $\overline{WAIT}$  signal detection timing.

Figure 27. PCMCIA WAIT Signal Detection Timing

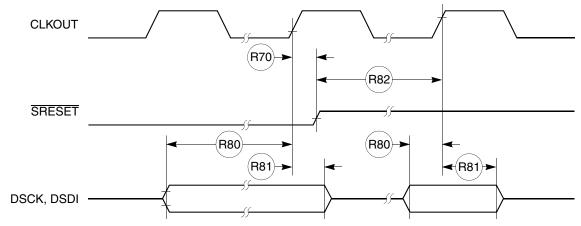

Figure 34 provides the reset timing for the debug port configuration.

Figure 34. Reset Timing—Debug Port Configuration

## **10 IEEE 1149.1 Electrical Specifications**

Table 13 provides the JTAG timings for the MPC860 shown in Figure 35 through Figure 38.

| Num | Characteristic                                         | All Freq | uencies | Unit |

|-----|--------------------------------------------------------|----------|---------|------|

| Num | Characteristic                                         | Min      | Мах     | Unit |

| J82 | TCK cycle time                                         | 100.00   |         | ns   |

| J83 | TCK clock pulse width measured at 1.5 V                | 40.00    | —       | ns   |

| J84 | TCK rise and fall times                                | 0.00     | 10.00   | ns   |

| J85 | TMS, TDI data setup time                               | 5.00     | —       | ns   |

| J86 | TMS, TDI data hold time                                | 25.00    | —       | ns   |

| J87 | TCK low to TDO data valid                              | _        | 27.00   | ns   |

| J88 | TCK low to TDO data invalid                            | 0.00     | —       | ns   |

| J89 | TCK low to TDO high impedance                          | _        | 20.00   | ns   |

| J90 | TRST assert time                                       | 100.00   | —       | ns   |

| J91 | TRST setup time to TCK low                             | 40.00    | —       | ns   |

| J92 | TCK falling edge to output valid                       | _        | 50.00   | ns   |

| J93 | TCK falling edge to output valid out of high impedance | _        | 50.00   | ns   |

| J94 | TCK falling edge to output high impedance              | —        | 50.00   | ns   |

| J95 | Boundary scan input valid to TCK rising edge           | 50.00    | —       | ns   |

| J96 | TCK rising edge to boundary scan input invalid         | 50.00    | —       | ns   |

Table 13. JTAG Timing

**CPM Electrical Characteristics**

# **11 CPM Electrical Characteristics**

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC860.

## 11.1 PIP/PIO AC Electrical Specifications

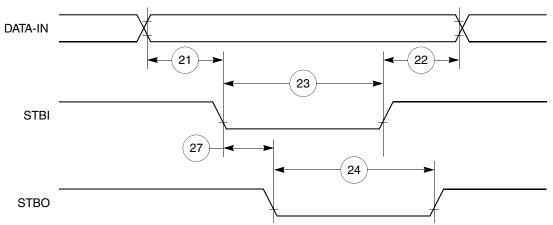

Table 14 provides the PIP/PIO AC timings as shown in Figure 39 through Figure 43.

## Table 14. PIP/PIO Timing

| Num | Characteristic                                                       | All Freq              | uencies | Unit |

|-----|----------------------------------------------------------------------|-----------------------|---------|------|

| Num |                                                                      | Min                   | Max     | onin |

| 21  | Data-in setup time to STBI low                                       | 0                     | _       | ns   |

| 22  | Data-in hold time to STBI high                                       | 2.5 – t3 <sup>1</sup> | —       | CLK  |

| 23  | STBI pulse width                                                     | 1.5                   | _       | CLK  |

| 24  | STBO pulse width                                                     | 1 CLK – 5 ns          | _       | ns   |

| 25  | Data-out setup time to STBO low                                      | 2                     | _       | CLK  |

| 26  | Data-out hold time from STBO high                                    | 5                     | _       | CLK  |

| 27  | STBI low to STBO low (Rx interlock)                                  | —                     | 2       | CLK  |

| 28  | STBI low to STBO high (Tx interlock)                                 | 2                     | _       | CLK  |

| 29  | Data-in setup time to clock high                                     | 15                    | _       | ns   |

| 30  | Data-in hold time from clock high                                    | 7.5                   | _       | ns   |

| 31  | Clock low to data-out valid (CPU writes data, control, or direction) | —                     | 25      | ns   |

<sup>1</sup> t3 = Specification 23.

Figure 39. PIP Rx (Interlock Mode) Timing Diagram

**CPM Electrical Characteristics**

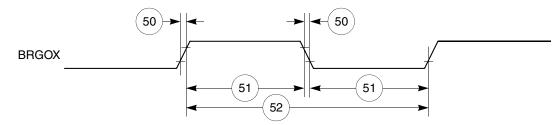

## 11.4 Baud Rate Generator AC Electrical Specifications

Table 17 provides the baud rate generator timings as shown in Figure 49.

#### Table 17. Baud Rate Generator Timing

| Num | Characteristic          | All Freq | uencies | Unit |

|-----|-------------------------|----------|---------|------|

| Num | Characteristic          | Min      | Max     | Unit |

| 50  | BRGO rise and fall time | _        | 10      | ns   |

| 51  | BRGO duty cycle         | 40       | 60      | %    |

| 52  | BRGO cycle              | 40       | _       | ns   |

## Figure 49. Baud Rate Generator Timing Diagram

## **11.5 Timer AC Electrical Specifications**

Table 18 provides the general-purpose timer timings as shown in Figure 50.

### Table 18. Timer Timing

| Num | Characteristic               | All Freq | Unit |      |

|-----|------------------------------|----------|------|------|

| NUM | Characteristic               | Min      | Мах  | Unit |

| 61  | TIN/TGATE rise and fall time | 10       |      | ns   |

| 62  | TIN/TGATE low time           | 1        | _    | CLK  |

| 63  | TIN/TGATE high time          | 2        | —    | CLK  |

| 64  | TIN/TGATE cycle time         | 3        | —    | CLK  |

| 65  | CLKO low to TOUT valid       | 3        | 25   | ns   |

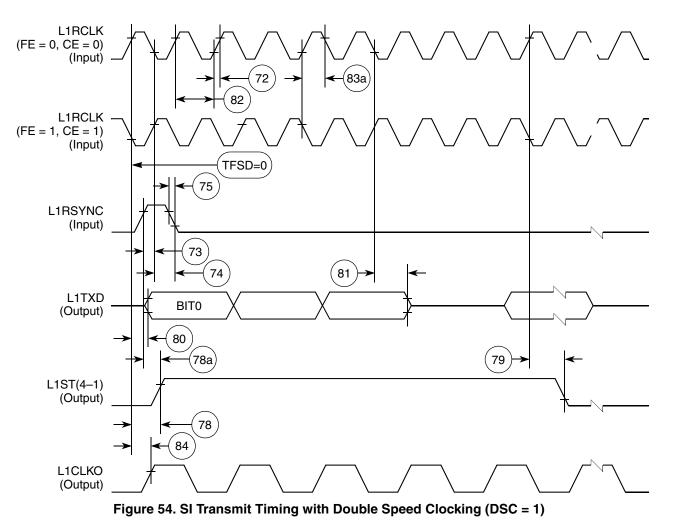

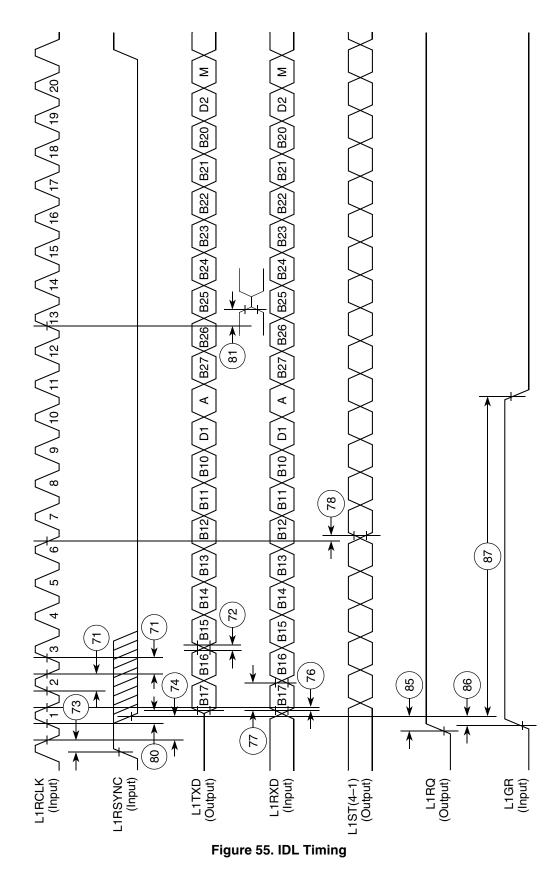

**CPM Electrical Characteristics**

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

**CPM Electrical Characteristics**

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

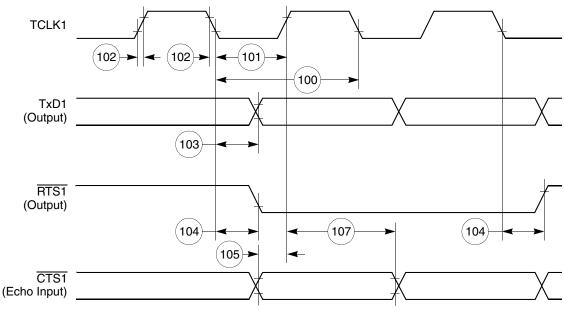

#### SCC in NMSI Mode Electrical Specifications 11.7

Table 20 provides the NMSI external clock timing.

| News | Ok ava stavistis                                     | All Freq      | uencies | 11   |

|------|------------------------------------------------------|---------------|---------|------|

| Num  | Characteristic                                       | Min           | Мах     | Unit |

| 100  | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK     | _       | ns   |

| 101  | RCLK1 and TCLK1 width low                            | 1/SYNCCLK + 5 | _       | ns   |

| 102  | RCLK1 and TCLK1 rise/fall time                       | —             | 15.00   | ns   |

| 103  | TXD1 active delay (from TCLK1 falling edge)          | 0.00          | 50.00   | ns   |

| 104  | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00          | 50.00   | ns   |

| 105  | CTS1 setup time to TCLK1 rising edge                 | 5.00          | —       | ns   |

| 106  | RXD1 setup time to RCLK1 rising edge                 | 5.00          | _       | ns   |

| 107  | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00          | —       | ns   |

| 108  | CD1 setup Time to RCLK1 rising edge                  | 5.00          | _       | ns   |

<sup>1</sup> The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to CD and CTS hold time when they are used as external sync signals.

## Table 21 provides the NMSI internal clock timing.

## Table 21. NMSI Internal Clock Timing

| Num | Characteristic                                       | All Freq | Unit      |      |

|-----|------------------------------------------------------|----------|-----------|------|

|     |                                                      | Min      | Мах       | onit |

| 100 | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00     | SYNCCLK/3 | MHz  |

| 102 | RCLK1 and TCLK1 rise/fall time                       | _        | —         | ns   |

| 103 | TXD1 active delay (from TCLK1 falling edge)          | 0.00     | 30.00     | ns   |

| 104 | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00     | 30.00     | ns   |

| 105 | CTS1 setup time to TCLK1 rising edge                 | 40.00    | —         | ns   |

| 106 | RXD1 setup time to RCLK1 rising edge                 | 40.00    | —         | ns   |

| 107 | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00     | —         | ns   |

| 108 | CD1 setup time to RCLK1 rising edge                  | 40.00    | —         | ns   |

<sup>1</sup> The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{CD}$  and  $\overline{CTS}$  hold time when they are used as external sync signals.

Figure 58. HDLC Bus Timing Diagram

## **11.8 Ethernet Electrical Specifications**

Table 22 provides the Ethernet timings as shown in Figure 59 through Figure 63.

| Num | Characteristic                                                  | All Freq | 11  |      |

|-----|-----------------------------------------------------------------|----------|-----|------|

| NUM |                                                                 | Min      | Мах | Unit |

| 120 | CLSN width high                                                 | 40       | _   | ns   |

| 121 | RCLK1 rise/fall time                                            | —        | 15  | ns   |

| 122 | RCLK1 width low                                                 | 40       | —   | ns   |

| 123 | RCLK1 clock period <sup>1</sup>                                 | 80       | 120 | ns   |

| 124 | RXD1 setup time                                                 | 20       | —   | ns   |

| 125 | RXD1 hold time                                                  | 5        | —   | ns   |

| 126 | RENA active delay (from RCLK1 rising edge of the last data bit) | 10       | —   | ns   |

| 127 | RENA width low                                                  | 100      | —   | ns   |

| 128 | TCLK1 rise/fall time                                            | —        | 15  | ns   |

| 129 | TCLK1 width low                                                 | 40       | —   | ns   |

| 130 | TCLK1 clock period <sup>1</sup>                                 | 99       | 101 | ns   |

| 131 | TXD1 active delay (from TCLK1 rising edge)                      | 10       | 50  | ns   |

| 132 | TXD1 inactive delay (from TCLK1 rising edge)                    | 10       | 50  | ns   |

| 133 | TENA active delay (from TCLK1 rising edge)                      | 10       | 50  | ns   |

| 134 | TENA inactive delay (from TCLK1 rising edge)                    | 10       | 50  | ns   |

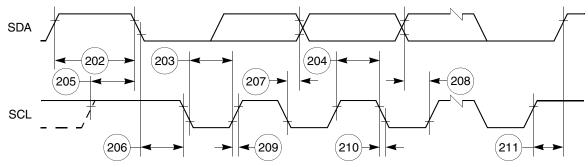

Figure 69 shows the  $I^2C$  bus timing.

Figure 69. I<sup>2</sup>C Bus Timing Diagram

# **12 UTOPIA AC Electrical Specifications**

Table 28 shows the AC electrical specifications for the UTOPIA interface.

| Num | Signal Characteristic                                                  | Direction | Min | Max | Unit |

|-----|------------------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (Internal clock option)                          | Output    | _   | 3.5 | ns   |

|     | Duty cycle                                                             |           | 50  | 50  | %    |

|     | Frequency                                                              |           | —   | 50  | MHz  |

| U1a | UtpClk rise/fall time (external clock option)                          | Input     | _   | 3.5 | ns   |

|     | Duty cycle                                                             |           | 40  | 60  | %    |

|     | Frequency                                                              |           | _   | 50  | MHz  |

| U2  | RxEnb and TxEnb active delay                                           | Output    | 2   | 16  | ns   |

| U3  | UTPB, SOC, Rxclav and Txclav setup time                                | Input     | 8   | —   | ns   |

| U4  | UTPB, SOC, Rxclav and Txclav hold time                                 | Input     | 1   | —   | ns   |

| U5  | UTPB, SOC active delay (and PHREQ and PHSEL active delay in MPHY mode) | Output    | 2   | 16  | ns   |

### Table 28. UTOPIA AC Electrical Specifications

# **13 FEC Electrical Characteristics**

This section provides the AC electrical specifications for the Fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 V or 3.3 V.

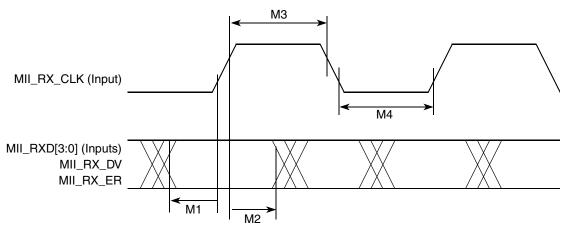

# 13.1 MII Receive Signal Timing (MII\_RXD[3:0], MII\_RX\_DV, MII\_RX\_ER, MII\_RX\_CLK)

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency - 1%.

Table 29 provides information on the MII receive signal timing.

| Num | Characteristic                                         | Min | Max | Unit                 |

|-----|--------------------------------------------------------|-----|-----|----------------------|

| M1  | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup | 5   | _   | ns                   |

| M2  | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold  | 5   | _   | ns                   |

| М3  | MII_RX_CLK pulse width high                            | 35% | 65% | MII_RX_CLK<br>period |

| M4  | MII_RX_CLK pulse width low                             | 35% | 65% | MII_RX_CLK<br>period |

### Table 29. Mll Receive Signal Timing

Figure 72 shows MII receive signal timing.

Figure 72. MII Receive Signal Timing Diagram

#### Mechanical Data and Ordering Information

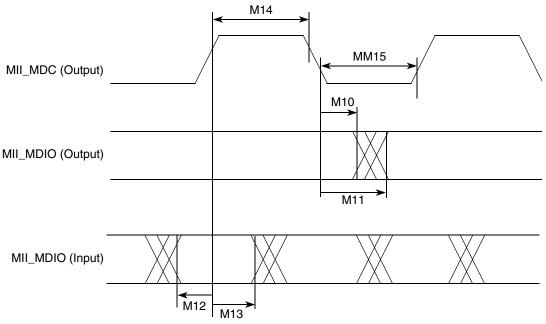

Figure 75 shows the MII serial management channel timing diagram.

Figure 75. MII Serial Management Channel Timing Diagram

# 14 Mechanical Data and Ordering Information

## 14.1 Ordering Information

Table 33 provides information on the MPC860 Revision D.4 derivative devices.

| Device   | Number of<br>SCCs <sup>1</sup> | Ethernet Support <sup>2</sup><br>(Mbps) | Multichannel<br>HDLC Support | ATM<br>Support |

|----------|--------------------------------|-----------------------------------------|------------------------------|----------------|

| MPC855T  | 1                              | 10/100                                  | Yes                          | Yes            |

| MPC860DE | 2                              | 10                                      | N/A                          | N/A            |

| MPC860DT |                                | 10/100                                  | Yes                          | Yes            |

| MPC860DP |                                | 10/100                                  | Yes                          | Yes            |

| MPC860EN | 4                              | 10                                      | N/A                          | N/A            |

| MPC860SR |                                | 10                                      | Yes                          | Yes            |

| MPC860T  |                                | 10/100                                  | Yes                          | Yes            |

| MPC860P  |                                | 10/100                                  | Yes                          | Yes            |

Table 33. MPC860 Family Revision D.4 Derivatives

<sup>1</sup> Serial communications controller (SCC)

<sup>2</sup> Up to 4 channels at 40 MHz or 2 channels at 25 MHz

Mechanical Data and Ordering Information

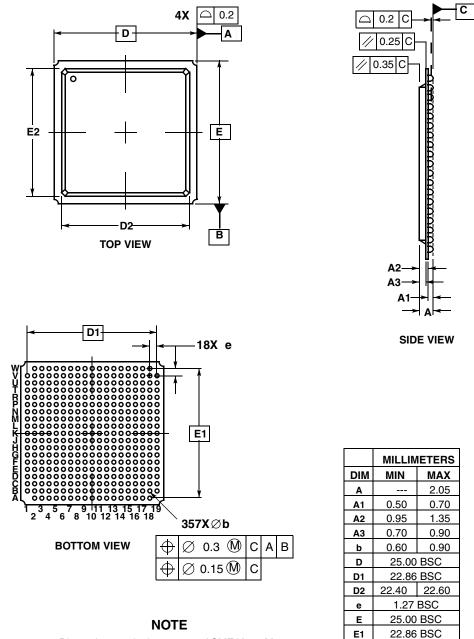

## 14.3 Mechanical Dimensions of the PBGA Package

Figure 77 shows the mechanical dimensions of the ZP PBGA package.

- 1. Dimensions and tolerance per ASME Y14.5M, 1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is the maximum solder ball diameter measured parallel to data C.

22.40

E2

22.60