## NXP USA Inc. - MPC860DTZQ66D4 Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 66MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (2), 10/100Mbps (1)                                             |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                      |

| Package / Case                  | 357-BBGA                                                               |

| Supplier Device Package         | 357-PBGA (25x25)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc860dtzq66d4 |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

# 1 Overview

The MPC860 power quad integrated communications controller (PowerQUICC<sup>TM</sup>) is a versatile one-chip integrated microprocessor and peripheral combination designed for a variety of controller applications. It particularly excels in communications and networking systems. The PowerQUICC unit is referred to as the MPC860 in this hardware specification.

The MPC860 implements Power Architecture<sup>TM</sup> technology and contains a superset of Freescale's MC68360 quad integrated communications controller (QUICC), referred to here as the QUICC, RISC communications proceessor module (CPM). The CPU on the MPC860 is a 32-bit core built on Power Architecture technology that incorporates memory management units (MMUs) and instruction and data caches.. The CPM from the MC68360 QUICC has been enhanced by the addition of the inter-integrated controller (I<sup>2</sup>C) channel. The memory controller has been enhanced, enabling the MPC860 to support any type of memory, including high-performance memories and new types of DRAMs. A PCMCIA socket controller supports up to two sockets. A real-time clock has also been integrated.

Table 1 shows the functionality supported by the MPC860 family.

| Part     | Cache (              | Kbytes)    | Ethe    | ernet  |     |     |                        |

|----------|----------------------|------------|---------|--------|-----|-----|------------------------|

|          | Instruction<br>Cache | Data Cache | 10T     | 10/100 | АТМ | SCC | Reference <sup>1</sup> |

| MPC860DE | 4                    | 4          | Up to 2 | _      | _   | 2   | 1                      |

| MPC860DT | 4                    | 4          | Up to 2 | 1      | Yes | 2   | 1                      |

| MPC860DP | 16                   | 8          | Up to 2 | 1      | Yes | 2   | 1                      |

| MPC860EN | 4                    | 4          | Up to 4 | _      | _   | 4   | 1                      |

| MPC860SR | 4                    | 4          | Up to 4 | —      | Yes | 4   | 1                      |

| MPC860T  | 4                    | 4          | Up to 4 | 1      | Yes | 4   | 1                      |

| MPC860P  | 16                   | 8          | Up to 4 | 1      | Yes | 4   | 1                      |

| MPC855T  | 4                    | 4          | 1       | 1      | Yes | 1   | 2                      |

Table 1. MPC860 Family Functionality

Supporting documentation for these devices refers to the following:

1. MPC860 PowerQUICC Family User's Manual (MPC860UM, Rev. 3)

2. MPC855T User's Manual (MPC855TUM, Rev. 1)

## 2 Features

The following list summarizes the key MPC860 features:

- Embedded single-issue, 32-bit core (implementing the Power Architecture technology) with thirty-two 32-bit general-purpose registers (GPRs)

- The core performs branch prediction with conditional prefetch without conditional execution.

- 4- or 8-Kbyte data cache and 4- or 16-Kbyte instruction cache (see Table 1)

- 16-Kbyte instruction caches are four-way, set-associative with 256 sets; 4-Kbyte instruction caches are two-way, set-associative with 128 sets.

- 8-Kbyte data caches are two-way, set-associative with 256 sets; 4-Kbyte data caches are two-way, set-associative with 128 sets.

- Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache blocks.

- Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and are lockable on a cache block basis.

- MMUs with 32-entry TLB, fully-associative instruction, and data TLBs

- MMUs support multiple page sizes of 4-, 16-, and 512-Kbytes, and 8-Mbytes; 16 virtual address spaces and 16 protection groups

- Advanced on-chip-emulation debug mode

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- 32 address lines

- Operates at up to 80 MHz

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank.

- Up to 15 wait states programmable per memory bank

- Glueless interface to DRAM, SIMMS, SRAM, EPROM, Flash EPROM, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{\text{CAS}}$  lines, four  $\overline{\text{WE}}$  lines, and one  $\overline{\text{OE}}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes to 256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture.

Features

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC)

- Reset controller

- IEEE 1149.1<sup>TM</sup> Std. test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- 23 internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- 10/100 Mbps Ethernet support, fully compliant with the IEEE 802.3u® Standard (not available when using ATM over UTOPIA interface)

- ATM support compliant with ATM forum UNI 4.0 specification

- Cell processing up to 50–70 Mbps at 50-MHz system clock

- Cell multiplexing/demultiplexing

- Support of AAL5 and AAL0 protocols on a per-VC basis. AAL0 support enables OAM and software implementation of other protocols.

- ATM pace control (APC) scheduler, providing direct support for constant bit rate (CBR) and unspecified bit rate (UBR) and providing control mechanisms enabling software support of available bit rate (ABR)

- Physical interface support for UTOPIA (10/100-Mbps is not supported with this interface) and byte-aligned serial (for example, T1/E1/ADSL)

- UTOPIA-mode ATM supports level-1 master with cell-level handshake, multi-PHY (up to four physical layer devices), connection to 25-, 51-, or 155-Mbps framers, and UTOPIA/system clock ratios of 1/2 or 1/3.

- Serial-mode ATM connection supports transmission convergence (TC) function for T1/E1/ADSL lines, cell delineation, cell payload scrambling/descrambling, automatic idle/unassigned cell insertion/stripping, header error control (HEC) generation, checking, and statistics.

- Communications processor module (CPM)

- RISC communications processor (CP)

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

## 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC860. Table 2 provides the maximum ratings.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

(GND = 0 V)

## Table 2. Maximum Tolerated Ratings

| Rating                              | Symbol              | Value                         | Unit |

|-------------------------------------|---------------------|-------------------------------|------|

| Supply voltage <sup>1</sup>         | V <sub>DDH</sub>    | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDL</sub>    | -0.3 to 4.0                   | V    |

|                                     | KAPWR               | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDSYN</sub>  | -0.3 to 4.0                   | V    |

| Input voltage <sup>2</sup>          | V <sub>in</sub>     | GND – 0.3 to V <sub>DDH</sub> | V    |

| Temperature <sup>3</sup> (standard) | T <sub>A(min)</sub> | 0                             | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Temperature <sup>3</sup> (extended) | T <sub>A(min)</sub> | -40                           | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Storage temperature range           | T <sub>stg</sub>    | –55 to 150                    | °C   |

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC860 is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>i</sub>.

### Table 4 shows the thermal characteristics for the MPC860.

### Table 4. MPC860 Thermal Resistance Data

| Rating                           | Env                  | vironment               | Symbol              | ZP<br>MPC860P | ZQ / VR<br>MPC860P | Unit |

|----------------------------------|----------------------|-------------------------|---------------------|---------------|--------------------|------|

| Mold Compound Thickness          |                      |                         |                     |               | 1.15               | mm   |

| Junction-to-ambient <sup>1</sup> | Natural convection   | Single-layer board (1s) | $R_{\theta JA}^2$   | 34            | 34                 | °C/W |

|                                  |                      | Four-layer board (2s2p) | $R_{\thetaJMA}{}^3$ | 22            | 22                 |      |

|                                  | Airflow (200 ft/min) | Single-layer board (1s) | $R_{\thetaJMA}{}^3$ | 27            | 27                 |      |

|                                  |                      | Four-layer board (2s2p) | $R_{\thetaJMA}{}^3$ | 18            | 18                 |      |

| Junction-to-board <sup>4</sup>   |                      |                         | $R_{\theta J B}$    | 14            | 13                 |      |

| Junction-to-case <sup>5</sup>    |                      |                         | $R_{	ext{	heta}JC}$ | 6             | 8                  |      |

| Junction-to-package top 6        | Natural convection   |                         | $\Psi_{JT}$         | 2             | 2                  |      |

<sup>1</sup> Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>4</sup> Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated value from the junction to the exposed pad without contact resistance.

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

|      | Chavastavistis                                                                                                                        | 33    | MHz   | 40 I  | MHz 50 MHz |       | MHz   | 66   | MHz   |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------------|-------|-------|------|-------|------|

| Num  | Characteristic                                                                                                                        | Min   | Max   | Min   | Max        | Min   | Max   | Min  | Max   | Unit |

| B31a | CLKOUT falling edge to CS valid—as requested by control bit CST1 in the corresponding word in UPM                                     | 7.58  | 14.33 | 6.25  | 13.00      | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid—as<br>requested by control bit CST2 in the<br>corresponding word in UPM                   | 1.50  | 8.00  | 1.50  | 8.00       | 1.50  | 8.00  | 1.50 | 8.00  | ns   |

| B31c | CLKOUT rising edge to $\overline{CS}$ valid—as requested by control bit CST3 in the corresponding word in UPM                         | 7.58  | 14.33 | 6.25  | 13.00      | 5.00  | 11.75 | 3.80 | 10.04 | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$ valid—as<br>requested by control bit CST1 in the<br>corresponding word in UPM, EBDF = 1        | 13.26 | 17.99 | 11.28 | 16.00      | 9.40  | 14.13 | 7.58 | 12.31 | ns   |

| B32  | CLKOUT falling edge to BS valid—as<br>requested by control bit BST4 in the<br>corresponding word in UPM                               | 1.50  | 6.00  | 1.50  | 6.00       | 1.50  | 6.00  | 1.50 | 6.00  | ns   |

| B32a | CLKOUT falling edge to $\overline{\text{BS}}$ valid—as<br>requested by control bit BST1 in the<br>corresponding word in UPM, EBDF = 0 | 7.58  | 14.33 | 6.25  | 13.00      | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B32b | CLKOUT rising edge to BS valid—as<br>requested by control bit BST2 in the<br>corresponding word in UPM                                | 1.50  | 8.00  | 1.50  | 8.00       | 1.50  | 8.00  | 1.50 | 8.00  | ns   |

| B32c | CLKOUT rising edge to BS valid—as<br>requested by control bit BST3 in the<br>corresponding word in UPM                                | 7.58  | 14.33 | 6.25  | 13.00      | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B32d | CLKOUT falling edge to $\overline{BS}$ valid—as<br>requested by control bit BST1 in the<br>corresponding word in UPM, EBDF = 1        | 13.26 | 17.99 | 11.28 | 16.00      | 9.40  | 14.13 | 7.58 | 12.31 | ns   |

| B33  | CLKOUT falling edge to GPL valid—as<br>requested by control bit GxT4 in the<br>corresponding word in UPM                              | 1.50  | 6.00  | 1.50  | 6.00       | 1.50  | 6.00  | 1.50 | 6.00  | ns   |

| B33a | CLKOUT rising edge to GPL valid—as<br>requested by control bit GxT3 in the<br>corresponding word in UPM                               | 7.58  | 14.33 | 6.25  | 13.00      | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B34  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST4 in the corresponding word in UPM         | 5.58  | —     | 4.25  | —          | 3.00  |       | 1.79 | —     | ns   |

| B34a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST1 in the corresponding word in UPM         | 13.15 | —     | 10.50 | —          | 8.00  | —     | 5.58 | —     | ns   |

| B34b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST2 in the corresponding word in UPM         | 20.73 | _     | 16.75 |            | 13.00 |       | 9.36 |       | ns   |

## Table 7. Bus Operation Timings (continued)

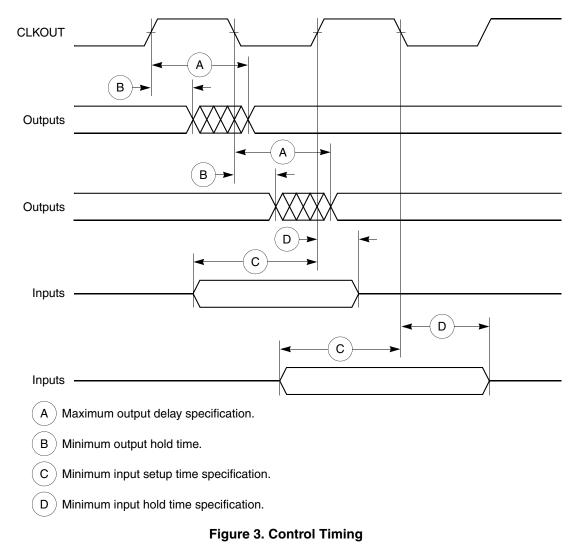

Figure 3 is the control timing diagram.

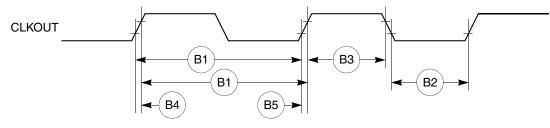

Figure 4 provides the timing for the external clock.

Figure 4. External Clock Timing

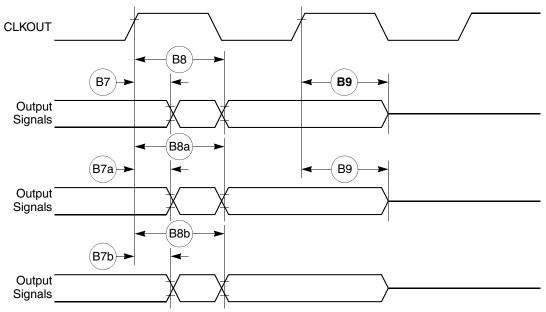

Figure 5 provides the timing for the synchronous output signals.

Figure 5. Synchronous Output Signals Timing

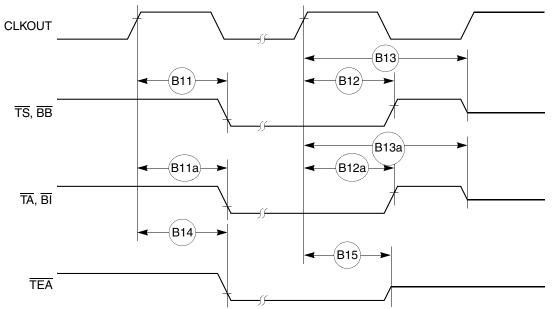

Figure 6 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 6. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

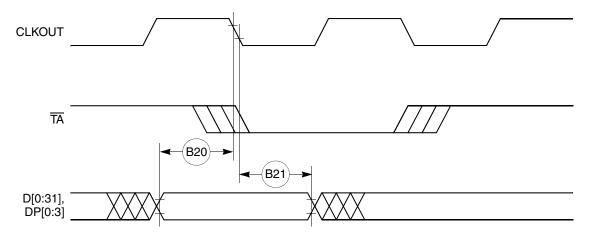

Figure 9 provides the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

Figure 9. Input Data Timing when Controlled by UPM in the Memory Controller and DLT3 = 1

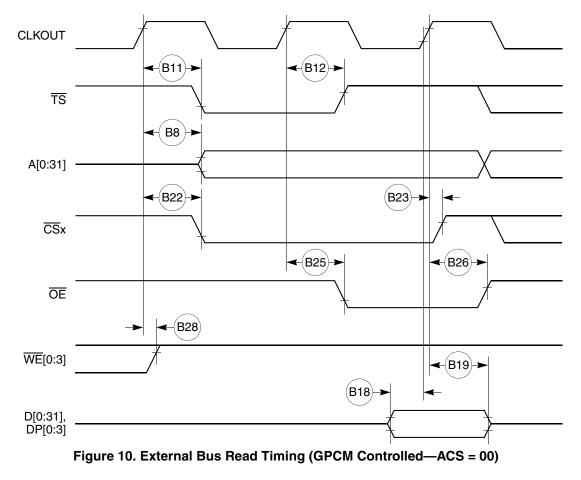

Figure 10 through Figure 13 provide the timing for the external bus read controlled by various GPCM factors.

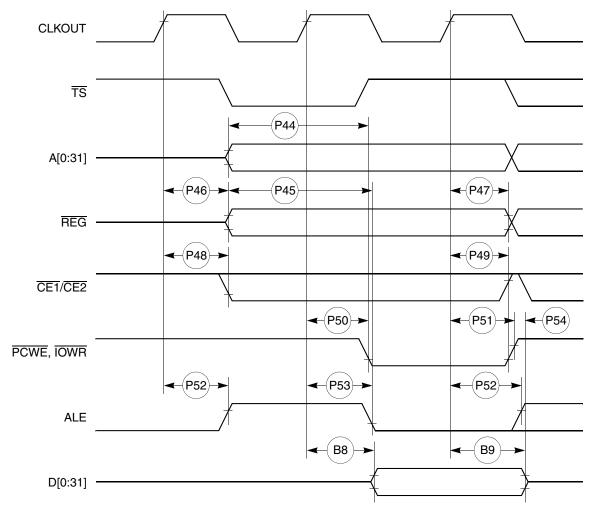

## Table 9 shows the PCMCIA timing for the MPC860.

Table 9. PCMCIA Timing

| Num | Characteristic                                                              | 33    | MHz   | 40    | MHz   | 50 I  | MHz   | 66 I  | MHz   | Unit |

|-----|-----------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Num | Characteristic                                                              | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| P44 | A(0:31), REG valid to PCMCIA Strobe asserted <sup>1</sup>                   | 20.73 | —     | 16.75 | —     | 13.00 | —     | 9.36  | —     | ns   |

| P45 | A(0:31), $\overline{\text{REG}}$ valid to ALE negation <sup>1</sup>         | 28.30 | —     | 23.00 | —     | 18.00 | —     | 13.15 | —     | ns   |

| P46 | CLKOUT to REG valid                                                         | 7.58  | 15.58 | 6.25  | 14.25 | 5.00  | 13.00 | 3.79  | 11.84 | ns   |

| P47 | CLKOUT to REG invalid                                                       | 8.58  | —     | 7.25  | —     | 6.00  | —     | 4.84  | —     | ns   |

| P48 | CLKOUT to CE1, CE2 asserted                                                 | 7.58  | 15.58 | 6.25  | 14.25 | 5.00  | 13.00 | 3.79  | 11.84 | ns   |

| P49 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ negated                       | 7.58  | 15.58 | 6.25  | 14.25 | 5.00  | 13.00 | 3.79  | 11.84 | ns   |

| P50 | CLKOUT to PCOE, IORD, PCWE, IOWR assert time                                | —     | 11.00 |       | 11.00 | _     | 11.00 | —     | 11.00 | ns   |

| P51 | CLKOUT to PCOE, IORD, PCWE, IOWR negate time                                | 2.00  | 11.00 | 2.00  | 11.00 | 2.00  | 11.00 | 2.00  | 11.00 | ns   |

| P52 | CLKOUT to ALE assert time                                                   | 7.58  | 15.58 | 6.25  | 14.25 | 5.00  | 13.00 | 3.79  | 10.04 | ns   |

| P53 | CLKOUT to ALE negate time                                                   | —     | 15.58 |       | 14.25 |       | 13.00 | —     | 11.84 | ns   |

| P54 | PCWE, IOWR negated to D(0:31) invalid <sup>1</sup>                          | 5.58  | —     | 4.25  | —     | 3.00  | —     | 1.79  | —     | ns   |

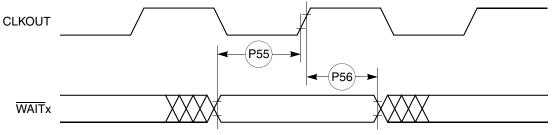

| P55 | ${\text{WAITA}} \text{ and } {\text{WAITB}} \text{ valid to CLKOUT rising}$ | 8.00  | —     | 8.00  | —     | 8.00  | —     | 8.00  | —     | ns   |

| P56 | CLKOUT rising edge to WAITA and WAITB invalid <sup>1</sup>                  | 2.00  | _     | 2.00  | _     | 2.00  | _     | 2.00  | _     | ns   |

<sup>1</sup> PSST = 1. Otherwise add PSST times cycle time.

PSHT = 0. Otherwise add PSHT times cycle time.

These synchronous timings define when the WAITx signals are detected in order to freeze (or relieve) the PCMCIA current cycle. The WAITx assertion will be effective only if it is detected 2 cycles before the PSL timer expiration. See Chapter 16, "PCMCIA Interface," in the *MPC860 PowerQUICCTM Family User's Manual*.

Figure 26. PCMCIA Access Cycle Timing External Bus Write

Figure 27 provides the PCMCIA  $\overline{WAIT}$  signal detection timing.

Figure 27. PCMCIA WAIT Signal Detection Timing

#### **IEEE 1149.1 Electrical Specifications**

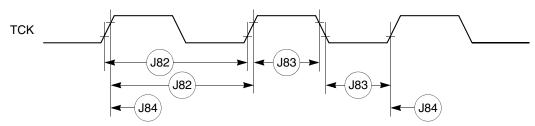

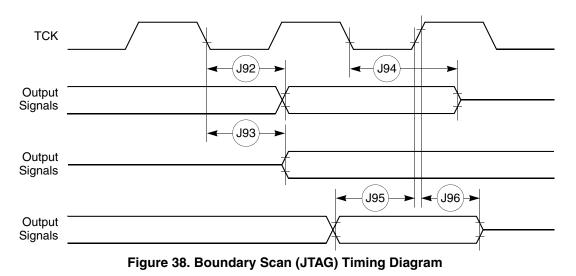

### Figure 35. JTAG Test Clock Input Timing

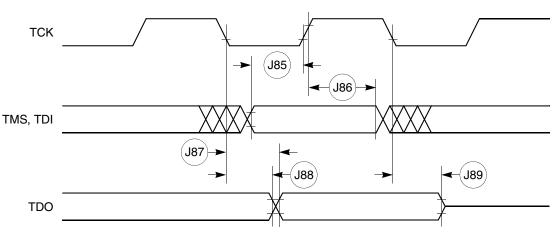

Figure 36. JTAG Test Access Port Timing Diagram

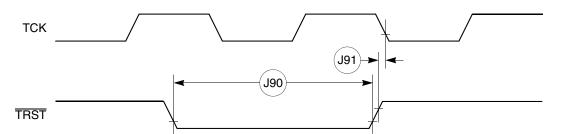

Figure 37. JTAG TRST Timing Diagram

## 11.4 Baud Rate Generator AC Electrical Specifications

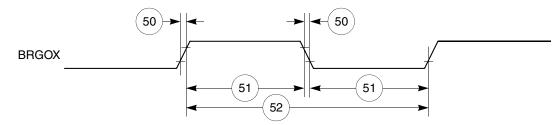

Table 17 provides the baud rate generator timings as shown in Figure 49.

### Table 17. Baud Rate Generator Timing

| Num | Characteristic          | All Freq | uencies | Unit |

|-----|-------------------------|----------|---------|------|

| Num | Characteristic          | Min      | Max     | Unit |

| 50  | BRGO rise and fall time | _        | 10      | ns   |

| 51  | BRGO duty cycle         | 40       | 60      | %    |

| 52  | BRGO cycle              | 40       | _       | ns   |

## Figure 49. Baud Rate Generator Timing Diagram

## **11.5 Timer AC Electrical Specifications**

Table 18 provides the general-purpose timer timings as shown in Figure 50.

## Table 18. Timer Timing

| Num | Ohavastaviatia               | All Freq | uencies | Unit |

|-----|------------------------------|----------|---------|------|

| NUM | Characteristic               | Min      | Мах     | Unit |

| 61  | TIN/TGATE rise and fall time | 10       |         | ns   |

| 62  | TIN/TGATE low time           | 1        | _       | CLK  |

| 63  | TIN/TGATE high time          | 2        | —       | CLK  |

| 64  | TIN/TGATE cycle time         | 3        | —       | CLK  |

| 65  | CLKO low to TOUT valid       | 3        | 25      | ns   |

| Num | Characteristic                                                      | All Freq | Unit  |            |

|-----|---------------------------------------------------------------------|----------|-------|------------|

|     | Characteristic                                                      | Min      | Max   | Unit       |

| 84  | L1CLK edge to L1CLKO valid (DSC = 1)                                | _        | 30.00 | ns         |

| 85  | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>              | 1.00     | —     | L1TCL<br>K |

| 86  | L1GR setup time <sup>2</sup>                                        | 42.00    | _     | ns         |

| 87  | L1GR hold time                                                      | 42.00    | —     | ns         |

| 88  | L1CLK edge to L1SYNC valid (FSD = 00) CNT = 0000, BYT = 0, DSC = 0) | _        | 0.00  | ns         |

### Table 19. SI Timing (continued)

<sup>1</sup> The ratio SYNCCLK/L1RCLK must be greater than 2.5/1.

<sup>2</sup> These specs are valid for IDL mode only.

<sup>3</sup> Where P = 1/CLKOUT. Thus, for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever comes later.

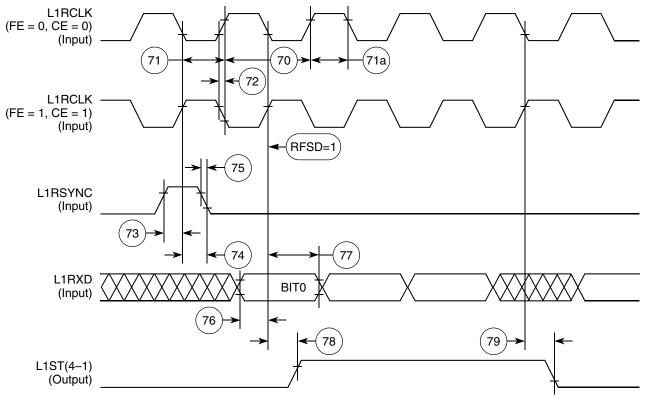

Figure 51. SI Receive Timing Diagram with Normal Clocking (DSC = 0)

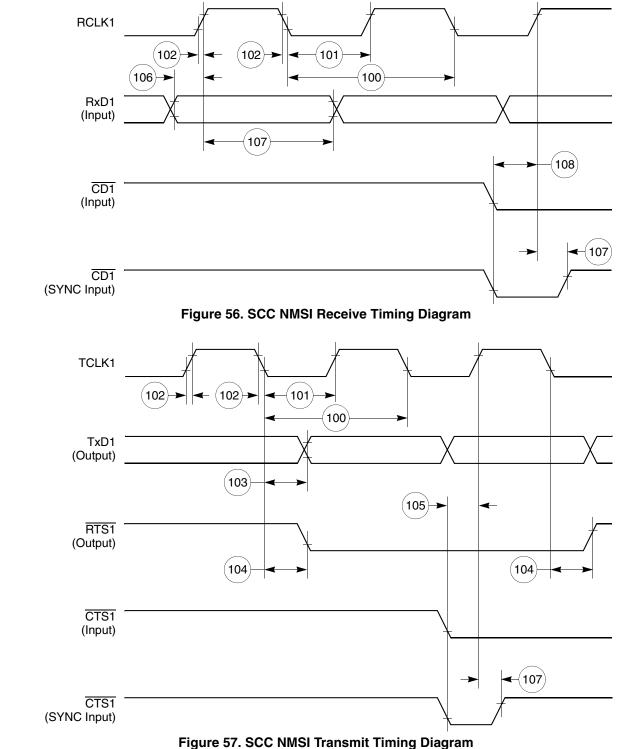

Figure 56 through Figure 58 show the NMSI timings.

rigure 57. See NMSF fransline finning Diagram

## **11.10 SPI Master AC Electrical Specifications**

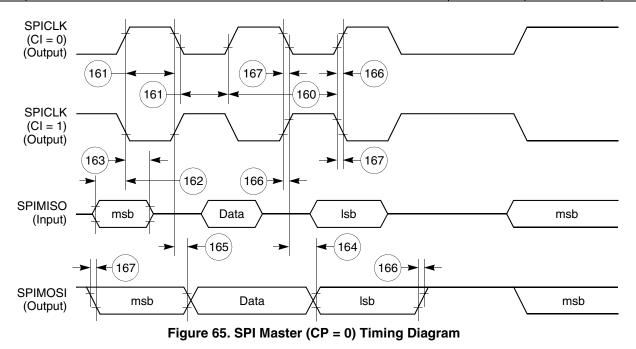

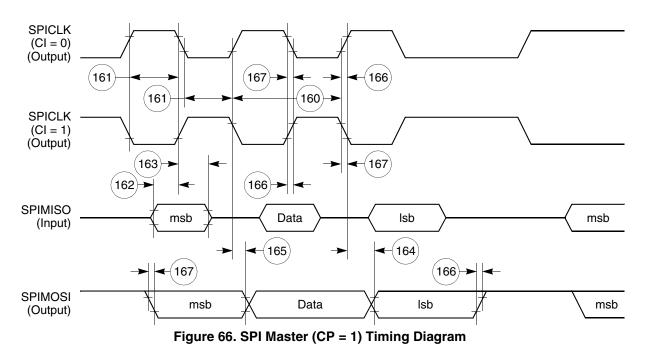

Table 24 provides the SPI master timings as shown in Figure 65 and Figure 66.

### Table 24. SPI Master Timing

| Num | Characteristic                      | All Freq | uencies | Unit             |

|-----|-------------------------------------|----------|---------|------------------|

| num | Characteristic                      | Min      | Мах     | Unit             |

| 160 | MASTER cycle time                   | 4        | 1024    | t <sub>cyc</sub> |

| 161 | MASTER clock (SCK) high or low time | 2        | 512     | t <sub>cyc</sub> |

| 162 | MASTER data setup time (inputs)     | 50       | —       | ns               |

| 163 | Master data hold time (inputs)      | 0        | —       | ns               |

| 164 | Master data valid (after SCK edge)  | —        | 20      | ns               |

| 165 | Master data hold time (outputs)     | 0        | —       | ns               |

| 166 | Rise time output                    | —        | 15      | ns               |

| 167 | Fall time output                    | —        | 15      | ns               |

## **11.11 SPI Slave AC Electrical Specifications**

Table 25 provides the SPI slave timings as shown in Figure 67 and Figure 68.

## Table 25. SPI Slave Timing

| Num | Characteristic                                              | All Freq | uencies | Unit             |

|-----|-------------------------------------------------------------|----------|---------|------------------|

| Num | Characteristic                                              | Min      | Мах     | Omi              |

| 170 | Slave cycle time                                            | 2        | —       | t <sub>cyc</sub> |

| 171 | Slave enable lead time                                      | 15       | —       | ns               |

| 172 | Slave enable lag time                                       | 15       | —       | ns               |

| 173 | Slave clock (SPICLK) high or low time                       | 1        | —       | t <sub>cyc</sub> |

| 174 | Slave sequential transfer delay (does not require deselect) | 1        | —       | t <sub>cyc</sub> |

| 175 | Slave data setup time (inputs)                              | 20       | —       | ns               |

| 176 | Slave data hold time (inputs)                               | 20       | —       | ns               |

| 177 | Slave access time                                           | _        | 50      | ns               |

## 11.12 I<sup>2</sup>C AC Electrical Specifications

Table 26 provides the  $I^2C$  (SCL < 100 kHz) timings.

## Table 26. I<sup>2</sup>C Timing (SCL < 100 kHz)

| Num | Characteristic                            | All Freq | uencies | Unit |

|-----|-------------------------------------------|----------|---------|------|

| Num | Characteristic                            | Min      | Max     | Onit |

| 200 | SCL clock frequency (slave)               | 0        | 100     | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100     | kHz  |

| 202 | Bus free time between transmissions       | 4.7      | _       | μS   |

| 203 | Low period of SCL                         | 4.7      | —       | μS   |

| 204 | High period of SCL                        | 4.0      | —       | μS   |

| 205 | Start condition setup time                | 4.7      | —       | μS   |

| 206 | Start condition hold time                 | 4.0      | —       | μS   |

| 207 | Data hold time                            | 0        | —       | μS   |

| 208 | Data setup time                           | 250      | —       | ns   |

| 209 | SDL/SCL rise time                         | —        | 1       | μS   |

| 210 | SDL/SCL fall time                         | —        | 300     | ns   |

| 211 | Stop condition setup time                 | 4.7      | —       | μS   |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3 × pre\_scaler × 2). The ratio SYNCCLK/(BRGCLK/pre\_scaler) must be greater than or equal to 4/1.

## Table 27 provides the $I^2C$ (SCL > 100 kHz) timings.

## Table 27. . I<sup>2</sup>C Timing (SCL > 100 kHz)

| Num | Characteristic                            | Expression | All Freq        | Unit          |    |

|-----|-------------------------------------------|------------|-----------------|---------------|----|

|     | Gharacteristic                            | Expression | Min             | Мах           |    |

| 200 | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48     | Hz |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48     | Hz |

| 202 | Bus free time between transmissions       |            | 1/(2.2 * fSCL)  | —             | s  |

| 203 | Low period of SCL                         |            | 1/(2.2 * fSCL)  | —             | s  |

| 204 | High period of SCL                        |            | 1/(2.2 * fSCL)  | _             | S  |

| 205 | Start condition setup time                |            | 1/(2.2 * fSCL)  | —             | S  |

| 206 | Start condition hold time                 |            | 1/(2.2 * fSCL)  | —             | S  |

| 207 | Data hold time                            |            | 0               | _             | S  |

| 208 | Data setup time                           |            | 1/(40 * fSCL)   | _             | S  |

| 209 | SDL/SCL rise time                         |            | —               | 1/(10 * fSCL) | s  |

| 210 | SDL/SCL fall time                         |            | —               | 1/(33 * fSCL) | S  |

| 211 | Stop condition setup time                 |            | 1/2(2.2 * fSCL) | S             |    |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) × pre\_scaler × 2). The ratio SYNCCLK/(BRGCLK / pre\_scaler) must be greater than or equal to 4/1.

#### Mechanical Data and Ordering Information

| Package Type                                                                                      | Freq. (MHz) /<br>Temp. (Tj) | Package            | Order Number                                                                                                                                                         |  |  |  |

|---------------------------------------------------------------------------------------------------|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Ball grid array <i>(continued)</i><br>ZP suffix—leaded<br>ZQ suffix—leaded<br>VR suffix—lead-free | 80<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ80D4<br>MPC860DEZQ80D4<br>MPC860DTZQ80D4<br>MPC860ENZQ80D4<br>MPC860SRZQ80D4<br>MPC860TZQ80D4<br>MPC860DPZQ80D4<br>MPC860PZQ80D4                            |  |  |  |

|                                                                                                   |                             | Tape and Reel      | MPC860PZQ80D4R2<br>MPC860PVR80D4R2                                                                                                                                   |  |  |  |

|                                                                                                   |                             | VR                 | MPC855TVR80D4<br>MPC860DEVR80D4<br>MPC860DPVR80D4<br>MPC860ENVR80D4<br>MPC860PVR80D4<br>MPC860SRVR80D4<br>MPC860SRVR80D4<br>MPC860TVR80D4                            |  |  |  |

| Ball grid array (CZP suffix)<br>CZP suffix—leaded<br>CZQ suffix—leaded<br>CVR suffix—lead-free    | 50<br>–40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ50D4<br>MPC855TCVR50D4<br>MPC860DECZQ50D4<br>MPC860DTCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860SRCZQ50D4<br>MPC860DPCZQ50D4<br>MPC860PCZQ50D4 |  |  |  |

|                                                                                                   |                             | Tape and Reel      | MPC855TCZQ50D4R2<br>MC860ENCVR50D4R2                                                                                                                                 |  |  |  |

|                                                                                                   |                             | CVR                | MPC860DECVR50D4<br>MPC860DTCVR50D4<br>MPC860ENCVR50D4<br>MPC860PCVR50D4<br>MPC860SRCVR50D4<br>MPC860SRCVR50D4<br>MPC860TCVR50D4                                      |  |  |  |

|                                                                                                   | 66<br>–40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ66D4<br>MPC855TCVR66D4<br>MPC860ENCZQ66D4<br>MPC860SRCZQ66D4<br>MPC860TCZQ66D4<br>MPC860DPCZQ66D4<br>MPC860PCZQ66D4                                        |  |  |  |

|                                                                                                   |                             | CVR                | MPC860DTCVR66D4<br>MPC860ENCVR66D4<br>MPC860PCVR66D4<br>MPC860SRCVR66D4<br>MPC860TCVR66D4                                                                            |  |  |  |

## Table 34. MPC860 Family Package/Frequency Availability (continued)

<sup>1</sup> The ZP package is no longer recommended for use. The ZQ package replaces the ZP package.

## 14.2 Pin Assignments

Figure 76 shows the top view pinout of the PBGA package. For additional information, see the MPC860 PowerQUICC User's Manual, or the MPC855T User's Manual.

| (         |           |           |           |                        |            |            |            |                           |            |                    |            |            |            |            |                        |               |            |              |         |

|-----------|-----------|-----------|-----------|------------------------|------------|------------|------------|---------------------------|------------|--------------------|------------|------------|------------|------------|------------------------|---------------|------------|--------------|---------|

|           | O<br>PD10 | O<br>PD8  | O<br>PD3  |                        | )<br>D0    | O<br>D4    | ()<br>D1   | ()<br>D2                  | )<br>D3    | )<br>D5            |            | )<br>D6    | ()<br>D7   | )<br>D29   | O<br>DP2               |               |            |              | w       |

| O<br>PD14 | O<br>PD13 | O<br>PD9  | O<br>PD6  | ⊖<br>M_Tx_I            |            | O<br>D13   | ()<br>D27  | 〇<br>D10                  | )<br>D14   | )<br>D18           | )<br>D20   | 0<br>D24   | ()<br>D28  | O<br>DP1   | O<br>DP3               |               | )<br>N/C \ |              | v<br>1  |

| 0<br>PA0  | O<br>PB14 | O<br>PD15 | O<br>PD4  | O<br>PD5               |            | ()<br>D8   | ()<br>D23  | ()<br>D11                 | 〇<br>D16   | ()<br>D19          | ()<br>D21  | 0<br>D26   | )<br>D30   | O<br>IPA5  | )<br>IPA4              | O<br>IPA2     | ○<br>N/C   |              | U       |

| O<br>PA1  | O<br>PC5  | O<br>PC4  | O<br>PD11 | O<br>PD7               |            | 0<br>1 D12 | 0<br>D17   | O<br>D9                   | )<br>D15   | 0<br>D22           | 0<br>D25   | O<br>D31   | O<br>IPA6  |            | )<br>IPA1              | O<br>IPA7     | ⊖<br>xfc   |              | т       |

| <br>₽C6   | 0<br>PA2  | O<br>PB15 | O<br>PD12 | $\left( \circ \right)$ |            | 0          | 0          | $\bigcirc$                | $\bigcirc$ | 0                  | 0          | $\bigcirc$ | 0          |            |                        |               |            |              | R<br>VR |

| O<br>PA4  | О<br>РВ17 | O<br>PA3  |           | 0                      |            | O<br>GND   | 0          | $\bigcirc$                | $\bigcirc$ | 0                  | $\bigcirc$ | $\bigcirc$ |            | $\circ$    |                        |               |            | C<br>ET XTAL | Р       |

| O<br>PB19 | O<br>PA5  | O<br>PB18 | 〇<br>PB16 | 0                      | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        |               |            |              | Ν       |

| 0<br>PA7  | 0<br>PC8  | 0<br>PA6  | O<br>PC7  | 0                      | $\circ$    | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        | BADDR28       |            | O<br>R29 VDD | M<br>L  |

| O<br>PB22 | O<br>PC9  | 0<br>PA8  | О<br>РВ20 | 0                      | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | 0<br>0P0               | $\bigcirc$ AS | O<br>OP1   |              | L       |

| O<br>PC10 | 0<br>PA9  | O<br>PB23 | O<br>PB21 | 0                      | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                |            | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        | 0<br>130 IPB6 |            |              | к       |

| O<br>PC11 | O<br>PB24 | 〇<br>PA10 | O<br>PB25 | 0                      | $\circ$    | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | O<br>IPB5              | O<br>IPB1     |            | O            | J       |

|           |           |           | О<br>тск  | 0                      | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | O<br>M_COI             |               |            |              | н       |

|           | O<br>TMS  | O<br>TDO  | O<br>PA11 | 0                      | 0          | )<br>GND   | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | O<br>GND   | 0          |                        |               | O<br>IPB4  | O<br>IPB3    | G       |

| O<br>PB26 | O<br>PC12 | 〇<br>PA12 |           | 0                      |            |            | 0          | 0                         | 0          | 0                  | 0          | 0          |            |            |                        | ⊖<br>⊤s       |            |              | F       |

| O<br>PB27 | O<br>PC13 | 〇<br>PA13 | O<br>PB29 | $\bigcirc$             | 0          | 0          | 0          | 0                         | 0          | 0                  | 0          | 0          | 0          | 0          | $\frac{\bigcirc}{CS3}$ |               |            |              | Е       |

| O<br>PB28 | O<br>PC14 | O<br>PA14 | O<br>PC15 | ()<br>A8               | O<br>N/C   | O<br>N/C   | ()<br>A15  | 〇<br>A19                  | ()<br>A25  | ()<br>A18          |            |            | O<br>N/C   |            | $\frac{\bigcirc}{CS2}$ |               |            |              | D       |

| O<br>PB30 | O<br>PA15 | O<br>PB31 | ()<br>A3  | ()<br>A9               | ()<br>A12  | 〇<br>A16   | ()<br>A20  | )<br>A24                  | )<br>A26   |                    |            |            |            |            |                        |               |            |              | с       |

| ()<br>A0  | ()<br>A1  | ()<br>A4  | 0<br>A6   | )<br>A10               | 〇<br>A13   | ()<br>A17  | 0<br>A21   | ()<br>A23                 | )<br>A22   |                    | $\bigcirc$ |            |            |            | $\frac{\bigcirc}{CS5}$ |               |            |              | в       |

|           | 0<br>A2   | 0<br>A5   | 0<br>A7   | 0<br>A11               | 0<br>A14   | 0<br>A27   | 0<br>A29   | )<br>()<br>()<br>()<br>() | 0<br>A28   | 0.120<br>()<br>A31 | VDDL       |            |            |            |                        |               |            | •            | А       |

| 19        | 18        | 17        | 16        | 15                     | 14         | 13         | 12         | 11                        | 10         | 9                  | 8          | 7          | 6          | 5          | 4                      | 3             | 2          | 1            | ١       |

**NOTE:** This is the top view of the device.

Figure 76. Pinout of the PBGA Package