#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| 2 0 0 0 0 0                     |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Active                                                      |

| Core Processor                  | MPC8xx                                                      |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 80MHz                                                       |

| Co-Processors/DSP               | Communications; CPM                                         |

| RAM Controllers                 | DRAM                                                        |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10Mbps (4)                                                  |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 3.3V                                                        |

| Operating Temperature           | 0°C ~ 95°C (TA)                                             |

| Security Features               | -                                                           |

| Package / Case                  | 357-BBGA                                                    |

| Supplier Device Package         | 357-PBGA (25x25)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc860envr80d4 |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC860. Table 2 provides the maximum ratings.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

(GND = 0 V)

#### Table 2. Maximum Tolerated Ratings

| Rating                              | Symbol              | Value                         | Unit |

|-------------------------------------|---------------------|-------------------------------|------|

| Supply voltage <sup>1</sup>         | V <sub>DDH</sub>    | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDL</sub>    | -0.3 to 4.0                   | V    |

|                                     | KAPWR               | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDSYN</sub>  | -0.3 to 4.0                   | V    |

| Input voltage <sup>2</sup>          | V <sub>in</sub>     | GND – 0.3 to V <sub>DDH</sub> | V    |

| Temperature <sup>3</sup> (standard) | T <sub>A(min)</sub> | 0                             | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Temperature <sup>3</sup> (extended) | T <sub>A(min)</sub> | -40                           | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Storage temperature range           | T <sub>stg</sub>    | –55 to 150                    | °C   |

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC860 is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>i</sub>.

#### Table 4 shows the thermal characteristics for the MPC860.

#### Table 4. MPC860 Thermal Resistance Data

| Rating                           | Env                  | vironment               | Symbol              | ZP<br>MPC860P | ZQ / VR<br>MPC860P | Unit |

|----------------------------------|----------------------|-------------------------|---------------------|---------------|--------------------|------|

| Mold Compound Thicknes           | 0.85                 | 1.15                    | mm                  |               |                    |      |

| Junction-to-ambient <sup>1</sup> | Natural convection   | Single-layer board (1s) | $R_{\theta JA}^2$   | 34            | 34                 | °C/W |

|                                  |                      | Four-layer board (2s2p) | $R_{\thetaJMA}{}^3$ | 22            | 22                 |      |

|                                  | Airflow (200 ft/min) | Single-layer board (1s) | $R_{\thetaJMA}{}^3$ | 27            | 27                 |      |

|                                  |                      | Four-layer board (2s2p) | $R_{\thetaJMA}{}^3$ | 18            | 18                 |      |

| Junction-to-board <sup>4</sup>   |                      |                         | $R_{\theta J B}$    | 14            | 13                 |      |

| Junction-to-case <sup>5</sup>    |                      |                         | $R_{	ext{	heta}JC}$ | 6             | 8                  |      |

| Junction-to-package top 6        | Natural convection   |                         | $\Psi_{JT}$         | 2             | 2                  |      |

<sup>1</sup> Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>4</sup> Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated value from the junction to the exposed pad without contact resistance.

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

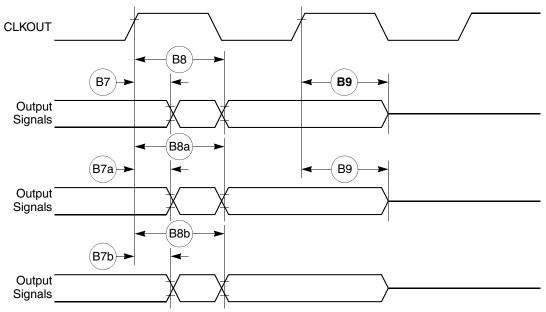

Table 7 provides the bus operation timing for the MPC860 at 33, 40, 50, and 66 MHz.

The maximum bus speed supported by the MPC860 is 66 MHz. Higher-speed parts must be operated in half-speed bus mode (for example, an MPC860 used at 80 MHz must be configured for a 40-MHz bus).

The timing for the MPC860 bus shown assumes a 50-pF load for maximum delays and a 0-pF load for minimum delays.

| Num              | Characteristic                                                                            | 33    | MHz   | 40 MHz |       | 50 I  | MHz   | 66 MHz |       | 11   |

|------------------|-------------------------------------------------------------------------------------------|-------|-------|--------|-------|-------|-------|--------|-------|------|

| Num              | Characteristic                                                                            | Min   | Max   | Min    | Max   | Min   | Max   | Min    | Max   | Unit |

| B1               | CLKOUT period                                                                             | 30.30 | 30.30 | 25.00  | 30.30 | 20.00 | 30.30 | 15.15  | 30.30 | ns   |

| B1a              | EXTCLK to CLKOUT phase skew<br>(EXTCLK > 15 MHz and MF <= 2)                              | -0.90 | 0.90  | -0.90  | 0.90  | -0.90 | 0.90  | -0.90  | 0.90  | ns   |

| B1b              | EXTCLK to CLKOUT phase skew<br>(EXTCLK > 10 MHz and MF < 10)                              | -2.30 | 2.30  | -2.30  | 2.30  | -2.30 | 2.30  | -2.30  | 2.30  | ns   |

| B1c              | CLKOUT phase jitter (EXTCLK > 15 MHz and MF <= $2$ ) <sup>1</sup>                         | -0.60 | 0.60  | -0.60  | 0.60  | -0.60 | 0.60  | -0.60  | 0.60  | ns   |

| B1d              | CLKOUT phase jitter <sup>1</sup>                                                          | -2.00 | 2.00  | -2.00  | 2.00  | -2.00 | 2.00  | -2.00  | 2.00  | ns   |

| B1e              | CLKOUT frequency jitter (MF < 10) <sup>1</sup>                                            | —     | 0.50  | —      | 0.50  | _     | 0.50  | —      | 0.50  | %    |

| B1f              | CLKOUT frequency jitter (10 < MF < 500) <sup>1</sup>                                      | —     | 2.00  | —      | 2.00  | _     | 2.00  | —      | 2.00  | %    |

| B1g              | CLKOUT frequency jitter (MF > 500) <sup>1</sup>                                           | —     | 3.00  | —      | 3.00  | _     | 3.00  | —      | 3.00  | %    |

| B1h              | Frequency jitter on EXTCLK <sup>2</sup>                                                   | _     | 0.50  |        | 0.50  |       | 0.50  |        | 0.50  | %    |

| B2               | CLKOUT pulse width low                                                                    | 12.12 | —     | 10.00  | —     | 8.00  | —     | 6.06   | _     | ns   |

| B3               | CLKOUT width high                                                                         | 12.12 | —     | 10.00  | _     | 8.00  | —     | 6.06   | _     | ns   |

| B4               | CLKOUT rise time <sup>3</sup>                                                             | _     | 4.00  |        | 4.00  |       | 4.00  |        | 4.00  | ns   |

| B5 <sup>33</sup> | CLKOUT fall time <sup>3</sup>                                                             | —     | 4.00  | —      | 4.00  | _     | 4.00  | —      | 4.00  | ns   |

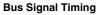

| B7               | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3) invalid                | 7.58  | —     | 6.25   | —     | 5.00  | —     | 3.80   | —     | ns   |

| B7a              | CLKOUT to TSIZ(0:1), REG, RSV, AT(0:3), BDIP, PTR invalid                                 | 7.58  | —     | 6.25   | —     | 5.00  | —     | 3.80   | —     | ns   |

| B7b              | CLKOUT to BR, BG, FRZ, VFLS(0:1),<br>VF(0:2) IWP(0:2), LWP(0:1), STS invalid <sup>4</sup> | 7.58  | —     | 6.25   | —     | 5.00  | —     | 3.80   | —     | ns   |

| B8               | CLKOUT to A(0:31), BADDR(28:30)<br>RD/WR, BURST, D(0:31), DP(0:3) valid                   | 7.58  | 14.33 | 6.25   | 13.00 | 5.00  | 11.75 | 3.80   | 10.04 | ns   |

| B8a              | CLKOUT to TSIZ(0:1), REG, RSV, AT(0:3)<br>BDIP, PTR valid                                 | 7.58  | 14.33 | 6.25   | 13.00 | 5.00  | 11.75 | 3.80   | 10.04 | ns   |

| B8b              | CLKOUT to BR, BG, VFLS(0:1), VF(0:2),<br>IWP(0:2), FRZ, LWP(0:1), STS valid <sup>4</sup>  | 7.58  | 14.33 | 6.25   | 13.00 | 5.00  | 11.75 | 3.80   | 10.04 | ns   |

Table 7. Bus Operation Timings

|      | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                      | 33 MHz 40 M |      | MHz 50 MHz |      |       | 66 MHz |       | 11   |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|------------|------|-------|--------|-------|------|------|

| Num  | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                      | Min         | Max  | Min        | Max  | Min   | Max    | Min   | Max  | Unit |

| B29d | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>EBDF = 0                                                                                                                                                                                                                                                                                                       | 43.45       |      | 35.5       |      | 28.00 |        | 20.73 |      | ns   |

| B29e | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0                                                                                                                                                                                                                                                                              | 43.45       | —    | 35.5       | _    | 28.00 |        | 29.73 | _    | ns   |

| B29f | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>EBDF = 1                                                                                                                                                                                                                                                                                                       | 8.86        |      | 6.88       |      | 5.00  |        | 3.18  |      | ns   |

| B29g | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                                                                                                                                                                                                              | 8.86        |      | 6.88       |      | 5.00  |        | 3.18  |      | ns   |

| B29h | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>EBDF = 1                                                                                                                                                                                                                                                                                                       | 38.67       |      | 31.38      |      | 24.50 |        | 17.83 |      | ns   |

| B29i | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                                                                                                                                                                                                              | 38.67       |      | 31.38      |      | 24.50 |        | 17.83 |      | ns   |

| B30  | $\overline{CS}$ , $\overline{WE}$ (0:3) negated to A(0:31),<br>BADDR(28:30) invalid GPCM write access <sup>8</sup>                                                                                                                                                                                                                                                                                                  | 5.58        | —    | 4.25       | —    | 3.00  | —      | 1.79  | —    | ns   |

| B30a | $\overline{\text{WE}}(0:3)$ negated to A(0:31), BADDR(28:30)<br>invalid GPCM, write access, TRLX = 0,<br>CSNT = 1, $\overline{\text{CS}}$ negated to A(0:31) invalid<br>GPCM write access, TRLX = 0, CSNT = 1<br>ACS = 10, or ACS = 11, EBDF = 0                                                                                                                                                                    | 13.15       | _    | 10.50      | _    | 8.00  | _      | 5.58  | _    | ns   |

| B30b | $\label{eq:weighted} \hline \hline WE(0:3) \ negated to \ A(0:31), \ invalid \ GPCM \\ BADDR(28:30) \ invalid \ GPCM \ write \ access, \\ TRLX = 1, \ CSNT = 1. \ \overline{CS} \ negated to \\ A(0:31), \ Invalid \ GPCM, \ write \ access, \\ TRLX = 1, \ CSNT = 1, \ ACS = 10, \ or \\ ACS = 11, \ EBDF = 0 \\ \hline \hline \hline \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                             | 43.45       | _    | 35.50      | _    | 28.00 |        | 20.73 | _    | ns   |

| B30c | $\label{eq:weighted_states} \begin{array}{ c c c c } \hline WE(0:3) \mbox{ negated to } A(0:31), \mbox{ BADDR}(28:30) \\ \hline invalid \mbox{ GPCM write access, TRLX = 0, } \\ \hline CSNT = 1. \end{tabular} \begin{array}{ c c c } \hline CS \mbox{ negated to } A(0:31) \mbox{ invalid } \\ \hline GPCM \mbox{ write access, TRLX = 0, } CSNT = 1, \\ \hline ACS = 10, \mbox{ ACS = 11, EBDF = 1} \end{array}$ | 8.36        | _    | 6.38       | _    | 4.50  | _      | 2.68  | _    | ns   |

| B30d | $\overline{WE}(0:3)$ negated to A(0:31), BADDR(28:30)<br>invalid GPCM write access, TRLX = 1,<br>CSNT =1. $\overline{CS}$ negated to A(0:31) invalid<br>GPCM write access TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                                                                                                                    | 38.67       | _    | 31.38      | _    | 24.50 | _      | 17.83 | _    | ns   |

| B31  | CLKOUT falling edge to $\overline{CS}$ valid—as requested by control bit CST4 in the corresponding word in UPM                                                                                                                                                                                                                                                                                                      | 1.50        | 6.00 | 1.50       | 6.00 | 1.50  | 6.00   | 1.50  | 6.00 | ns   |

## Table 7. Bus Operation Timings (continued)

| NI   | Characteristic                                                                                                                       | 33    | MHz | 40 MHz |     | 50 MHz |     | 66 MHz |     | Unit |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------|-----|--------|-----|--------|-----|------|

| Num  | Characteristic                                                                                                                       | Min   | Мах | Min    | Мах | Min    | Max | Min    | Мах | Unit |

| B35  | A(0:31), BADDR(28:30) to $\overline{CS}$ valid—as<br>requested by control bit BST4 in the<br>corresponding word in UPM               | 5.58  |     | 4.25   |     | 3.00   | _   | 1.79   |     | ns   |

| B35a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{BS}}$ valid—as requested by control bit BST1 in the corresponding word in UPM | 13.15 |     | 10.50  | —   | 8.00   | _   | 5.58   |     | ns   |

| B35b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{BS}}$ valid—as requested by control bit BST2 in the corresponding word in UPM | 20.73 |     | 16.75  | —   | 13.00  | _   | 9.36   |     | ns   |

| B36  | A(0:31), BADDR(28:30), and D(0:31) to<br>GPL valid—as requested by control bit GxT4<br>in the corresponding word in UPM              | 5.58  |     | 4.25   |     | 3.00   | _   | 1.79   |     | ns   |

| B37  | UPWAIT valid to CLKOUT falling edge9                                                                                                 | 6.00  |     | 6.00   |     | 6.00   | _   | 6.00   |     | ns   |

| B38  | CLKOUT falling edge to UPWAIT valid <sup>9</sup>                                                                                     | 1.00  | _   | 1.00   | _   | 1.00   |     | 1.00   |     | ns   |

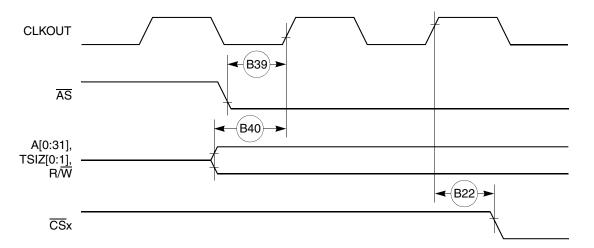

| B39  | AS valid to CLKOUT rising edge <sup>10</sup>                                                                                         | 7.00  |     | 7.00   |     | 7.00   | _   | 7.00   |     | ns   |

| B40  | A(0:31), TSIZ(0:1), RD/WR, BURST, valid to CLKOUT rising edge                                                                        | 7.00  |     | 7.00   | _   | 7.00   |     | 7.00   | —   | ns   |

| B41  | $\overline{\text{TS}}$ valid to CLKOUT rising edge (setup time)                                                                      | 7.00  |     | 7.00   |     | 7.00   | _   | 7.00   |     | ns   |

| B42  | CLKOUT rising edge to $\overline{TS}$ valid (hold time)                                                                              | 2.00  | _   | 2.00   | _   | 2.00   | _   | 2.00   | _   | ns   |

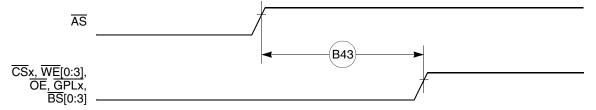

| B43  | AS negation to memory controller signals negation                                                                                    | _     | TBD | _      | TBD | —      | TBD | _      | TBD | ns   |

| Table 7 | Bus O | neration | Timinas | (continued) |

|---------|-------|----------|---------|-------------|

|         | Du3 0 | peration | rinnigs | (continucu) |

<sup>1</sup> Phase and frequency jitter performance results are only valid if the input jitter is less than the prescribed value.

<sup>2</sup> If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time) then the maximum allowed jitter on EXTAL can be up to 2%.

<sup>3</sup> The timings specified in B4 and B5 are based on full strength clock.

<sup>4</sup> The timing for BR output is relevant when the MPC860 is selected to work with external bus arbiter. The timing for BG output is relevant when the MPC860 is selected to work with internal bus arbiter.

<sup>5</sup> The timing required for BR input is relevant when the MPC860 is selected to work with internal bus arbiter. The timing for BG input is relevant when the MPC860 is selected to work with external bus arbiter.

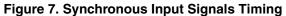

<sup>6</sup> The D(0:31) and DP(0:3) input timings B18 and B19 refer to the rising edge of the CLKOUT in which the TA input signal is asserted.

<sup>7</sup> The D(0:31) and DP(0:3) input timings B20 and B21 refer to the falling edge of the CLKOUT. This timing is valid only for read accesses controlled by chip-selects under control of the UPM in the memory controller, for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

<sup>8</sup> The timing B30 refers to  $\overline{CS}$  when ACS = 00 and to  $\overline{WE}(0:3)$  when CSNT = 0.

<sup>9</sup> The signal UPWAIT is considered asynchronous to the CLKOUT and synchronized internally. The timings specified in B37 and B38 are specified to enable the freeze of the UPM output signals as described in Figure 18.

<sup>10</sup> The AS signal is considered asynchronous to the CLKOUT. The timing B39 is specified in order to allow the behavior specified in Figure 21.

Figure 5 provides the timing for the synchronous output signals.

Figure 5. Synchronous Output Signals Timing

Figure 6 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 6. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

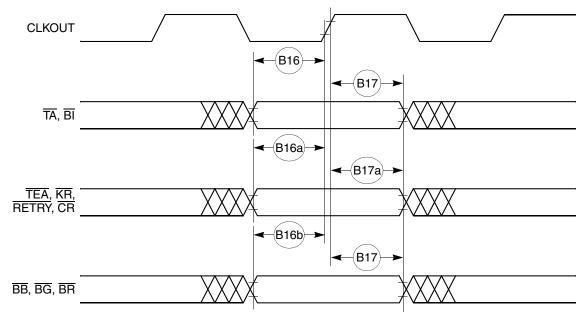

Figure 7 provides the timing for the synchronous input signals.

Figure 8 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 8. Input Data Timing in Normal Case

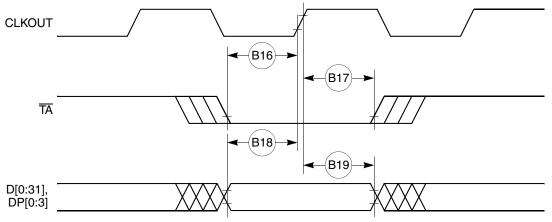

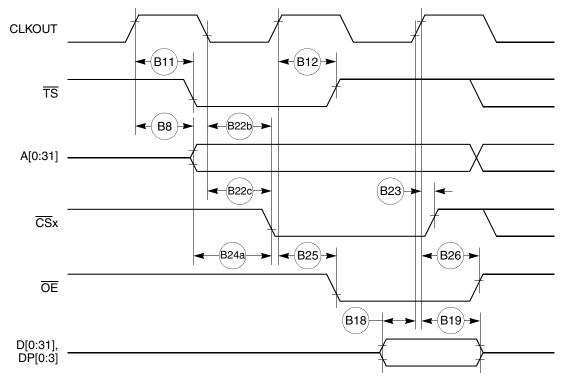

Figure 12. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 11)

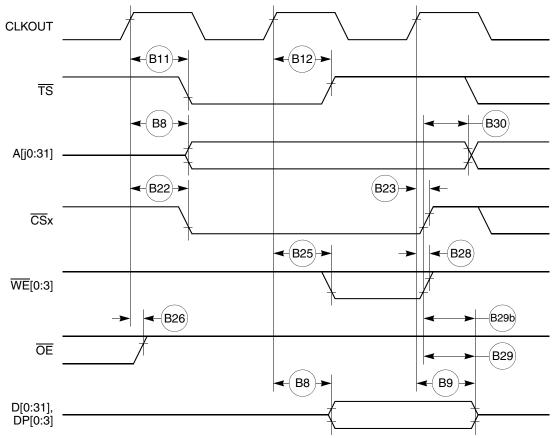

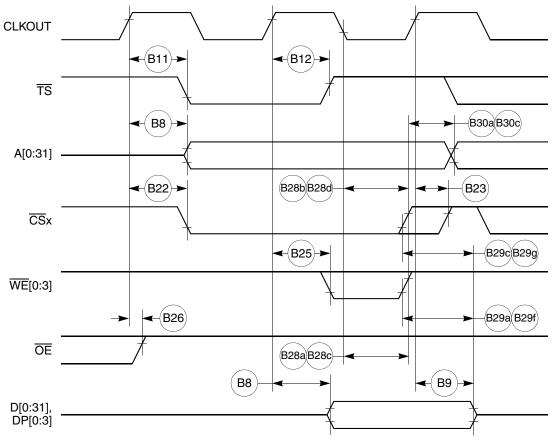

Figure 14 through Figure 16 provide the timing for the external bus write controlled by various GPCM factors.

Figure 14. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 0)

Figure 15. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

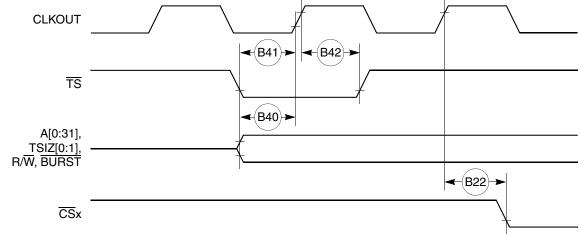

Figure 20 provides the timing for the synchronous external master access controlled by the GPCM.

Figure 20. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

Figure 21 provides the timing for the asynchronous external master memory access controlled by the GPCM.

Figure 22 provides the timing for the asynchronous external master control signals negation.

Figure 22. Asynchronous External Master—Control Signals Negation Timing

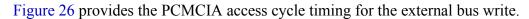

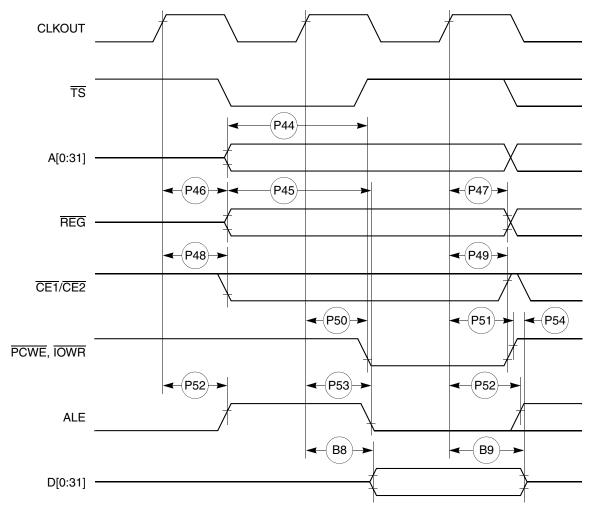

## Table 9 shows the PCMCIA timing for the MPC860.

Table 9. PCMCIA Timing

| Num | Characteristic                                                              | 33    | MHz   | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|-----|-----------------------------------------------------------------------------|-------|-------|--------|-------|--------|-------|--------|-------|------|

| Num | Characteristic                                                              | Min   | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| P44 | A(0:31), REG valid to PCMCIA Strobe asserted <sup>1</sup>                   | 20.73 | —     | 16.75  | —     | 13.00  | —     | 9.36   | —     | ns   |

| P45 | A(0:31), $\overline{\text{REG}}$ valid to ALE negation <sup>1</sup>         | 28.30 | —     | 23.00  | —     | 18.00  | —     | 13.15  | —     | ns   |

| P46 | CLKOUT to REG valid                                                         | 7.58  | 15.58 | 6.25   | 14.25 | 5.00   | 13.00 | 3.79   | 11.84 | ns   |

| P47 | CLKOUT to REG invalid                                                       | 8.58  | —     | 7.25   | —     | 6.00   | —     | 4.84   | —     | ns   |

| P48 | CLKOUT to CE1, CE2 asserted                                                 | 7.58  | 15.58 | 6.25   | 14.25 | 5.00   | 13.00 | 3.79   | 11.84 | ns   |

| P49 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ negated                       | 7.58  | 15.58 | 6.25   | 14.25 | 5.00   | 13.00 | 3.79   | 11.84 | ns   |

| P50 | CLKOUT to PCOE, IORD, PCWE, IOWR assert time                                | —     | 11.00 |        | 11.00 | _      | 11.00 | —      | 11.00 | ns   |

| P51 | CLKOUT to PCOE, IORD, PCWE, IOWR negate time                                | 2.00  | 11.00 | 2.00   | 11.00 | 2.00   | 11.00 | 2.00   | 11.00 | ns   |

| P52 | CLKOUT to ALE assert time                                                   | 7.58  | 15.58 | 6.25   | 14.25 | 5.00   | 13.00 | 3.79   | 10.04 | ns   |

| P53 | CLKOUT to ALE negate time                                                   | —     | 15.58 |        | 14.25 |        | 13.00 | —      | 11.84 | ns   |

| P54 | PCWE, IOWR negated to D(0:31) invalid <sup>1</sup>                          | 5.58  | —     | 4.25   | —     | 3.00   | —     | 1.79   | —     | ns   |

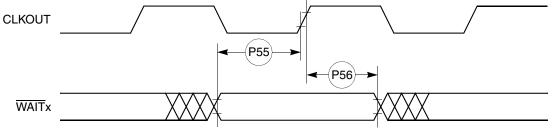

| P55 | ${\text{WAITA}} \text{ and } {\text{WAITB}} \text{ valid to CLKOUT rising}$ | 8.00  | —     | 8.00   | —     | 8.00   | —     | 8.00   | —     | ns   |

| P56 | CLKOUT rising edge to WAITA and WAITB invalid <sup>1</sup>                  | 2.00  | _     | 2.00   | _     | 2.00   | _     | 2.00   | _     | ns   |

<sup>1</sup> PSST = 1. Otherwise add PSST times cycle time.

PSHT = 0. Otherwise add PSHT times cycle time.

These synchronous timings define when the WAITx signals are detected in order to freeze (or relieve) the PCMCIA current cycle. The WAITx assertion will be effective only if it is detected 2 cycles before the PSL timer expiration. See Chapter 16, "PCMCIA Interface," in the *MPC860 PowerQUICCTM Family User's Manual*.

### Figure 26. PCMCIA Access Cycle Timing External Bus Write

Figure 27 provides the PCMCIA  $\overline{WAIT}$  signal detection timing.

Figure 27. PCMCIA WAIT Signal Detection Timing

**CPM Electrical Characteristics**

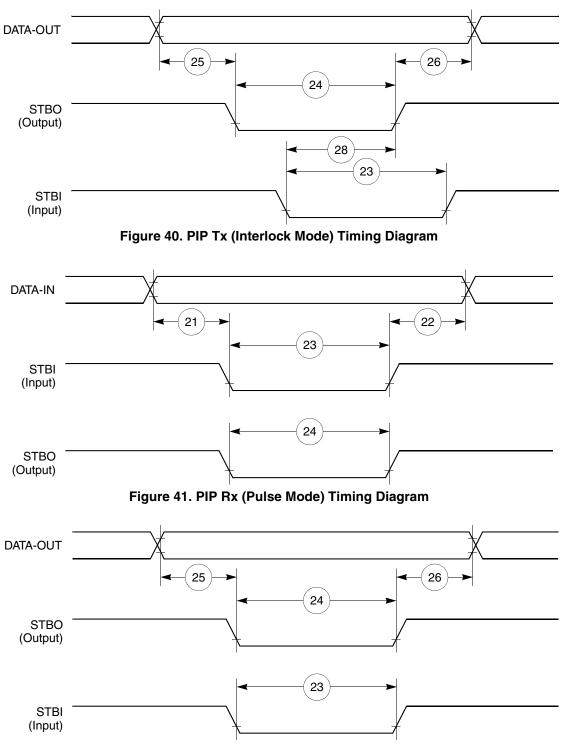

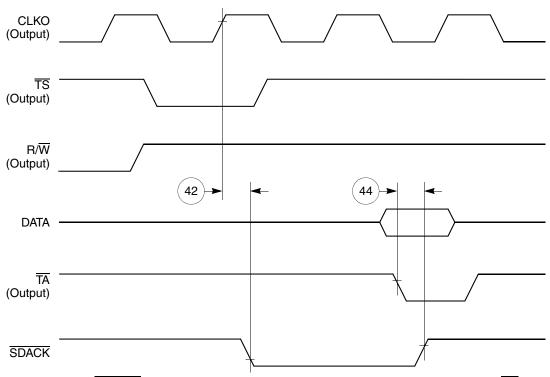

Figure 42. PIP TX (Pulse Mode) Timing Diagram

**CPM Electrical Characteristics**

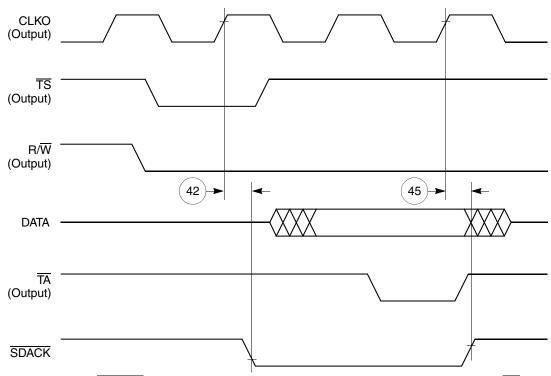

Figure 47. SDACK Timing Diagram—Peripheral Write, Internally-Generated TA

Figure 48. SDACK Timing Diagram—Peripheral Read, Internally-Generated TA

**CPM Electrical Characteristics**

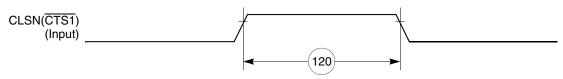

| Num | Characteristic                                 | All Freq | Unit |      |

|-----|------------------------------------------------|----------|------|------|

| Num | Characteristic                                 | Min      | Мах  | Unit |

| 135 | RSTRT active delay (from TCLK1 falling edge)   | 10       | 50   | ns   |

| 136 | RSTRT inactive delay (from TCLK1 falling edge) | 10       | 50   | ns   |

| 137 | REJECT width low                               | 1        | —    | CLK  |

| 138 | CLKO1 low to SDACK asserted <sup>2</sup>       | _        | 20   | ns   |

| 139 | CLKO1 low to SDACK negated <sup>2</sup>        | _        | 20   | ns   |

#### Table 22. Ethernet Timing (continued)

<sup>1</sup> The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 2/1.

<sup>2</sup> SDACK is asserted whenever the SDMA writes the incoming frame DA into memory.

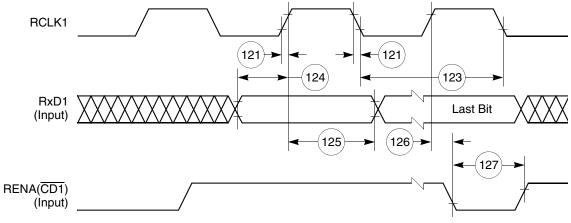

Figure 59. Ethernet Collision Timing Diagram

Figure 60. Ethernet Receive Timing Diagram

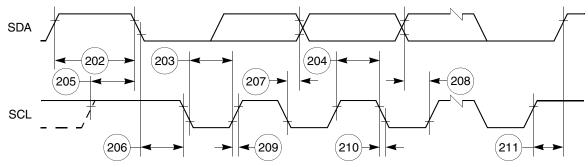

Figure 69 shows the  $I^2C$  bus timing.

Figure 69. I<sup>2</sup>C Bus Timing Diagram

# **12 UTOPIA AC Electrical Specifications**

Table 28 shows the AC electrical specifications for the UTOPIA interface.

| Num | Signal Characteristic                                                  | Direction | Min | Max | Unit |

|-----|------------------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (Internal clock option)                          | Output    | _   | 3.5 | ns   |

|     | Duty cycle                                                             |           | 50  | 50  | %    |

|     | Frequency                                                              |           | —   | 50  | MHz  |

| U1a | UtpClk rise/fall time (external clock option)                          | Input     | _   | 3.5 | ns   |

|     | Duty cycle                                                             |           | 40  | 60  | %    |

|     | Frequency                                                              |           | _   | 50  | MHz  |

| U2  | RxEnb and TxEnb active delay                                           | Output    | 2   | 16  | ns   |

| U3  | UTPB, SOC, Rxclav and Txclav setup time                                | Input     | 8   | —   | ns   |

| U4  | UTPB, SOC, Rxclav and Txclav hold time                                 | Input     | 1   | —   | ns   |

| U5  | UTPB, SOC active delay (and PHREQ and PHSEL active delay in MPHY mode) | Output    | 2   | 16  | ns   |

### Table 28. UTOPIA AC Electrical Specifications

## Table 34 identifies the packages and operating frequencies available for the MPC860.

| Package Type                                                                   | Freq. (MHz) /<br>Temp. (Tj) | Package            | Order Number                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------|-----------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball grid array<br>ZP suffix—leaded<br>ZQ suffix—leaded<br>VR suffix—lead-free | 50<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ50D4<br>MPC860DEZQ50D4<br>MPC860DTZQ50D4<br>MPC860ENZQ50D4<br>MPC860SRZQ50D4<br>MPC860TZQ50D4<br>MPC860DPZQ50D4<br>MPC860PZQ50D4                                                                          |

|                                                                                |                             | Tape and Reel      | MPC855TZQ50D4R2<br>MPC860DEZQ50D4R2<br>MPC860ENZQ50D4R2<br>MPC860SRZQ50D4R2<br>MPC860TZQ50D4R2<br>MPC860TZQ50D4R2<br>MPC860TZQ50D4R2<br>MPC855TVR50D4R2<br>MPC860ENVR50D4R2<br>MPC860SRVR50D4R2<br>MPC860TVR50D4R2 |

|                                                                                |                             | VR                 | MPC855TVR50D4<br>MPC860DEVR50D4<br>MPC860DPVR50D4<br>MPC860DTVR50D4<br>MPC860ENVR50D4<br>MPC860PVR50D4<br>MPC860SRVR50D4<br>MPC860SRVR50D4                                                                         |

|                                                                                | 66<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ66D4<br>MPC860DEZQ66D4<br>MPC860DTZQ66D4<br>MPC860ENZQ66D4<br>MPC860SRZQ66D4<br>MPC860TZQ66D4<br>MPC860DPZQ66D4<br>MPC860PZQ66D4                                                                          |

|                                                                                |                             | Tape and Reel      | MPC860SRZQ66D4R2<br>MPC860PZQ66D4R2                                                                                                                                                                                |

|                                                                                |                             | VR                 | MPC855TVR66D4<br>MPC860DEVR66D4<br>MPC860DPVR66D4<br>MPC860DTVR66D4<br>MPC860ENVR66D4<br>MPC860PVR66D4<br>MPC860SRVR66D4<br>MPC860TVR66D4                                                                          |

## Table 34. MPC860 Family Package/Frequency Availability

#### Mechanical Data and Ordering Information

| Package Type                                                                                                    | Freq. (MHz) /<br>Temp. (Tj) | Package                                                                                                                                                              | Order Number                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Ball grid array <i>(continued)</i><br>ZP suffix—leaded<br>ZQ suffix—leaded<br>VR suffix—lead-free               | 80<br>0° to 95°C            | ZP/ZQ <sup>1</sup>                                                                                                                                                   | MPC855TZQ80D4<br>MPC860DEZQ80D4<br>MPC860DTZQ80D4<br>MPC860ENZQ80D4<br>MPC860SRZQ80D4<br>MPC860TZQ80D4<br>MPC860DPZQ80D4<br>MPC860PZQ80D4 |

|                                                                                                                 |                             | Tape and Reel                                                                                                                                                        | MPC860PZQ80D4R2<br>MPC860PVR80D4R2                                                                                                        |

|                                                                                                                 |                             | VR                                                                                                                                                                   | MPC855TVR80D4<br>MPC860DEVR80D4<br>MPC860DPVR80D4<br>MPC860ENVR80D4<br>MPC860PVR80D4<br>MPC860SRVR80D4<br>MPC860SRVR80D4<br>MPC860TVR80D4 |

| all grid array (CZP suffix) 50 ZP/Z<br>ZP suffix—leaded -40° to 95°C<br>ZQ suffix—lead-free VR suffix—lead-free | ZP/ZQ <sup>1</sup>          | MPC855TCZQ50D4<br>MPC855TCVR50D4<br>MPC860DECZQ50D4<br>MPC860DTCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860SRCZQ50D4<br>MPC860DPCZQ50D4<br>MPC860PCZQ50D4 |                                                                                                                                           |

|                                                                                                                 |                             | Tape and Reel                                                                                                                                                        | MPC855TCZQ50D4R2<br>MC860ENCVR50D4R2                                                                                                      |

|                                                                                                                 |                             | CVR                                                                                                                                                                  | MPC860DECVR50D4<br>MPC860DTCVR50D4<br>MPC860ENCVR50D4<br>MPC860PCVR50D4<br>MPC860SRCVR50D4<br>MPC860SRCVR50D4<br>MPC860TCVR50D4           |

|                                                                                                                 | 66<br>–40° to 95°C          | ZP/ZQ <sup>1</sup>                                                                                                                                                   | MPC855TCZQ66D4<br>MPC855TCVR66D4<br>MPC860ENCZQ66D4<br>MPC860SRCZQ66D4<br>MPC860TCZQ66D4<br>MPC860DPCZQ66D4<br>MPC860PCZQ66D4             |

|                                                                                                                 |                             | CVR                                                                                                                                                                  | MPC860DTCVR66D4<br>MPC860ENCVR66D4<br>MPC860PCVR66D4<br>MPC860SRCVR66D4<br>MPC860TCVR66D4                                                 |

## Table 34. MPC860 Family Package/Frequency Availability (continued)

<sup>1</sup> The ZP package is no longer recommended for use. The ZQ package replaces the ZP package.

## 14.2 Pin Assignments

Figure 76 shows the top view pinout of the PBGA package. For additional information, see the MPC860 PowerQUICC User's Manual, or the MPC855T User's Manual.

| (         |           |           |           |                        |            |            |            |                           |            |            |            |            |            |            |                        |               |             |              |         |

|-----------|-----------|-----------|-----------|------------------------|------------|------------|------------|---------------------------|------------|------------|------------|------------|------------|------------|------------------------|---------------|-------------|--------------|---------|

|           | O<br>PD10 | O<br>PD8  | O<br>PD3  |                        | )<br>D0    | O<br>D4    | ()<br>D1   | ()<br>D2                  | ()<br>D3   | )<br>D5    |            | )<br>D6    | ()<br>D7   | )<br>D29   | O<br>DP2               |               |             |              | w       |

| O<br>PD14 | O<br>PD13 | O<br>PD9  | O<br>PD6  | ⊖<br>M_Tx_             |            | O<br>D13   | ()<br>D27  | 〇<br>D10                  | )<br>D14   | )<br>D18   | )<br>D20   | 0<br>D24   | ()<br>D28  | O<br>DP1   | O<br>DP3               |               | ()<br>N/C \ |              | V       |

| 0<br>PA0  | O<br>PB14 | O<br>PD15 | O<br>PD4  | O<br>PD5               |            | ()<br>D8   | ()<br>D23  | ()<br>D11                 | 〇<br>D16   | )<br>D19   | ()<br>D21  | 0<br>D26   | )<br>D30   | O<br>IPA5  | )<br>IPA4              | O<br>IPA2     | ⊖<br>N/C    |              | U       |

| O<br>PA1  | O<br>PC5  | O<br>PC4  | O<br>PD11 | O<br>PD7               |            | 0<br>1 D12 | 0<br>D17   | O<br>D9                   | )<br>D15   | 0<br>D22   | 0<br>D25   | O<br>D31   | O<br>IPA6  |            | )<br>IPA1              | O<br>IPA7     | ⊖<br>xfc    |              | т       |

| <br>₽C6   | 0<br>PA2  | O<br>PB15 | O<br>PD12 | $\left( \circ \right)$ |            | 0          | 0          | 0                         | 0          | 0          | 0          | $\bigcirc$ | 0          |            |                        |               |             |              | R<br>VR |

| O<br>PA4  | О<br>РВ17 | O<br>PA3  |           | 0                      |            | O<br>GND   | 0          | $\bigcirc$                | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ |            | $\circ$    |                        |               |             | C<br>T XTAL  | Р       |

| O<br>PB19 | O<br>PA5  | O<br>PB18 | 〇<br>PB16 | 0                      | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        |               |             |              | N       |

| 0<br>PA7  | 0<br>PC8  | 0<br>PA6  | O<br>PC7  | 0                      | $\circ$    | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        | BADDR28       | O<br>BADD   | O<br>R29 VDD | M<br>L  |

| O<br>PB22 | O<br>PC9  | 0<br>PA8  | О<br>РВ20 | 0                      | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | 0<br>0P0               |               | O<br>OP1    |              | L       |

| O<br>PC10 | 0<br>PA9  | O<br>PB23 | O<br>PB21 | 0                      | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | O<br>GND   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        | 0<br>130 IPB6 |             |              | к       |

| O<br>PC11 | O<br>PB24 | 〇<br>PA10 | O<br>PB25 | 0                      | $\circ$    | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | O<br>IPB5              | O<br>IPB1     |             | O            | J       |

|           |           |           | О<br>тск  | 0                      | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | O<br>M_COI             |               |             |              | н       |

|           | O<br>TMS  | O<br>TDO  | O<br>PA11 | 0                      | 0          | )<br>GND   | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | O<br>GND   | 0          |                        |               |             | O<br>IPB3    | G       |

| O<br>PB26 | O<br>PC12 | 〇<br>PA12 |           | 0                      |            |            | 0          | 0                         | 0          | 0          | 0          | 0          |            |            |                        | ⊖<br>⊤s       |             |              | F       |

| O<br>PB27 | O<br>PC13 | 〇<br>PA13 | O<br>PB29 | $\bigcirc$             | 0          | 0          | 0          | 0                         | 0          | 0          | 0          | 0          | 0          | 0          | $\frac{\bigcirc}{CS3}$ |               |             |              | Е       |

| O<br>PB28 | O<br>PC14 | O<br>PA14 | O<br>PC15 | ()<br>A8               | O<br>N/C   | O<br>N/C   | ()<br>A15  | 〇<br>A19                  | ()<br>A25  | )<br>A18   |            |            | O<br>N/C   |            | $\frac{\bigcirc}{CS2}$ |               |             |              | D       |

| O<br>PB30 | O<br>PA15 | O<br>PB31 | ()<br>A3  | ()<br>A9               | ()<br>A12  | 〇<br>A16   | ()<br>A20  | ()<br>A24                 | ()<br>A26  |            |            |            |            |            |                        |               |             |              | с       |

| ()<br>A0  | ()<br>A1  | ()<br>A4  | 0<br>A6   | )<br>A10               | 〇<br>A13   | ()<br>A17  | ()<br>A21  | ()<br>A23                 | 0<br>A22   |            | $\bigcirc$ |            |            |            | $\frac{\bigcirc}{CS5}$ |               |             |              | в       |

|           | 0<br>A2   | 0<br>A5   | 0<br>A7   | 0<br>A11               | 0<br>A14   | 0<br>A27   | 0<br>A29   | )<br>()<br>()<br>()<br>() | 0<br>A28   | <br>A31    | VDDL       |            |            |            |                        |               |             |              | А       |

| 19        | 18        | 17        | 16        | 15                     | 14         | 13         | 12         | 11                        | 10         | 9          | 8          | 7          | 6          | 5          | 4                      | 3             | 2           | 1            | ر       |

**NOTE:** This is the top view of the device.

Figure 76. Pinout of the PBGA Package