#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 50MHz                                                                 |

| Co-Processors/DSP               | Communications; CPM                                                   |

| RAM Controllers                 | DRAM                                                                  |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10Mbps (4), 10/100Mbps (1)                                            |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                       |

| Security Features               | -                                                                     |

| Package / Case                  | 357-BBGA                                                              |

| Supplier Device Package         | 357-PBGA (25x25)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc860pvr50d4 |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC)

- Reset controller

- IEEE 1149.1<sup>TM</sup> Std. test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- 23 internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- 10/100 Mbps Ethernet support, fully compliant with the IEEE 802.3u® Standard (not available when using ATM over UTOPIA interface)

- ATM support compliant with ATM forum UNI 4.0 specification

- Cell processing up to 50–70 Mbps at 50-MHz system clock

- Cell multiplexing/demultiplexing

- Support of AAL5 and AAL0 protocols on a per-VC basis. AAL0 support enables OAM and software implementation of other protocols.

- ATM pace control (APC) scheduler, providing direct support for constant bit rate (CBR) and unspecified bit rate (UBR) and providing control mechanisms enabling software support of available bit rate (ABR)

- Physical interface support for UTOPIA (10/100-Mbps is not supported with this interface) and byte-aligned serial (for example, T1/E1/ADSL)

- UTOPIA-mode ATM supports level-1 master with cell-level handshake, multi-PHY (up to four physical layer devices), connection to 25-, 51-, or 155-Mbps framers, and UTOPIA/system clock ratios of 1/2 or 1/3.

- Serial-mode ATM connection supports transmission convergence (TC) function for T1/E1/ADSL lines, cell delineation, cell payload scrambling/descrambling, automatic idle/unassigned cell insertion/stripping, header error control (HEC) generation, checking, and statistics.

- Communications processor module (CPM)

- RISC communications processor (CP)

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

# 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC860. Table 2 provides the maximum ratings.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

(GND = 0 V)

### Table 2. Maximum Tolerated Ratings

| Rating                              | Symbol              | Value                         | Unit |

|-------------------------------------|---------------------|-------------------------------|------|

| Supply voltage <sup>1</sup>         | V <sub>DDH</sub>    | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDL</sub>    | -0.3 to 4.0                   | V    |

|                                     | KAPWR               | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDSYN</sub>  | -0.3 to 4.0                   | V    |

| Input voltage <sup>2</sup>          | V <sub>in</sub>     | GND – 0.3 to V <sub>DDH</sub> | V    |

| Temperature <sup>3</sup> (standard) | T <sub>A(min)</sub> | 0                             | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Temperature <sup>3</sup> (extended) | T <sub>A(min)</sub> | -40                           | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Storage temperature range           | T <sub>stg</sub>    | –55 to 150                    | °C   |

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC860 is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>i</sub>.

**Bus Signal Timing**

|      | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                       | 33 MHz 40 |      | 40 I  | MHz 50 MHz |       |      | 66 MHz |      |      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------|------------|-------|------|--------|------|------|

| Num  |                                                                                                                                                                                                                                                                                                                                                                                                                      | Min       | Max  | Min   | Max        | Min   | Max  | Min    | Max  | Unit |

| B29d | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>EBDF = 0                                                                                                                                                                                                                                                                                                        | 43.45     |      | 35.5  |            | 28.00 |      | 20.73  | _    | ns   |

| B29e | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0                                                                                                                                                                                                                                                                               | 43.45     | —    | 35.5  | _          | 28.00 |      | 29.73  | _    | ns   |

| B29f | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>EBDF = 1                                                                                                                                                                                                                                                                                                        | 8.86      |      | 6.88  |            | 5.00  |      | 3.18   |      | ns   |

| B29g | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                                                                                                                                                                                                               | 8.86      |      | 6.88  |            | 5.00  |      | 3.18   |      | ns   |

| B29h | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>EBDF = 1                                                                                                                                                                                                                                                                                                        | 38.67     |      | 31.38 |            | 24.50 |      | 17.83  |      | ns   |

| B29i | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                                                                                                                                                                                                               | 38.67     |      | 31.38 |            | 24.50 |      | 17.83  |      | ns   |

| B30  | $\overline{CS}$ , $\overline{WE}$ (0:3) negated to A(0:31),<br>BADDR(28:30) invalid GPCM write access <sup>8</sup>                                                                                                                                                                                                                                                                                                   | 5.58      | —    | 4.25  | —          | 3.00  | —    | 1.79   | —    | ns   |

| B30a | $\overline{\text{WE}}(0:3)$ negated to A(0:31), BADDR(28:30)<br>invalid GPCM, write access, TRLX = 0,<br>CSNT = 1, $\overline{\text{CS}}$ negated to A(0:31) invalid<br>GPCM write access, TRLX = 0, CSNT = 1<br>ACS = 10, or ACS = 11, EBDF = 0                                                                                                                                                                     | 13.15     | _    | 10.50 | _          | 8.00  | _    | 5.58   | _    | ns   |

| B30b | $\label{eq:weighted} \hline \hline WE(0:3) \ negated to \ A(0:31), \ invalid \ GPCM \\ BADDR(28:30) \ invalid \ GPCM \ write \ access, \\ TRLX = 1, \ CSNT = 1. \ \overline{CS} \ negated to \\ A(0:31), \ Invalid \ GPCM, \ write \ access, \\ TRLX = 1, \ CSNT = 1, \ ACS = 10, \ or \\ ACS = 11, \ EBDF = 0 \\ \hline \hline \hline \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                              | 43.45     | _    | 35.50 |            | 28.00 |      | 20.73  | _    | ns   |

| B30c | $\label{eq:weighted_states} \begin{array}{ c c c c c } \hline \hline WE(0:3) \mbox{ negated to } A(0:31), \mbox{ BADDR}(28:30) \\ \hline \mbox{ invalid GPCM write access, TRLX = 0, } \\ \hline CSNT = 1. \end{tabular} \begin{array}{ c c c c } \hline CS \mbox{ negated to } A(0:31) \mbox{ invalid } \\ \hline GPCM \mbox{ write access, TRLX = 0, } \\ \hline ACS = 10, \mbox{ ACS = 11, EBDF = 1} \end{array}$ | 8.36      | _    | 6.38  | _          | 4.50  | _    | 2.68   | _    | ns   |

| B30d | $\overline{WE}(0:3)$ negated to A(0:31), BADDR(28:30)<br>invalid GPCM write access, TRLX = 1,<br>CSNT =1. $\overline{CS}$ negated to A(0:31) invalid<br>GPCM write access TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                                                                                                                     | 38.67     | _    | 31.38 | _          | 24.50 | _    | 17.83  | _    | ns   |

| B31  | CLKOUT falling edge to $\overline{CS}$ valid—as requested by control bit CST4 in the corresponding word in UPM                                                                                                                                                                                                                                                                                                       | 1.50      | 6.00 | 1.50  | 6.00       | 1.50  | 6.00 | 1.50   | 6.00 | ns   |

# Table 7. Bus Operation Timings (continued)

|      | Objective de la la                                                                                                                    | 33 MHz 40 N |       | MHz 50 MHz |       |       | 66 MHz |      | Unit  |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|------------|-------|-------|--------|------|-------|------|

| Num  | Characteristic                                                                                                                        | Min         | Max   | Min        | Max   | Min   | Max    | Min  | Max   | Unit |

| B31a | CLKOUT falling edge to CS valid—as requested by control bit CST1 in the corresponding word in UPM                                     | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid—as<br>requested by control bit CST2 in the<br>corresponding word in UPM                   | 1.50        | 8.00  | 1.50       | 8.00  | 1.50  | 8.00   | 1.50 | 8.00  | ns   |

| B31c | CLKOUT rising edge to $\overline{CS}$ valid—as requested by control bit CST3 in the corresponding word in UPM                         | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.04 | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$ valid—as<br>requested by control bit CST1 in the<br>corresponding word in UPM, EBDF = 1        | 13.26       | 17.99 | 11.28      | 16.00 | 9.40  | 14.13  | 7.58 | 12.31 | ns   |

| B32  | CLKOUT falling edge to BS valid—as<br>requested by control bit BST4 in the<br>corresponding word in UPM                               | 1.50        | 6.00  | 1.50       | 6.00  | 1.50  | 6.00   | 1.50 | 6.00  | ns   |

| B32a | CLKOUT falling edge to $\overline{\text{BS}}$ valid—as<br>requested by control bit BST1 in the<br>corresponding word in UPM, EBDF = 0 | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B32b | CLKOUT rising edge to BS valid—as<br>requested by control bit BST2 in the<br>corresponding word in UPM                                | 1.50        | 8.00  | 1.50       | 8.00  | 1.50  | 8.00   | 1.50 | 8.00  | ns   |

| B32c | CLKOUT rising edge to BS valid—as<br>requested by control bit BST3 in the<br>corresponding word in UPM                                | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B32d | CLKOUT falling edge to $\overline{BS}$ valid—as<br>requested by control bit BST1 in the<br>corresponding word in UPM, EBDF = 1        | 13.26       | 17.99 | 11.28      | 16.00 | 9.40  | 14.13  | 7.58 | 12.31 | ns   |

| B33  | CLKOUT falling edge to GPL valid—as<br>requested by control bit GxT4 in the<br>corresponding word in UPM                              | 1.50        | 6.00  | 1.50       | 6.00  | 1.50  | 6.00   | 1.50 | 6.00  | ns   |

| B33a | CLKOUT rising edge to GPL valid—as<br>requested by control bit GxT3 in the<br>corresponding word in UPM                               | 7.58        | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80 | 10.54 | ns   |

| B34  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST4 in the corresponding word in UPM         | 5.58        | —     | 4.25       | —     | 3.00  |        | 1.79 | —     | ns   |

| B34a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST1 in the corresponding word in UPM         | 13.15       | —     | 10.50      | —     | 8.00  | —      | 5.58 | —     | ns   |

| B34b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid—as requested by control bit CST2 in the corresponding word in UPM         | 20.73       | _     | 16.75      |       | 13.00 |        | 9.36 |       | ns   |

## Table 7. Bus Operation Timings (continued)

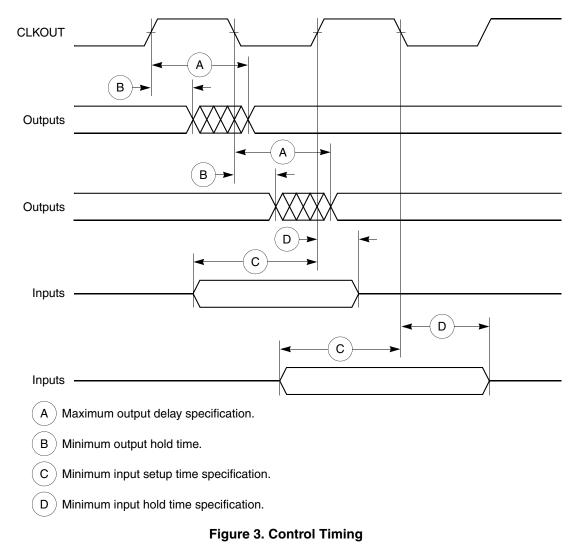

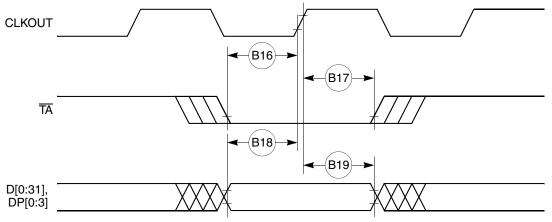

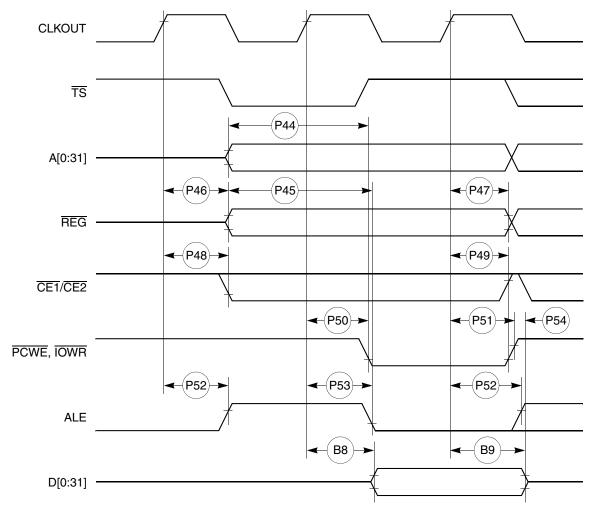

Figure 3 is the control timing diagram.

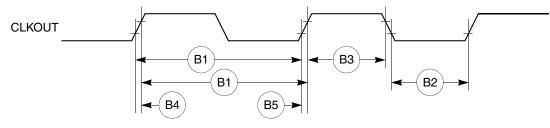

Figure 4 provides the timing for the external clock.

Figure 4. External Clock Timing

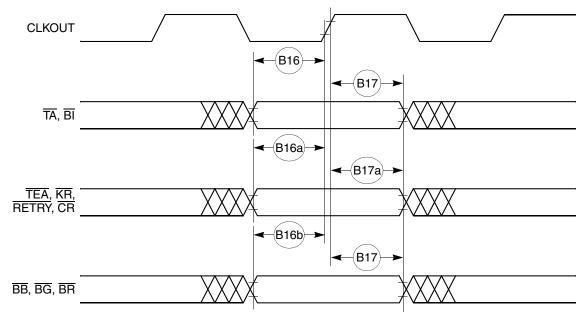

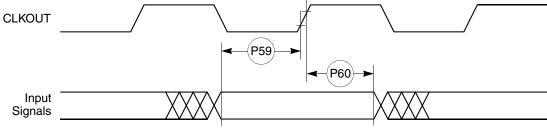

Figure 7 provides the timing for the synchronous input signals.

Figure 8 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 8. Input Data Timing in Normal Case

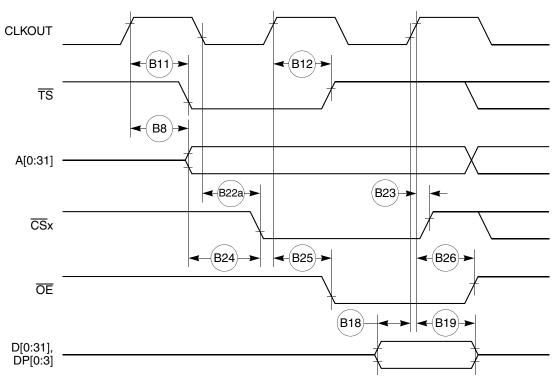

Figure 12. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 11)

**Bus Signal Timing**

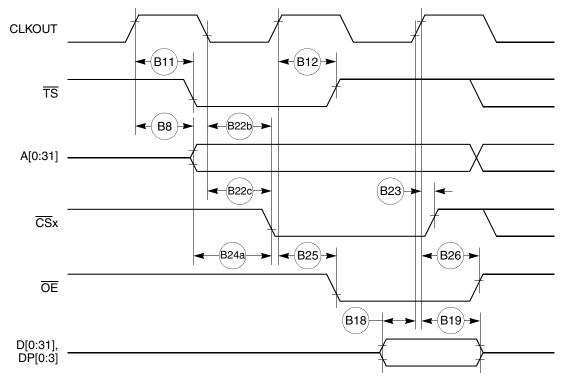

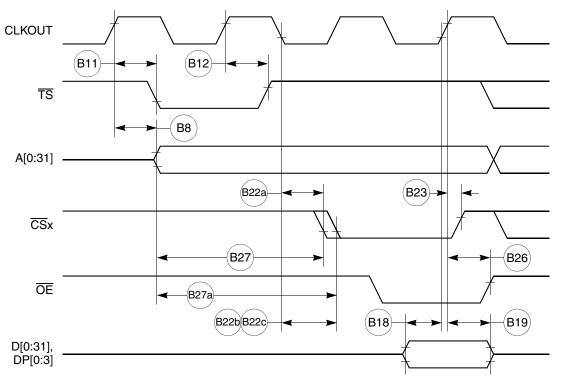

Figure 13. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 10, ACS = 11)

1

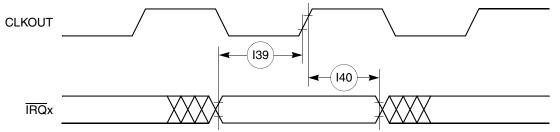

Table 8 provides interrupt timing for the MPC860.

#### Table 8. Interrupt Timing

| Num | Characteristic <sup>1</sup>                   | All Freq                | Unit |      |

|-----|-----------------------------------------------|-------------------------|------|------|

| Num | Characteristic                                | Min                     | Мах  | Unit |

| 139 | IRQx valid to CLKOUT rising edge (setup time) | 6.00                    | —    | ns   |

| 140 | IRQx hold time after CLKOUT                   | 2.00                    | —    | ns   |

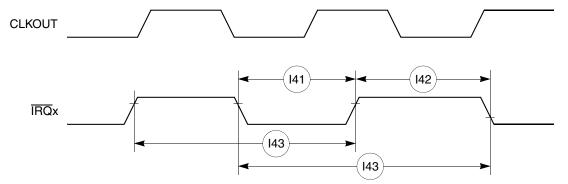

| 141 | IRQx pulse width low                          | 3.00                    | —    | ns   |

| 142 | IRQx pulse width high                         | 3.00                    | —    | ns   |

| 143 | IRQx edge-to-edge time                        | $4 \times T_{CLOCKOUT}$ | —    | —    |

The timings I39 and I40 describe the testing conditions under which the IRQ lines are tested when being defined as level-sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT.

The timings I41, I42, and I43 are specified to allow the correct function of the IRQ lines detection circuitry and have no direct relation with the total system interrupt latency that the MPC860 is able to support.

Figure 23 provides the interrupt detection timing for the external level-sensitive lines.

Figure 23. Interrupt Detection Timing for External Level Sensitive Lines

Figure 24 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 24. Interrupt Detection Timing for External Edge Sensitive Lines

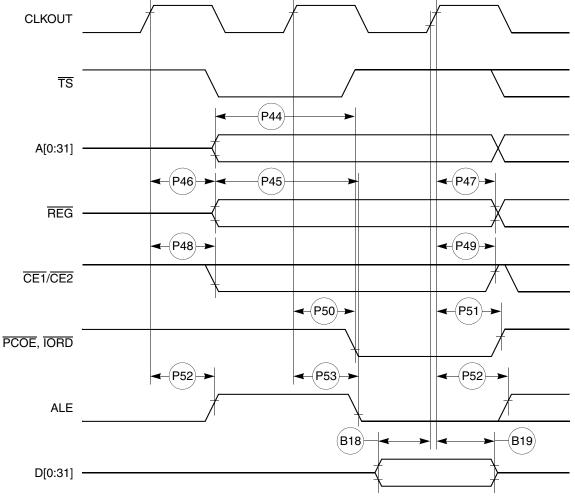

Figure 25 provides the PCMCIA access cycle timing for the external bus read.

Figure 25. PCMCIA Access Cycle Timing External Bus Read

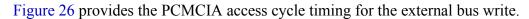

**Bus Signal Timing**

Figure 26. PCMCIA Access Cycle Timing External Bus Write

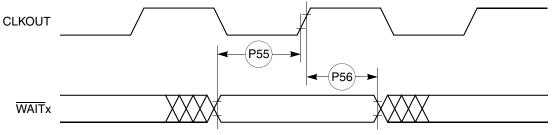

Figure 27 provides the PCMCIA  $\overline{WAIT}$  signal detection timing.

Figure 27. PCMCIA WAIT Signal Detection Timing

Table 10 shows the PCMCIA port timing for the MPC860.

Table 10. PCMCIA Port Timing

| Num | Characteristic                           | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|-----|------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

|     |                                          |        | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

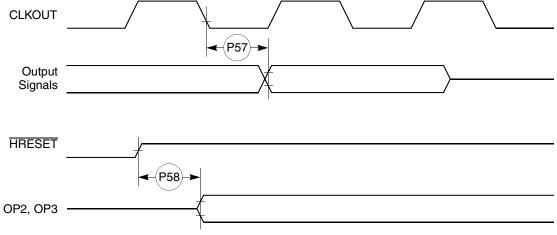

| P57 | CLKOUT to OPx valid                      | —      | 19.00 | —      | 19.00 |        | 19.00 | _      | 19.00 | ns   |

| P58 | HRESET negated to OPx drive <sup>1</sup> | 25.73  | _     | 21.75  | _     | 18.00  | —     | 14.36  | _     | ns   |

| P59 | IP_Xx valid to CLKOUT rising edge        | 5.00   | _     | 5.00   | _     | 5.00   | —     | 5.00   | _     | ns   |

| P60 | CLKOUT rising edge to IP_Xx invalid      | 1.00   |       | 1.00   | —     | 1.00   | —     | 1.00   |       | ns   |

<sup>1</sup> OP2 and OP3 only.

Figure 28 provides the PCMCIA output port timing for the MPC860.

Figure 28. PCMCIA Output Port Timing

Figure 29 provides the PCMCIA output port timing for the MPC860.

Figure 29. PCMCIA Input Port Timing

Bus Signal Timing

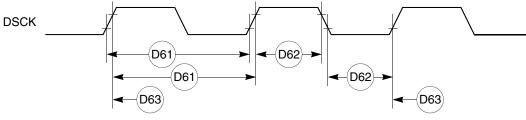

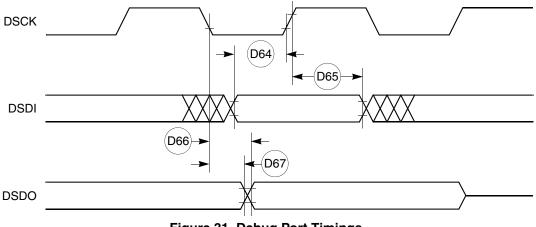

Table 11 shows the debug port timing for the MPC860.

Table 11. Debug Port Timing

| Num | Characteristic              | All Freq                  | Unit  |      |

|-----|-----------------------------|---------------------------|-------|------|

| NUM | Characteristic              | Min                       | Мах   | Unit |

| P61 | DSCK cycle time             | $3 \times T_{CLOCKOUT}$   | _     | —    |

| P62 | DSCK clock pulse width      | $1.25 	imes T_{CLOCKOUT}$ | _     | —    |

| P63 | DSCK rise and fall times    | 0.00                      | 3.00  | ns   |

| P64 | DSDI input data setup time  | 8.00                      | _     | ns   |

| P65 | DSDI data hold time         | 5.00                      | _     | ns   |

| P66 | DSCK low to DSDO data valid | 0.00                      | 15.00 | ns   |

| P67 | DSCK low to DSDO invalid    | 0.00                      | 2.00  | ns   |

Figure 30 provides the input timing for the debug port clock.

Figure 30. Debug Port Clock Input Timing

Figure 31 provides the timing for the debug port.

Figure 31. Debug Port Timings

**CPM Electrical Characteristics**

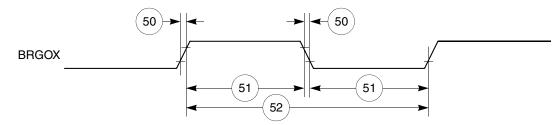

# 11.4 Baud Rate Generator AC Electrical Specifications

Table 17 provides the baud rate generator timings as shown in Figure 49.

### Table 17. Baud Rate Generator Timing

| Num | Characteristic          | Min Max | Unit    |      |

|-----|-------------------------|---------|---------|------|

| Num | Characteristic          |         | Min Max | Unit |

| 50  | BRGO rise and fall time | _       | 10      | ns   |

| 51  | BRGO duty cycle         | 40      | 60      | %    |

| 52  | BRGO cycle              | 40      | _       | ns   |

## Figure 49. Baud Rate Generator Timing Diagram

# **11.5 Timer AC Electrical Specifications**

Table 18 provides the general-purpose timer timings as shown in Figure 50.

### Table 18. Timer Timing

| Num | Characteristic               | All Freq | Unit |      |

|-----|------------------------------|----------|------|------|

| NUM |                              | Min      | Мах  | Unit |

| 61  | TIN/TGATE rise and fall time | 10       |      | ns   |

| 62  | TIN/TGATE low time           | 1        | _    | CLK  |

| 63  | TIN/TGATE high time          | 2        | —    | CLK  |

| 64  | TIN/TGATE cycle time         | 3        | —    | CLK  |

| 65  | CLKO low to TOUT valid       | 3        | 25   | ns   |

Figure 58. HDLC Bus Timing Diagram

# **11.8 Ethernet Electrical Specifications**

Table 22 provides the Ethernet timings as shown in Figure 59 through Figure 63.

| Num | Characteristic                                                  | All Freq | uencies | Unit |

|-----|-----------------------------------------------------------------|----------|---------|------|

| Num | Characteristic                                                  | Min      | Max     | Unit |

| 120 | CLSN width high                                                 | 40       | _       | ns   |

| 121 | RCLK1 rise/fall time                                            | —        | 15      | ns   |

| 122 | RCLK1 width low                                                 | 40       | —       | ns   |

| 123 | RCLK1 clock period <sup>1</sup>                                 | 80       | 120     | ns   |

| 124 | RXD1 setup time                                                 | 20       | —       | ns   |

| 125 | RXD1 hold time                                                  | 5        | —       | ns   |

| 126 | RENA active delay (from RCLK1 rising edge of the last data bit) | 10       | —       | ns   |

| 127 | RENA width low                                                  | 100      | —       | ns   |

| 128 | TCLK1 rise/fall time                                            | —        | 15      | ns   |

| 129 | TCLK1 width low                                                 | 40       | —       | ns   |

| 130 | TCLK1 clock period <sup>1</sup>                                 | 99       | 101     | ns   |

| 131 | TXD1 active delay (from TCLK1 rising edge)                      | 10       | 50      | ns   |

| 132 | TXD1 inactive delay (from TCLK1 rising edge)                    | 10       | 50      | ns   |

| 133 | TENA active delay (from TCLK1 rising edge)                      | 10       | 50      | ns   |

| 134 | TENA inactive delay (from TCLK1 rising edge)                    | 10       | 50      | ns   |

**CPM Electrical Characteristics**

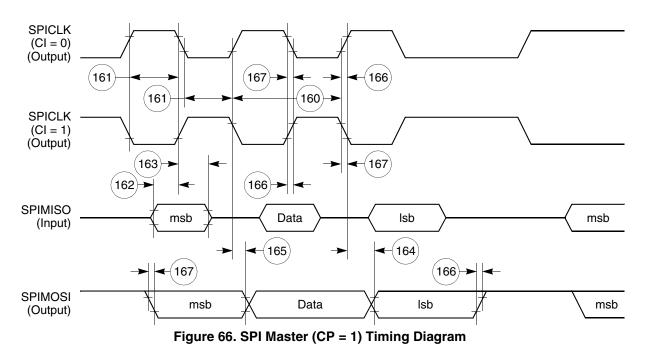

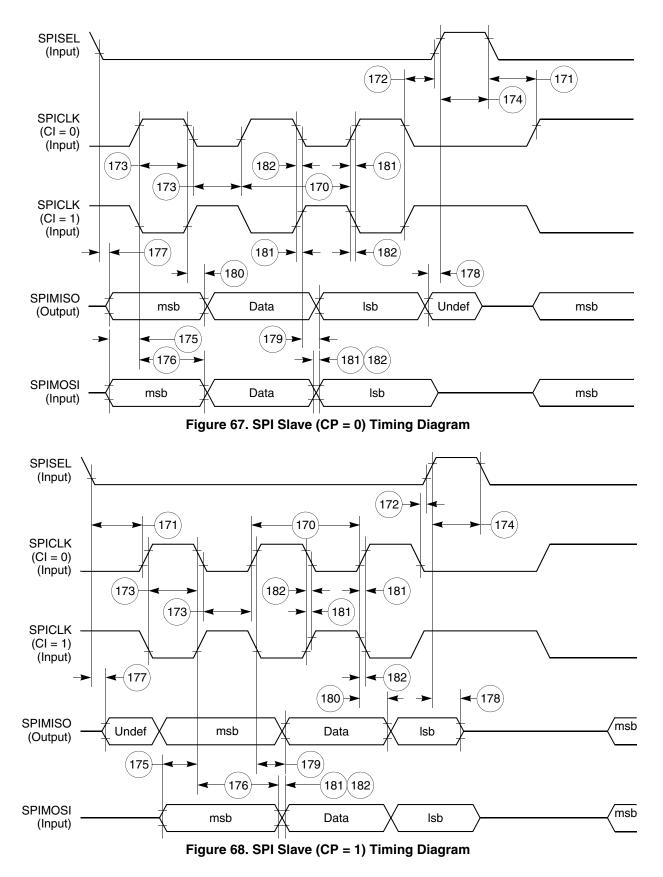

# **11.11 SPI Slave AC Electrical Specifications**

Table 25 provides the SPI slave timings as shown in Figure 67 and Figure 68.

## Table 25. SPI Slave Timing

| Num | Characteristic                                              | All Freq | uencies | Unit             |

|-----|-------------------------------------------------------------|----------|---------|------------------|

| Num | Characteristic                                              | Min      | Мах     | Omi              |

| 170 | Slave cycle time                                            | 2        | —       | t <sub>cyc</sub> |

| 171 | Slave enable lead time                                      | 15       | —       | ns               |

| 172 | Slave enable lag time                                       | 15       | —       | ns               |

| 173 | Slave clock (SPICLK) high or low time                       | 1        | —       | t <sub>cyc</sub> |

| 174 | Slave sequential transfer delay (does not require deselect) | 1        | —       | t <sub>cyc</sub> |

| 175 | Slave data setup time (inputs)                              | 20       | —       | ns               |

| 176 | Slave data hold time (inputs)                               | 20       | —       | ns               |

| 177 | Slave access time                                           | _        | 50      | ns               |

**CPM Electrical Characteristics**

#### Mechanical Data and Ordering Information

| Package Type                                                                                      | Freq. (MHz) /<br>Temp. (Tj) | Package            | Order Number                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball grid array <i>(continued)</i><br>ZP suffix—leaded<br>ZQ suffix—leaded<br>VR suffix—lead-free | 80<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ80D4<br>MPC860DEZQ80D4<br>MPC860DTZQ80D4<br>MPC860ENZQ80D4<br>MPC860SRZQ80D4<br>MPC860TZQ80D4<br>MPC860DPZQ80D4<br>MPC860PZQ80D4                            |

|                                                                                                   |                             | Tape and Reel      | MPC860PZQ80D4R2<br>MPC860PVR80D4R2                                                                                                                                   |

|                                                                                                   |                             | VR                 | MPC855TVR80D4<br>MPC860DEVR80D4<br>MPC860DPVR80D4<br>MPC860ENVR80D4<br>MPC860PVR80D4<br>MPC860SRVR80D4<br>MPC860SRVR80D4<br>MPC860TVR80D4                            |

| Ball grid array (CZP suffix)<br>CZP suffix—leaded<br>CZQ suffix—lead-free                         | 50<br>–40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ50D4<br>MPC855TCVR50D4<br>MPC860DECZQ50D4<br>MPC860DTCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860SRCZQ50D4<br>MPC860DPCZQ50D4<br>MPC860PCZQ50D4 |

|                                                                                                   |                             | Tape and Reel      | MPC855TCZQ50D4R2<br>MC860ENCVR50D4R2                                                                                                                                 |

|                                                                                                   |                             | CVR                | MPC860DECVR50D4<br>MPC860DTCVR50D4<br>MPC860ENCVR50D4<br>MPC860PCVR50D4<br>MPC860SRCVR50D4<br>MPC860SRCVR50D4<br>MPC860TCVR50D4                                      |

|                                                                                                   | 66<br>–40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ66D4<br>MPC855TCVR66D4<br>MPC860ENCZQ66D4<br>MPC860SRCZQ66D4<br>MPC860TCZQ66D4<br>MPC860DPCZQ66D4<br>MPC860PCZQ66D4                                        |

|                                                                                                   |                             | CVR                | MPC860DTCVR66D4<br>MPC860ENCVR66D4<br>MPC860PCVR66D4<br>MPC860SRCVR66D4<br>MPC860TCVR66D4                                                                            |

## Table 34. MPC860 Family Package/Frequency Availability (continued)

<sup>1</sup> The ZP package is no longer recommended for use. The ZQ package replaces the ZP package.

Mechanical Data and Ordering Information

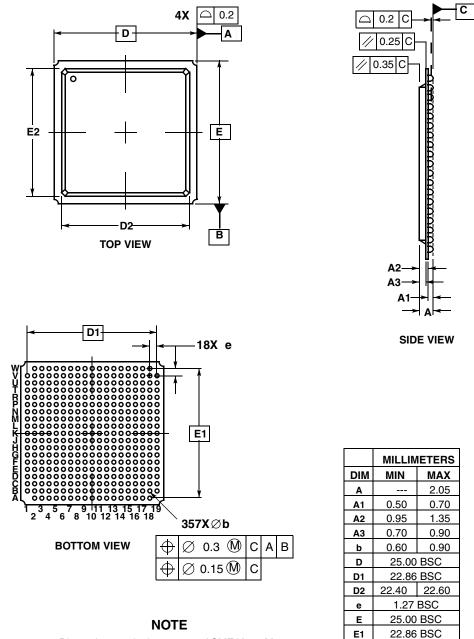

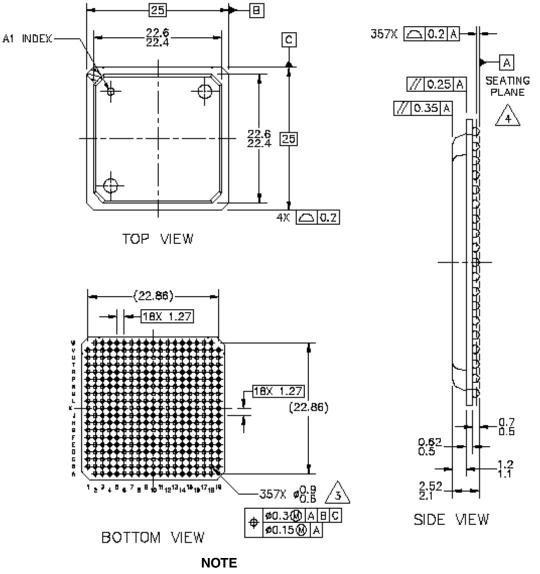

# 14.3 Mechanical Dimensions of the PBGA Package

Figure 77 shows the mechanical dimensions of the ZP PBGA package.

- 1. Dimensions and tolerance per ASME Y14.5M, 1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is the maximum solder ball diameter measured parallel to data C.

22.40

E2

22.60

Figure 78 shows the mechanical dimensions of the ZQ PBGA package.

- 1. All Dimensions in millimeters.

- 2. Dimensions and tolerance per ASME Y14.5M, 1994.

- 3. Maximum Solder Ball Diameter measured parallel to Datum A.

- 4. Datum A, the seating plane, is defined by the spherical crowns of the solder balls.

Figure 78. Mechanical Dimensions and Bottom Surface Nomenclature of the ZQ PBGA Package