#### Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Active                                                      |

| Core Processor                  | MPC8xx                                                      |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 80MHz                                                       |

| Co-Processors/DSP               | Communications; CPM                                         |

| RAM Controllers                 | DRAM                                                        |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10Mbps (4)                                                  |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 3.3V                                                        |

| Operating Temperature           | 0°C ~ 95°C (TJ)                                             |

| Security Features               | -                                                           |

| Package / Case                  | 357-BBGA                                                    |

| Supplier Device Package         | 357-PBGA (25x25)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc860srzq80d4 |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table 7. Bus Operation Timings (continued)**

| N    | Observatoristis                                                                                                                      | 33    | MHz   | 40 I  | MHz   | 50 1  | MHz   | 66   | MHz   | 11!4 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|-------|------|

| Num  | Characteristic                                                                                                                       | Min   | Max   | Min   | Max   | Min   | Max   | Min  | Max   | Unit |

| B31a | CLKOUT falling edge to CS valid—as requested by control bit CST1 in the corresponding word in UPM                                    |       | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B31b | CLKOUT rising edge to CS valid—as requested by control bit CST2 in the corresponding word in UPM                                     | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50 | 8.00  | ns   |

| B31c | CLKOUT rising edge to CS valid—as requested by control bit CST3 in the corresponding word in UPM                                     | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.04 | ns   |

| B31d | CLKOUT falling edge to $\overline{\text{CS}}$ valid—as requested by control bit CST1 in the corresponding word in UPM, EBDF = 1      | 13.26 | 17.99 | 11.28 | 16.00 | 9.40  | 14.13 | 7.58 | 12.31 | ns   |

| B32  | CLKOUT falling edge to BS valid—as requested by control bit BST4 in the corresponding word in UPM                                    |       | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | ns   |       |      |

| B32a | CLKOUT falling edge to $\overline{\text{BS}}$ valid—as requested by control bit BST1 in the corresponding word in UPM, EBDF = 0      | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B32b | CLKOUT rising edge to BS valid—as requested by control bit BST2 in the corresponding word in UPM                                     | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50 | 8.00  | ns   |

| B32c | CLKOUT rising edge to BS valid—as requested by control bit BST3 in the corresponding word in UPM                                     | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B32d | CLKOUT falling edge to BS valid—as requested by control bit BST1 in the corresponding word in UPM, EBDF = 1                          | 13.26 | 17.99 | 11.28 | 16.00 | 9.40  | 14.13 | 7.58 | 12.31 | ns   |

| B33  | CLKOUT falling edge to GPL valid—as requested by control bit GxT4 in the corresponding word in UPM                                   | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50 | 6.00  | ns   |

| B33a | CLKOUT rising edge to GPL valid—as requested by control bit GxT3 in the corresponding word in UPM                                    | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80 | 10.54 | ns   |

| B34  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST4 in the corresponding word in UPM | 5.58  | _     | 4.25  | _     | 3.00  | _     | 1.79 | _     | ns   |

| B34a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST1 in the corresponding word in UPM | 13.15 | _     | 10.50 | _     | 8.00  | _     | 5.58 | _     | ns   |

| B34b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST2 in the corresponding word in UPM | 20.73 | _     | 16.75 | _     | 13.00 | _     | 9.36 | _     | ns   |

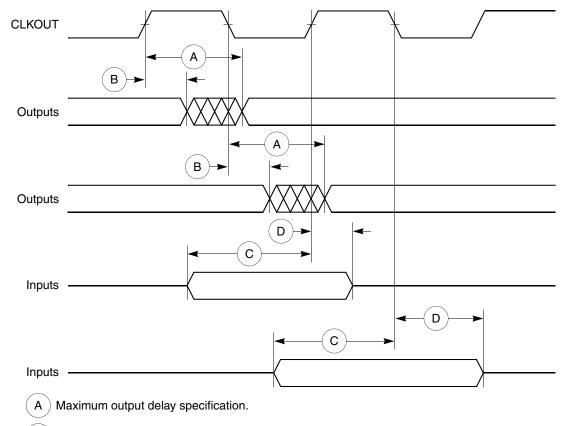

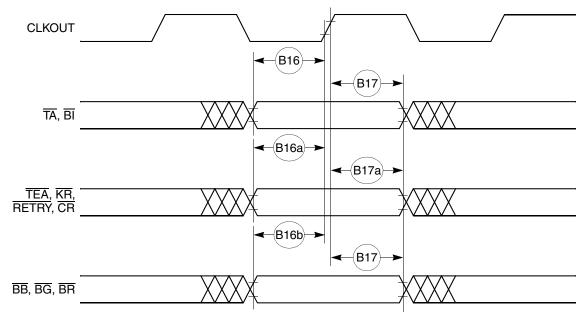

Figure 3 is the control timing diagram.

- (B) Minimum output hold time.

- C Minimum input setup time specification.

- (D) Minimum input hold time specification.

Figure 3. Control Timing

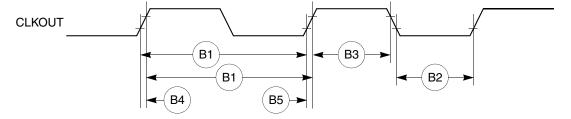

Figure 4 provides the timing for the external clock.

Figure 4. External Clock Timing

### **Bus Signal Timing**

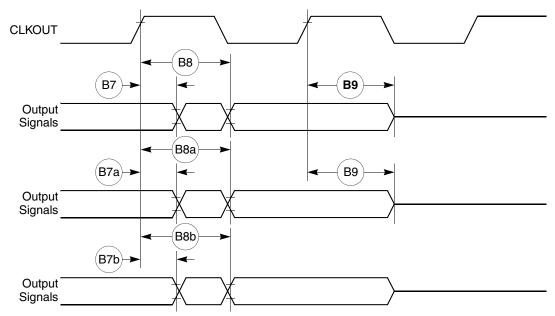

Figure 5 provides the timing for the synchronous output signals.

Figure 5. Synchronous Output Signals Timing

Figure 6 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 6. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

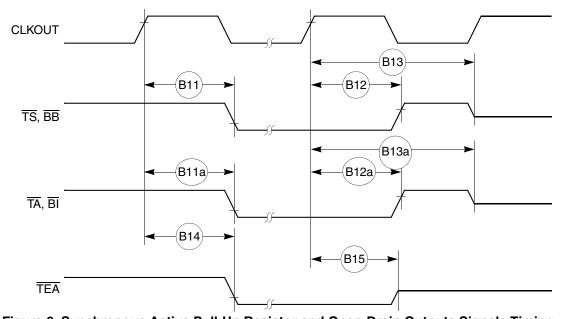

Figure 7 provides the timing for the synchronous input signals.

Figure 7. Synchronous Input Signals Timing

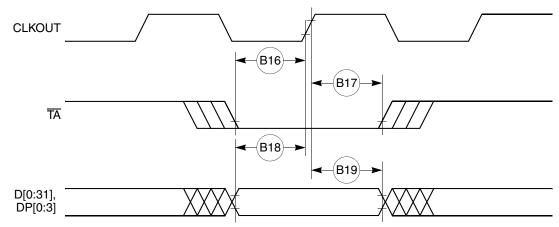

Figure 8 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 8. Input Data Timing in Normal Case

### **Bus Signal Timing**

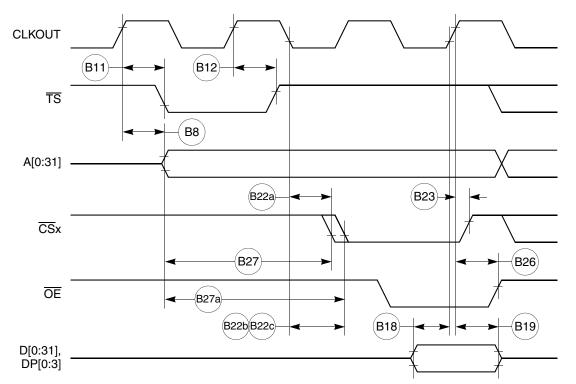

Figure 13. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 10, ACS = 11)

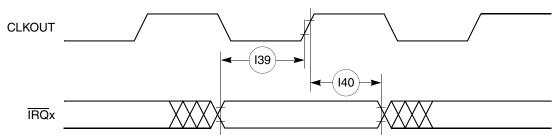

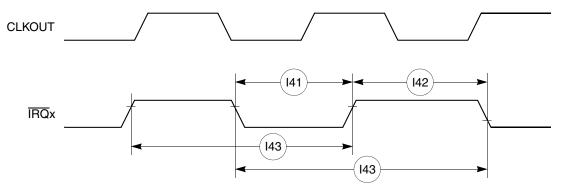

Table 8 provides interrupt timing for the MPC860.

**Table 8. Interrupt Timing**

| Num | Characteristic <sup>1</sup>                   | All Frequencies  Min Max  |   | l locit |

|-----|-----------------------------------------------|---------------------------|---|---------|

|     | Characteristic                                |                           |   | Unit    |

| 139 | IRQx valid to CLKOUT rising edge (setup time) | 6.00                      | _ | ns      |

| 140 | IRQx hold time after CLKOUT                   | 2.00                      | _ | ns      |

| I41 | IRQx pulse width low                          | 3.00                      | _ | ns      |

| 142 | IRQx pulse width high                         | 3.00                      | _ | ns      |

| 143 | ĪRQx edge-to-edge time                        | 4 × T <sub>CLOCKOUT</sub> | _ | _       |

The timings I39 and I40 describe the testing conditions under which the IRQ lines are tested when being defined as level-sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT.

The timings I41, I42, and I43 are specified to allow the correct function of the IRQ lines detection circuitry and have no direct relation with the total system interrupt latency that the MPC860 is able to support.

Figure 23 provides the interrupt detection timing for the external level-sensitive lines.

Figure 23. Interrupt Detection Timing for External Level Sensitive Lines

Figure 24 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 24. Interrupt Detection Timing for External Edge Sensitive Lines

Freescale Semiconductor 33

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

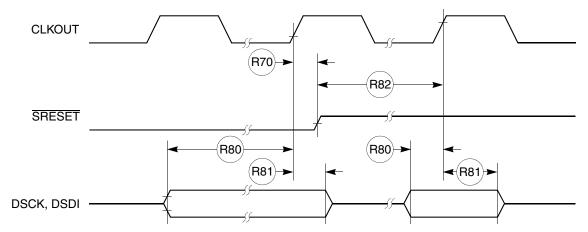

## Table 12 shows the reset timing for the MPC860.

## **Table 12. Reset Timing**

|     | Characteristic                                                                       |        | 1Hz   | 40 MHz |        | 50 MHz |       | 66 MHz |       | Unit |

|-----|--------------------------------------------------------------------------------------|--------|-------|--------|--------|--------|-------|--------|-------|------|

| Num | Characteristic                                                                       | Min    | Max   | Min    | Max    | Min    | Max   | Min    | Max   | Unit |

| R69 | CLKOUT to HRESET high impedance                                                      | _      | 20.00 | _      | 20.00  | _      | 20.00 | _      | 20.00 | ns   |

| R70 | CLKOUT to SRESET high impedance                                                      | _      | 20.00 | _      | 20.00  | _      | 20.00 | _      | 20.00 | ns   |

| R71 | RSTCONF pulse width                                                                  | 515.15 | _     | 425.00 |        | 340.00 | _     | 257.58 | _     | ns   |

| R72 |                                                                                      | _      | _     | _      | _      | _      | _     | _      | _     |      |

| R73 | Configuration data to HRESET rising edge setup time                                  | 504.55 | _     | 425.00 | _      | 350.00 | _     | 277.27 | _     | ns   |

| R74 | Configuration data to RSTCONF rising edge setup time                                 |        |       | _      | 350.00 | _      | ns    |        |       |      |

| R75 | Configuration data hold time after RSTCONF negation                                  |        | _     | 0.00   | _      | 0.00   | _     | 0.00   | _     | ns   |

| R76 | Configuration data hold time after HRESET negation                                   | 0.00   | _     | 0.00   | _      | 0.00   | _     | 0.00   | _     | ns   |

| R77 | HRESET and RSTCONF asserted to data out drive                                        | _      | 25.00 |        | 25.00  | _      | 25.00 | _      | 25.00 | ns   |

| R78 | RSTCONF negated to data out high impedance                                           | _      | 25.00 | _      | 25.00  | _      | 25.00 | _      | 25.00 | ns   |

| R79 | CLKOUT of last rising edge before chip three-state HRESET to data out high impedance |        | _     | 25.00  | _      | 25.00  | _     | 25.00  | ns    |      |

| R80 | DSDI, DSCK setup 90.91 -                                                             |        | _     | 75.00  | _      | 60.00  | _     | 45.45  | _     | ns   |

| R81 | DSDI, DSCK hold time                                                                 | 0.00   | _     | 0.00   | _      | 0.00   | _     | 0.00   | _     | ns   |

| R82 | SRESET negated to CLKOUT rising edge for DSDI and DSCK sample                        | 242.42 |       | 200.00 |        | 160.00 | _     | 121.21 | _     | ns   |

Figure 34 provides the reset timing for the debug port configuration.

Figure 34. Reset Timing—Debug Port Configuration

# 10 IEEE 1149.1 Electrical Specifications

Table 13 provides the JTAG timings for the MPC860 shown in Figure 35 through Figure 38.

| Table | 13. ւ | JTAG | Tim | ing |

|-------|-------|------|-----|-----|

|-------|-------|------|-----|-----|

| Nives | Characteristic                                         | All Freq |       |      |

|-------|--------------------------------------------------------|----------|-------|------|

| Num   | Characteristic                                         | Min      | Max   | Unit |

| J82   | TCK cycle time                                         | 100.00   | _     | ns   |

| J83   | TCK clock pulse width measured at 1.5 V                | 40.00    | _     | ns   |

| J84   | TCK rise and fall times                                | 0.00     | 10.00 | ns   |

| J85   | TMS, TDI data setup time                               | 5.00     | _     | ns   |

| J86   | TMS, TDI data hold time                                |          | _     | ns   |

| J87   | TCK low to TDO data valid                              | _        | 27.00 | ns   |

| J88   | TCK low to TDO data invalid                            | 0.00     | _     | ns   |

| J89   | TCK low to TDO high impedance                          | _        | 20.00 | ns   |

| J90   | TRST assert time                                       | 100.00   | _     | ns   |

| J91   | TRST setup time to TCK low                             | 40.00    | _     | ns   |

| J92   | TCK falling edge to output valid                       | _        | 50.00 | ns   |

| J93   | TCK falling edge to output valid out of high impedance | _        | 50.00 | ns   |

| J94   | TCK falling edge to output high impedance              | _        | 50.00 | ns   |

| J95   | Boundary scan input valid to TCK rising edge           | 50.00    | _     | ns   |

| J96   | TCK rising edge to boundary scan input invalid 5       |          | _     | ns   |

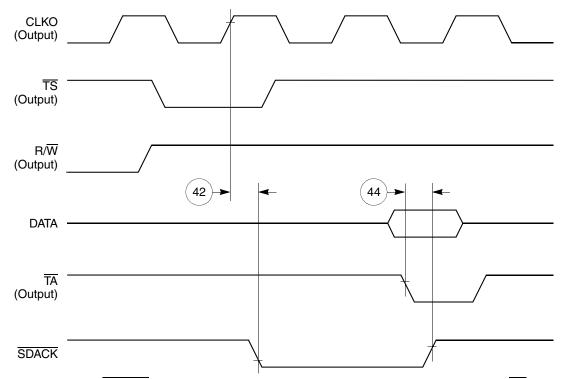

Figure 47. SDACK Timing Diagram—Peripheral Write, Internally-Generated TA

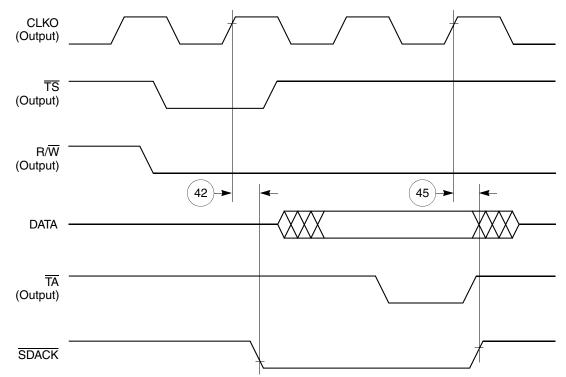

Figure 48. SDACK Timing Diagram—Peripheral Read, Internally-Generated TA

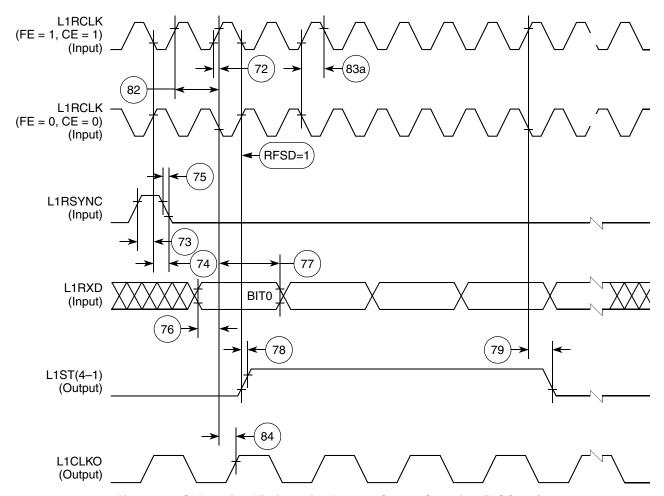

Figure 52. SI Receive Timing with Double-Speed Clocking (DSC = 1)

### **CPM Electrical Characteristics**

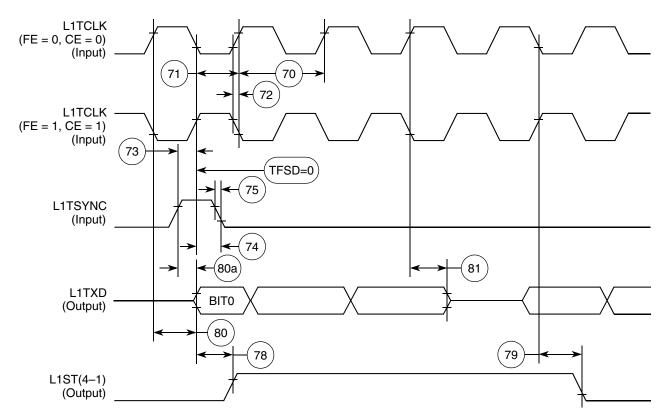

Figure 53. SI Transmit Timing Diagram (DSC = 0)

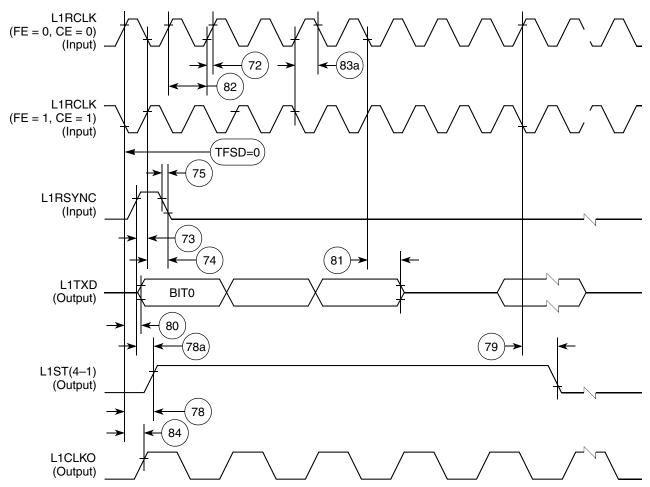

Figure 54. SI Transmit Timing with Double Speed Clocking (DSC = 1)

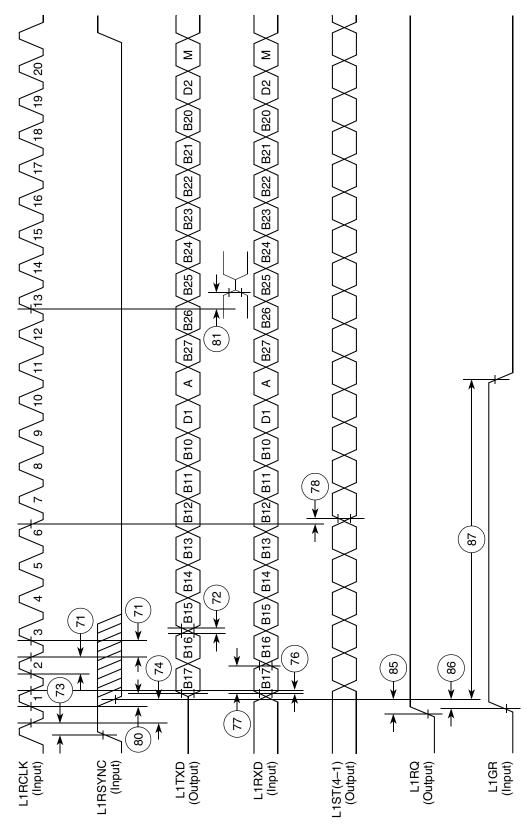

Figure 55. IDL Timing

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

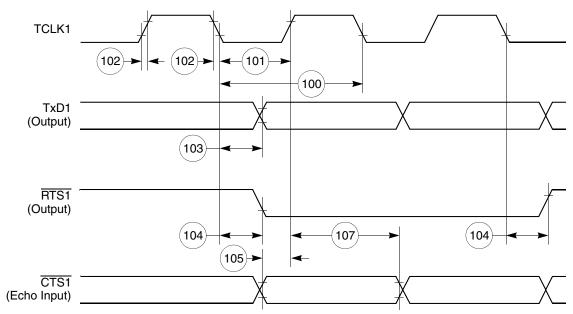

#### **SCC in NMSI Mode Electrical Specifications** 11.7

Table 20 provides the NMSI external clock timing.

**Table 20. NMSI External Clock Timing**

| Neves | Ohawaatawiatia                                       | All Freq      | uencies | I I m i t |  |

|-------|------------------------------------------------------|---------------|---------|-----------|--|

| Num   | Characteristic                                       | Min           | Max     | Unit      |  |

| 100   | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK     | _       | ns        |  |

| 101   | RCLK1 and TCLK1 width low                            | 1/SYNCCLK + 5 | _       | ns        |  |

| 102   | RCLK1 and TCLK1 rise/fall time                       | _             | 15.00   | ns        |  |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00          | 50.00   | ns        |  |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00          | 50.00   | ns        |  |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 5.00          | _       | ns        |  |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 5.00          | _       | ns        |  |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00          | _       | ns        |  |

| 108   | CD1 setup Time to RCLK1 rising edge                  | 5.00          | _       | ns        |  |

Table 21 provides the NMSI internal clock timing.

**Table 21. NMSI Internal Clock Timing**

| Num | Characteristic                                       | All Freq | l lasia   |      |  |

|-----|------------------------------------------------------|----------|-----------|------|--|

| Num |                                                      | Min      | Max       | Unit |  |

| 100 | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00     | SYNCCLK/3 | MHz  |  |

| 102 | RCLK1 and TCLK1 rise/fall time                       | _        | ns        |      |  |

| 103 | TXD1 active delay (from TCLK1 falling edge)          | 0.00     | 30.00     | ns   |  |

| 104 | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00     | 30.00     | ns   |  |

| 105 | CTS1 setup time to TCLK1 rising edge                 | 40.00    | _         | ns   |  |

| 106 | RXD1 setup time to RCLK1 rising edge                 | 40.00    | _         | ns   |  |

| 107 | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00     | _         | ns   |  |

| 108 | CD1 setup time to RCLK1 rising edge 40.00 —          |          |           |      |  |

<sup>&</sup>lt;sup>1</sup> The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 3/1.

The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 2.25/1.

Also applies to CD and CTS hold time when they are used as external sync signals.

$<sup>^2</sup>$  Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as external sync signals.

Figure 58. HDLC Bus Timing Diagram

# 11.8 Ethernet Electrical Specifications

Table 22 provides the Ethernet timings as shown in Figure 59 through Figure 63.

**Table 22. Ethernet Timing**

| N   | Obavastavistis                                                  | All Freq | uencies | 11   |  |

|-----|-----------------------------------------------------------------|----------|---------|------|--|

| Num | Characteristic                                                  | Min      | Max     | Unit |  |

| 120 | CLSN width high                                                 | 40       | _       | ns   |  |

| 121 | RCLK1 rise/fall time                                            | _        | 15      | ns   |  |

| 122 | RCLK1 width low                                                 | 40       | _       | ns   |  |

| 123 | RCLK1 clock period <sup>1</sup>                                 | 80       | 120     | ns   |  |

| 124 | RXD1 setup time 20 —                                            |          |         |      |  |

| 125 | RXD1 hold time                                                  | 5        | _       | ns   |  |

| 126 | RENA active delay (from RCLK1 rising edge of the last data bit) | 10       | _       | ns   |  |

| 127 | RENA width low                                                  | 100      | _       | ns   |  |

| 128 | TCLK1 rise/fall time                                            | 1        | 15      | ns   |  |

| 129 | TCLK1 width low                                                 | 40       | _       | ns   |  |

| 130 | TCLK1 clock period <sup>1</sup>                                 | 99       | 101     | ns   |  |

| 131 | TXD1 active delay (from TCLK1 rising edge)                      | 10       | 50      | ns   |  |

| 132 | TXD1 inactive delay (from TCLK1 rising edge)                    | 10       | 50      | ns   |  |

| 133 | TENA active delay (from TCLK1 rising edge) 10 50                |          |         |      |  |

| 134 | TENA inactive delay (from TCLK1 rising edge) 10 50              |          |         |      |  |

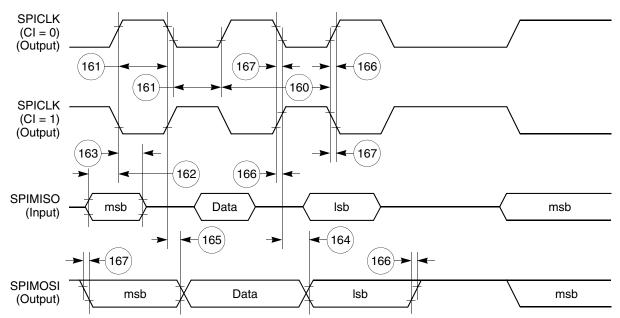

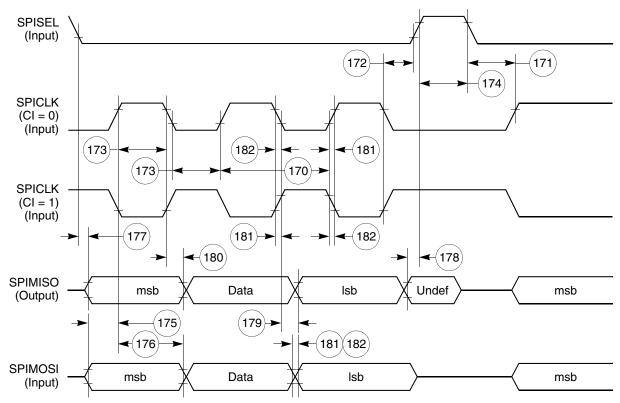

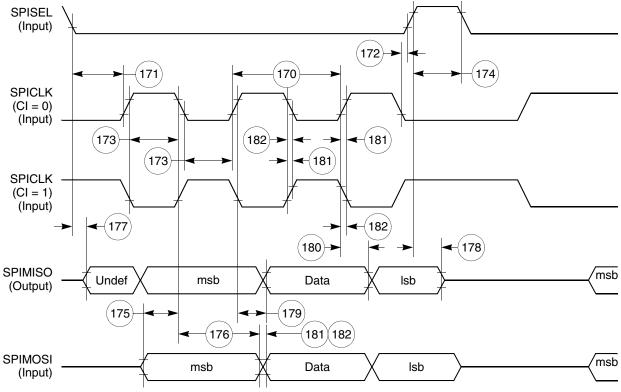

## 11.10 SPI Master AC Electrical Specifications

Table 24 provides the SPI master timings as shown in Figure 65 and Figure 66.

**Table 24. SPI Master Timing**

| Num | Characteristic                      | All Freq | Unit |                  |  |

|-----|-------------------------------------|----------|------|------------------|--|

| Num | Characteristic                      | Min      | Max  | Unit             |  |

| 160 | MASTER cycle time                   | 4        | 1024 | t <sub>cyc</sub> |  |

| 161 | MASTER clock (SCK) high or low time | 2        | 512  | t <sub>cyc</sub> |  |

| 162 | MASTER data setup time (inputs)     | 50       | _    | ns               |  |

| 163 | Master data hold time (inputs)      | 0        | _    | ns               |  |

| 164 | Master data valid (after SCK edge)  | _        | 20   | ns               |  |

| 165 | Master data hold time (outputs) 0 — |          | _    | ns               |  |

| 166 | Rise time output                    | _        | 15   | ns               |  |

| 167 | Fall time output — 15               |          |      |                  |  |

Figure 65. SPI Master (CP = 0) Timing Diagram

Figure 67. SPI Slave (CP = 0) Timing Diagram

Figure 68. SPI Slave (CP = 1) Timing Diagram

#### **FEC Electrical Characteristics** 13

This section provides the AC electrical specifications for the Fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 V or 3.3 V.

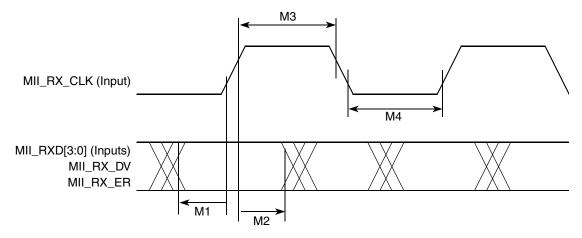

### MII Receive Signal Timing (MII\_RXD[3:0], MII\_RX\_DV, MII\_RX\_ER, 13.1 MII RX CLK)

The receiver functions correctly up to a MII RX CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII RX CLK frequency – 1%.

Table 29 provides information on the MII receive signal timing.

| Num | Characteristic                                         | Min | Max | Unit              |

|-----|--------------------------------------------------------|-----|-----|-------------------|

| M1  | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup | 5   | _   | ns                |

| M2  | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold  | 5   | _   | ns                |

| МЗ  | MII_RX_CLK pulse width high                            | 35% | 65% | MII_RX_CLK period |

| M4  | MII_RX_CLK pulse width low                             | 35% | 65% | MII_RX_CLK period |

**Table 29. MII Receive Signal Timing**

Figure 72 shows MII receive signal timing.

Figure 72. MII Receive Signal Timing Diagram

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10 Freescale Semiconductor 67

**Document Revision History**

# 15 Document Revision History

Table 35 lists significant changes between revisions of this hardware specification.

**Table 35. Document Revision History**

| Revision | Date    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10       | 09/2015 | In Table 34, moved MPC855TCVR50D4 and MPC855TCVR66D4 under the extended temperature (–40° to 95°C) and removed MC860ENCVR50D4R2 from the normal temperature Tape and Reel.                                                                                                                                                                                                                                                                                                                               |

| 9        | 10/2011 | Updated orderable part numbers in Table 34, "MPC860 Family Package/Frequency Availability."                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8        | 08/2007 | <ul> <li>Updated template.</li> <li>On page 1, added a second paragraph.</li> <li>After Table 2, inserted a new figure showing the undershoot/overshoot voltage (Figure 1) and renumbered the rest of the figures.</li> <li>In Figure 3, changed all reference voltage measurement points from 0.2 and 0.8 V to 50% level.</li> <li>In Table 16, changed num 46 description to read, "TA assertion to rising edge"</li> <li>In Figure 46, changed TA to reflect the rising edge of the clock.</li> </ul> |

| 7.0      | 9/2004  | <ul> <li>Added a tablefootnote to Table 6 DC Electrical Specifications about meeting the VIL Max of the I2C Standard</li> <li>Replaced the thermal characteristics in Table 4 by the ZQ package</li> <li>Add the new parts to the Ordering and Availablity Chart in Table 34</li> <li>Added the mechanical spec of the ZQ package in Figure 78</li> <li>Removed all of the old revisions from Table 5</li> </ul>                                                                                         |

| 6.3      | 9/2003  | Added Section 11.2 on the Port C interrupt pins     Nontechnical reformatting                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2      | 8/2003  | Changed B28a through B28d and B29d to show that TRLX can be 0 or 1     Changed reference documentation to reflect the Rev 2 MPC860 PowerQUICC Family Users Manual     Nontechnical reformatting                                                                                                                                                                                                                                                                                                          |

| 6.1      | 11/2002 | <ul> <li>Corrected UTOPIA RXenb* and TXenb* timing values</li> <li>Changed incorrect usage of Vcc to Vdd</li> <li>Corrected dual port RAM to 8 Kbytes</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

| 6        | 10/2002 | Added the MPC855T. Corrected Figure 26 on page -36.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.1      | 11/2001 | Revised template format, removed references to MAC functionality, changed Table 7 B23 max value @ 66 MHz from 2ns to 8ns, added this revision history table                                                                                                                                                                                                                                                                                                                                              |

MPC860 PowerQUICC Family Hardware Specifications, Rev. 10

How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC, QorlQ, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. CoreNet, QorlQ Qonverge, QUICC Engine, and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2007-2015 Freescale Semiconductor, Inc.

Document Number: MPC860EC

Rev. 10 09/2015