#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 50MHz                                                                   |

| Co-Processors/DSP               | Communications; CPM                                                     |

| RAM Controllers                 | DRAM                                                                    |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | ·                                                                       |

| Ethernet                        | 10Mbps (4), 10/100Mbps (1)                                              |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 3.3V                                                                    |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                         |

| Security Features               | -                                                                       |

| Package / Case                  | 357-BBGA                                                                |

| Supplier Device Package         | 357-PBGA (25x25)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc860tzq50d4r2 |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

# 1 Overview

The MPC860 power quad integrated communications controller (PowerQUICC<sup>TM</sup>) is a versatile one-chip integrated microprocessor and peripheral combination designed for a variety of controller applications. It particularly excels in communications and networking systems. The PowerQUICC unit is referred to as the MPC860 in this hardware specification.

The MPC860 implements Power Architecture<sup>TM</sup> technology and contains a superset of Freescale's MC68360 quad integrated communications controller (QUICC), referred to here as the QUICC, RISC communications proceessor module (CPM). The CPU on the MPC860 is a 32-bit core built on Power Architecture technology that incorporates memory management units (MMUs) and instruction and data caches.. The CPM from the MC68360 QUICC has been enhanced by the addition of the inter-integrated controller (I<sup>2</sup>C) channel. The memory controller has been enhanced, enabling the MPC860 to support any type of memory, including high-performance memories and new types of DRAMs. A PCMCIA socket controller supports up to two sockets. A real-time clock has also been integrated.

Table 1 shows the functionality supported by the MPC860 family.

| Part     | Cache (              | Cache (Kbytes) |         | ernet  |     |     |                        |

|----------|----------------------|----------------|---------|--------|-----|-----|------------------------|

|          | Instruction<br>Cache | Data Cache     | 10T     | 10/100 | АТМ | SCC | Reference <sup>1</sup> |

| MPC860DE | 4                    | 4              | Up to 2 | _      | _   | 2   | 1                      |

| MPC860DT | 4                    | 4              | Up to 2 | 1      | Yes | 2   | 1                      |

| MPC860DP | 16                   | 8              | Up to 2 | 1      | Yes | 2   | 1                      |

| MPC860EN | 4                    | 4              | Up to 4 | _      | _   | 4   | 1                      |

| MPC860SR | 4                    | 4              | Up to 4 | —      | Yes | 4   | 1                      |

| MPC860T  | 4                    | 4              | Up to 4 | 1      | Yes | 4   | 1                      |

| MPC860P  | 16                   | 8              | Up to 4 | 1      | Yes | 4   | 1                      |

| MPC855T  | 4                    | 4              | 1       | 1      | Yes | 1   | 2                      |

Table 1. MPC860 Family Functionality

Supporting documentation for these devices refers to the following:

1. MPC860 PowerQUICC Family User's Manual (MPC860UM, Rev. 3)

2. MPC855T User's Manual (MPC855TUM, Rev. 1)

# 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC860. Table 2 provides the maximum ratings.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

(GND = 0 V)

## Table 2. Maximum Tolerated Ratings

| Rating                              | Symbol              | Value                         | Unit |

|-------------------------------------|---------------------|-------------------------------|------|

| Supply voltage <sup>1</sup>         | V <sub>DDH</sub>    | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDL</sub>    | -0.3 to 4.0                   | V    |

|                                     | KAPWR               | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDSYN</sub>  | -0.3 to 4.0                   | V    |

| Input voltage <sup>2</sup>          | V <sub>in</sub>     | GND – 0.3 to V <sub>DDH</sub> | V    |

| Temperature <sup>3</sup> (standard) | T <sub>A(min)</sub> | 0                             | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Temperature <sup>3</sup> (extended) | T <sub>A(min)</sub> | -40                           | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Storage temperature range           | T <sub>stg</sub>    | –55 to 150                    | °C   |

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC860 is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>i</sub>.

Layout Practices

where:

$\Psi_{JT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per JEDEC JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

# 7.6 References

| Semiconductor Equipment and Materials International | (415) 964-5111       |

|-----------------------------------------------------|----------------------|

| 805 East Middlefield Rd.                            |                      |

| Mountain View, CA 94043                             |                      |

| MIL-SPEC and EIA/JESD (JEDEC) Specifications        | 800-854-7179 or      |

| (Available from Global Engineering Documents)       | 303-397-7956         |

| JEDEC Specifications                                | http://www.jedec.org |

- 1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 8 Layout Practices

Each  $V_{DD}$  pin on the MPC860 should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on the chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1 µF-bypass capacitors located as close as possible to the four sides of the package. The capacitor leads and associated printed circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than half an inch per capacitor lead. A four-layer board employing two inner layers as  $V_{CC}$  and GND planes is recommended.

All output pins on the MPC860 have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of 6 inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{CC}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

|      | Ohamata i ii                                                                                                                                    | 33 MHz 40 Mł |       | MHz 50 MHz |       |       | 66 MHz |       | 11-1-1-1 |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------------|-------|-------|--------|-------|----------|------|

| Num  | Characteristic                                                                                                                                  | Min          | Max   | Min        | Max   | Min   | Max    | Min   | Max      | Unit |

| B23  | CLKOUT rising edge to $\overline{\text{CS}}$ negated GPCM read access, GPCM write access ACS = 00, TRLX = 0, and CSNT = 0                       | 2.00         | 8.00  | 2.00       | 8.00  | 2.00  | 8.00   | 2.00  | 8.00     | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 10, TRLX = 0                                                                    | 5.58         | —     | 4.25       | _     | 3.00  | —      | 1.79  | _        | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 11, TRLX = 0                                                                    | 13.15        | —     | 10.50      | _     | 8.00  | _      | 5.58  | —        | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}$ (0:3) asserted                                                                          | _            | 9.00  | _          | 9.00  | —     | 9.00   | _     | 9.00     | ns   |

| B26  | CLKOUT rising edge to OE negated                                                                                                                | 2.00         | 9.00  | 2.00       | 9.00  | 2.00  | 9.00   | 2.00  | 9.00     | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 10, TRLX = 1                                                                    | 35.88        | _     | 29.25      | _     | 23.00 | _      | 16.94 | _        | ns   |

| B27a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 11, TRLX = 1                                                                    | 43.45        | —     | 35.50      | —     | 28.00 | —      | 20.73 | —        | ns   |

| B28  | CLKOUT rising edge to $\overline{WE}(0:3)$ negated<br>GPCM write access CSNT = 0                                                                | _            | 9.00  | _          | 9.00  | —     | 9.00   | _     | 9.00     | ns   |

| B28a | CLKOUT falling edge to $\overline{WE}(0:3)$ negated<br>GPCM write access TRLX = 0, 1, CSNT = 1,<br>EBDF = 0                                     | 7.58         | 14.33 | 6.25       | 13.00 | 5.00  | 11.75  | 3.80  | 10.54    | ns   |

| B28b | CLKOUT falling edge to $\overline{CS}$ negated GPCM<br>write access TRLX = 0, 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0                   | _            | 14.33 | _          | 13.00 | _     | 11.75  | —     | 10.54    | ns   |

| B28c | CLKOUT falling edge to $\overline{WE}$ (0:3) negated<br>GPCM write access TRLX = 0, 1, CSNT = 1<br>write access TRLX = 0, CSNT = 1,<br>EBDF = 1 | 10.86        | 17.99 | 8.88       | 16.00 | 7.00  | 14.13  | 5.18  | 12.31    | ns   |

| B28d | CLKOUT falling edge to $\overline{CS}$ negated GPCM<br>write access TRLX = 0, 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                   | _            | 17.99 | —          | 16.00 | —     | 14.13  | —     | 12.31    | ns   |

| B29  | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access CSNT = 0, EBDF = 0                                                 | 5.58         | —     | 4.25       | —     | 3.00  | —      | 1.79  | —        | ns   |

| B29a | $\overline{WE}(0:3)$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>EBDF = 0                                   | 13.15        | —     | 10.5       | —     | 8.00  | —      | 5.58  |          | ns   |

| B29b | $\overline{CS}$ negated to D(0:31), DP(0:3), High-Z<br>GPCM write access, ACS = 00, TRLX = 0, 1,<br>and CSNT = 0                                | 5.58         |       | 4.25       |       | 3.00  |        | 1.79  |          | ns   |

| B29c | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0          | 13.15        |       | 10.5       |       | 8.00  |        | 5.58  |          | ns   |

## Table 7. Bus Operation Timings (continued)

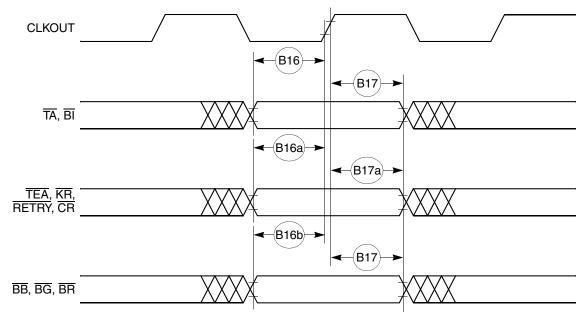

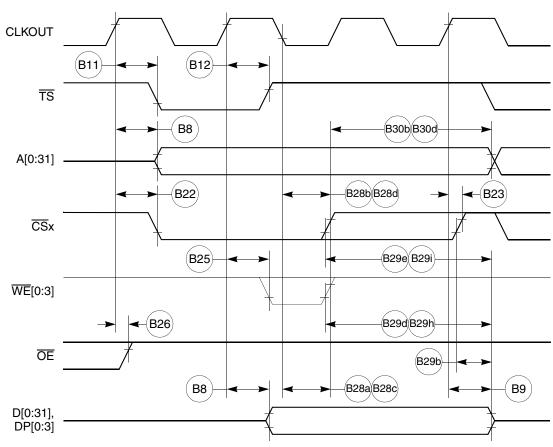

Figure 7 provides the timing for the synchronous input signals.

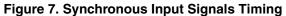

Figure 8 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 8. Input Data Timing in Normal Case

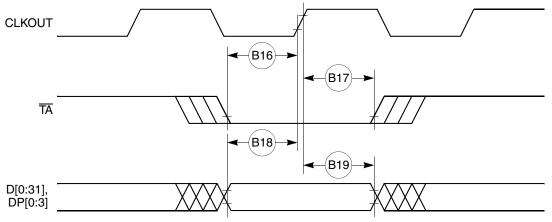

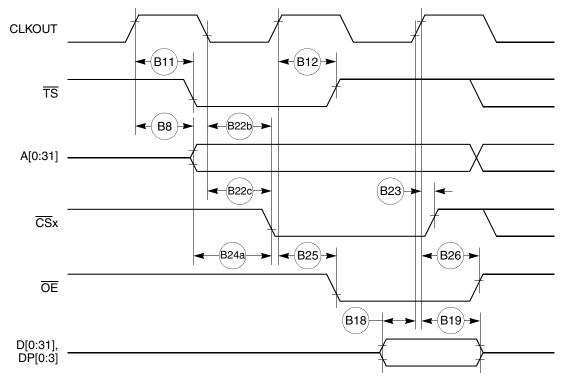

Figure 12. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 11)

**Bus Signal Timing**

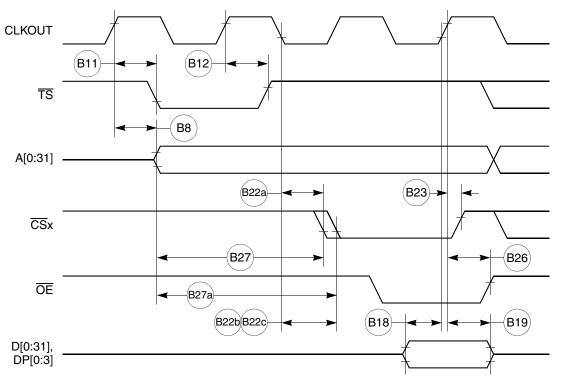

Figure 13. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 10, ACS = 11)

**Bus Signal Timing**

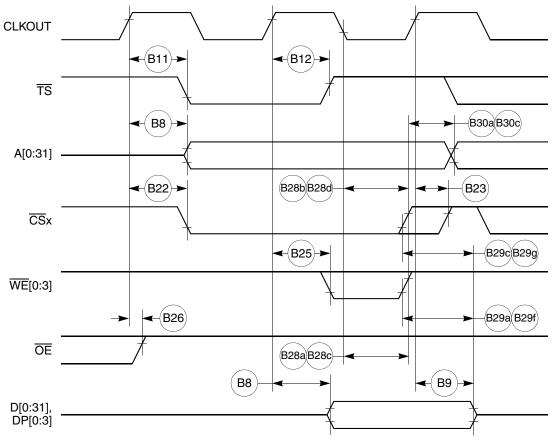

Figure 15. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

Table 12 shows the reset timing for the MPC860.

Table 12. Reset Timing

| Num | Characteristic                                                                             | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|-----|--------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| NUM | Unaracteristic                                                                             | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| R69 | CLKOUT to HRESET high impedance                                                            | —      | 20.00 | —      | 20.00 | _      | 20.00 | —      | 20.00 | ns   |

| R70 | CLKOUT to SRESET high impedance                                                            | —      | 20.00 | —      | 20.00 | —      | 20.00 | —      | 20.00 | ns   |

| R71 | RSTCONF pulse width                                                                        | 515.15 | _     | 425.00 |       | 340.00 | _     | 257.58 | —     | ns   |

| R72 | _                                                                                          | —      | _     | —      | _     | —      | _     | —      | —     |      |

| R73 | Configuration data to HRESET rising edge setup time                                        | 504.55 | —     | 425.00 | —     | 350.00 | _     | 277.27 | —     | ns   |

| R74 | Configuration data to RSTCONF rising edge setup time                                       | 350.00 | —     | 350.00 | —     | 350.00 | _     | 350.00 | —     | ns   |

| R75 | Configuration data hold time after<br>RSTCONF negation                                     | 0.00   | —     | 0.00   | —     | 0.00   | _     | 0.00   | —     | ns   |

| R76 | Configuration data hold time after<br>HRESET negation                                      | 0.00   | —     | 0.00   | —     | 0.00   | _     | 0.00   | —     | ns   |

| R77 | HRESET and RSTCONF asserted to data out drive                                              | —      | 25.00 |        | 25.00 | —      | 25.00 | —      | 25.00 | ns   |

| R78 | RSTCONF negated to data out high impedance                                                 | —      | 25.00 | —      | 25.00 | —      | 25.00 | —      | 25.00 | ns   |

| R79 | CLKOUT of last rising edge before chip<br>three-state HRESET to data out high<br>impedance | —      | 25.00 | —      | 25.00 | —      | 25.00 | —      | 25.00 | ns   |

| R80 | DSDI, DSCK setup                                                                           | 90.91  | —     | 75.00  | _     | 60.00  |       | 45.45  | —     | ns   |

| R81 | DSDI, DSCK hold time                                                                       | 0.00   | _     | 0.00   |       | 0.00   |       | 0.00   | —     | ns   |

| R82 | SRESET negated to CLKOUT rising edge for DSDI and DSCK sample                              | 242.42 | —     | 200.00 | —     | 160.00 | _     | 121.21 | —     | ns   |

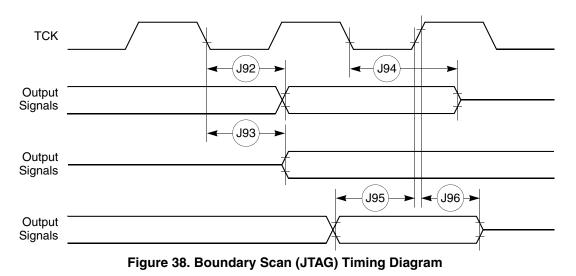

### **IEEE 1149.1 Electrical Specifications**

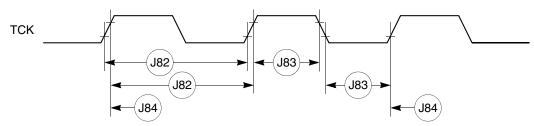

## Figure 35. JTAG Test Clock Input Timing

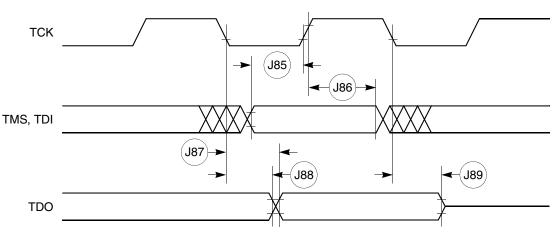

Figure 36. JTAG Test Access Port Timing Diagram

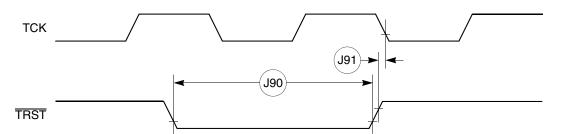

Figure 37. JTAG TRST Timing Diagram

**CPM Electrical Characteristics**

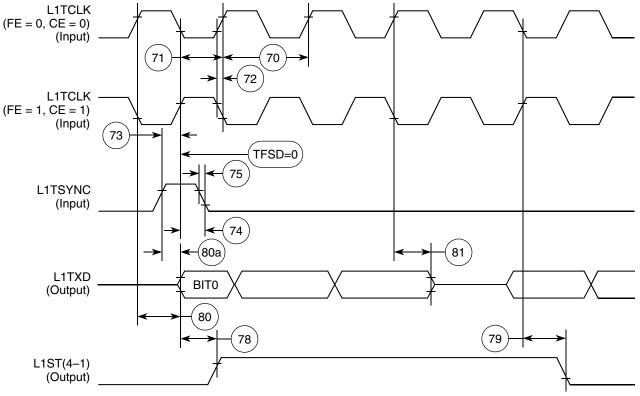

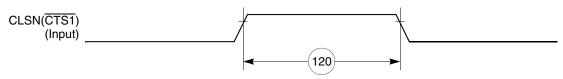

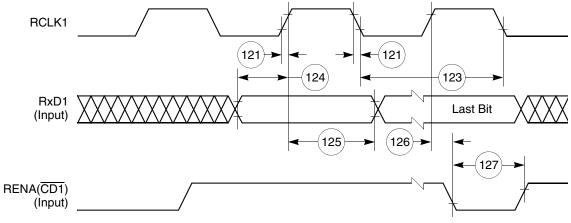

#### SCC in NMSI Mode Electrical Specifications 11.7

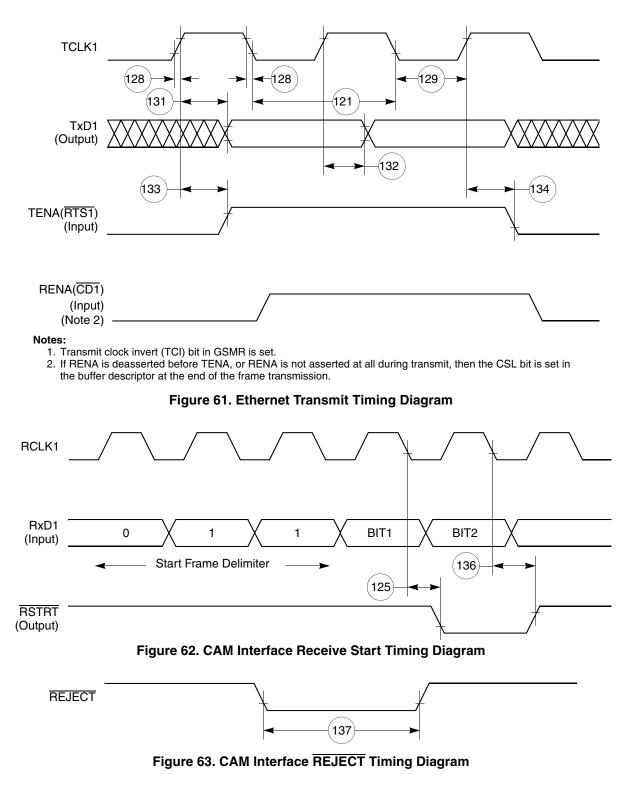

Table 20 provides the NMSI external clock timing.

| News | Characteristic                                       | All Freq      | uencies | 11   |

|------|------------------------------------------------------|---------------|---------|------|

| Num  | Characteristic                                       | Min           | Мах     | Unit |

| 100  | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK     | _       | ns   |

| 101  | RCLK1 and TCLK1 width low                            | 1/SYNCCLK + 5 | _       | ns   |

| 102  | RCLK1 and TCLK1 rise/fall time                       | —             | 15.00   | ns   |

| 103  | TXD1 active delay (from TCLK1 falling edge)          | 0.00          | 50.00   | ns   |

| 104  | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00          | 50.00   | ns   |

| 105  | CTS1 setup time to TCLK1 rising edge                 | 5.00          | —       | ns   |

| 106  | RXD1 setup time to RCLK1 rising edge                 | 5.00          | _       | ns   |

| 107  | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00          | —       | ns   |

| 108  | CD1 setup Time to RCLK1 rising edge                  | 5.00          | _       | ns   |

<sup>1</sup> The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to CD and CTS hold time when they are used as external sync signals.

# Table 21 provides the NMSI internal clock timing.

# Table 21. NMSI Internal Clock Timing

| Num | Characteristic                                       | All Freq | Unit      |      |

|-----|------------------------------------------------------|----------|-----------|------|

| num | Characteristic                                       | Min      | Мах       | Unit |

| 100 | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00     | SYNCCLK/3 | MHz  |

| 102 | RCLK1 and TCLK1 rise/fall time                       | _        | —         | ns   |

| 103 | TXD1 active delay (from TCLK1 falling edge)          | 0.00     | 30.00     | ns   |

| 104 | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00     | 30.00     | ns   |

| 105 | CTS1 setup time to TCLK1 rising edge                 | 40.00    | —         | ns   |

| 106 | RXD1 setup time to RCLK1 rising edge                 | 40.00    | —         | ns   |

| 107 | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00     | —         | ns   |

| 108 | CD1 setup time to RCLK1 rising edge                  | 40.00    | _         | ns   |

<sup>1</sup> The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{CD}$  and  $\overline{CTS}$  hold time when they are used as external sync signals.

**CPM Electrical Characteristics**

| Num | Characteristic                                 | All Freq | Linit |      |

|-----|------------------------------------------------|----------|-------|------|

| Num |                                                | Min      | Мах   | Unit |

| 135 | RSTRT active delay (from TCLK1 falling edge)   | 10       | 50    | ns   |

| 136 | RSTRT inactive delay (from TCLK1 falling edge) | 10       | 50    | ns   |

| 137 | REJECT width low                               | 1        | —     | CLK  |

| 138 | CLKO1 low to SDACK asserted <sup>2</sup>       | _        | 20    | ns   |

| 139 | CLKO1 low to SDACK negated <sup>2</sup>        | _        | 20    | ns   |

## Table 22. Ethernet Timing (continued)

<sup>1</sup> The ratios SYNCCLK/RCLK1 and SYNCCLK/TCLK1 must be greater than or equal to 2/1.

<sup>2</sup> SDACK is asserted whenever the SDMA writes the incoming frame DA into memory.

Figure 59. Ethernet Collision Timing Diagram

Figure 60. Ethernet Receive Timing Diagram

**CPM Electrical Characteristics**

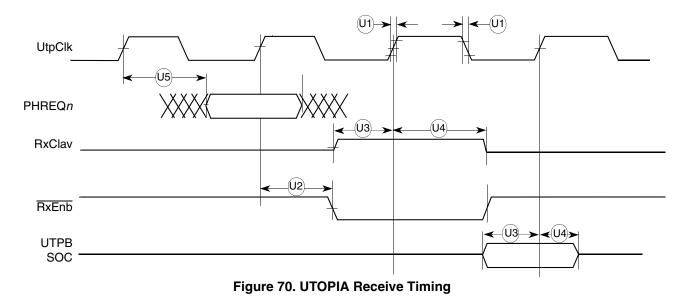

### **UTOPIA AC Electrical Specifications**

Figure 70 shows signal timings during UTOPIA receive operations.

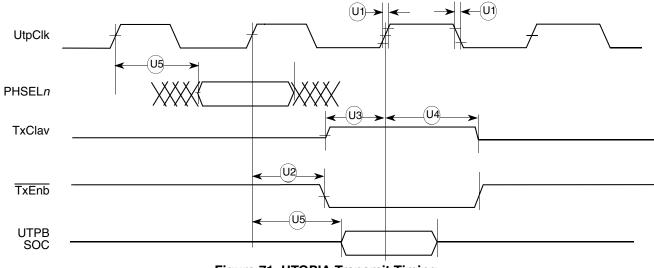

Figure 71 shows signal timings during UTOPIA transmit operations.

Figure 71. UTOPIA Transmit Timing

**FEC Electrical Characteristics**

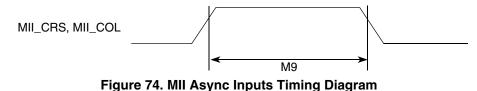

# 13.3 MII Async Inputs Signal Timing (MII\_CRS, MII\_COL)

Table 31 provides information on the MII async inputs signal timing.

Table 31. MII Async Inputs Signal Timing

| Num | Characteristic                       | Min | Max | Unit                 |

|-----|--------------------------------------|-----|-----|----------------------|

| M9  | MII_CRS, MII_COL minimum pulse width | 1.5 | _   | MII_TX_CLK<br>period |

Figure 74 shows the MII asynchronous inputs signal timing diagram.

# 13.4 MII Serial Management Channel Timing (MII\_MDIO, MII\_MDC)

Table 32 provides information on the MII serial management channel signal timing. The FEC functions correctly with a maximum MDC frequency in excess of 2.5 MHz. The exact upper bound is under investigation.

| Num | Characteristic                                                              | Min | Max | Unit              |

|-----|-----------------------------------------------------------------------------|-----|-----|-------------------|

| M10 | MII_MDC falling edge to MII_MDIO output invalid (minimum propagation delay) | 0   | _   | ns                |

| M11 | MII_MDC falling edge to MII_MDIO output valid (max prop delay)              | _   | 25  | ns                |

| M12 | MII_MDIO (input) to MII_MDC rising edge setup                               | 10  | _   | ns                |

| M13 | MII_MDIO (input) to MII_MDC rising edge hold                                | 0   | _   | ns                |

| M14 | MII_MDC pulse width high                                                    | 40% | 60% | MII_MDC<br>period |

| M15 | MII_MDC pulse width low                                                     | 40% | 60% | MII_MDC<br>period |

### Table 32. MII Serial Management Channel Timing

# Table 34 identifies the packages and operating frequencies available for the MPC860.

| Package Type                                                                   | Freq. (MHz) /<br>Temp. (Tj) | Package            | Order Number                                                                                                                                                                                                        |  |  |  |  |

|--------------------------------------------------------------------------------|-----------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Ball grid array<br>ZP suffix—leaded<br>ZQ suffix—leaded<br>VR suffix—lead-free | 50<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ50D4<br>MPC860DEZQ50D4<br>MPC860DTZQ50D4<br>MPC860ENZQ50D4<br>MPC860SRZQ50D4<br>MPC860TZQ50D4<br>MPC860DPZQ50D4<br>MPC860PZQ50D4                                                                           |  |  |  |  |

|                                                                                |                             | Tape and Reel      | MPC855TZQ50D4R2<br>MPC860DEZQ50D4R2<br>MPC860ENZQ50D4R2<br>MPC860SRZQ50D4R2<br>MPC860TZQ50D4R2<br>MPC860TZQ50D4R2<br>MPC860DPZQ50D4R2<br>MPC855TVR50D4R2<br>MPC860ENVR50D4R2<br>MPC860SRVR50D4R2<br>MPC860TVR50D4R2 |  |  |  |  |

|                                                                                |                             | VR                 | MPC855TVR50D4<br>MPC860DEVR50D4<br>MPC860DPVR50D4<br>MPC860DTVR50D4<br>MPC860ENVR50D4<br>MPC860PVR50D4<br>MPC860SRVR50D4<br>MPC860SRVR50D4<br>MPC860TVR50D4                                                         |  |  |  |  |

|                                                                                | 66<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ66D4<br>MPC860DEZQ66D4<br>MPC860DTZQ66D4<br>MPC860ENZQ66D4<br>MPC860SRZQ66D4<br>MPC860TZQ66D4<br>MPC860DPZQ66D4<br>MPC860PZQ66D4                                                                           |  |  |  |  |

|                                                                                |                             | Tape and Reel      | MPC860SRZQ66D4R2<br>MPC860PZQ66D4R2                                                                                                                                                                                 |  |  |  |  |

|                                                                                |                             | VR                 | MPC855TVR66D4<br>MPC860DEVR66D4<br>MPC860DPVR66D4<br>MPC860DTVR66D4<br>MPC860ENVR66D4<br>MPC860PVR66D4<br>MPC860SRVR66D4<br>MPC860TVR66D4                                                                           |  |  |  |  |

# Table 34. MPC860 Family Package/Frequency Availability

### Mechanical Data and Ordering Information

| Package Type                                                                                      | Freq. (MHz) /<br>Temp. (Tj) | Order Number       |                                                                                                                                                                      |  |  |

|---------------------------------------------------------------------------------------------------|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ball grid array <i>(continued)</i><br>ZP suffix—leaded<br>ZQ suffix—leaded<br>VR suffix—lead-free | 80<br>0° to 95°C            | ZP/ZQ <sup>1</sup> | MPC855TZQ80D4<br>MPC860DEZQ80D4<br>MPC860DTZQ80D4<br>MPC860ENZQ80D4<br>MPC860SRZQ80D4<br>MPC860TZQ80D4<br>MPC860DPZQ80D4<br>MPC860PZQ80D4                            |  |  |

|                                                                                                   |                             | Tape and Reel      | MPC860PZQ80D4R2<br>MPC860PVR80D4R2                                                                                                                                   |  |  |

|                                                                                                   |                             | VR                 | MPC855TVR80D4<br>MPC860DEVR80D4<br>MPC860DPVR80D4<br>MPC860ENVR80D4<br>MPC860PVR80D4<br>MPC860SRVR80D4<br>MPC860SRVR80D4<br>MPC860TVR80D4                            |  |  |

| Ball grid array (CZP suffix)<br>CZP suffix—leaded<br>CZQ suffix—leaded<br>CVR suffix—lead-free    | 50<br>–40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ50D4<br>MPC855TCVR50D4<br>MPC860DECZQ50D4<br>MPC860DTCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860ENCZQ50D4<br>MPC860SRCZQ50D4<br>MPC860DPCZQ50D4<br>MPC860PCZQ50D4 |  |  |

|                                                                                                   |                             | Tape and Reel      | MPC855TCZQ50D4R2<br>MC860ENCVR50D4R2                                                                                                                                 |  |  |

|                                                                                                   |                             | CVR                | MPC860DECVR50D4<br>MPC860DTCVR50D4<br>MPC860ENCVR50D4<br>MPC860PCVR50D4<br>MPC860SRCVR50D4<br>MPC860SRCVR50D4<br>MPC860TCVR50D4                                      |  |  |

|                                                                                                   | 66<br>–40° to 95°C          | ZP/ZQ <sup>1</sup> | MPC855TCZQ66D4<br>MPC855TCVR66D4<br>MPC860ENCZQ66D4<br>MPC860SRCZQ66D4<br>MPC860TCZQ66D4<br>MPC860DPCZQ66D4<br>MPC860PCZQ66D4                                        |  |  |

|                                                                                                   |                             | CVR                | MPC860DTCVR66D4<br>MPC860ENCVR66D4<br>MPC860PCVR66D4<br>MPC860SRCVR66D4<br>MPC860TCVR66D4                                                                            |  |  |

## Table 34. MPC860 Family Package/Frequency Availability (continued)

<sup>1</sup> The ZP package is no longer recommended for use. The ZQ package replaces the ZP package.

# 14.2 Pin Assignments

Figure 76 shows the top view pinout of the PBGA package. For additional information, see the MPC860 PowerQUICC User's Manual, or the MPC855T User's Manual.

| (         |           |           |           |                        |                        |            |            |                           |            |                    |            |            |            |            |                        |               |            |              |         |

|-----------|-----------|-----------|-----------|------------------------|------------------------|------------|------------|---------------------------|------------|--------------------|------------|------------|------------|------------|------------------------|---------------|------------|--------------|---------|

|           | O<br>PD10 | O<br>PD8  | O<br>PD3  |                        | )<br>D0                | O<br>D4    | ()<br>D1   | ()<br>D2                  | )<br>D3    | )<br>D5            |            | )<br>D6    | ()<br>D7   | )<br>D29   | O<br>DP2               |               |            |              | w       |

| O<br>PD14 | O<br>PD13 | O<br>PD9  | O<br>PD6  | ⊖<br>M_Tx_I            |                        | O<br>D13   | ()<br>D27  | 〇<br>D10                  | )<br>D14   | )<br>D18           | )<br>D20   | 0<br>D24   | ()<br>D28  | O<br>DP1   | O<br>DP3               |               | )<br>N/C \ |              | v<br>1  |

| 0<br>PA0  | O<br>PB14 | O<br>PD15 | O<br>PD4  | O<br>PD5               |                        | ()<br>D8   | ()<br>D23  | ()<br>D11                 | 〇<br>D16   | ()<br>D19          | ()<br>D21  | 0<br>D26   | )<br>D30   | O<br>IPA5  | )<br>IPA4              | O<br>IPA2     | ○<br>N/C   |              | U       |

| O<br>PA1  | O<br>PC5  | O<br>PC4  | O<br>PD11 | O<br>PD7               |                        | 0<br>1 D12 | 0<br>D17   | O<br>D9                   | )<br>D15   | 0<br>D22           | 0<br>D25   | O<br>D31   | O<br>IPA6  |            | )<br>IPA1              | O<br>IPA7     | ⊖<br>xfc   |              | т       |

| <br>₽C6   | 0<br>PA2  | O<br>PB15 | O<br>PD12 | $\left( \circ \right)$ |                        | 0          | 0          | $\bigcirc$                | $\bigcirc$ | 0                  | 0          | $\bigcirc$ | 0          |            |                        |               |            |              | R<br>VR |

| O<br>PA4  | О<br>РВ17 | O<br>PA3  |           | 0                      | $\left( \circ \right)$ |            | 0          | $\bigcirc$                | $\bigcirc$ | 0                  | $\bigcirc$ | $\bigcirc$ |            | $\circ$    |                        |               |            | C<br>ET XTAL | Р       |

| O<br>PB19 | O<br>PA5  | O<br>PB18 | 〇<br>PB16 | 0                      | 0                      | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        |               |            |              | Ν       |

| 0<br>PA7  | 0<br>PC8  | 0<br>PA6  | O<br>PC7  | 0                      | $\circ$                | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        | BADDR28       |            | O<br>R29 VDD | M<br>L  |

| O<br>PB22 | O<br>PC9  | 0<br>PA8  | О<br>РВ20 | 0                      | $\bigcirc$             | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | 0<br>0P0               | $\bigcirc$ AS | O<br>OP1   |              | L       |

| O<br>PC10 | O<br>PA9  | O<br>PB23 | O<br>PB21 | 0                      | 0                      | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                |            | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |                        | 0<br>130 IPB6 |            |              | к       |

| O<br>PC11 | O<br>PB24 | 〇<br>PA10 | O<br>PB25 | 0                      | $\circ$                | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | O<br>IPB5              | O<br>IPB1     |            | O            | J       |

|           |           |           | О<br>тск  | 0                      | 0                      | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | O<br>M_COI             |               |            |              | н       |

|           | O<br>TMS  | O<br>TDO  | O<br>PA11 | 0                      | 0                      | )<br>GND   | $\bigcirc$ | $\bigcirc$                | $\bigcirc$ | $\bigcirc$         | $\bigcirc$ | $\bigcirc$ | O<br>GND   | 0          |                        |               | O<br>IPB4  | O<br>IPB3    | G       |

| O<br>PB26 | O<br>PC12 | 〇<br>PA12 |           | 0                      |                        |            | 0          | 0                         | 0          | 0                  | 0          | 0          |            |            |                        | ⊖<br>⊤s       |            |              | F       |

| O<br>PB27 | O<br>PC13 | 〇<br>PA13 | O<br>PB29 | $\bigcirc$             | 0                      | 0          | 0          | 0                         | 0          | 0                  | 0          | 0          | 0          | 0          | $\frac{\bigcirc}{CS3}$ |               |            |              | Е       |

| O<br>PB28 | O<br>PC14 | O<br>PA14 | O<br>PC15 | ()<br>A8               | O<br>N/C               | O<br>N/C   | ()<br>A15  | 〇<br>A19                  | ()<br>A25  | ()<br>A18          |            |            | O<br>N/C   |            | $\frac{\bigcirc}{CS2}$ |               |            |              | D       |

| O<br>PB30 | O<br>PA15 | O<br>PB31 | ()<br>A3  | ()<br>A9               | ()<br>A12              | 〇<br>A16   | ()<br>A20  | )<br>A24                  | ()<br>A26  |                    |            |            |            |            |                        |               |            |              | с       |

| ()<br>A0  | ()<br>A1  | ()<br>A4  | 0<br>A6   | )<br>A10               | 〇<br>A13               | ()<br>A17  | ()<br>A21  | ()<br>A23                 | )<br>A22   |                    | $\bigcirc$ |            |            |            | $\frac{\bigcirc}{CS5}$ |               |            |              | в       |

|           | 0<br>A2   | 0<br>A5   | 0<br>A7   | 0<br>A11               | 0<br>A14               | 0<br>A27   | 0<br>A29   | )<br>()<br>()<br>()<br>() | 0<br>A28   | 0.120<br>()<br>A31 | VDDL       |            |            |            |                        |               |            | •            | А       |

| 19        | 18        | 17        | 16        | 15                     | 14                     | 13         | 12         | 11                        | 10         | 9                  | 8          | 7          | 6          | 5          | 4                      | 3             | 2          | 1            | ١       |

**NOTE:** This is the top view of the device.

Figure 76. Pinout of the PBGA Package