#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                                            |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0, ARM® Cortex®-M4                                                                    |

| Core Size                  | 32-Bit Dual-Core                                                                                    |

| Speed                      | 204MHz                                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, MMC/SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 83                                                                                                  |

| Program Memory Size        | -                                                                                                   |

| Program Memory Type        | ROMIess                                                                                             |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 200K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                         |

| Data Converters            | A/D 8x10b SAR; D/A 1x10b                                                                            |

| Oscillator Type            | External, Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 144-LQFP                                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc43s20fbd144e                             |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                                                                                                                                              |

|--------|---------|----------|----------|---------|-----|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3_4   | A15     | C14      | B8       | 119     | [2] | N;          | I/O  | GPIO1[14] — General purpose digital input/output pin.                                                                                                                                    |

|        |         |          |          |         |     | PU          | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | I/O  | SPIFI_SIO3 — I/O lane 3 for SPIFI.                                                                                                                                                       |

|        |         |          |          |         |     |             | 0    | U1_TXD — Transmitter output for UART 1.                                                                                                                                                  |

|        |         |          |          |         |     |             | I/O  | <b>I2S0_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification.                             |

|        |         |          |          |         |     |             | I/O  | <b>I2S1_RX_SDA</b> — I2S1 Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> S-bus specification.         |

|        |         |          |          |         |     |             | 0    | LCD_VD13 — LCD data.                                                                                                                                                                     |

| P3_5   | C12     | C11      | B7       | 121     | [2] | N;          | I/O  | GPIO1[15] — General purpose digital input/output pin.                                                                                                                                    |

|        |         |          |          |         |     | PU          | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | I/O  | SPIFI_SIO2 — I/O lane 2 for SPIFI.                                                                                                                                                       |

|        |         |          |          |         |     |             | I    | U1_RXD — Receiver input for UART 1.                                                                                                                                                      |

|        |         |          |          |         |     |             | I/O  | <b>I2S0_TX_SDA</b> — I2S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification. |

|        |         |          |          |         |     |             | I/O  | <b>I2S1_RX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification.                              |

|        |         |          |          |         |     |             | 0    | LCD_VD12 — LCD data.                                                                                                                                                                     |

| P3_6   | B13     | B12      | C7       | 122     | [2] | N;          | I/O  | GPIO0[6] — General purpose digital input/output pin.                                                                                                                                     |

|        |         |          |          |         |     | PU          | I/O  | SPI_MISO — Master In Slave Out for SPI.                                                                                                                                                  |

|        |         |          |          |         |     |             | I/O  | SSP0_SSEL — Slave Select for SSP0.                                                                                                                                                       |

|        |         |          |          |         |     |             | I/O  | SPIFI_MISO — Input 1 in SPIFI quad mode; SPIFI output IO1.                                                                                                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | I/O  | SSP0_MISO — Master In Slave Out for SSP0.                                                                                                                                                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

| P3_7   | C11     | C10      | D7       | 123     | [2] | N;          | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     | PU          | I/O  | SPI_MOSI — Master Out Slave In for SPI.                                                                                                                                                  |

|        |         |          |          |         |     |             | I/O  | SSP0_MISO — Master In Slave Out for SSP0.                                                                                                                                                |

|        |         |          |          |         |     |             | I/O  | SPIFI_MOSI — Input I0 in SPIFI quad mode; SPIFI output IO0.                                                                                                                              |

|        |         |          |          |         |     |             | I/O  | GPIO5[10] — General purpose digital input/output pin.                                                                                                                                    |

|        |         |          |          |         |     |             | I/O  | SSP0_MOSI — Master Out Slave in for SSP0.                                                                                                                                                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

Product data sheet

LPC43S50\_S30\_S20

All information provided in this document is subject to legal disclaimers.

## 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                                                                                                                                                               |

|--------|---------|----------|----------|---------|-----|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P9_6   | L11     | M9       | -        | 72      | [2] | N;          | I/O  | GPIO4[11] — General purpose digital input/output pin.                                                                                                                                                     |

|        |         |          |          |         |     | PU          | 0    | MCOB1 — Motor control PWM channel 1, output B.                                                                                                                                                            |

|        |         |          |          |         |     |             | 1    | <b>USB1_PWR_FAULT</b> — USB1 Port power fault signal indicating over-current condition; this signal monitors over-current on the USB1 bus (external circuitry required to detect over-current condition). |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | I    | <b>ENET_COL</b> — Ethernet Collision detect (MII interface).                                                                                                                                              |

|        |         |          |          |         |     |             | I/O  | SGPIO8 — General purpose digital input/output pin.                                                                                                                                                        |

|        |         |          |          |         |     |             | I    | U0_RXD — Receiver input for USART0.                                                                                                                                                                       |

| PA_0   | L12     | L10      | -        | -       | [2] | N;          | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     | PU          | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | 0    | I2S1_RX_MCLK — I2S1 receive master clock.                                                                                                                                                                 |

|        |         |          |          |         |     |             | 0    | CGU_OUT1 — CGU spare clock output 1.                                                                                                                                                                      |

|        |         |          |          |         |     | 701         | -    | R — Function reserved.                                                                                                                                                                                    |

| PA_1   | J14     | H12      | -        | -       | [3] | N;          | I/O  | GPIO4[8] — General purpose digital input/output pin.                                                                                                                                                      |

|        |         |          |          |         |     | PU          | I    | <b>QEI_IDX</b> — Quadrature Encoder Interface INDEX input.                                                                                                                                                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | 0    | U2_TXD — Transmitter output for USART2.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

| PA_2   | K15     | J13      | -        | -       | [3] | N;          | I/O  | GPIO4[9] — General purpose digital input/output pin.                                                                                                                                                      |

|        |         |          |          |         |     | PU          | I    | <b>QEI_PHB</b> — Quadrature Encoder Interface PHB input.                                                                                                                                                  |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | I    | U2_RXD — Receiver input for USART2.                                                                                                                                                                       |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                                    |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

## 32-bit ARM Cortex-M4/M0 microcontroller

|        | ISB0, a | nd USI   | B1 fun   | ctions  | are | not ava            | ailabl | e on all parts. See <u>Table 2</u> .                                                                                                                                  |

|--------|---------|----------|----------|---------|-----|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type   | Description                                                                                                                                                           |

| PC_3   | F5      | -        | -        | -       | [5] | N;                 | I/O    | <b>USB1_ULPI_D5</b> — ULPI link bidirectional data line 5.                                                                                                            |

|        |         |          |          |         |     | PU                 | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    | 0      | <b>U1_RTS</b> — Request to Send output for UART 1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART 1.                                    |

|        |         |          |          |         |     |                    | 0      | ENET_TXD3 — Ethernet transmit data 3 (MII interface).                                                                                                                 |

|        |         |          |          |         |     |                    | I/O    | GPIO6[2] — General purpose digital input/output pin.                                                                                                                  |

|        |         |          |          |         |     |                    | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    | 0      | <b>SD_VOLT1</b> — SD/MMC bus voltage select output 1.                                                                                                                 |

|        |         |          |          |         |     |                    | AI     | <b>ADC1_0</b> — DAC output; ADC1 and ADC0, input channel 0.<br>Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

| PC_4   | F4      | -        | -        | -       | [2] | N;                 | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     | PU                 | I/O    | USB1_ULPI_D4 — ULPI link bidirectional data line 4.                                                                                                                   |

|        |         |          |          |         |     |                    | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    |        | <b>ENET_TX_EN</b> — Ethernet transmit enable (RMII/MII interface).                                                                                                    |

|        |         |          |          |         |     |                    | I/O    | <b>GPIO6[3]</b> — General purpose digital input/output pin.                                                                                                           |

|        |         |          |          |         |     |                    | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    | I      | T3_CAP1 — Capture input 1 of timer 3.                                                                                                                                 |

|        |         |          |          |         |     |                    | I/O    | <b>SD_DAT0</b> — SD/MMC data bus line 0.                                                                                                                              |

| PC_5   | G4      | -        | -        | -       | [2] | N;                 | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     | PU                 | I/O    | <b>USB1_ULPI_D3</b> — ULPI link bidirectional data line 3.                                                                                                            |

|        |         |          |          |         |     |                    | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    | 0      | <b>ENET_TX_ER</b> — Ethernet Transmit Error (MII interface).                                                                                                          |

|        |         |          |          |         |     |                    | I/O    | <b>GPIO6[4]</b> — General purpose digital input/output pin.                                                                                                           |

|        |         |          |          |         |     |                    | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    | I      | T3_CAP2 — Capture input 2 of timer 3.                                                                                                                                 |

|        |         |          |          |         |     |                    | I/O    | SD_DAT1 — SD/MMC data bus line 1.                                                                                                                                     |

| PC_6   | H6      | -        | -        | -       | [2] | N;<br>PU           | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     | FU                 | I/O    | USB1_ULPI_D2 — ULPI link bidirectional data line 2.                                                                                                                   |

|        |         |          |          |         |     |                    | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    |        | <b>ENET_RXD2</b> — Ethernet receive data 2 (MII interface).                                                                                                           |

|        |         |          |          |         |     |                    | I/O    | <b>GPIO6[5]</b> — General purpose digital input/output pin.                                                                                                           |

|        |         |          |          |         |     |                    | -      | R — Function reserved.                                                                                                                                                |

|        |         |          |          |         |     |                    |        | T3_CAP3 — Capture input 3 of timer 3.                                                                                                                                 |

|        |         |          |          |         |     |                    | I/O    | <b>SD_DAT2</b> — SD/MMC data bus line 2.                                                                                                                              |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                          |

|--------|---------|----------|----------|---------|-----|-------------|------|----------------------------------------------------------------------|

| PD_0   | N2      | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_15</b> — SCTimer/PWM output 15. Match output 3 of timer 3.  |

|        |         |          |          |         |     |             | 0    | <b>EMC_DQMOUT2</b> — Data mask 2 used with SDRAM and static devices. |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | GPIO6[14] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | SGPIO4 — General purpose digital input/output pin.                   |

| PD_1   | P1      | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     | PU          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | 0    | EMC_CKEOUT2 — SDRAM clock enable 2.                                  |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | GPIO6[15] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |             | 0    | <b>SD_POW</b> — SD/MMC power monitor output.                         |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | SGPI05 — General purpose digital input/output pin.                   |

| PD_2   | R1      | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_7</b> — SCTimer/PWM output 7. Match output 3 of timer 1.    |

|        |         |          |          |         |     |             | I/O  | EMC_D16 — External memory data line 16.                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | GPIO6[16] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | SGPIO6 — General purpose digital input/output pin.                   |

| PD_3   | P4      | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_6</b> — SCTimer/PWM output 7. Match output 2 of timer 1.    |

|        |         |          |          |         |     |             | I/O  | EMC_D17 — External memory data line 17.                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | GPIO6[17] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | SGPI07 — General purpose digital input/output pin.                   |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

## 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |                                | Reset state | Type     | Description                                                                                                                                                                       |

|--------|---------|----------|----------|---------|--------------------------------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PF_6   | E7      | -        | -        | -       | [5]                            | N;          | -        | R — Function reserved.                                                                                                                                                            |

|        |         |          |          |         |                                | PU          | I/O      | <b>U3_DIR</b> — RS-485/EIA-485 output enable/direction control for USART3.                                                                                                        |

|        |         |          |          |         |                                |             | I/O      | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                         |

|        |         |          |          |         |                                |             | 0        | TRACEDATA[1] — Trace data, bit 1.                                                                                                                                                 |

|        |         |          |          |         |                                |             | I/O      | GPI07[20] — General purpose digital input/output pin.                                                                                                                             |

|        |         |          |          |         |                                |             | -        | R — Function reserved.                                                                                                                                                            |

|        |         |          |          |         |                                |             | I/O      | SGPIO5 — General purpose digital input/output pin.                                                                                                                                |

|        |         |          |          |         |                                |             | I/O      | <b>I2S1_TX_SDA</b> — I2S1 transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> S-bus specification. |

|        |         |          |          |         |                                |             | AI       | <b>ADC1_3</b> — ADC1 and ADC0, input channel 3. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.                            |

| PF_7   | B7      | -        | -        | -       | [5]                            | N;          | -        | R — Function reserved.                                                                                                                                                            |

|        | PU      |          | PU       | I/O     | U3_BAUD — Baud pin for USART3. |             |          |                                                                                                                                                                                   |

|        |         |          |          |         |                                |             | I/O      | SSP1_MOSI — Master Out Slave in for SSP1.                                                                                                                                         |

|        |         |          |          |         |                                |             | 0        | TRACEDATA[2] — Trace data, bit 2.                                                                                                                                                 |

|        |         |          |          |         |                                |             | I/O      | GPI07[21] — General purpose digital input/output pin.                                                                                                                             |

|        |         |          |          |         |                                |             | -        | R — Function reserved.                                                                                                                                                            |

|        |         |          |          |         |                                |             | I/O      | SGPIO6 — General purpose digital input/output pin.                                                                                                                                |

|        |         |          |          |         |                                |             | I/O      | <b>I2S1_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $\beta$ S-bus specification.                  |

|        |         |          |          |         |                                |             | Al/<br>O | <b>ADC1_7</b> — ADC1 and ADC0, input channel 7 or band gap output. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.         |

| PF_8   | E6      | -        | -        | -       | [5]                            | N;          | -        | R — Function reserved.                                                                                                                                                            |

|        |         |          |          |         |                                | PU          | I/O      | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                                        |

|        |         |          |          |         |                                |             | I        | CTIN_2 — SCTimer/PWM input 2. Capture input 2 of timer 0.                                                                                                                         |

|        |         |          |          |         |                                |             | 0        | TRACEDATA[3] — Trace data, bit 3.                                                                                                                                                 |

|        |         |          |          |         |                                |             | I/O      | GPI07[22] — General purpose digital input/output pin.                                                                                                                             |

|        |         |          |          |         |                                |             | -        | R — Function reserved.                                                                                                                                                            |

|        |         |          |          |         |                                |             | I/O      | SGPI07 — General purpose digital input/output pin.                                                                                                                                |

|        |         |          |          |         |                                |             | -        | R — Function reserved.                                                                                                                                                            |

|        |         |          |          |         |                                |             | AI       | <b>ADC0_2</b> — ADC0 and ADC1, input channel 2. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.                            |

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

## 32-bit ARM Cortex-M4/M0 microcontroller

### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

| Symbol     | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                                                                                                                        |

|------------|---------|----------|----------|---------|-----|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock pins |         |          |          |         |     |             |      |                                                                                                                                                                    |

| CLK0       | N5      | M4       | K3       | 45      | [4] | О;          | 0    | EMC_CLK0 — SDRAM clock 0.                                                                                                                                          |

|            |         |          |          |         |     | PU          | 0    | CLKOUT — Clock output pin.                                                                                                                                         |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | I/O  | SD_CLK — SD/MMC card clock.                                                                                                                                        |

|            |         |          |          |         |     |             | 0    | <b>EMC_CLK01</b> — SDRAM clock 0 and clock 1 combined.                                                                                                             |

|            |         |          |          |         |     |             | I/O  | SSP1_SCK — Serial clock for SSP1.                                                                                                                                  |

|            |         |          |          |         |     |             | I    | <b>ENET_TX_CLK (ENET_REF_CLK)</b> — Ethernet Transmit<br>Clock (MII interface) or Ethernet Reference Clock (RMII<br>interface).                                    |

| CLK1       | T10     | -        | -        | -       | [4] | О;          | 0    | EMC_CLK1 — SDRAM clock 1.                                                                                                                                          |

|            |         |          |          |         |     | PU          | 0    | CLKOUT — Clock output pin.                                                                                                                                         |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | 0    | CGU_OUT0 — CGU spare clock output 0.                                                                                                                               |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | 0    | I2S1_TX_MCLK — I2S1 transmit master clock.                                                                                                                         |

| CLK2       | D14     | P10      | K6       | 99      | [4] | O;          | 0    | EMC_CLK3 — SDRAM clock 3.                                                                                                                                          |

|            |         |          |          |         |     | PU          | 0    | CLKOUT — Clock output pin.                                                                                                                                         |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | I/O  | SD_CLK — SD/MMC card clock.                                                                                                                                        |

|            |         |          |          |         |     |             | 0    | <b>EMC_CLK23</b> — SDRAM clock 2 and clock 3 combined.                                                                                                             |

|            |         |          |          |         |     |             | 0    | I2S0_TX_MCLK — I2S transmit master clock.                                                                                                                          |

|            |         |          |          |         |     |             | I/O  | <b>I2S1_RX_SCK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the I <sup>2</sup> S-bus specification. |

| CLK3       | P12     | -        | -        | -       | [4] | О;          | 0    | EMC_CLK2 — SDRAM clock 2.                                                                                                                                          |

|            |         |          |          |         |     | PU          | 0    | CLKOUT — Clock output pin.                                                                                                                                         |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | 0    | CGU_OUT1 — CGU spare clock output 1.                                                                                                                               |

|            |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                             |

|            |         |          |          |         |     |             | I/O  | <b>I2S1_RX_SCK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the I <sup>2</sup> S-bus specification. |

### 32-bit ARM Cortex-M4/M0 microcontroller

## 7.6.1 Features

- Controls system exceptions and peripheral interrupts.

- The Cortex-M4 NVIC supports up to 53 vectored interrupts.

- Eight programmable interrupt priority levels with hardware priority level masking.

- Relocatable vector table.

- Non-Maskable Interrupt (NMI).

- Software interrupt generation.

## 7.6.2 Interrupt sources

Each peripheral device has one interrupt line connected to the NVIC but may have several interrupt flags. Individual interrupt flags can represent more than one interrupt source.

## 7.7 System Tick timer (SysTick)

The ARM Cortex-M4 includes a system tick timer (SysTick) that is intended to generate a dedicated SYSTICK exception at a 10 ms interval.

Remark: The SysTick is not included in the ARM Cortex-M0 core.

## 7.8 Event router

The event router combines various internal signals, interrupts, and the external interrupt pins (WAKEUP[3:0]) to create an interrupt in the NVIC, if enabled. In addition, the event router creates a wake-up signal to the ARM core and the CCU for waking up from Sleep, Deep-sleep, Power-down, and Deep power-down modes. Individual events can be configured as edge or level sensitive and can be enabled or disabled in the event router. The event router can be battery powered.

The following events if enabled in the event router can create a wake-up signal from sleep, deep-sleep, power-down, and deep power-down modes and/or create an interrupt:

- External pins WAKEUP0/1/2/3 and RESET

- Alarm timer, RTC (32 kHz oscillator running)

The following events if enabled in the event router can create a wake-up signal from sleep mode only and/or create an interrupt:

- WWDT, BOD interrupts

- C\_CAN0/1 and QEI interrupts

- Ethernet, USB0, USB1 signals

- Selected outputs of combined timers (SCTimer/PWM and timer0/1/3)

**Remark:** Any interrupt can wake up the ARM Cortex-M4 from sleep mode if enabled in the NVIC.

## 7.9 Global Input Multiplexer Array (GIMA)

The GIMA routes signals to event-driven peripheral targets like the SCTimer/PWM, timers, event router, or the ADCs.

LPC43S50 S30 S20

## 32-bit ARM Cortex-M4/M0 microcontroller

## 7.18.5 I<sup>2</sup>C-bus interface

Remark: The LPC43S50/S30/S20 contain two I<sup>2</sup>C-bus interfaces.

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock line (SCL) and a Serial Data line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (for example an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

## 7.18.5.1 Features

- I<sup>2</sup>C0 is a standard I<sup>2</sup>C-compliant bus interface with open-drain pins. I<sup>2</sup>C0 also supports Fast mode plus with bit rates up to 1 Mbit/s.

- I<sup>2</sup>C1 uses standard I/O pins with bit rates of up to 400 kbit/s (Fast I<sup>2</sup>C-bus).

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- All I<sup>2</sup>C-bus controllers support multiple address recognition and a bus monitor mode.

## 7.18.6 I<sup>2</sup>S interface

**Remark:** The LPC43S50/S30/S20 contain two I<sup>2</sup>S-bus interfaces.

The I<sup>2</sup>S-bus provides a standard communication interface for digital audio applications.

The  $l^2S$ -bus specification defines a 3-wire serial bus using one data line, one clock line, and one word select signal. The basic  $l^2S$ -bus connection has one master, which is always the master, and one slave. The  $l^2S$ -bus interface provides a separate transmit and receive channel, each of which can operate as either a master or a slave.

### 7.18.6.1 Features

- The I<sup>2</sup>S interface has separate input/output channels, each of which can operate in master or slave mode.

- Capable of handling 8-bit, 16-bit, and 32-bit word sizes.

- Mono and stereo audio data supported.

- The sampling frequency can range from 16 kHz to 192 kHz (16, 22.05, 32, 44.1, 48, 96, 192) kHz.

- Support for an audio master clock.

32-bit ARM Cortex-M4/M0 microcontroller

## 10. Static characteristics

## Table 10. Static characteristics

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.

| Symbol                     | Parameter                        | Conditions                                                                                       |               | Min | Typ <u>[1]</u> | Max | Unit |

|----------------------------|----------------------------------|--------------------------------------------------------------------------------------------------|---------------|-----|----------------|-----|------|

| Supply pins                |                                  |                                                                                                  |               |     |                |     |      |

| V <sub>DD(IO)</sub>        | input/output supply voltage      |                                                                                                  |               | 2.2 | -              | 3.6 | V    |

| V <sub>DD(REG)(3V3)</sub>  | regulator supply voltage (3.3 V) |                                                                                                  | [2]           | 2.2 | -              | 3.6 | V    |

| V <sub>DDA(3V3)</sub>      | analog supply voltage            | on pin VDDA                                                                                      |               | 2.2 | -              | 3.6 | V    |

|                            | (3.3 V)                          | on pins<br>USB0_VDDA3V3_<br>DRIVER and<br>USB0_VDDA3V3                                           |               | 3.0 | 3.3            | 3.6 | V    |

| V <sub>BAT</sub>           | battery supply voltage           |                                                                                                  | [2]           | 2.2 | -              | 3.6 | V    |

| V <sub>prog(pf)</sub>      | polyfuse programming voltage     | on pin VPP (for OTP)                                                                             | [3]           | 2.7 | -              | 3.6 | V    |

| I <sub>prog(pf)</sub>      | polyfuse programming<br>current  | on pin VPP; OTP<br>programming time ≤<br>1.6 ms                                                  |               | -   | -              | 30  | mA   |

| I <sub>DD(REG)</sub> (3V3) | regulator supply current (3.3 V) | Active mode; M0-core in reset; code                                                              |               |     |                |     |      |

|                            |                                  | while(1){}                                                                                       |               |     |                |     |      |

|                            |                                  | executed from RAM; all<br>peripherals disabled;<br>PLL1 enabled                                  |               |     |                |     |      |

|                            |                                  | CCLK = 12 MHz                                                                                    | [4]           | -   | 6.6            | -   | mA   |

|                            |                                  | CCLK = 60 MHz                                                                                    | [4]           |     | 25.3           | -   | mA   |

|                            |                                  | CCLK = 120 MHz                                                                                   | [4]           | -   | 48.4           | -   | mA   |

|                            |                                  | CCLK = 180 MHz                                                                                   | [4]           | -   | 72.0           | -   | mA   |

|                            |                                  | CCLK = 204 MHz                                                                                   | [4]           | -   | 81.5           | -   | mA   |

| I <sub>DD(REG)(3V3)</sub>  | regulator supply current (3.3 V) | after WFE/WFI instruction<br>executed from RAM; all<br>peripherals disabled; M0<br>core in reset |               |     |                |     |      |

|                            |                                  | sleep mode                                                                                       | [4][5]        | -   | 5.0            | -   | mA   |

|                            |                                  | deep-sleep mode                                                                                  | [4]           | -   | 30             | -   | μA   |

|                            |                                  | power-down mode                                                                                  | [4]           | -   | 15             | -   | μA   |

|                            |                                  | deep power-down<br>mode                                                                          | <u>[4][6]</u> | -   | 0.03           | -   | μΑ   |

|                            |                                  | deep power-down<br>mode; VBAT floating                                                           | <u>[4]</u> _  | -   | 2              | -   | μΑ   |

| I <sub>BAT</sub>           | battery supply current           | active mode; $V_{BAT} = 3.2 V$ ;<br>$V_{DD(REG)(3V3)} = 3.6 V$ .                                 | <u>[7]</u>    | -   | 0              | -   | nA   |

## 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol                   | Parameter                                                                   | Conditions                                           |      | Min  | Typ <u>[1]</u> | Max  | Unit |

|--------------------------|-----------------------------------------------------------------------------|------------------------------------------------------|------|------|----------------|------|------|

| ILI                      | input leakage current                                                       | $V_{I} = V_{DD(IO)}$                                 | [13] | -    | 4.5            | -    | μA   |

|                          |                                                                             | V <sub>I</sub> = 5 V                                 |      | -    | -              | 10   | μA   |

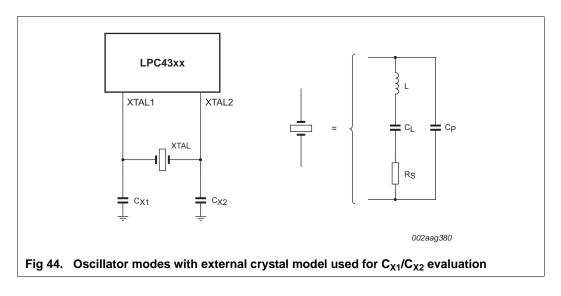

| Oscillator pi            | ns                                                                          |                                                      |      | 1    |                |      |      |

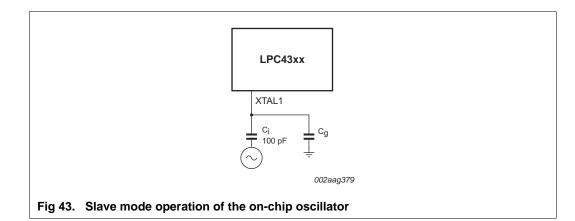

| V <sub>i(XTAL1)</sub>    | input voltage on pin<br>XTAL1                                               |                                                      |      | -0.5 | -              | 1.2  | V    |

| V <sub>o(XTAL2)</sub>    | output voltage on pin<br>XTAL2                                              |                                                      |      | -0.5 | -              | 1.2  | V    |

| C <sub>io</sub>          | input/output<br>capacitance                                                 |                                                      | [17] | -    | -              | 0.8  | pF   |

| USB0 pins <sup>[1]</sup> | 8]                                                                          |                                                      |      | 1    |                | L    |      |

| VI                       | input voltage                                                               | on pins USB0_DP;<br>USB0_DM; USB0_VBUS               |      |      |                |      |      |

|                          |                                                                             | $V_{DD(IO)} \ge 2.2 \text{ V}$                       |      | 0    | -              | 5.25 | V    |

|                          |                                                                             | $V_{DD(IO)} = 0 V$                                   |      | 0    | -              | 3.6  | V    |

| R <sub>pd</sub>          | pull-down resistance                                                        | on pin USB0_VBUS                                     |      | 48   | 64             | 80   | kΩ   |

| V <sub>IC</sub>          | common-mode input                                                           | high-speed mode                                      |      | -50  | 200            | 500  | mV   |

|                          | voltage                                                                     | full-speed/low-speed<br>mode                         |      | 800  | -              | 2500 | mV   |

|                          |                                                                             | chirp mode                                           |      | -50  | -              | 600  | mV   |

| V <sub>i(dif)</sub>      | differential input voltage                                                  |                                                      |      | 100  | 400            | 1100 | mV   |

| USB1 pins (              | USB1_DP/USB1_DM) <sup>[18]</sup>                                            |                                                      |      | 1    |                | I    |      |

| I <sub>OZ</sub>          | OFF-state output current                                                    | 0 V < V <sub>I</sub> < 3.3 V                         | [18] | -    | -              | ±10  | μΑ   |

| V <sub>BUS</sub>         | bus supply voltage                                                          |                                                      | [19] | -    | -              | 5.25 | V    |

| V <sub>DI</sub>          | differential input sensitivity voltage                                      | (D+) - (D-)                                          |      | 0.2  | -              | -    | V    |

| V <sub>CM</sub>          | differential common<br>mode voltage range                                   | includes V <sub>DI</sub> range                       |      | 0.8  | -              | 2.5  | V    |

| V <sub>th(rs)se</sub>    | single-ended receiver<br>switching threshold<br>voltage                     |                                                      |      | 0.8  | -              | 2.0  | V    |

| V <sub>OL</sub>          | LOW-level output<br>voltage for<br>low-/full-speed                          | $R_L$ of 1.5 k $\Omega$ to 3.6 V                     |      | -    | -              | 0.18 | V    |

| V <sub>OH</sub>          | HIGH-level output<br>voltage (driven) for<br>low-/full-speed                | $R_L$ of 15 k $\Omega$ to GND                        |      | 2.8  | -              | 3.5  | V    |

| C <sub>trans</sub>       | transceiver capacitance                                                     | pin to GND                                           |      | -    | -              | 20   | pF   |

| Z <sub>DRV</sub>         | driver output<br>impedance for driver<br>which is not high-speed<br>capable | with 33 $\Omega$ series resistor; steady state drive | [20] | 36   | -              | 44.1 | Ω    |

## Table 10. Static characteristics ...continued T 10 % to : 25 % unloss otherwise appointed

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

The recommended operating condition for the battery supply is  $V_{DD(REG)(3V3)} > V_{BAT} + 0.2$  V. See Figure 18. [2]

LPC43S50\_S30\_S20 Product data sheet

94 of 156

## 32-bit ARM Cortex-M4/M0 microcontroller

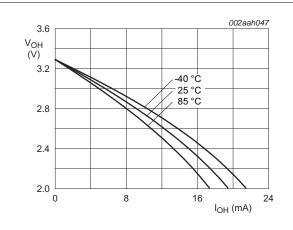

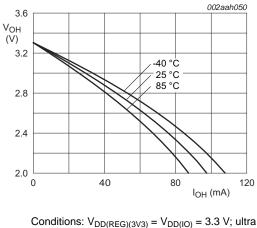

Conditions:  $V_{DD(REG)(3V3)} = V_{DD(IO)} = 3.3 V$ ; normal-drive; EHD = 0x0.

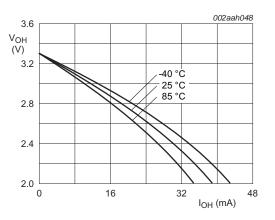

$\label{eq:conditions: V_DD(REG)(3V3)} \mbox{ = } V_{DD(IO)} \mbox{ = } 3.3 \mbox{ V;} \\ medium-drive; \mbox{ EHD} \mbox{ = } 0x1. \\ \end{tabular}$

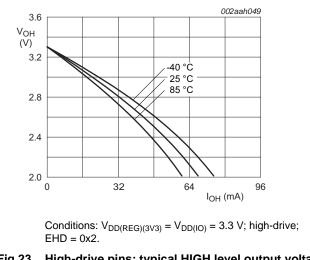

Conditions:  $V_{DD(REG)(3V3)} = V_{DD(IO)} = 3.3$  V; ultra high-drive; EHD = 0x3.

## 32-bit ARM Cortex-M4/M0 microcontroller

## 11.11 SSP interface

### Table 24. Dynamic characteristics: SSP pins in SPI mode

$T_{amb} = -40$  °C to +85 °C; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V;  $C_L = 20$  pF. Sampled at 10 % and 90 % of the signal level; EHS = 1 for all pins. Simulated values.

| Symbol               | Parameter                 | Conditions                                                  |     | Min                            | Тур | Max                           | Unit |

|----------------------|---------------------------|-------------------------------------------------------------|-----|--------------------------------|-----|-------------------------------|------|

| SSP mas              | ter                       |                                                             |     |                                |     |                               |      |

| T <sub>cy(clk)</sub> | clock cycle time          | full-duplex mode                                            | [1] | $1/(25.5 \times 10^{6})$       | -   | -                             | s    |

|                      |                           | when only transmitting                                      |     | 1/(51 × 10 <sup>6</sup> )      | -   | -                             | s    |

| t <sub>DS</sub>      | data set-up time          | in SPI mode                                                 |     | 13.6                           | -   | -                             | ns   |

| t <sub>DH</sub>      | data hold time            | in SPI mode                                                 |     | -3.8                           | -   | -                             | ns   |

| t <sub>v(Q)</sub>    | data output valid<br>time | in SPI mode                                                 |     | -                              | -   | 6.0                           | ns   |

| t <sub>h(Q)</sub>    | data output hold<br>time  | in SPI mode                                                 |     | -1.1                           | -   | -                             | ns   |

| t <sub>lead</sub>    | lead time                 | continuous transfer mode<br>SPI mode; CPOL = 0;<br>CPHA = 0 |     | $T_{cy(clk)}$ + 3.2            | -   | T <sub>cy(clk)</sub> + 6.1    | ns   |

|                      |                           | SPI mode; CPOL = 0;<br>CPHA = 1                             |     | $0.5 	imes T_{cy(clk)}$ + 3.2  | -   | $0.5 	imes T_{cy(clk)}$ + 6.1 | ns   |

|                      |                           | SPI mode; CPOL = 1;<br>CPHA = 0                             |     | T <sub>cy(clk)</sub> + 3.2     | -   | T <sub>cy(clk)</sub> + 6.1    | ns   |

|                      |                           | SPI mode; CPOL = 1;<br>CPHA = 1                             |     | $0.5 \times T_{cy(clk)} + 3.2$ | -   | $0.5 	imes T_{cy(clk)}$ + 6.1 | ns   |

|                      |                           | synchronous serial<br>frame mode                            |     | $0.5 \times T_{cy(clk)} + 3.2$ | -   | $0.5 	imes T_{cy(clk)}$ + 6.1 | ns   |

|                      |                           | microwire frame format                                      |     | $T_{cy(clk)}$ + 3.2            | -   | T <sub>cy(clk)</sub> + 6.1    | ns   |

| t <sub>lag</sub>     | lag time                  | continuous transfer mode<br>SPI mode; CPOL = 0;<br>CPHA = 0 |     | $0.5 	imes T_{cy(clk)}$        | -   | -                             | ns   |

|                      |                           | SPI mode; CPOL = 0;<br>CPHA = 1                             |     | T <sub>cy(clk)</sub>           | -   | -                             | ns   |

|                      |                           | SPI mode; CPOL = 1;<br>CPHA = 0                             |     | $0.5 \times T_{cy(clk)}$       | -   | -                             | ns   |

|                      |                           | SPI mode; CPOL = 1;<br>CPHA = 1                             |     | T <sub>cy(clk)</sub>           | -   | -                             | ns   |

|                      |                           | synchronous serial<br>frame mode                            |     | T <sub>cy(clk)</sub>           | -   | -                             | ns   |

|                      |                           | microwire frame format                                      |     | $0.5 	imes T_{cy(clk)}$        | -   | -                             | ns   |

## 32-bit ARM Cortex-M4/M0 microcontroller

## 11.12 SPI interface

### Table 25. Dynamic characteristics: SPI

$T_{amb} = -40$  °C to +85 °C; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V. Simulated values.

| Symbol                | Parameter              | Conditions |     | Min                              | Тур | Max                             | Unit |

|-----------------------|------------------------|------------|-----|----------------------------------|-----|---------------------------------|------|

| T <sub>cy(PCLK)</sub> | PCLK cycle time        |            |     | 5                                |     |                                 | ns   |

| T <sub>cy(clk)</sub>  | clock cycle time       |            | [1] | 40                               | -   | -                               | ns   |

| Master                |                        |            |     |                                  |     |                                 |      |

| t <sub>DS</sub>       | data set-up time       |            |     | 7.2                              | -   | -                               | ns   |

| t <sub>DH</sub>       | data hold time         |            |     | 0                                | -   | -                               | ns   |