Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                                    |

|----------------------------|-----------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M0                                                                                        |

| Core Size                  | 32-Bit Dual-Core                                                                                          |

| Speed                      | 204MHz                                                                                                    |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, Motor Control PWM, POR, PWM, WDT                                        |

| Number of I/O              | 83                                                                                                        |

| Program Memory Size        | ·                                                                                                         |

| Program Memory Type        | ROMIess                                                                                                   |

| EEPROM Size                | -                                                                                                         |

| RAM Size                   | 264K x 8                                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                               |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                      |

| Oscillator Type            | Internal                                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                         |

| Mounting Type              | Surface Mount                                                                                             |

| Package / Case             | 144-LQFP                                                                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc43s30fbd144e                                   |

|                            |                                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                                                                                                                                                        |

|--------|---------|----------|----------|---------|-----|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2_2   | M15     | L13      | F5       | 84      | [2] | N;          | I/O  | <b>SGPIO6</b> — General purpose digital input/output pin.                                                                                                                                          |

|        |         |          |          |         |     | PU          | I/O  | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                                                         |

|        |         |          |          |         |     |             | I/O  | EMC_A11 — External memory address line 11.                                                                                                                                                         |

|        |         |          |          |         |     |             | 0    | <b>USB0_IND1</b> — USB0 port indicator LED control output 1.                                                                                                                                       |

|        |         |          |          |         |     |             | I/O  | <b>GPIO5[2]</b> — General purpose digital input/output pin.                                                                                                                                        |

|        |         |          |          |         |     |             | I    | <b>CTIN_6</b> — SCTimer/PWM input 6. Capture input 1 of timer 3.                                                                                                                                   |

|        |         |          |          |         |     |             | I    | T3_CAP2 — Capture input 2 of timer 3.                                                                                                                                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                             |

| P2_3   | J12     | G11      | D8       | 87      | [3] | N;          | I/O  | SGPI012 — General purpose digital input/output pin.                                                                                                                                                |

|        |         |          |          |         |     | PU          | I/O  | <b>I2C1_SDA</b> — I <sup>2</sup> C1 data input/output (this pin does not use a specialized I2C pad).                                                                                               |

|        |         |          |          |         |     |             | 0    | U3_TXD — Transmitter output for USART3.                                                                                                                                                            |

|        |         |          |          |         |     |             | I    | <b>CTIN_1</b> — SCTimer/PWM input 1. Capture input 1 of timer 0. Capture input 1 of timer 2.                                                                                                       |

|        |         |          |          |         |     |             | I/O  | GPIO5[3] — General purpose digital input/output pin.                                                                                                                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |             | 0    | T3_MAT0 — Match output 0 of timer 3.                                                                                                                                                               |

|        |         |          |          |         |     |             | 0    | <b>USB0_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active HIGH).                                                    |

|        |         |          |          |         |     |             |      | Add a pull-down resistor to disable the power switch at reset.<br>This signal has opposite polarity compared to the USB_PPWR<br>used on other NXP LPC parts.                                       |

| P2_4   | K11     | L9       | D9       | 88      | [3] | N;          | I/O  | SGPI013 — General purpose digital input/output pin.                                                                                                                                                |

|        |         |          |          |         |     | PU          | I/O  | <b>I2C1_SCL</b> — I <sup>2</sup> C1 clock input/output (this pin does not use a specialized I2C pad).                                                                                              |

|        |         |          |          |         |     |             | I    | U3_RXD — Receiver input for USART3.                                                                                                                                                                |

|        |         |          |          |         |     |             | I    | <b>CTIN_0</b> — SCTimer/PWM input 0. Capture input 0 of timer 0, 1, 2, 3.                                                                                                                          |

|        |         |          |          |         |     |             | I/O  | GPIO5[4] — General purpose digital input/output pin.                                                                                                                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                             |

|        |         |          |          |         |     |             | 0    | T3_MAT1 — Match output 1 of timer 3.                                                                                                                                                               |

|        |         |          |          |         |     |             | I    | <b>USB0_PWR_FAULT</b> — Port power fault signal indicating overcurrent condition; this signal monitors over-current on the USB bus (external circuitry required to detect over-current condition). |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                            |  |  |  |  |

|--------|---------|----------|----------|---------|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P2_5   | K14     | J12      | D10      | 91      | [3] | N;                 | I/O  | SGPI014 — General purpose digital input/output pin.                                                                                    |  |  |  |  |

|        |         |          |          |         |     | PU                 | I    | CTIN_2 — SCTimer/PWM input 2. Capture input 2 of timer 0.                                                                              |  |  |  |  |

|        |         |          |          |         |     |                    | I    | <b>USB1_VBUS</b> — Monitors the presence of USB1 bus power.                                                                            |  |  |  |  |

|        |         |          |          |         |     |                    |      | Note: This signal must be HIGH for USB reset to occur.                                                                                 |  |  |  |  |

|        |         |          |          |         |     |                    | I    | ADCTRIG1 — ADC trigger input 1.                                                                                                        |  |  |  |  |

|        |         |          |          |         |     |                    | I/O  | <b>GPIO5[5]</b> — General purpose digital input/output pin.                                                                            |  |  |  |  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                 |  |  |  |  |

|        |         |          |          |         |     |                    | 0    | T3_MAT2 — Match output 2 of timer 3.                                                                                                   |  |  |  |  |

|        |         |          |          |         |     |                    | 0    | <b>USB0_IND0</b> — USB0 port indicator LED control output 0.                                                                           |  |  |  |  |

| P2_6   | K16     | J14      | G9       | 95      | [2] | N;                 | I/O  | SGPIO7 — General purpose digital input/output pin.                                                                                     |  |  |  |  |

|        |         |          |          |         |     | PU                 | I/O  | <b>U0_DIR</b> — RS-485/EIA-485 output enable/direction control for USART0.                                                             |  |  |  |  |

|        |         |          |          |         |     |                    | I/O  | EMC_A10 — External memory address line 10.                                                                                             |  |  |  |  |

|        |         |          |          |         |     |                    | 0    | <b>USB0_IND0</b> — USB0 port indicator LED control output 0.                                                                           |  |  |  |  |

|        |         |          |          |         |     |                    | I/O  | GPIO5[6] — General purpose digital input/output pin.                                                                                   |  |  |  |  |

|        |         |          |          |         |     |                    | I    | CTIN_7 — SCTimer/PWM input 7.                                                                                                          |  |  |  |  |

|        |         |          |          |         |     |                    | I    | T3_CAP3 — Capture input 3 of timer 3.                                                                                                  |  |  |  |  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                 |  |  |  |  |

| P2_7   | H14     | G12      | C10      | 96      | [2] | N;<br>PU           | I/O  | <b>GPIO0[7]</b> — General purpose digital input/output pin. If this pin is pulled LOW at reset, the part enters ISP mode using USART0. |  |  |  |  |

|        |         |          |          |         |     |                    | 0    | <b>CTOUT_1</b> — SCTimer/PWM output 1. Match output 3 of timer 3.                                                                      |  |  |  |  |

|        |         |          |          |         |     |                    | I/O  | <b>U3_UCLK</b> — Serial clock input/output for USART3 in synchronous mode.                                                             |  |  |  |  |

|        |         |          |          |         |     |                    | I/O  | EMC_A9 — External memory address line 9.                                                                                               |  |  |  |  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                 |  |  |  |  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                 |  |  |  |  |

|        |         |          |          |         |     |                    | 0    | T3_MAT3 — Match output 3 of timer 3.                                                                                                   |  |  |  |  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                 |  |  |  |  |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                                                                                                                                      |

|--------|---------|----------|----------|---------|-----|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3_1   | G11     | D10      | F7       | 114     | [2] | N;<br>PU    | I/O  | <b>I2S0_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification.                     |

|        |         |          |          |         |     |             | I/O  | <b>I2S0_RX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $\ell$ S-bus specification.                   |

|        |         |          |          |         |     |             | I    | CAN0_RD — CAN receiver input.                                                                                                                                                    |

|        |         |          |          |         |     |             | 0    | USB1_IND1 — USB1 Port indicator LED control output 1.                                                                                                                            |

|        |         |          |          |         |     |             | I/O  | GPIO5[8] — General purpose digital input/output pin.                                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                           |

|        |         |          |          |         |     |             | 0    | LCD_VD15 — LCD data.                                                                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                           |

| P3_2   | F11     | D9       | G6       | 116     | [2] | OL;<br>PU   | I/O  | <b>I2S0_TX_SDA</b> — I2S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> S-bus specification. |

|        |         |          |          |         |     |             | I/O  | <b>I2S0_RX_SDA</b> — I2S Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification.                  |

|        |         |          |          |         |     |             | 0    | CAN0_TD — CAN transmitter output.                                                                                                                                                |

|        |         |          |          |         |     |             | 0    | USB1_IND0 — USB1 Port indicator LED control output 0.                                                                                                                            |

|        |         |          |          |         |     |             | I/O  | GPIO5[9] — General purpose digital input/output pin.                                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                           |

|        |         |          |          |         |     |             | 0    | LCD_VD14 — LCD data.                                                                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                           |

| P3_3   | B14     | B13      | A7       | 118     | [4] | N;          | -    | R — Function reserved.                                                                                                                                                           |

|        |         |          |          |         |     | PU          | I/O  | SPI_SCK — Serial clock for SPI.                                                                                                                                                  |

|        |         |          |          |         |     |             | I/O  | SSP0_SCK — Serial clock for SSP0.                                                                                                                                                |

|        |         |          |          |         |     |             | 0    | SPIFI_SCK — Serial clock for SPIFI.                                                                                                                                              |

|        |         |          |          |         |     |             | 0    | CGU_OUT1 — CGU spare clock output 1.                                                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                           |

|        |         |          |          |         |     |             | 0    | I2S0_TX_MCLK — I2S transmit master clock.                                                                                                                                        |

|        |         |          |          |         |     |             | I/O  | <b>I2S1_TX_SCK</b> — Transmit Clock. It is driven by the master<br>and received by the slave. Corresponds to the signal SCK in<br>the I <sup>2</sup> S-bus specification.        |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol   | USB0,   |          |          | cuons   | are |             |      | e on all parts. See <u>Table 2</u> .  Description                                         |

|----------|---------|----------|----------|---------|-----|-------------|------|-------------------------------------------------------------------------------------------|

| cymbol - | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | •                                                                                         |

| P8_3     | J3      | H3       | -        | -       | [2] | N;          | I/O  | <b>GPIO4[3]</b> — General purpose digital input/output pin.                               |

|          |         |          |          |         |     | PU          | I/O  | <b>USB1_ULPI_D2</b> — ULPI link bidirectional data line 2.                                |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | 0    | LCD_VD12 — LCD data.                                                                      |

|          |         |          |          |         |     |             | 0    | LCD_VD19 — LCD data.                                                                      |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | 0    | T0_MAT3 — Match output 3 of timer 0.                                                      |

| P8_4     | J2      | H2       | -        | -       | [2] | N;          | I/O  | GPIO4[4] — General purpose digital input/output pin.                                      |

|          |         |          |          |         |     | PU          | I/O  | USB1_ULPI_D1 — ULPI link bidirectional data line 1.                                       |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | 0    | LCD_VD7 — LCD data.                                                                       |

|          |         |          |          |         |     |             | 0    | LCD_VD16 — LCD data.                                                                      |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | I    | T0_CAP0 — Capture input 0 of timer 0.                                                     |

| P8_5     | J1      | H1       | -        | -       | [2] | N;          | I/O  | GPIO4[5] — General purpose digital input/output pin.                                      |

|          |         |          |          |         |     | PU          | I/O  | USB1_ULPI_D0 — ULPI link bidirectional data line 0.                                       |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | 0    | LCD_VD6 — LCD data.                                                                       |

|          |         |          |          |         |     |             | 0    | LCD_VD8 — LCD data.                                                                       |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | I    | T0_CAP1 — Capture input 1 of timer 0.                                                     |

| P8_6     | K3      | J3       | -        | -       | [2] | N;          | I/O  | GPIO4[6] — General purpose digital input/output pin.                                      |

|          |         |          |          |         |     | PU          | I    | <b>USB1_ULPI_NXT</b> — ULPI link NXT signal. Data flow control signal from the PHY.       |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | 0    | LCD_VD5 — LCD data.                                                                       |

|          |         |          |          |         |     |             | 0    | <b>LCD_LP</b> — Line synchronization pulse (STN). Horizontal synchronization pulse (TFT). |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | -    | R — Function reserved.                                                                    |

|          |         |          |          |         |     |             | I    | T0_CAP2 — Capture input 2 of timer 0.                                                     |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

#### 32-bit ARM Cortex-M4/M0 microcontroller

#### Symbol Description state TFBGA180 TFBGA100 LBGA256 LQFP144 Reset : [1] Type L5 [2] PC\_11 N; R — Function reserved. PU I. USB1\_ULPI\_DIR — ULPI link DIR signal. Controls the ULPI data line direction. U1\_DCD — Data Carrier Detect input for UART 1. Т R — Function reserved. I/O GPIO6[10] — General purpose digital input/output pin. R — Function reserved. R — Function reserved. I/O SD\_DAT4 — SD/MMC data bus line 4. PC\_12 [2] L6 N; R — Function reserved. PU R — Function reserved. O U1\_DTR — Data Terminal Ready output for UART 1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART 1. R — Function reserved. GPIO6[11] — General purpose digital input/output pin. I/O SGPI011 — General purpose digital input/output pin. I/O I2S0\_TX\_SDA - I2S transmit data. It is driven by the I/O transmitter and read by the receiver. Corresponds to the signal SD in the I<sup>2</sup>S-bus specification. SD DAT5 - SD/MMC data bus line 5. I/O PC 13 M1 [2] R — Function reserved. N; PU R — Function reserved. \_ U1\_TXD — Transmitter output for UART 1. Ο R — Function reserved. GPIO6[12] — General purpose digital input/output pin. I/O SGPI012 — General purpose digital input/output pin. I/O 12S0 TX WS - Transmit Word Select. It is driven by the I/O master and received by the slave. Corresponds to the signal WS in the PS-bus specification. I/O SD DAT6 — SD/MMC data bus line 6. PC\_14 N1 [2] R — Function reserved. N; PU R — Function reserved. U1\_RXD — Receiver input for UART 1. Т R — Function reserved. GPIO6[13] — General purpose digital input/output pin. I/O I/O SGPI013 — General purpose digital input/output pin. 0 ENET\_TX\_ER — Ethernet Transmit Error (MII interface). SD\_DAT7 — SD/MMC data bus line 7. I/O

#### Table 3. Pin description ... continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

LPC43S50 S30 S20

32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                                                                                        |

|--------|---------|----------|----------|---------|-----|-------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| PE_3   | K12     | K10      | -        | -       | [2] | N;          | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     | PU          | 0    | CAN0_TD — CAN transmitter output.                                                                                                  |

|        |         |          |          |         |     |             | I    | ADCTRIG1 — ADC trigger input 1.                                                                                                    |

|        |         |          |          |         |     |             | I/O  | <b>EMC_A21</b> — External memory address line 21.                                                                                  |

|        |         |          |          |         |     |             | I/O  | <b>GPIO7[3]</b> — General purpose digital input/output pin.                                                                        |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

| PE_4   | K13     | J11      | -        | -       | [2] | N;          | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     | PU          | I    | NMI — External interrupt input to NMI.                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     |             | I/O  | EMC_A22 — External memory address line 22.                                                                                         |

|        |         |          |          |         |     |             | I/O  | GPI07[4] — General purpose digital input/output pin.                                                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

| PE_5   | N16     | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_3</b> — SCTimer/PWM output 3. Match output 3 of timer 0.                                                                  |

|        |         |          |          |         |     |             | 0    | <b>U1_RTS</b> — Request to Send output for UART 1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART 1. |

|        |         |          |          |         |     |             | I/O  | EMC_D24 — External memory data line 24.                                                                                            |

|        |         |          |          |         |     |             | I/O  | GPI07[5] — General purpose digital input/output pin.                                                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

| PE_6   | M16     | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_2</b> — SCTimer/PWM output 2. Match output 2 of timer 0.                                                                  |

|        |         |          |          |         |     |             | I    | U1_RI — Ring Indicator input for UART 1.                                                                                           |

|        |         |          |          |         |     |             | I/O  | EMC_D25 — External memory data line 25.                                                                                            |

|        |         |          |          |         |     |             | I/O  | GPIO7[6] — General purpose digital input/output pin.                                                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                             |

|        |         | 1        | 1        |         | 1   | 1           |      | R — Function reserved.                                                                                                             |

#### Table 3. Pin description ... continued

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180               | TFBGA100 | LQFP144 |                                                                                                                                                        | Reset state | Type | Description                                                                                                                                            |

|--------|---------|------------------------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| PF_9   | D6      | -                      | -        | -       | [5]                                                                                                                                                    | N;          | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        | PU          | I/O  | <b>U0_DIR</b> — RS-485/EIA-485 output enable/direction control for USART0.                                                                             |

|        |         |                        |          |         |                                                                                                                                                        |             | 0    | <b>CTOUT_1</b> — SCTimer/PWM output 1. Match output 3 of timer 3.                                                                                      |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | I/O  | GPI07[23] — General purpose digital input/output pin.                                                                                                  |

|        | -       | R — Function reserved. |          |         |                                                                                                                                                        |             |      |                                                                                                                                                        |

|        |         |                        |          |         |                                                                                                                                                        |             | I/O  | SGPIO3 — General purpose digital input/output pin.                                                                                                     |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          | AI      | <b>ADC1_2</b> — ADC1 and ADC0, input channel 2. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |             |      |                                                                                                                                                        |

| PF_10  | A3      | -                      | -        | -       | [5]                                                                                                                                                    | N;          | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        | PU          | 0    | U0_TXD — Transmitter output for USART0.                                                                                                                |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | I/O  | GPI07[24] — General purpose digital input/output pin.                                                                                                  |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | I    | <b>SD_WP</b> — SD/MMC card write protect input.                                                                                                        |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | AI   | <b>ADC0_5</b> — ADC0 and ADC1, input channel 5. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

| PF_11  | A2      | -                      | -        | -       | [5]                                                                                                                                                    | N;          | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        | PU          | I    | U0_RXD — Receiver input for USART0.                                                                                                                    |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | I/O  | GPI07[25] — General purpose digital input/output pin.                                                                                                  |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | 0    | <b>SD_VOLT2</b> — SD/MMC bus voltage select output 2.                                                                                                  |

|        |         |                        |          |         |                                                                                                                                                        |             | -    | R — Function reserved.                                                                                                                                 |

|        |         |                        |          |         |                                                                                                                                                        |             | AI   | <b>ADC1_5</b> — ADC1 and ADC0, input channel 5. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

#### 32-bit ARM Cortex-M4/M0 microcontroller

- 16 DMA request lines.

- Single DMA and burst DMA request signals. Each peripheral connected to the DMA Controller can assert either a burst DMA request or a single DMA request. The DMA burst size is set by programming the DMA Controller.

- Memory-to-memory, memory-to-peripheral, peripheral-to-memory, and peripheral-to-peripheral transfers are supported.

- Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

- Hardware DMA channel priority.

- AHB slave DMA programming interface. The DMA Controller is programmed by writing to the DMA control registers over the AHB slave interface.

- Two AHB bus masters for transferring data. These interfaces transfer data when a DMA request goes active. Master 1 can access memories and peripherals, master 0 can access memories only.

- 32-bit AHB master bus width.

- Incrementing or non-incrementing addressing for source and destination.

- Programmable DMA burst size. The DMA burst size can be programmed to more efficiently transfer data.

- Internal four-word FIFO per channel.

- Supports 8, 16, and 32-bit wide transactions.

- Big-endian and little-endian support. The DMA Controller defaults to little-endian mode on reset.

- An interrupt to the processor can be generated on a DMA completion or when a DMA error has occurred.

- Raw interrupt status. The DMA error and DMA count raw interrupt status can be read prior to masking.

#### 7.17.3 SPI Flash Interface (SPIFI)

The SPI Flash Interface allows low-cost serial flash memories to be connected to the ARM Cortex-M4 processor with little performance penalty compared to parallel flash devices with higher pin count.

After a few commands configure the interface at startup, the entire flash content is accessible as normal memory using byte, halfword, and word accesses by the processor and/or DMA channels. Simple sequences of commands handle erasing and programming.

Many serial flash devices use a half-duplex command-driven SPI protocol for device setup and initialization and then move to a half-duplex, command-driven 4-bit protocol for normal operation. Different serial flash vendors and devices accept or require different commands and command formats. SPIFI provides sufficient flexibility to be compatible with common flash devices and includes extensions to help insure compatibility with future devices.

#### 7.17.3.1 Features

• Interfaces to serial flash memory in the main memory map.

#### 32-bit ARM Cortex-M4/M0 microcontroller

- Built-in fractional baud rate generator covering wide range of baud rates without a need for external crystals of particular values.

- Auto baud capabilities and FIFO control mechanism that enables software flow control implementation.

- Support for RS-485/9-bit/EIA-485 mode.

- USART3 includes an IrDA mode to support infrared communication.

- All USARTs have DMA support.

- Support for synchronous mode at a data bit rate of up to 8 Mbit/s.

- Smart card mode conforming to ISO7816 specification

#### 7.18.3 SPI serial I/O controller

The LPC43S50/S30/S20 contain one SPI controller. SPI is a full-duplex serial interface designed to handle multiple masters and slaves connected to a given bus. Only a single master and a single slave can communicate on the interface during a given data transfer. During a data transfer the master always sends 8 bits to 16 bits of data to the slave, and the slave always sends 8 bits to 16 bits of data to the master.

#### 7.18.3.1 Features

- Maximum SPI data bit rate 25 Mbit/s.

- Compliant with SPI specification

- Synchronous, serial, full-duplex communication

- Combined SPI master and slave

- Maximum data bit rate of one eighth of the input clock rate

- 8 bits to 16 bits per transfer

#### 7.18.4 SSP serial I/O controller

Remark: The LPC43S50/S30/S20 contain two SSP controllers.

The SSP controller can operate on a SPI, 4-wire SSI, or Microwire bus. It can interact with multiple masters and slaves on the bus. Only a single master and a single slave can communicate on the bus during a given data transfer. The SSP supports full-duplex transfers, with frames of 4 bit to 16 bit of data flowing from the master to the slave and from the slave to the master. In practice, often only one of these data flows carries meaningful data.

#### 7.18.4.1 Features

- Maximum SSP speed in full-duplex mode of 25 Mbit/s; for transmit only 50 Mbit/s (master) and 17 Mbit/s (slave).

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses

- Synchronous serial communication

- Master or slave operation

- 8-frame FIFOs for both transmit and receive

- 4-bit to 16-bit frame

- DMA transfers supported by GPDMA

LPC43S50 S30 S20

#### 32-bit ARM Cortex-M4/M0 microcontroller

#### 7.18.5 I<sup>2</sup>C-bus interface

Remark: The LPC43S50/S30/S20 contain two I<sup>2</sup>C-bus interfaces.

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock line (SCL) and a Serial Data line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (for example an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

#### 7.18.5.1 Features

- I<sup>2</sup>C0 is a standard I<sup>2</sup>C-compliant bus interface with open-drain pins. I<sup>2</sup>C0 also supports Fast mode plus with bit rates up to 1 Mbit/s.

- I<sup>2</sup>C1 uses standard I/O pins with bit rates of up to 400 kbit/s (Fast I<sup>2</sup>C-bus).

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- All I<sup>2</sup>C-bus controllers support multiple address recognition and a bus monitor mode.

#### 7.18.6 I<sup>2</sup>S interface

**Remark:** The LPC43S50/S30/S20 contain two I<sup>2</sup>S-bus interfaces.

The I<sup>2</sup>S-bus provides a standard communication interface for digital audio applications.

The  $l^2S$ -bus specification defines a 3-wire serial bus using one data line, one clock line, and one word select signal. The basic  $l^2S$ -bus connection has one master, which is always the master, and one slave. The  $l^2S$ -bus interface provides a separate transmit and receive channel, each of which can operate as either a master or a slave.

#### 7.18.6.1 Features

- The I<sup>2</sup>S interface has separate input/output channels, each of which can operate in master or slave mode.

- Capable of handling 8-bit, 16-bit, and 32-bit word sizes.

- Mono and stereo audio data supported.

- The sampling frequency can range from 16 kHz to 192 kHz (16, 22.05, 32, 44.1, 48, 96, 192) kHz.

- Support for an audio master clock.

#### 32-bit ARM Cortex-M4/M0 microcontroller

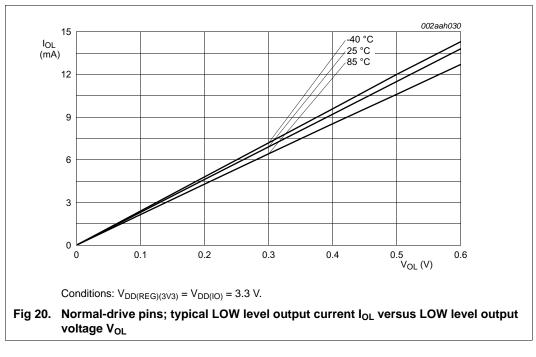

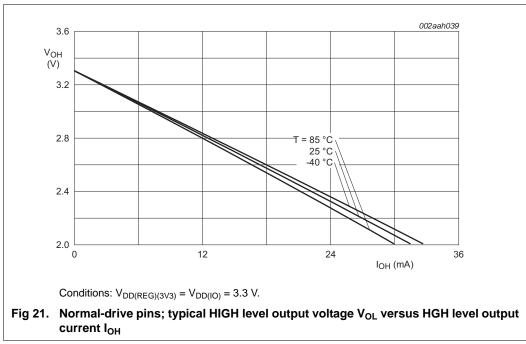

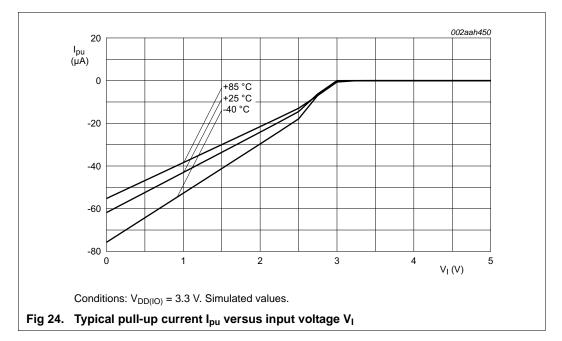

## 10.4 Electrical pin characteristics

#### 32-bit ARM Cortex-M4/M0 microcontroller

32-bit ARM Cortex-M4/M0 microcontroller

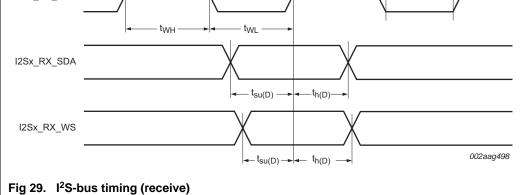

# I2Sx\_RX\_SCK

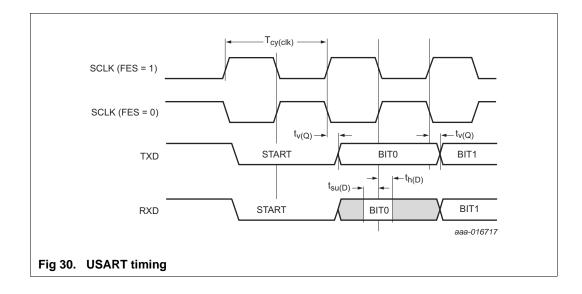

## 11.10 USART interface

#### Table 23. USART dynamic characteristics

$T_{amb} = -40 \text{ °C to } 85 \text{ °C}; 2.2 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}; 2.7 \text{ V} \le V_{DD(IO)} \le 3.6 \text{ V}; C_L = 20 \text{ pF. EHS} = 1 \text{ for all pins. Simulated values.}$

| Symbol             | Parameter              | Min  | Max | Unit |

|--------------------|------------------------|------|-----|------|

| USART master (i    | n synchronous mode)    | I    | I   |      |

| t <sub>su(D)</sub> | data input set-up time | 26.6 | -   | ns   |

| t <sub>h(D)</sub>  | data input hold time   | 0    | -   | ns   |

| t <sub>v(Q)</sub>  | data output valid time | 0    | 8.8 | ns   |

| USART slave (in    | synchronous mode)      | I    |     |      |

| t <sub>su(D)</sub> | data input set-up time | 1.2  | -   | ns   |

| t <sub>h(D)</sub>  | data input hold time   | 0.4  | -   | ns   |

| t <sub>v(Q)</sub>  | data output valid time | 5.5  | 24  | ns   |

32-bit ARM Cortex-M4/M0 microcontroller

#### 32-bit ARM Cortex-M4/M0 microcontroller

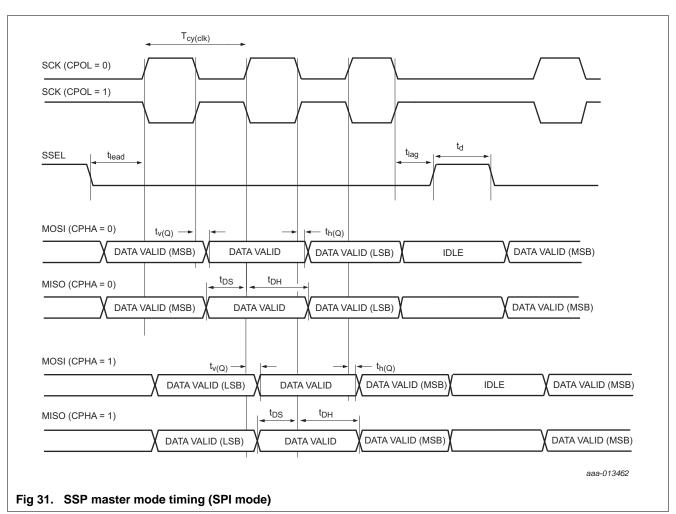

## 11.12 SPI interface

#### Table 25. Dynamic characteristics: SPI

$T_{amb} = -40$  °C to +85 °C; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V. Simulated values.

| Symbol                | Parameter              | Conditions |     | Min                              | Тур | Max                             | Unit |

|-----------------------|------------------------|------------|-----|----------------------------------|-----|---------------------------------|------|

| T <sub>cy(PCLK)</sub> | PCLK cycle time        |            |     | 5                                |     |                                 | ns   |

| T <sub>cy(clk)</sub>  | clock cycle time       |            | [1] | 40                               | -   | -                               | ns   |

| Master                |                        |            |     |                                  |     |                                 |      |

| t <sub>DS</sub>       | data set-up time       |            |     | 7.2                              | -   | -                               | ns   |

| t <sub>DH</sub>       | data hold time         |            |     | 0                                | -   | -                               | ns   |

| t <sub>v(Q)</sub>     | data output valid time |            |     | -                                | -   | 3.7                             | ns   |

| t <sub>h(Q)</sub>     | data output hold time  |            |     | -                                | -   | 1.2                             | ns   |

| Slave                 |                        |            |     |                                  |     |                                 |      |

| t <sub>DS</sub>       | data set-up time       |            |     | 1.2                              | -   | -                               | ns   |

| t <sub>DH</sub>       | data hold time         |            |     | 3 x T <sub>cy(PCLK)</sub> + 0.54 | -   | -                               | ns   |

| t <sub>v(Q)</sub>     | data output valid time |            |     | -                                | -   | 3 x T <sub>cy(PCLK)</sub> + 9.7 | ns   |

| t <sub>h(Q)</sub>     | data output hold time  |            |     | -                                | -   | 2 x T <sub>cy(PCLK)</sub> + 7.1 | ns   |

[1]  $T_{cy(clk)} = 8/BASE_SPI_CLK$ .  $Tcy(PCLK) = 1/BASE_SPI_CLK$ .

32-bit ARM Cortex-M4/M0 microcontroller

11.13 SSP/SPI timing diagrams

#### 32-bit ARM Cortex-M4/M0 microcontroller

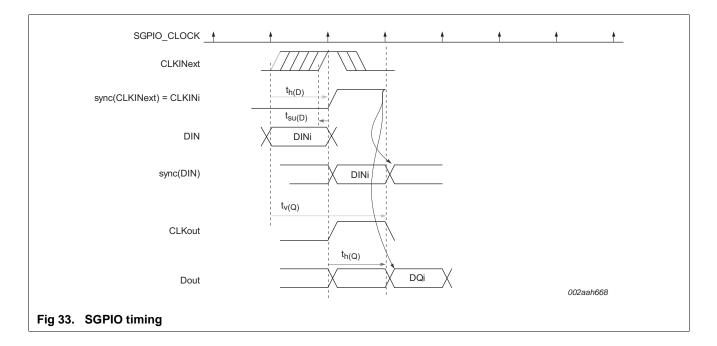

| Symbol             | Parameter              | Conditions                |            | Min                    | Тур | Max                    | Unit |

|--------------------|------------------------|---------------------------|------------|------------------------|-----|------------------------|------|

| t <sub>su(D)</sub> | data input set-up time |                           |            | 2                      | -   | -                      | ns   |

| t <sub>h(D)</sub>  | data input hold time   |                           | [1]        | T <sub>SGPIO</sub> + 2 | -   | -                      | ns   |

| t <sub>su(D)</sub> | data input set-up time | sampled by<br>SGPIO_CLOCK | <u>[1]</u> | T <sub>SGPIO</sub> + 2 | -   | -                      | ns   |

| t <sub>h(D)</sub>  | data input hold time   | sampled by<br>SGPIO_CLOCK | [1]        | T <sub>SGPIO</sub> + 2 | -   | -                      | ns   |

| t <sub>v(Q)</sub>  | data output valid time |                           | [1]        | -                      | -   | 2 x T <sub>SGPIO</sub> | ns   |

| t <sub>h(Q)</sub>  | data output hold time  |                           | [1]        | T <sub>SGPIO</sub>     | -   |                        | ns   |

| t <sub>v(Q)</sub>  | data output valid time | sampled by<br>SGPIO_CLOCK | <u>[1]</u> | -3                     | -   | 3                      | ns   |

| t <sub>h(Q)</sub>  | data output hold time  | sampled by<br>SGPIO_CLOCK | <u>[1]</u> | -3                     | -   | 3                      | ns   |

Table 26. Dynamic characteristics: SGPIO  $T_{amb} = -40 \ ^{\circ}C$  to +85  $\ ^{\circ}C$ ; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6 \ V$ ; 2.7 V  $\leq V_{DD(IO)} \leq 3.6 \ V$ . Simulated values.

[1] SGPIO\_CLOCK is the internally generated SGPIO clock.  $T_{SGPIO} = 1/f_{SGPIO_CLOCK}$ .

32-bit ARM Cortex-M4/M0 microcontroller

### 11.16 USB interface

#### Table 30. Dynamic characteristics: USB0 and USB1 pins (full-speed)

$C_L = 50 \text{ pF}; R_{pu} = 1.5 \text{ k}\Omega \text{ on } D + \text{ to } V_{DD(IO)}; 3.0 \text{ V} \le V_{DD(IO)} \le 3.6 \text{ V}.$

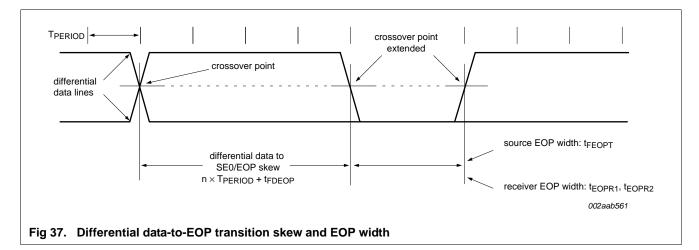

| Symbol             | Parameter                                                   | Conditions                              |     | Min   | Тур | Max    | Unit |

|--------------------|-------------------------------------------------------------|-----------------------------------------|-----|-------|-----|--------|------|

| t <sub>r</sub>     | rise time                                                   | 10 % to 90 %                            |     | 4     | -   | 20     | ns   |

| t <sub>f</sub>     | fall time                                                   | 10 % to 90 %                            |     | 4     | -   | 20     | ns   |

| t <sub>FRFM</sub>  | differential rise and fall time matching                    | t <sub>r</sub> / t <sub>f</sub>         |     | 90    | -   | 111.11 | %    |

| V <sub>CRS</sub>   | output signal crossover voltage                             |                                         |     | 1.3   | -   | 2.0    | V    |

| t <sub>FEOPT</sub> | source SE0 interval of EOP                                  | see Figure 37                           |     | 160   | -   | 175    | ns   |

| t <sub>FDEOP</sub> | source jitter for differential transition to SE0 transition | see Figure 37                           |     | -2    | -   | +5     | ns   |

| t <sub>JR1</sub>   | receiver jitter to next transition                          |                                         |     | -18.5 | -   | +18.5  | ns   |

| t <sub>JR2</sub>   | receiver jitter for paired transitions                      | 10 % to 90 %                            |     | -9    | -   | +9     | ns   |

| t <sub>EOPR1</sub> | EOP width at receiver                                       | must reject as<br>EOP; see<br>Figure 37 | [1] | 40    | -   | -      | ns   |

| t <sub>EOPR2</sub> | EOP width at receiver                                       | must accept as<br>EOP; see<br>Figure 37 | [1] | 82    | -   | -      | ns   |

[1] Characterized but not implemented as production test. Guaranteed by design.

**Remark:** If only USB0 (HS USB) is used, the pins VDDREG and VDDIO can be at different voltages within the operating range but should have the same ramp up time. If USB1(FS USB) is used, the pins VDDREG and VDDIO should be a minimum of 3.0 V and be tied together.

126 of 156

#### 32-bit ARM Cortex-M4/M0 microcontroller

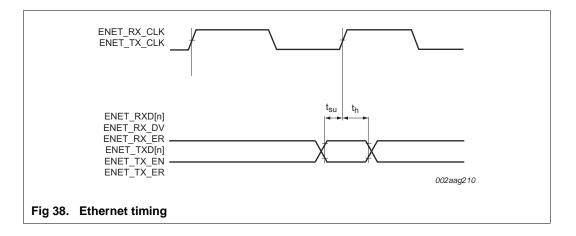

#### Table 32. Dynamic characteristics: Ethernet

$T_{amb} = -40 \ ^{\circ}C$  to 85  $\ ^{\circ}C$ ; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6 \ V$ ; 2.7 V  $\leq V_{DD(IO)} \leq 3.6 \ V$ . Values guaranteed by design.

| Symbol                | Parameter        | Conditions                                                         |               | Min | Max      | Unit     |

|-----------------------|------------------|--------------------------------------------------------------------|---------------|-----|----------|----------|

| RMII mo               | de               |                                                                    |               |     | <b>I</b> |          |

| f <sub>clk</sub>      | clock frequency  | for ENET_RX_CLK                                                    | <u>[1]</u>    | -   | 50       | MHz      |

| $\delta_{\text{clk}}$ | clock duty cycle |                                                                    | [1]           | 50  | 50       | %        |

| t <sub>su</sub>       | set-up time      | for ENET_TXDn, ENET_TX_EN,<br>ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV | [1][2]        | 4   | -        | ns       |

| t <sub>h</sub>        | hold time        | for ENET_TXDn, ENET_TX_EN,<br>ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV | [1][2]        | 2   | -        | ns       |

| MII mode              | )                |                                                                    |               |     |          | <b>I</b> |

| f <sub>clk</sub>      | clock frequency  | for ENET_TX_CLK                                                    | <u>[1]</u>    | -   | 25       | MHz      |

| $\delta_{\text{clk}}$ | clock duty cycle |                                                                    | [1]           | 50  | 50       | %        |

| t <sub>su</sub>       | set-up time      | for ENET_TXDn, ENET_TX_EN,<br>ENET_TX_ER                           | <u>[1][2]</u> | 4   | -        | ns       |

| t <sub>h</sub>        | hold time        | for ENET_TXDn, ENET_TX_EN,<br>ENET_TX_ER                           | [1][2]        | 2   | -        | ns       |

| f <sub>clk</sub>      | clock frequency  | for ENET_RX_CLK                                                    | [1]           | -   | 25       | MHz      |

| $\delta_{\text{clk}}$ | clock duty cycle |                                                                    | [1]           | 50  | 50       | %        |

| t <sub>su</sub>       | set-up time      | for ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV                           | <u>[1][2]</u> | 4   | -        | ns       |

| t <sub>h</sub>        | hold time        | for ENET_RXDn, ENET_RX_ER,<br>ENET_RX_DV                           | [1][2]        | 2   | -        | ns       |

[1] Output drivers can drive a load ≥ 25 pF accommodating over 12 inch of PCB trace and the input capacitance of the receiving device.

[2] Timing values are given from the point at which the clock signal waveform crosses 1.4 V to the valid input or output level.

#### 32-bit ARM Cortex-M4/M0 microcontroller

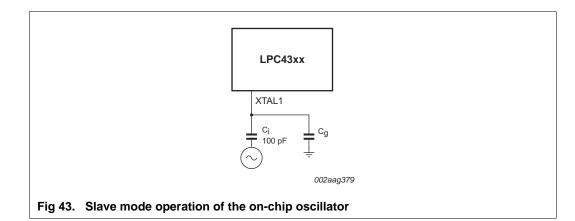

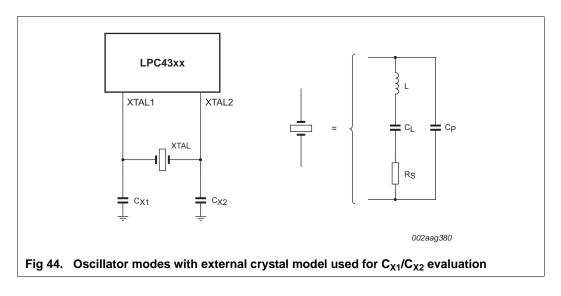

Table 41.

Recommended values for C<sub>X1/X2</sub> in oscillation mode (crystal and external components parameters) low frequency mode ...continued

| Maximum crystal series resistance R <sub>S</sub> | External load capacitors $C_{X1}, C_{X2}$ |

|--------------------------------------------------|-------------------------------------------|

| < 160 Ω                                          | 18 pF, 18 pF                              |

| < 160 Ω                                          | 39 pF, 39 pF                              |

| < 120 Ω                                          | 18 pF, 18 pF                              |

| < 80 Ω                                           | 33 pF, 33 pF                              |

| <100 Ω                                           | 18 pF, 18 pF                              |

| < 80 Ω                                           | 33 pF, 33 pF                              |

|                                                  | resistance R <sub>s</sub> < 160 Ω         |

## Table 42.Recommended values for $C_{X1/X2}$ in oscillation mode (crystal and external<br/>components parameters) high frequency mode

| Fundamental oscillation frequency | Maximum crystal series<br>resistance R <sub>S</sub> | External load capacitors $C_{X1}$ , $C_{x2}$ |

|-----------------------------------|-----------------------------------------------------|----------------------------------------------|

| 15 MHz                            | < 80 Ω                                              | 18 pF, 18 pF                                 |

| 20 MHz                            | < 80 Ω                                              | 39 pF, 39 pF                                 |

|                                   | < 100 Ω                                             | 47 pF, 47 pF                                 |

All information provided in this document is subject to legal disclaimers.