Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                                           |

|----------------------------|-----------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                    |

| Core Processor             | ARM® Cortex®-M4/M0                                                                                        |

| Core Size                  | 32-Bit Dual-Core                                                                                          |

| Speed                      | 204MHz                                                                                                    |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT                           |

| Number of I/O              | 164                                                                                                       |

| Program Memory Size        | -                                                                                                         |

| Program Memory Type        | ROMIess                                                                                                   |

| EEPROM Size                | -                                                                                                         |

| RAM Size                   | 264К х 8                                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                               |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                      |

| Oscillator Type            | Internal                                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                         |

| Mounting Type              | Surface Mount                                                                                             |

| Package / Case             | 256-LBGA                                                                                                  |

| Supplier Device Package    | 256-LBGA (17x17)                                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc43s30fet256e                                   |

|                            |                                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M4/M0 microcontroller

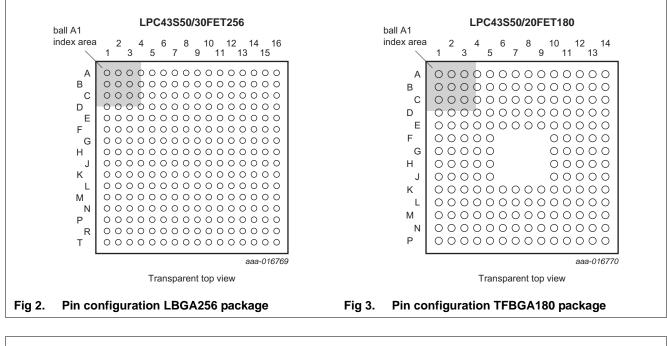

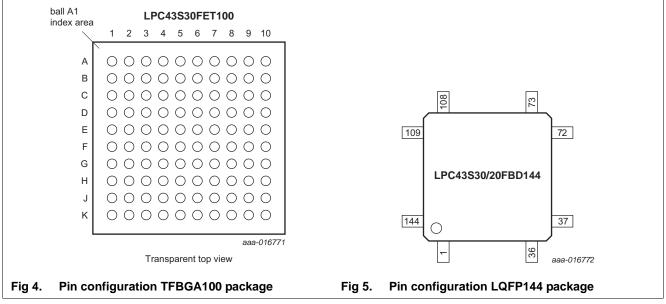

### 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

On the LPC43S50/S30/S20, digital pins are grouped into 16 ports, named P0 to P9 and PA to PF, with up to 20 pins used per port. Each digital pin can support up to eight different digital functions, including General-Purpose I/O (GPIO), selectable through the System Configuration Unit (SCU) registers. The pin name is not indicative of the GPIO port assigned to it.

### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                                                                                                                                              |

|--------|---------|----------|----------|---------|-----|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3_4   | A15     | C14      | B8       | 119     | [2] | N;          | I/O  | GPIO1[14] — General purpose digital input/output pin.                                                                                                                                    |

|        |         |          |          |         |     | PU          | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | I/O  | SPIFI_SIO3 — I/O lane 3 for SPIFI.                                                                                                                                                       |

|        |         |          |          |         |     |             | 0    | U1_TXD — Transmitter output for UART 1.                                                                                                                                                  |

|        |         |          |          |         |     |             | I/O  | <b>I2S0_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification.                             |

|        |         |          |          |         |     |             | I/O  | <b>I2S1_RX_SDA</b> — I2S1 Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> S-bus specification.         |

|        |         |          |          |         |     |             | 0    | LCD_VD13 — LCD data.                                                                                                                                                                     |

| P3_5   | C12     | C11      | B7       | 121     | [2] | N;          | I/O  | GPIO1[15] — General purpose digital input/output pin.                                                                                                                                    |

|        |         |          |          |         |     | PU          | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | I/O  | SPIFI_SIO2 — I/O lane 2 for SPIFI.                                                                                                                                                       |

|        |         |          |          |         |     |             | I    | U1_RXD — Receiver input for UART 1.                                                                                                                                                      |

|        |         |          |          |         |     |             | I/O  | <b>I2S0_TX_SDA</b> — I2S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification. |

|        |         |          |          |         |     |             | I/O  | <b>I2S1_RX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $\rho$ S-bus specification.                           |

|        |         |          |          |         |     |             | 0    | LCD_VD12 — LCD data.                                                                                                                                                                     |

| P3_6   | B13     | B12      | C7       | 122     | [2] | N;          | I/O  | GPIO0[6] — General purpose digital input/output pin.                                                                                                                                     |

|        |         |          |          |         |     | PU          | I/O  | SPI_MISO — Master In Slave Out for SPI.                                                                                                                                                  |

|        |         |          |          |         |     |             | I/O  | SSP0_SSEL — Slave Select for SSP0.                                                                                                                                                       |

|        |         |          |          |         |     |             | I/O  | SPIFI_MISO — Input 1 in SPIFI quad mode; SPIFI output IO1.                                                                                                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | I/O  | SSP0_MISO — Master In Slave Out for SSP0.                                                                                                                                                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

| P3_7   | C11     | C10      | D7       | 123     | [2] | N;          | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     | PU          | I/O  | SPI_MOSI — Master Out Slave In for SPI.                                                                                                                                                  |

|        |         |          |          |         |     |             | I/O  | SSP0_MISO — Master In Slave Out for SSP0.                                                                                                                                                |

|        |         |          |          |         |     |             | I/O  | SPIFI_MOSI — Input I0 in SPIFI quad mode; SPIFI output IO0.                                                                                                                              |

|        |         |          |          |         |     |             | I/O  | GPIO5[10] — General purpose digital input/output pin.                                                                                                                                    |

|        |         |          |          |         |     |             | I/O  | SSP0_MOSI — Master Out Slave in for SSP0.                                                                                                                                                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                                                                                                                   |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

Product data sheet

LPC43S50\_S30\_S20

All information provided in this document is subject to legal disclaimers.

### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | , USBU, 8 |          |          | CUONS   | are |                    |      | e on all parts. See <u>Table 2</u> .  Description                                                                                  |

|--------|-----------|----------|----------|---------|-----|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------|

|        | LBGA256   | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type |                                                                                                                                    |

| P5_2   | R4        | M3       | -        | 46      | [2] | N;                 | I/O  | <b>GPIO2[11]</b> — General purpose digital input/output pin.                                                                       |

|        |           |          |          |         |     | PU                 | I    | MCI1 — Motor control PWM channel 1, input.                                                                                         |

|        |           |          |          |         |     |                    | I/O  | EMC_D14 — External memory data line 14.                                                                                            |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

|        |           |          |          |         |     |                    | 0    | <b>U1_RTS</b> — Request to Send output for UART 1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART 1. |

|        |           |          |          |         |     |                    | I    | T1_CAP2 — Capture input 2 of timer 1.                                                                                              |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

| P5_3   | Т8        | P6       | -        | 54      | [2] | N;                 | I/O  | GPIO2[12] — General purpose digital input/output pin.                                                                              |

|        |           |          |          |         |     | PU                 | I    | MCI0 — Motor control PWM channel 0, input.                                                                                         |

|        |           |          |          |         |     |                    | I/O  | EMC_D15 — External memory data line 15.                                                                                            |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

|        |           |          |          |         |     |                    | I    | U1_RI — Ring Indicator input for UART 1.                                                                                           |

|        |           |          |          |         |     |                    | I    | T1_CAP3 — Capture input 3 of timer 1.                                                                                              |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

| P5_4   | P9        | N7       | -        | 57      | [2] | N;                 | I/O  | GPIO2[13] — General purpose digital input/output pin.                                                                              |

|        |           |          |          |         |     | PU                 | 0    | MCOB0 — Motor control PWM channel 0, output B.                                                                                     |

|        |           |          |          |         |     |                    | I/O  | EMC_D8 — External memory data line 8.                                                                                              |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

|        |           |          |          |         |     |                    | I    | <b>U1_CTS</b> — Clear to Send input for UART 1.                                                                                    |

|        |           |          |          |         |     |                    | 0    | T1_MAT0 — Match output 0 of timer 1.                                                                                               |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

| P5_5   | P10       | N8       | -        | 58      | [2] | N;                 | I/O  | GPIO2[14] — General purpose digital input/output pin.                                                                              |

|        |           |          |          |         |     | PU                 | 0    | MCOA1 — Motor control PWM channel 1, output A.                                                                                     |

|        |           |          |          |         |     |                    | I/O  | EMC_D9 — External memory data line 9.                                                                                              |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

|        |           |          |          |         |     |                    | I    | <b>U1_DCD</b> — Data Carrier Detect input for UART 1.                                                                              |

|        |           |          |          |         |     |                    | 0    | T1_MAT1 — Match output 1 of timer 1.                                                                                               |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                             |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

### 32-bit ARM Cortex-M4/M0 microcontroller

|        | , USB0, a | ana US   | B1 tun   | ctions  | are | -                  |      | e on all parts. See <u>Table 2</u> .                                                                                                                             |

|--------|-----------|----------|----------|---------|-----|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | LBGA256   | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                      |

| P9_2   | N8        | M6       | -        | -       | [2] | N;                 | I/O  | GPIO4[14] — General purpose digital input/output pin.                                                                                                            |

|        |           |          |          |         |     | PU                 | 0    | MCOB2 — Motor control PWM channel 2, output B.                                                                                                                   |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |           |          |          |         |     |                    | I/O  | <b>I2S0_TX_SDA</b> — I2S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification. |

|        |           |          |          |         |     |                    | I    | ENET_RXD3 — Ethernet receive data 3 (MII interface).                                                                                                             |

|        |           |          |          |         |     |                    | I/O  | SGPIO2 — General purpose digital input/output pin.                                                                                                               |

|        |           |          |          |         |     |                    | I/O  | SSP0_MOSI — Master Out Slave in for SSP0.                                                                                                                        |

| P9_3   | M6        | P5       | -        | -       | [2] | N;                 | I/O  | GPIO4[15] — General purpose digital input/output pin.                                                                                                            |

|        |           |          |          |         |     | PU                 | 0    | MCOA0 — Motor control PWM channel 0, output A.                                                                                                                   |

|        |           |          |          |         |     |                    | 0    | USB1_IND1 — USB1 Port indicator LED control output 1.                                                                                                            |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |           |          |          |         |     |                    | I    | ENET_RXD2 — Ethernet receive data 2 (MII interface).                                                                                                             |

|        |           |          |          |         |     |                    | I/O  | SGPIO9 — General purpose digital input/output pin.                                                                                                               |

|        |           |          |          |         |     |                    | 0    | U3_TXD — Transmitter output for USART3.                                                                                                                          |

| P9_4   | N10       | M8       | -        | -       | [2] | N;                 | -    | R — Function reserved.                                                                                                                                           |

|        |           |          |          |         |     | PU                 | 0    | MCOB0 — Motor control PWM channel 0, output B.                                                                                                                   |

|        |           |          |          |         |     |                    | 0    | USB1_IND0 — USB1 Port indicator LED control output 0.                                                                                                            |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |           |          |          |         |     |                    | I/O  | GPIO5[17] — General purpose digital input/output pin.                                                                                                            |

|        |           |          |          |         |     |                    | 0    | ENET_TXD2 — Ethernet transmit data 2 (MII interface).                                                                                                            |

| 1      |           |          |          |         |     |                    | I/O  | SGPIO4 — General purpose digital input/output pin.                                                                                                               |

|        |           |          |          |         |     |                    | I    | U3_RXD — Receiver input for USART3.                                                                                                                              |

| P9_5   | M9        | L7       | -        | 69      | [2] | N;                 | -    | R — Function reserved.                                                                                                                                           |

|        |           |          |          |         |     | PU                 | 0    | MCOA1 — Motor control PWM channel 1, output A.                                                                                                                   |

| 1      |           |          |          |         |     |                    | 0    | <b>USB1_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active high).                  |

|        |           |          |          |         |     |                    |      | Add a pull-down resistor to disable the power switch at reset.<br>This signal has opposite polarity compared to the USB_PPWR<br>used on other NXP LPC parts.     |

|        |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |           |          |          |         |     |                    | I/O  | GPIO5[18] — General purpose digital input/output pin.                                                                                                            |

|        |           |          |          |         |     |                    | 0    | <b>ENET_TXD3</b> — Ethernet transmit data 3 (MII interface).                                                                                                     |

|        |           |          |          |         |     |                    | I/O  | SGPIO3 — General purpose digital input/output pin.                                                                                                               |

|        |           |          |          |         |     |                    | 0    | U0_TXD — Transmitter output for USART0.                                                                                                                          |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

#### 32-bit ARM Cortex-M4/M0 microcontroller

#### Symbol Description state TFBGA180 TFBGA100 LBGA256 LQFP144 Reset : [1] Type L5 [2] PC\_11 N; R — Function reserved. PU I. USB1\_ULPI\_DIR — ULPI link DIR signal. Controls the ULPI data line direction. U1\_DCD — Data Carrier Detect input for UART 1. Т R — Function reserved. I/O GPIO6[10] — General purpose digital input/output pin. R — Function reserved. R — Function reserved. I/O SD\_DAT4 — SD/MMC data bus line 4. PC\_12 [2] L6 N; R — Function reserved. PU R — Function reserved. O U1\_DTR — Data Terminal Ready output for UART 1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART 1. R — Function reserved. GPIO6[11] — General purpose digital input/output pin. I/O SGPI011 — General purpose digital input/output pin. I/O I2S0\_TX\_SDA - I2S transmit data. It is driven by the I/O transmitter and read by the receiver. Corresponds to the signal SD in the I<sup>2</sup>S-bus specification. SD DAT5 - SD/MMC data bus line 5. I/O PC 13 M1 [2] R — Function reserved. N; PU R — Function reserved. \_ U1\_TXD — Transmitter output for UART 1. Ο R — Function reserved. GPIO6[12] — General purpose digital input/output pin. I/O SGPI012 — General purpose digital input/output pin. I/O 12S0 TX WS - Transmit Word Select. It is driven by the I/O master and received by the slave. Corresponds to the signal WS in the PS-bus specification. I/O SD DAT6 — SD/MMC data bus line 6. PC\_14 N1 [2] R — Function reserved. N; PU R — Function reserved. U1\_RXD — Receiver input for UART 1. Т R — Function reserved. GPIO6[13] — General purpose digital input/output pin. I/O I/O SGPI013 — General purpose digital input/output pin. 0 ENET\_TX\_ER — Ethernet Transmit Error (MII interface). SD\_DAT7 — SD/MMC data bus line 7. I/O

#### Table 3. Pin description ... continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

LPC43S50 S30 S20

32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                          |

|--------|---------|----------|----------|---------|-----|-------------|------|----------------------------------------------------------------------|

| PD_0   | N2      | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_15</b> — SCTimer/PWM output 15. Match output 3 of timer 3.  |

|        |         |          |          |         |     |             | 0    | <b>EMC_DQMOUT2</b> — Data mask 2 used with SDRAM and static devices. |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | GPIO6[14] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | SGPIO4 — General purpose digital input/output pin.                   |

| PD_1   | P1      | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     | PU          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | 0    | EMC_CKEOUT2 — SDRAM clock enable 2.                                  |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | GPIO6[15] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |             | 0    | <b>SD_POW</b> — SD/MMC power monitor output.                         |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | SGPI05 — General purpose digital input/output pin.                   |

| PD_2   | R1      | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_7</b> — SCTimer/PWM output 7. Match output 3 of timer 1.    |

|        |         |          |          |         |     |             | I/O  | EMC_D16 — External memory data line 16.                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | GPIO6[16] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | SGPIO6 — General purpose digital input/output pin.                   |

| PD_3   | P4      | -        | -        | -       | [2] | N;          | -    | R — Function reserved.                                               |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_6</b> — SCTimer/PWM output 7. Match output 2 of timer 1.    |

|        |         |          |          |         |     |             | I/O  | EMC_D17 — External memory data line 17.                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | GPIO6[17] — General purpose digital input/output pin.                |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                               |

|        |         |          |          |         |     |             | I/O  | SGPI07 — General purpose digital input/output pin.                   |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

### 32-bit ARM Cortex-M4/M0 microcontroller

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

| Symbol                  | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |            | Reset state | Type | Description                                                                                                                                                                                           |

|-------------------------|---------|----------|----------|---------|------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAKEUP1                 | A10     | C8       | -        | -       | [11]       | I; IA       | I    | External wake-up input; can raise an interrupt and can cause wake-up from any of the low-power modes. A pulse with a duration > 45 ns wakes up the part. This pin does not have an internal pull-up.  |

| WAKEUP2                 | C9      | E5       | -        | -       | [11]       | I; IA       | I    | External wake-up input; can raise an interrupt and can cause wake-up from any of the low-power modes. A pulse with a duration > 45 ns wakes up the part. This pin does not have an internal pull-up.  |

| WAKEUP3                 | D8      | -        | -        | -       | [11]       | I; IA       | I    | External wake-up input; can raise an interrupt and can cause wake-up from any of the low-power modes. A pulse with a duration > 45 ns wakes up the part. This pin does not have an internal pull-up.  |

| ADC pins                |         |          |          |         |            |             |      |                                                                                                                                                                                                       |

| ADC0_0/<br>ADC1_0/DAC   | E3      | B6       | A2       | 6       | [8]        | I; IA       | I    | ADC input channel 0. Shared between 10-bit ADC0/1 and DAC.                                                                                                                                            |

| ADC0_1/<br>ADC1_1       | C3      | C4       | A1       | 2       | [8]        | I; IA       | I    | ADC input channel 1. Shared between 10-bit ADC0/1.                                                                                                                                                    |

| ADC0_2/<br>ADC1_2       | A4      | B3       | B3       | 143     | [8]        | I; IA       | I    | ADC input channel 2. Shared between 10-bit ADC0/1.                                                                                                                                                    |

| ADC0_3/<br>ADC1_3       | B5      | B4       | A3       | 139     | [8]        | I; IA       | I    | ADC input channel 3. Shared between 10-bit ADC0/1.                                                                                                                                                    |

| ADC0_4/<br>ADC1_4       | C6      | A5       | -        | 138     | [8]        | I; IA       | I    | ADC input channel 4. Shared between 10-bit ADC0/1.                                                                                                                                                    |

| ADC0_5/<br>ADC1_5       | B3      | C3       | -        | 144     | [8]        | I; IA       | I    | ADC input channel 5. Shared between 10-bit ADC0/1.                                                                                                                                                    |

| ADC0_6/<br>ADC1_6       | A5      | A4       | -        | 142     | [8]        | I; IA       | I    | ADC input channel 6. Shared between 10-bit ADC0/1.                                                                                                                                                    |

| ADC0_7/<br>ADC1_7       | C5      | B5       | -        | 136     | <u>[8]</u> | I; IA       | I    | ADC input channel 7. Shared between 10-bit ADC0/1.                                                                                                                                                    |

| RTC                     |         |          |          |         |            |             |      |                                                                                                                                                                                                       |

| RTC_ALARM               | A11     | A10      | C3       | 129     | [11]       | 0           | 0    | RTC controlled output. This pin has an internal pull-up. The reset state of this pin is LOW after POR. For all other types of reset, the reset state depends on the state of the RTC alarm interrupt. |

| RTCX1                   | A8      | A8       | A5       | 125     | [8]        | -           | I    | Input to the RTC 32 kHz ultra-low power oscillator circuit.                                                                                                                                           |

| RTCX2                   | B8      | B7       | B5       | 126     | [8]        | -           | 0    | Output from the RTC 32 kHz ultra-low power oscillator circuit.                                                                                                                                        |

| Crystal oscillat        | or pins | 5        |          |         |            | •           |      |                                                                                                                                                                                                       |

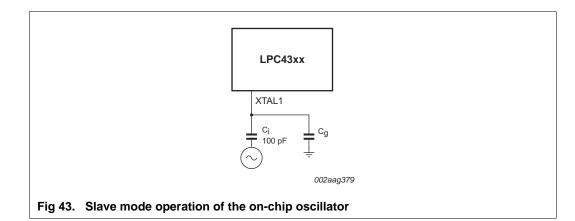

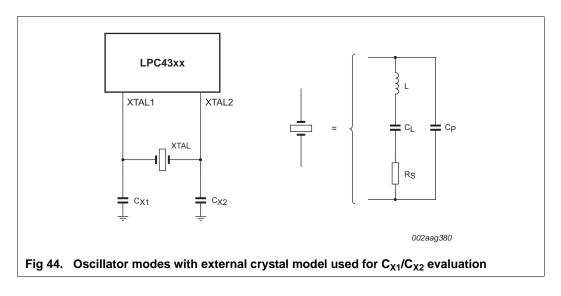

| XTAL1                   | D1      | C1       | B1       | 12      | <u>[8]</u> | -           | I    | Input to the oscillator circuit and internal clock generator circuits.                                                                                                                                |

| XTAL2                   | E1      | D1       | C1       | 13      | [8]        | -           | 0    | Output from the oscillator amplifier.                                                                                                                                                                 |

| Power and gro           | und pii | ns       |          |         |            | 1           |      |                                                                                                                                                                                                       |

| USB0_VDDA<br>3V3_DRIVER | F3      | E3       | D1       | 16      |            | -           | -    | Separate analog 3.3 V power supply for driver.                                                                                                                                                        |

#### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol        | LBGA256                                                                                           | TFBGA180 | TFBGA100                              | LQFP144                 |                              | Reset state<br>[1] | Type | Description    |

|---------------|---------------------------------------------------------------------------------------------------|----------|---------------------------------------|-------------------------|------------------------------|--------------------|------|----------------|

| VSSIO         | C4,<br>D13,<br>G6,<br>G7,<br>G8,<br>H8,<br>H9,<br>J8,<br>J9,<br>K9,<br>K10,<br>M13,<br>P7,<br>P13 | -        | C8,<br>D4,<br>D5,<br>G8,<br>J3,<br>J6 | 4,<br>40,<br>76,<br>109 | [ <u>13]</u><br>[ <u>14]</u> | -                  | -    | Ground.        |

| VSSA          | B2                                                                                                | A3       | C2                                    | 135                     |                              | -                  | -    | Analog ground. |

| Not connected |                                                                                                   |          |                                       |                         |                              |                    |      |                |

| -             | B9                                                                                                | B8       | -                                     | -                       |                              | -                  | -    | n.c.           |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

[1] N = neutral, input buffer disabled; no extra VDDIO current consumption if the input is driven midway between supplies; set the EZI bit in the SFS register to enable the input buffer; I = input; OL = output driving LOW; OH = output driving HIGH; AI/O = analog input/output; IA = inactive; PU = pull-up enabled (weak pull-up resistor pulls up pin to VDDIO; F = floating. Reset state reflects the pin state at reset without boot code operation.

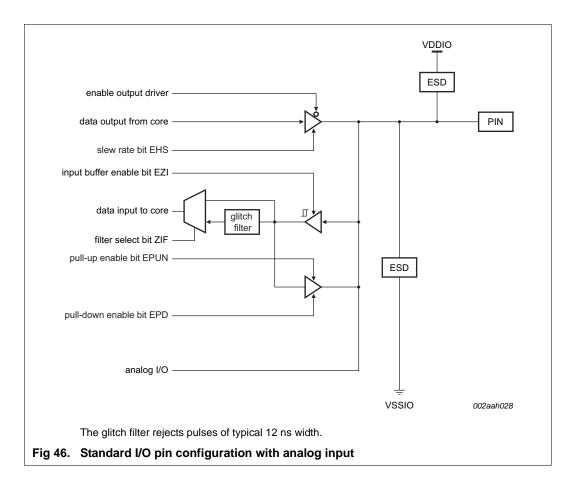

[2] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides digital I/O functions with TTL levels and hysteresis; normal drive strength.

- [3] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides digital I/O functions with TTL levels, and hysteresis; high drive strength.

- [4] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides high-speed digital I/O functions with TTL levels and hysteresis.

- [5] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input or output (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V). When configured as an ADC input or DAC output, the pin is not 5 V tolerant and the digital section of the pad must be disabled by setting the pin to an input function and disabling the pull-up resistor through the pin's SFSP register.

- [6] 5 V tolerant transparent analog pad.

- [7] For maximum load  $C_L = 6.5 \,\mu$ F and maximum pull-down resistance  $R_{pd} = 80 \,k\Omega$ , the VBUS signal takes about 2 s to fall from VBUS = 5 V to VBUS = 0.2 V when it is no longer driven.

- [8] Transparent analog pad. Not 5 V tolerant.

- [9] Pad provides USB functions 5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V. It is designed in accordance with the USB specification, revision 2.0 (Full-speed and Low-speed mode only).

- [10] Open-drain 5 V tolerant digital I/O pad, compatible with I2C-bus Fast Mode Plus specification. This pad requires an external pull-up to provide output functionality. When power is switched off, this pin connected to the I2C-bus is floating and does not disturb the I2C lines.

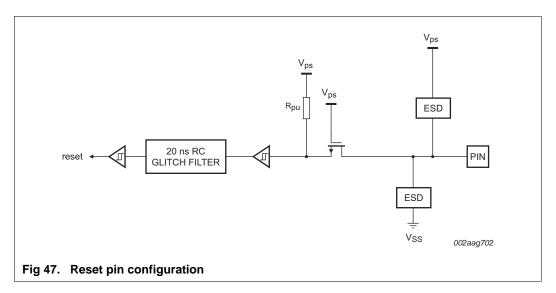

- [11] 5 V tolerant pad with 20 ns glitch filter; provides digital I/O functions with open-drain output and hysteresis.

- [12] On the TFBGA100 package, VPP is internally connected to VDDIO.

- [13] On the LQFP144 package, VSSIO and VSS are connected to a common ground plane.

- [14] On the TFBGA100 package, VSS is internally connected to VSSIO.

32-bit ARM Cortex-M4/M0 microcontroller

### 7. Functional description

### 7.1 Architectural overview

The ARM Cortex-M4 includes three AHB-Lite buses: the system bus, the I-CODE bus, and the D-code bus. The I-CODE and D-code core buses allow for concurrent code and data accesses from different slave ports.

The LPC43S50/S30/S20 use a multi-layer AHB matrix to connect the ARM Cortex-M4 buses and other bus masters to peripherals in a flexible manner that optimizes performance by allowing peripherals that are on different slaves ports of the matrix to be accessed simultaneously by different bus masters.

An ARM Cortex-M0 co-processor is included in the LPC43S50/S30/S20, capable of off-loading the main ARM Cortex-M4 application processor. Most peripheral interrupts are connected to both processors. The processors communicate with each other via an interprocessor communication protocol.

### 7.2 ARM Cortex-M4 processor

The ARM Cortex-M4 CPU incorporates a 3-stage pipeline, uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals, and includes an internal prefetch unit that supports speculative branching. The ARM Cortex-M4 supports single-cycle digital signal processing and SIMD instructions. A hardware floating-point processor is integrated in the core. The processor includes an NVIC with up to 53 interrupts.

### 7.3 ARM Cortex-M0 coprocessor

The ARM Cortex-M0 is a general purpose, 32-bit microprocessor, which offers high performance and very low-power consumption. The ARM Cortex-M0 co-processor uses a 3-stage pipeline von-Neumann architecture and a small but powerful instruction set providing high-end processing hardware. The co-processor incorporates an NVIC with 32 interrupts.

### 7.4 Interprocessor communication

The ARM Cortex-M4 and ARM Cortex-M0 interprocessor communication is based on using shared SRAM as mailbox and one processor raising an interrupt on the other processor's NVIC, for example after it has delivered a new message in the mailbox. The receiving processor can reply by raising an interrupt on the sending processor's NVIC to acknowledge the message.

### 32-bit ARM Cortex-M4/M0 microcontroller

- 16 DMA request lines.

- Single DMA and burst DMA request signals. Each peripheral connected to the DMA Controller can assert either a burst DMA request or a single DMA request. The DMA burst size is set by programming the DMA Controller.

- Memory-to-memory, memory-to-peripheral, peripheral-to-memory, and peripheral-to-peripheral transfers are supported.

- Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

- Hardware DMA channel priority.

- AHB slave DMA programming interface. The DMA Controller is programmed by writing to the DMA control registers over the AHB slave interface.

- Two AHB bus masters for transferring data. These interfaces transfer data when a DMA request goes active. Master 1 can access memories and peripherals, master 0 can access memories only.

- 32-bit AHB master bus width.

- Incrementing or non-incrementing addressing for source and destination.

- Programmable DMA burst size. The DMA burst size can be programmed to more efficiently transfer data.

- Internal four-word FIFO per channel.

- Supports 8, 16, and 32-bit wide transactions.

- Big-endian and little-endian support. The DMA Controller defaults to little-endian mode on reset.

- An interrupt to the processor can be generated on a DMA completion or when a DMA error has occurred.

- Raw interrupt status. The DMA error and DMA count raw interrupt status can be read prior to masking.

### 7.17.3 SPI Flash Interface (SPIFI)

The SPI Flash Interface allows low-cost serial flash memories to be connected to the ARM Cortex-M4 processor with little performance penalty compared to parallel flash devices with higher pin count.

After a few commands configure the interface at startup, the entire flash content is accessible as normal memory using byte, halfword, and word accesses by the processor and/or DMA channels. Simple sequences of commands handle erasing and programming.

Many serial flash devices use a half-duplex command-driven SPI protocol for device setup and initialization and then move to a half-duplex, command-driven 4-bit protocol for normal operation. Different serial flash vendors and devices accept or require different commands and command formats. SPIFI provides sufficient flexibility to be compatible with common flash devices and includes extensions to help insure compatibility with future devices.

#### 7.17.3.1 Features

• Interfaces to serial flash memory in the main memory map.

### 32-bit ARM Cortex-M4/M0 microcontroller

Active mode and sleep mode apply to the state of the core. In a dual-core system, either core can be in active or sleep mode independently of the other core.

If the core is in Active mode, it is fully operational and can access peripherals and memories as configured by software. If the core is in Sleep mode, it receives no clocks, but peripherals and memories remain running.

Either core can enter sleep mode from active mode independently of the other core and while the other core remains in active mode or is in sleep mode.

Power-down modes apply to the entire system. In the Power-down modes, both cores and all peripherals except for peripherals in the always-on power domain are shut down. Memories can remain powered for retaining memory contents as defined by the individual power-down mode.

Either core in active mode can put the part into one of the three power down modes if the core is enabled to do so. If both cores are enabled for putting the system into power-down, then the system enters power-down only once both cores have received a WFI or WFE instruction.

Wake-up from sleep mode is caused by an interrupt or event in the core's NVIC. The interrupt is captured in the NVIC and an event is captured in the Event router. Both cores can wake up from sleep mode independently of each other.

Wake-up from the Power-down modes, Deep-sleep, Power-down, and Deep power-down, is caused by an event on the WAKEUP pins or an event from the RTC or alarm timer.

When waking up from Deep power-down mode, the part resets and attempts to boot.

### 7.23 Serial Wire Debug/JTAG

Debug and trace functions are integrated into the ARM Cortex-M4. Serial wire debug and trace functions are supported in addition to a standard JTAG debug and parallel trace functions. The ARM Cortex-M4 is configured to support up to eight breakpoints and four watch points.

Remark: Serial Wire Debug is supported for the ARM Cortex-M4 only,

The ARM Cortex-M0 coprocessor supports JTAG debug. A standard ARM Cortex-compliant debugger can debug the ARM Cortex-M4 and the ARM Cortex-M0 cores separately or both cores simultaneously.

**Remark:** In order to debug the ARM Cortex-M0, release the M0 reset by software in the RGU block.

32-bit ARM Cortex-M4/M0 microcontroller

| Symbol              | Parameter                     | Conditions                                                                                     |      | Min                            | Typ[1]                | Max                           | Unit |

|---------------------|-------------------------------|------------------------------------------------------------------------------------------------|------|--------------------------------|-----------------------|-------------------------------|------|

| I <sub>BAT</sub>    | battery supply current        | V <sub>DD(REG)(3V3)</sub> = 3.3 V;<br>V <sub>BAT</sub> = 3.6 V                                 | [8]  |                                |                       |                               |      |

|                     |                               | deep-sleep mode                                                                                |      | -                              | 2                     | -                             | μA   |

|                     |                               | power-down mode                                                                                | [8]  | -                              | 2                     | -                             | μA   |

|                     |                               | deep power-down<br>mode                                                                        | [8]  | -                              | 2                     | -                             | μA   |

| I <sub>DD(IO)</sub> | I/O supply current            | deep sleep mode                                                                                | -    | -                              | 1                     | -                             | μA   |

| (-)                 |                               | power-down mode                                                                                | -    | -                              | 1                     | -                             | μA   |

|                     |                               | deep power-down mode                                                                           | [9]  | -                              | 0.05                  | -                             | μA   |

| I <sub>DDA</sub>    | Analog supply current         | on pin VDDA;                                                                                   | [11] | -                              | 0.4                   | -                             |      |

|                     |                               | deep sleep mode                                                                                |      |                                |                       |                               | μA   |

|                     |                               | power-down mode                                                                                | [11] | -                              | 0.4                   | -                             | μA   |

|                     |                               | deep power-down<br>mode                                                                        | [11] | -                              | 0.007                 | -                             | μA   |

| RESET,RTC           | _ALARM, WAKEUPn pins          |                                                                                                |      |                                |                       |                               |      |

| V <sub>IH</sub>     | HIGH-level input<br>voltage   |                                                                                                | [10] | 0.8 × (V <sub>ps</sub> – 0.35) | -                     | 5.5                           | V    |

| V <sub>IL</sub>     | LOW-level input voltage       |                                                                                                | [10] | 0                              | -                     | 0.3 × (V <sub>ps</sub> – 0.1) | V    |

| V <sub>hys</sub>    | hysteresis voltage            |                                                                                                | [10] | $0.05 \times (V_{ps} - 0.35)$  | -                     | -                             | V    |

| Vo                  | output voltage                |                                                                                                | [10] | -                              | V <sub>ps</sub> - 0.2 | -                             | V    |

| Standard I/C        | D pins - normal drive strengt | h                                                                                              |      | I                              |                       |                               |      |

| CI                  | input capacitance             |                                                                                                |      | -                              | -                     | 2                             | pF   |

| ILL                 | LOW-level leakage current     | V <sub>I</sub> = 0 V; on-chip pull-up<br>resistor disabled                                     |      | -                              | 3                     | -                             | nA   |

| I <sub>LH</sub>     | HIGH-level leakage current    | V <sub>I</sub> = V <sub>DD(IO)</sub> ; on-chip<br>pull-down resistor<br>disabled               |      | -                              | 3                     | -                             | nA   |

|                     |                               | V <sub>I</sub> = 5 V                                                                           |      | -                              | -                     | 20                            | nA   |

| I <sub>OZ</sub>     | OFF-state output current      | $V_O = 0 V$ to $V_{DD(IO)}$ ;<br>on-chip pull-up/down<br>resistors disabled;<br>absolute value |      | -                              | 3                     | -                             | nA   |

| VI                  | input voltage                 | pin configured to provide<br>a digital function;                                               |      | 0                              | -                     | 5.5                           | V    |

|                     |                               | $V_{DD(IO)} \ge 2.2 \text{ V}$ $V_{DD(IO)} = 0 \text{ V}$                                      |      | 0                              |                       | 3.6                           | V    |

| M                   |                               | (-)                                                                                            |      | 0                              | -                     |                               | V    |

| Vo                  | output voltage                | output active                                                                                  |      |                                | -                     | V <sub>DD(IO)</sub>           |      |

| V <sub>IH</sub>     | HIGH-level input<br>voltage   |                                                                                                |      | $0.7 \times V_{DD(IO)}$        | -                     | 5.5                           | V    |

| V <sub>IL</sub>     | LOW-level input voltage       |                                                                                                |      | 0                              | -                     | $0.3 \times V_{DD(IO)}$       | V    |

| V <sub>hys</sub>    | hysteresis voltage            |                                                                                                |      | 0.1 ×<br>V <sub>DD(IO)</sub>   | -                     | -                             | V    |

### Table 10. Static characteristics ... continued

Product data sheet

LPC43S50\_S30\_S20

All information provided in this document is subject to legal disclaimers.

### 32-bit ARM Cortex-M4/M0 microcontroller

#### Table 24. Dynamic characteristics: SSP pins in SPI mode

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 2.2 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}; 2.7 \text{ V} \le V_{DD(IO)} \le 3.6 \text{ V}; C_L = 20 \text{ pF. Sampled at } 10 \text{ \% and } 90 \text{ \% of the signal level; EHS} = 1 \text{ for all pins. Simulated values.}$

| Symbol           | Parameter  | Conditions                        | Min                            | Тур                      | Max | Unit |

|------------------|------------|-----------------------------------|--------------------------------|--------------------------|-----|------|

| t <sub>lag</sub> | lag time   | continuous transfer mode          | $0.5T_{cy(clk)} + 0.2$         | -                        | -   | ns   |

| 1                |            | SPI mode; CPOL = 0;<br>CPHA = 0   |                                |                          |     |      |

|                  |            | SPI mode; CPOL = 0;<br>CPHA = 1   | $T_{cy(clk)}$ + 0.2            | -                        | -   | ns   |

|                  |            | SPI mode; CPOL = 1;<br>CPHA = 0   | $0.5 \times T_{cy(clk)} + 0.2$ | -                        | -   | ns   |

|                  |            | SPI mode; CPOL = 1;<br>CPHA = 1   | $T_{cy(clk)}$ + 0.2            | -                        | -   | ns   |

|                  |            | synchronous serial frame mode     | $T_{cy(clk)}$ + 0.2            | -                        | -   | ns   |

|                  |            | microwire frame format            | $0.5 	imes T_{cy(clk)}$        | -                        | -   | ns   |

| t <sub>d</sub>   | delay time | continuous transfer mode          | -                              | $0.5\times T_{cy(clk)}$  | -   | ns   |

|                  |            | SPI mode; CPOL = 0;<br>CPHA = $0$ |                                |                          |     |      |

|                  |            | SPI mode; CPOL = 0;<br>CPHA = 1   | -                              | n/a                      | -   | ns   |

|                  |            | SPI mode; CPOL = 1;<br>CPHA = 0   | -                              | $0.5 \times T_{cy(clk)}$ | -   | ns   |

|                  |            | SPI mode; CPOL = 1;<br>CPHA = 1   | -                              | n/a                      | -   | ns   |

|                  |            | synchronous serial frame mode     | -                              | T <sub>cy(clk)</sub>     | -   | ns   |

|                  |            | microwire frame format            | -                              | n/a                      | -   | ns   |

[1] T<sub>cy(clk)</sub> = (SSPCLKDIV × (1 + SCR) × CPSDVSR) / f<sub>main</sub>. The clock cycle time derived from the SPI bit rate T<sub>cy(clk)</sub> is a function of the main clock frequency f<sub>main</sub>, the SSP peripheral clock divider (SSPCLKDIV), the SSP SCR parameter (specified in the SSP0CR0 register), and the SSP CPSDVSR parameter (specified in the SSP clock prescale register).

$$\label{eq:constraint} \begin{split} [2] \quad T_{cy(clk)} \geq 12 \times T_{cy(PCLK)}. \end{split}$$

#### 32-bit ARM Cortex-M4/M0 microcontroller

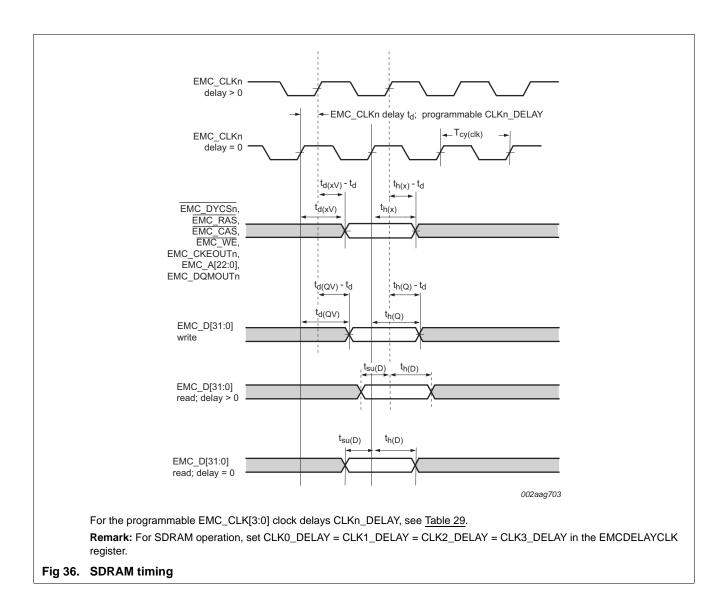

### 11.15 External memory interface

#### Table 27. Dynamic characteristics: Static asynchronous external memory interface

$C_L = 22 \text{ pF}$  for EMC\_Dn  $C_L = 20 \text{ pF}$  for all others;  $T_{amb} = -40 \text{ °C}$  to +85 °C;  $2.2 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}$ ; 2.7  $\text{V} \le V_{DD(IO)} \le 3.6 \text{ V}$ ; values guaranteed by design. Timing parameters are given for single memory access cycles. In a normal read operation, the EMC changes the address while CS is asserted resulting in multiple memory accesses.

| Symbol                | Parameter <sup>[1]</sup>     | Conditions |            | Min                                                                                      | Тур | Max                                                                                      | Unit |

|-----------------------|------------------------------|------------|------------|------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------|------|

| Read cycl             | e parameters                 | 1          |            |                                                                                          |     |                                                                                          |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time |            |            | -3.1                                                                                     | -   | 1.6                                                                                      | ns   |

| t <sub>CSLOEL</sub>   | CS LOW to OE LOW time        |            | [2]        | $-0.6 + T_{cy(clk)} \times$<br>WAITOEN                                                   | -   | $\begin{array}{l} \textbf{1.3 + T}_{cy(clk)} \times \\ \textbf{WAITOEN} \end{array}$     | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time       | PB = 1     |            | -0.7                                                                                     | -   | 1.8                                                                                      | ns   |

| t <sub>OELOEH</sub>   | OE LOW to OE HIGH time       |            | [2]        |                                                                                          | -   | $\begin{array}{c} -0.4 + \\ (WAITRD - \\ WAITOEN + 1) \times \\ T_{cy(clk)} \end{array}$ | ns   |

| t <sub>am</sub>       | memory access time           |            |            | -                                                                                        | -   | −16 +<br>(WAITRD −<br>WAITOEN +1) ×<br>T <sub>cy(clk)</sub>                              | ns   |

| t <sub>h(D)</sub>     | data input hold time         |            |            | -16                                                                                      | -   | -                                                                                        | ns   |

| t <sub>CSHBLSH</sub>  | CS HIGH to BLS HIGH time     | PB = 1     |            | -0.4                                                                                     | -   | 1.9                                                                                      | ns   |

| t <sub>CSHOEH</sub>   | CS HIGH to OE HIGH time      |            |            | -0.4                                                                                     | -   | 1.4                                                                                      | ns   |

| t <sub>OEHANV</sub>   | OE HIGH to address invalid   | PB = 1     |            | -2.0                                                                                     | -   | 2.6                                                                                      | ns   |

| t <sub>CSHEOR</sub>   | CS HIGH to end of read time  |            | [3]        | -2.0                                                                                     | -   | 0                                                                                        | ns   |

| t <sub>CSLSOR</sub>   | CS LOW to start of read time |            | [4]        | 0                                                                                        | -   | 1.8                                                                                      | ns   |

| Write cycl            | e parameters                 | l          |            |                                                                                          | 4   |                                                                                          |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time |            |            | -3.1                                                                                     | -   | 1.6                                                                                      | ns   |

| t <sub>CSLDV</sub>    | CS LOW to data valid time    |            |            | -3.1                                                                                     | -   | 1.5                                                                                      | ns   |

| t <sub>CSLWEL</sub>   | CS LOW to WE LOW time        | PB = 1     |            | -1.5                                                                                     | -   | 0.2                                                                                      | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time       | PB = 1     |            | -0.7                                                                                     | -   | 1.8                                                                                      | ns   |

| t <sub>WELWEH</sub>   | WE LOW to WE HIGH time       | PB = 1     | [2]        |                                                                                          | -   | $\begin{matrix} -0.4 + \\ (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} \end{matrix}$  | ns   |

| t <sub>WEHDNV</sub>   | WE HIGH to data invalid time | PB = 1     | [2]        | $-0.9 + T_{cy(clk)}$                                                                     | -   | 2.3 + T <sub>cy(clk)</sub>                                                               | ns   |

| t <sub>WEHEOW</sub>   | WE HIGH to end of write time | PB = 1     | [2]<br>[5] | -0.4 + T <sub>cy(clk)</sub>                                                              | -   | -0.3 + T <sub>cy(clk)</sub>                                                              | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW            | PB = 0     |            | -0.7                                                                                     | -   | 1.8                                                                                      | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS HIGH time     | PB = 0     | [2]        | $\begin{array}{c} -0.9 + \\ (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} \end{array}$ | -   | $\begin{matrix} -0.1 + \\ (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} \end{matrix}$  | ns   |

### **NXP Semiconductors**

### LPC43S50/S30/S20

32-bit ARM Cortex-M4/M0 microcontroller

32-bit ARM Cortex-M4/M0 microcontroller

### 11.16 USB interface

#### Table 30. Dynamic characteristics: USB0 and USB1 pins (full-speed)

$C_L = 50 \text{ pF}; R_{pu} = 1.5 \text{ k}\Omega \text{ on } D + \text{ to } V_{DD(IO)}; 3.0 \text{ V} \le V_{DD(IO)} \le 3.6 \text{ V}.$

| Symbol             | Parameter                                                   | Conditions                              |     | Min   | Тур | Max    | Unit |

|--------------------|-------------------------------------------------------------|-----------------------------------------|-----|-------|-----|--------|------|

| t <sub>r</sub>     | rise time                                                   | 10 % to 90 %                            |     | 4     | -   | 20     | ns   |

| t <sub>f</sub>     | fall time                                                   | 10 % to 90 %                            |     | 4     | -   | 20     | ns   |

| t <sub>FRFM</sub>  | differential rise and fall time matching                    | t <sub>r</sub> / t <sub>f</sub>         |     | 90    | -   | 111.11 | %    |

| V <sub>CRS</sub>   | output signal crossover voltage                             |                                         |     | 1.3   | -   | 2.0    | V    |

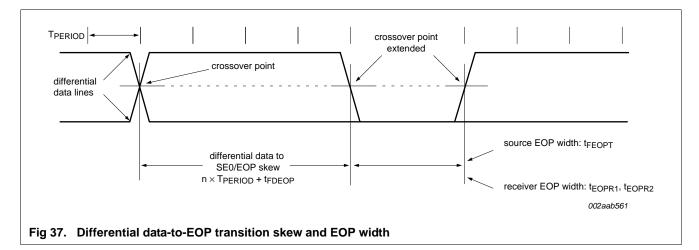

| t <sub>FEOPT</sub> | source SE0 interval of EOP                                  | see Figure 37                           |     | 160   | -   | 175    | ns   |

| t <sub>FDEOP</sub> | source jitter for differential transition to SE0 transition | see Figure 37                           |     | -2    | -   | +5     | ns   |

| t <sub>JR1</sub>   | receiver jitter to next transition                          |                                         |     | -18.5 | -   | +18.5  | ns   |

| t <sub>JR2</sub>   | receiver jitter for paired transitions                      | 10 % to 90 %                            |     | -9    | -   | +9     | ns   |

| t <sub>EOPR1</sub> | EOP width at receiver                                       | must reject as<br>EOP; see<br>Figure 37 | [1] | 40    | -   | -      | ns   |

| t <sub>EOPR2</sub> | EOP width at receiver                                       | must accept as<br>EOP; see<br>Figure 37 | [1] | 82    | -   | -      | ns   |

[1] Characterized but not implemented as production test. Guaranteed by design.