Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 53                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 24x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-QFP                                                                  |

| Supplier Device Package    | 64-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr32acfuer |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 13.8.3 ESCI Control Register 3                    | 160   |

|---------------------------------------------------|-------|

| 13.8.4 ESCI Status Register 1                     |       |

| 13.8.5 ESCI Status Register 2                     |       |

| 13.8.6 ESCI Data Register                         |       |

| 13.8.7 ESCI Baud Rate Register                    |       |

| 13.8.8 ESCI Prescaler Register                    |       |

| 13.9 ESCI Arbiter                                 |       |

| 13.9.1 ESCI Arbiter Control Register              |       |

| 13.9.2 ESCI Arbiter Data Register                 |       |

| 13.9.3 Bit Time Measurement                       |       |

| 13.9.4 Arbitration Mode                           |       |

| 7 I Dillator Mode                                 |       |

| Chapter 14                                        |       |

| System Integration Module (SIM)                   |       |

| 14.1 Introduction                                 |       |

| 14.2 SIM Bus Clock Control and Generation         | . 186 |

| 14.2.1 Bus Timing                                 |       |

| 14.2.2 Clock Startup from POR or LVI Reset        |       |

| 14.2.3 Clocks in Stop Mode and Wait Mode          | . 186 |

| 14.3 Reset and System Initialization              | . 187 |

| 14.3.1 External Pin Reset                         |       |

| 14.3.2 Active Resets from Internal Sources        |       |

| 14.3.2.1 Power-On Reset                           |       |

| 14.3.2.2 Computer Operating Properly (COP) Reset  |       |

| 14.3.2.3 Illegal Opcode Reset                     |       |

| 14.3.2.4 Illegal Address Reset                    |       |

| 14.3.2.5 Low-Voltage Inhibit (LVI) Reset          |       |

| 14.3.2.6 Monitor Mode Entry Module Reset (MODRST) |       |

| 14.4 SIM Counter                                  |       |

| 14.4.1 SIM Counter During Power-On Reset          |       |

| 14.4.2 SIM Counter During Stop Mode Recovery      |       |

| 14.4.3 SIM Counter and Reset States               |       |

| 14.5 Exception Control                            |       |

| 14.5.1 Interrupts                                 |       |

| 14.5.1.1 Hardware Interrupts                      |       |

| 14.5.1.2 SWI Instruction                          |       |

| 14.5.1.3 Interrupt Status Registers               |       |

| 14.5.2 Reset                                      |       |

| 14.5.3 Break Interrupts                           |       |

| 14.5.4 Status Flag Protection in Break Mode       |       |

| 14.6 Low-Power Modes                              |       |

| 14.6.1 Wait Mode                                  |       |

| 14.6.2 Stop Mode                                  |       |

| 14.7 SIM Registers                                |       |

| 14.7.1 Break Status Register                      |       |

| 14.7.2 SIM Reset Status Register                  | . 199 |

| 14 / 3 Dieak Flag Coulto Benister                 | / III |

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

| Addr.         | Register Name                                 | _                | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0   |  |  |

|---------------|-----------------------------------------------|------------------|---------------------------|------------|--------|-------------|----------------|--------------|-------|---------|--|--|

| \$0024        | TIM1 Counter Modulo<br>Register Low (T1MODL)  | Read:<br>Write:  | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0   |  |  |

|               | See page 236.                                 |                  | 1                         | 1          | 1      | 1           | 1              | 1            | 1     | 1       |  |  |

|               | TIM1 Channel 0 Status and                     | Read:            | CH0F                      | CH0IE      | MS0B   | MS0A        | ELS0B          | ELS0A        | TOV0  | CH0MAX  |  |  |

| \$0025        | Control Register (T1SC0)                      | Write:           | 0                         | OFIOIL     | WIOOD  | WOOA        | LLOOD          | LLOUA        | 1000  | OHOWAX  |  |  |

|               | See page 237.                                 | Reset:           | 0                         | 0          | 0      | 0           | 0              | 0            | 0     | 0       |  |  |

| \$0026        | TIM1 Channel 0<br>Register High (T1CH0H)      | Read:<br>Write:  | Bit 15                    | 14         | 13     | 12          | 11             | 10           | 9     | Bit 8   |  |  |

|               | See page 240.                                 | Reset:           |                           |            |        | Indetermina | te after reset |              |       |         |  |  |

| \$0027        | TIM1 Channel 0<br>Register Low (T1CH0L)       | Read:<br>Write:  | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0   |  |  |

| ,             | See page 240.                                 | Reset:           |                           |            |        | Indetermina | te after reset |              |       |         |  |  |

|               | TIM1 Channel 1 Status and                     | Read:            | CH1F                      | OLIVE      | 0      | 14044       | FLOAD          | El 04 A      | TO)// | CULANAN |  |  |

| \$0028        | Control Register (T1SC1)                      | Write:           | 0                         | CH1IE      |        | - MS1A      | ELS1B          | ELS1A        | TOV1  | CH1MAX  |  |  |

|               | See page 237.                                 | Reset:           | 0                         | 0          | 0      | 0           | 0              | 0            | 0     | 0       |  |  |

| \$0029        | TIM1 Channel 1<br>Register High (T1CH1H)      | Read:<br>Write:  | Bit 15                    | 14         | 13     | 12          | 11             | 10           | 9     | Bit 8   |  |  |

|               | See page 240.                                 | Reset:           | Indeterminate after reset |            |        |             |                |              |       |         |  |  |

| \$002A        | TIM1 Channel 1<br>Register Low (T1CH1L)       | Read:<br>Write:  | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0   |  |  |

|               | See page 240.                                 | Reset:           | Indeterminate after reset |            |        |             |                |              |       |         |  |  |

|               | TIM2 Status and Control                       | Read:            | TOF                       | TOIE       | TSTOP  | 0           | 0              | PS2          | PS1   | PS0     |  |  |

| \$002B        | Register (T2SC)                               | Write:           | 0                         | TOIL       | 10101  | TRST        |                | 1 02         | 101   | 1 00    |  |  |

|               | See page 237.                                 | Reset:           | 0                         | 0          | 1      | 0           | 0              | 0            | 0     | 0       |  |  |

|               | TIM2 Counter                                  | Read:            | Bit 15                    | 14         | 13     | 12          | 11             | 10           | 9     | Bit 8   |  |  |

| \$002C        | Register High (T2CNTH)<br>See page 235.       | Write:           |                           |            |        |             |                |              |       |         |  |  |

|               | Gee page 200.                                 | Reset:           | 0                         | 0          | 0      | 0           | 0              | 0            | 0     | 0       |  |  |

| ф000 <b>D</b> | TIM2 Counter                                  | Read:            | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0   |  |  |

| \$002D        | Register Low (T2CNTL)<br>See page 235.        | Write:<br>Reset: | 0                         | 0          | 0      | 0           |                | 0            | 0     | 0       |  |  |

|               |                                               | Read:            |                           | I          | T U    | T           | 0              | 0            | I     | T       |  |  |

| \$002E        | TIM2 Counter Modulo<br>Register High (T2MODH) | Write:           | Bit 15                    | 14         | 13     | 12          | 11             | 10           | 9     | Bit 8   |  |  |

|               | See page 236.                                 | Reset:           | 1                         | 1          | 1      | 1           | 1              | 1            | 1     | 1       |  |  |

| \$002F        | TIM2 Counter Modulo<br>Register Low (T2MODL)  | Read:<br>Write:  | Bit 7                     | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0   |  |  |

|               | See page 236.                                 | Reset:           | 1                         | 1          | 1      | 1           | 1              | 1            | 1     | 1       |  |  |

|               |                                               |                  |                           | = Unimplem | nented | R = Reserve | ed             | U = Unaffect | ed    |         |  |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 9)

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

| Addr.  | Register Name                            |                 | Bit 7  | 6                   | 5      | 4           | 3                   | 2            | 1      | Bit 0   |  |

|--------|------------------------------------------|-----------------|--------|---------------------|--------|-------------|---------------------|--------------|--------|---------|--|

|        | ADC Status and Control                   | Read:           | COCO   | AIEN                | ADCO   | ADCH4       | ADCH3               | ADCH2        | ADCH1  | ADCH0   |  |

| \$003C | Register (ADSCR)                         | Write:          | R      | AIEN                | ADCO   | ADCI 14     | ADOIR               | ADCI12       | ADOITI | ADCITIO |  |

|        | See page 65.                             | Reset:          | 0      | 0                   | 0      | 1           | 1                   | 1            | 1      | 1       |  |

|        | ADC Data High Register                   | Read:           | 0      | 0                   | 0      | 0           | 0                   | 0            | AD9    | AD8     |  |

| \$003D | (ADRH)                                   | Write:          |        |                     |        |             |                     |              |        |         |  |

|        | See page 67.                             | Reset:          |        | Unaffected by reset |        |             |                     |              |        |         |  |

|        | ADC Data Low Register                    | Read:           | AD7    | AD6                 | AD5    | AD4         | A3                  | AD2          | AD1    | AD0     |  |

| \$003E | (ADRL)                                   | Write:          |        |                     |        |             |                     |              |        |         |  |

|        | See page 67.                             | Reset:          |        | ı                   | ı      | Unaffecte   | d by reset          | ı            | I      | 1       |  |

|        | ADC Clock Register                       | Read:           | ADIV2  | ADIV1               | ADIV0  | ADICLK      | MODE1               | MODE0        | R      | 0       |  |

| \$003F | (ADCLK)<br>See page 69.                  | Write:          |        |                     |        |             |                     |              |        |         |  |

|        | Gee page 09.                             | Reset:          | 0      | 0                   | 0      | 0           | 0                   | 1            | 0      | 0       |  |

| \$0440 | Port F Data Register<br>(PTF)            | Read:<br>Write: | PTF7   | PTF6                | PTF5   | PTF4        | PTAF3               | PTF2         | PTF1   | PTF0    |  |

|        | See page 147.                            | Reset:          |        |                     |        | Unaffecte   | d by reset          |              |        |         |  |

| \$0441 | Port G Data Register<br>(PTG)            | Read:<br>Write: | PTG7   | PTG6                | PTG5   | PTG4        | PTG3                | PTG2         | PTG1   | PTG0    |  |

|        | See page 149.                            | Reset:          |        | Unaffected by reset |        |             |                     |              |        |         |  |

| \$0444 | Data Direction Register F<br>(DDRF)      | Read:<br>Write: | DDRF7  | DDRF6               | DDRF5  | DDRF4       | DDRF3               | DDRF2        | DDRF1  | DDRF0   |  |

|        | See page 148.                            | Reset:          | 0      | 0                   | 0      | 0           | 0                   | 0            | 0      | 0       |  |

| \$0445 | Data Direction Register G (DDRG)         | Read:<br>Write: | DDRG7  | DDRG6               | DDRG5  | DDRG4       | DDRG3               | DDRG2        | DDRG1  | DDRG0   |  |

|        | See page 150.                            | Reset:          | 0      | 0                   | 0      | 0           | 0                   | 0            | 0      | 0       |  |

| \$0448 | Keyboard Interrupt Polarity Register     | Read:<br>Write: | KBIP7  | KBIP6               | KBIP5  | KBIP4       | KBIP3               | KBIP2        | KBIP1  | KBIP0   |  |

|        | (INTKBIPR)<br>See page 119.              | Reset:          | 0      | 0                   | 0      | 0           | 0                   | 0            | 0      | 0       |  |

|        | TIM2 Channel 2 Status and                | Read:           | CH2F   |                     |        |             |                     |              |        |         |  |

| \$0456 | Control Register (T2SC2)                 | Write:          | 0      | CH2IE               | MS2B   | MS2A        | ELS2B               | ELS2A        | TOV2   | CH2MAX  |  |

|        | See page 255.                            | Reset:          | 0      | 0                   | 0      | 0           | 0                   | 0            | 0      | 0       |  |

| \$0457 | TIM2 Channel 2<br>Register High (T2CH2H) | Read:<br>Write: | Bit 15 | 14                  | 13     | 12          | 11                  | 10           | 9      | Bit 8   |  |

| +2.0.  | See page 258.                            | Reset:          |        |                     |        | Indetermina | L<br>te after reset | <u> </u>     |        |         |  |

| \$0458 | TIM2 Channel 2<br>Register Low (T2CH2L)  | Read:<br>Write: | Bit 7  | 6                   | 5      | 4           | 3                   | 2            | 1      | Bit 0   |  |

|        | See page 258.                            | Reset:          |        |                     |        | Indetermina | te after reset      |              |        |         |  |

|        |                                          |                 |        | = Unimplem          | nented | R = Reserve | d                   | U = Unaffect | ed     |         |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 6 of 9)

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

Programming tools are available from Freescale Semiconductor. Contact your local representative for more information.

#### NOTE

A security feature prevents viewing of the FLASH contents. (1)

## 2.6.2 FLASH-1 Control and Block Protect Registers

The FLASH-1 array has two registers that control its operation, the FLASH-1 control register (FL1CR) and the FLASH-1 block protect register (FL1BPR).

## 2.6.2.1 FLASH-1 Control Register

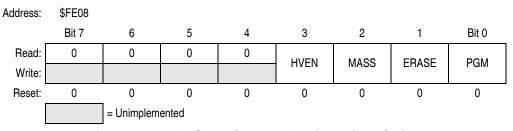

The FLASH-1 control register (FL1CR) controls FLASH program and erase operations.

Figure 2-3. FLASH-1 Control Register (FL1CR)

## **HVEN** — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

Setting this read/write bit configures the FLASH-1 array for mass erase operation.

- 1 = MASS erase operation selected

- 0 = MASS erase operation unselected

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

## **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

- **E.** The time between each FLASH address change (step 7 to step 7), or the time between the last FLASH address programmed to clearing the PGM bit (step 7 to step 10) must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

- **F.** Be cautious when programming the FLASH-2 array to ensure that non-FLASH locations are not used as the address that is written to when selecting either the desired row address range in step 3 of the algorithm or the byte to be programmed in step 7 of the algorithm.

#### 2.7.7 Low-Power Modes

The WAIT and STOP instructions will place the MCU in low power-consumption standby modes.

#### 2.7.7.1 Wait Mode

Putting the MCU into wait mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly; however, no memory activity will take place since the CPU is inactive.

The WAIT instruction should not be executed while performing a program or erase operation on the FLASH. Wait mode will suspend any FLASH program/erase operations and leave the memory in a standby mode.

#### 2.7.7.2 Stop Mode

Putting the MCU into stop mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly; however, no memory activity will take place since the CPU is inactive.

The STOP instruction should not be executed while performing a program or erase operation on the FLASH. Stop mode will suspend any FLASH program/erase operations and leave the memory in a standby mode.

#### NOTE

Standby mode is the power saving mode of the FLASH module, in which all internal control signals to the FLASH are inactive and the current consumption of the FLASH is minimum.

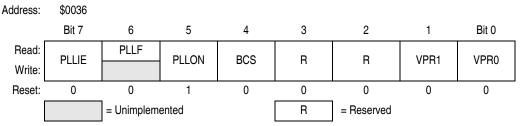

## 4.5.1 PLL Control Register

The PLL control register (PCTL) contains the interrupt enable and flag bits, the on/off switch, the base clock selector bit, and the VCO power-of-two range selector bits.

Figure 4-4. PLL Control Register (PCTL)

## PLLIE — PLL Interrupt Enable Bit

This read/write bit enables the PLL to generate an interrupt request when the LOCK bit toggles, setting the PLL flag, PLLF. When the AUTO bit in the PLL bandwidth control register (PBWC) is clear, PLLIE cannot be written and reads as 0. Reset clears the PLLIE bit.

- 1 = PLL interrupts enabled

- 0 = PLL interrupts disabled

## PLLF — PLL Interrupt Flag Bit

This read-only bit is set whenever the LOCK bit toggles. PLLF generates an interrupt request if the PLLIE bit also is set. PLLF always reads as 0 when the AUTO bit in the PLL bandwidth control register (PBWC) is clear. Clear the PLLF bit by reading the PLL control register. Reset clears the PLLF bit.

- 1 = Change in lock condition

- 0 = No change in lock condition

#### NOTE

Do not inadvertently clear the PLLF bit. Any read or read-modify-write operation on the PLL control register clears the PLLF bit.

### PLLON — PLL On Bit

This read/write bit activates the PLL and enables the VCO clock, CGMVCLK. PLLON cannot be cleared if the VCO clock is driving the base clock, CGMOUT (BCS = 1). (See 4.3.8 Base Clock Selector Circuit.) Reset sets this bit so that the loop can stabilize as the MCU is powering up.

- 1 = PLL on

- 0 = PLL off

### **BCS** — Base Clock Select Bit

This read/write bit selects either the crystal oscillator output, CGMXCLK, or the VCO clock, CGMVCLK, as the source of the CGM output, CGMOUT. CGMOUT frequency is one-half the frequency of the selected clock. BCS cannot be set while the PLLON bit is clear. After toggling BCS, it may take up to three CGMXCLK and three CGMVCLK cycles to complete the transition from one source clock to the other. During the transition, CGMOUT is held in stasis. (See 4.3.8 Base Clock Selector Circuit.) Reset clears the BCS bit.

- 1 = CGMVCLK divided by two drives CGMOUT

- 0 = CGMXCLK divided by two drives CGMOUT

#### NOTE

PLLON and BCS have built-in protection that prevents the base clock selector circuit from selecting the VCO clock as the source of the base clock

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### Computer Operating Properly (COP) Module

The COP counter is a free-running 6-bit counter preceded by the 12-bit SIM counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 CGMXCLK cycles, depending on the state of the COP rate select bit, COPRS, in the configuration register. With a 262,128 CGMXCLK cycle overflow option, a 4.9152-MHz crystal gives a COP timeout period of 53.3 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the RST pin low for 32 CGMXCLK cycles and sets the COP bit in the reset status register (RSR).

In monitor mode, the COP is disabled if the  $\overline{RST}$  pin or the  $\overline{IRQ}$  is held at  $V_{TST}$ . During the break state,  $V_{TST}$  on the  $\overline{RST}$  pin disables the COP.

#### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

# 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

#### 6.3.1 CGMXCLK

CGMXCLK is the crystal oscillator output signal. CGMXCLK frequency is equal to the crystal frequency.

## 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

#### 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector. See 6.4 COP Control Register.

### 6.3.4 Power-On Reset

The power-on reset (POR) circuit clears the SIM counter 4096 CGMXCLK cycles after power-up.

### 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

## Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

## C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

- 1 = Carry out of bit 7

- 0 = No carry out of bit 7

# 7.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (document order number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about the architecture of the CPU.

## 7.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 7.5.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

#### 7.5.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 7.6 CPU During Break Interrupts

If a break module is present on the MCU, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD or with \$FEFC:\$FEFD in monitor mode

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the MCU to normal operation if the break interrupt has been deasserted.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## **Central Processor Unit (CPU)**

# Table 7-1. Instruction Set Summary (Sheet 5 of 6)

| Source                                                                                          | Operation                                                         | Description                                                                                                                                                                                                                     |   | Effect on CCR |          |   |          |   | Address<br>Mode                                     | Opcode                                           | Operand                                   | es                                   |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|----------|---|----------|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| Form                                                                                            | Operation                                                         | Boothplion                                                                                                                                                                                                                      | ٧ | Н             | I        | N | z        | С | Add                                                 | Opc                                              | Ope                                       | Cycles                               |

| PULA                                                                                            | Pull A from Stack                                                 | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                                              | - | -             | -        | - | -        | - | INH                                                 | 86                                               |                                           | 2                                    |

| PULH                                                                                            | Pull H from Stack                                                 | SP ← (SP + 1); Pull (H)                                                                                                                                                                                                         | - | -             | -        | - | -        | _ | INH                                                 | 8A                                               |                                           | 2                                    |

| PULX                                                                                            | Pull X from Stack                                                 | $SP \leftarrow (SP + 1); Pull (X)$                                                                                                                                                                                              | - | -             | _        | - | _        | _ | INH                                                 | 88                                               |                                           | 2                                    |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                    | Rotate Left through Carry                                         | b7 b0                                                                                                                                                                                                                           | ţ | _             | _        | 1 | 1        | 1 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X<br>ROR opr,SP                                    | Rotate Right through Carry                                        | b7 b0                                                                                                                                                                                                                           | 1 | _             | -        | 1 | 1        | Î | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| RSP                                                                                             | Reset Stack Pointer                                               | SP ← \$FF                                                                                                                                                                                                                       | - | -             | -        | - | -        | _ | INH                                                 | 9C                                               |                                           | 1                                    |

| RTI                                                                                             | Return from Interrupt                                             | $\begin{array}{l} SP \leftarrow (SP) + 1;  Pull  (CCR) \\ SP \leftarrow (SP) + 1;  Pull  (A) \\ SP \leftarrow (SP) + 1;  Pull  (X) \\ SP \leftarrow (SP) + 1;  Pull  (PCH) \\ SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array}$ | 1 | 1             | <b>‡</b> | ‡ | <b>1</b> | ‡ | INH                                                 | 80                                               |                                           | 7                                    |

| RTS                                                                                             | Return from Subroutine                                            | $SP \leftarrow SP + 1$ ; Pull (PCH)<br>$SP \leftarrow SP + 1$ ; Pull (PCL)                                                                                                                                                      | - | -             | -        | ı | ı        | _ | INH                                                 | 81                                               |                                           | 4                                    |

| SBC #opr<br>SBC opr<br>SBC opr,<br>SBC opr,X<br>SBC opr,X<br>SBC ,X<br>SBC opr,SP<br>SBC opr,SP | Subtract with Carry                                               | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                  | 1 | _             | _        | 1 | 1        | 1 | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A2<br>B2<br>C2<br>D2<br>E2<br>F2<br>9EE2<br>9ED2 |                                           | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| SEC                                                                                             | Set Carry Bit                                                     | C ← 1                                                                                                                                                                                                                           | - | -             | _        | _ | _        | 1 | INH                                                 | 99                                               |                                           | 1                                    |

| SEI                                                                                             | Set Interrupt Mask                                                | I ← 1                                                                                                                                                                                                                           | - | -             | 1        | _ | _        | _ | INH                                                 | 9B                                               |                                           | 2                                    |

| STA opr<br>STA opr<br>STA opr,X<br>STA opr,X<br>STA ,X<br>STA opr,SP<br>STA opr,SP              | Store A in M                                                      | M ← (A)                                                                                                                                                                                                                         | 0 | _             | _        | 1 | 1        | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | B7<br>C7<br>D7<br>E7<br>F7<br>9EE7<br>9ED7       | dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 3<br>4<br>4<br>3<br>2<br>4<br>5      |

| STHX opr                                                                                        | Store H:X in M                                                    | (M:M + 1) ← (H:X)                                                                                                                                                                                                               | 0 | -             | -        | 1 | 1        | - | DIR                                                 | 35                                               | dd                                        | 4                                    |

| STOP                                                                                            | Enable Interrupts, Stop Processing,<br>Refer to MCU Documentation | I ← 0; Stop Processing                                                                                                                                                                                                          | _ | -             | 0        | _ | _        | _ | INH                                                 | 8E                                               |                                           | 1                                    |

| STX opr<br>STX opr,<br>STX opr,X<br>STX opr,X<br>STX,X<br>STX opr,SP<br>STX opr,SP              | Store X in M                                                      | $M \leftarrow (X)$                                                                                                                                                                                                              | 0 | _             | -        | ‡ | ‡        | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | BF<br>CF<br>DF<br>EF<br>FF<br>9EEF<br>9EDF       |                                           | 3<br>4<br>4<br>3<br>2<br>4<br>5      |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB,X<br>SUB opr,SP<br>SUB opr,SP   | Subtract                                                          | $A \leftarrow (A) - (M)$                                                                                                                                                                                                        | 1 | -             | _        | ‡ | ‡        | ‡ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 |                                           | 23443245                             |

#### **Low-Power Modes**

# 10.4 Central Processor Unit (CPU)

## 10.4.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- · Disables the CPU clock

## 10.4.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 10.5 Clock Generator Module (CGM)

#### 10.5.1 Wait Mode

The clock generator module (CGM) remains active in wait mode. Before entering wait mode, software can disengage and turn off the PLL by clearing the BCS and PLLON bits in the PLL control register (PCTL). Less power-sensitive applications can disengage the PLL without turning it off. Applications that require the PLL to wake the MCU from wait mode also can deselect the PLL output without turning off the PLL.

## 10.5.2 **Stop Mode**

If the OSCENINSTOP bit in the CONFIG2 register is cleared (default), then the STOP instruction disables the CGM (oscillator and phase-locked loop) and holds low all CGM outputs (CGMXCLK, CGMOUT, and CGMINT).

If the OSCENINSTOP bit in the CONFIG2 register is set, then the phase locked loop is shut off, but the oscillator will continue to operate in stop mode.

# 10.6 Computer Operating Properly Module (COP)

## 10.6.1 Wait Mode

The COP remains active during wait mode. If COP is enabled, a reset will occur at COP timeout.

#### **10.6.2 Stop Mode**

Stop mode turns off the CGMXCLK input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

The STOP bit in the CONFIG1 register enables the STOP instruction. To prevent inadvertently turning off the COP with a STOP instruction, disable the STOP instruction by clearing the STOP bit.

#### **Low-Power Modes**

# 10.11 Serial Peripheral Interface Module (SPI)

#### 10.11.1 Wait Mode

The serial peripheral interface (SPI) module remains active in wait mode. Any enabled CPU interrupt request from the SPI module can bring the MCU out of wait mode.

If SPI module functions are not required during wait mode, reduce power consumption by disabling the SPI module before executing the WAIT instruction.

## 10.11.2 Stop Mode

The SPI module is inactive in stop mode. The STOP instruction does not affect SPI register states. SPI operation resumes after an external interrupt. If stop mode is exited by reset, any transfer in progress is aborted, and the SPI is reset.

# 10.12 Timer Interface Module (TIM1 and TIM2)

#### 10.12.1 Wait Mode

The timer interface modules (TIM) remain active in wait mode. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

## 10.12.2 Stop Mode

The TIM is inactive in stop mode. The STOP instruction does not affect register states or the state of the TIM counter. TIM operation resumes when the MCU exits stop mode after an external interrupt.

# 10.13 Timebase Module (TBM)

#### 10.13.1 Wait Mode

The timebase module (TBM) remains active after execution of the WAIT instruction. In wait mode, the timebase register is not accessible by the CPU.

If the timebase functions are not required during wait mode, reduce the power consumption by stopping the timebase before enabling the WAIT instruction.

#### 10.13.2 Stop Mode

The timebase module may remain active after execution of the STOP instruction if the oscillator has been enabled to operate during stop mode through the OSCENINSTOP bit in the CONFIG2 register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

If the oscillator has not been enabled to operate in stop mode, the timebase module will not be active during stop mode. In stop mode, the timebase register is not accessible by the CPU.

If the timebase functions are not required during stop mode, reduce the power consumption by stopping the timebase before enabling the STOP instruction.

#### **Enhanced Serial Communications Interface (ESCI) Module**

#### **AROVFL**— Arbiter Counter Overflow Bit

This read-only bit indicates an arbiter counter overflow. Clear AROVFL by writing any value to SCIACTL. Writing 0s to AM1 and AM0 resets the counter keeps it in this idle state. Reset clears AROVFL.

- 1 = Arbiter counter overflow has occurred

- 0 = No arbiter counter overflow has occurred

#### ARD8— Arbiter Counter MSB

This read-only bit is the MSB of the 9-bit arbiter counter. Clear ARD8 by writing any value to SCIACTL. Reset clears ARD8.

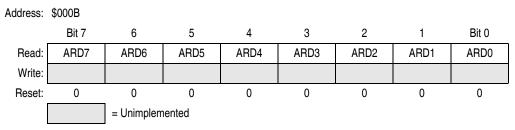

## 13.9.2 ESCI Arbiter Data Register

Figure 13-20. ESCI Arbiter Data Register (SCIADAT)

#### ARD7-ARD0 — Arbiter Least Significant Counter Bits

These read-only bits are the eight LSBs of the 9-bit arbiter counter. Clear ARD7–ARD0 by writing any value to SCIACTL. Writing 0s to AM1 and AM0 permanently resets the counter and keeps it in this idle state. Reset clears ARD7–ARD0.

#### 13.9.3 Bit Time Measurement

Two bit time measurement modes, described here, are available according to the state of ACLK.

- ACLK = 0 The counter is clocked with the bus clock divided by four. The counter is started when

a falling edge on the RxD pin is detected. The counter will be stopped on the next falling edge.

ARUN is set while the counter is running, AFIN is set on the second falling edge on RxD (for

instance, the counter is stopped). This mode is used to recover the received baud rate. See

Figure 13-21.

- 2. ACLK = 1 The counter is clocked with one half of the ESCI input clock generated by the ESCI prescaler. The counter is started when a 0 is detected on RxD (see Figure 13-22). A 0 on RxD on enabling the bit time measurement with ACLK = 1 leads to immediate start of the counter (see Figure 13-23). The counter will be stopped on the next rising edge of RxD. This mode is used to measure the length of a received break.

#### 13.9.4 Arbitration Mode

If AM[1:0] is set to 10, the arbiter module operates in arbitration mode. On every rising edge of SCI\_TxD (output of the ESCI module, internal chip signal), the counter is started. When the counter reaches \$38 (ACLK = 0) or \$08 (ACLK = 1), RxD is statically sensed. If in this case, RxD is sensed low (for example, another bus is driving the bus dominant) ALOST is set. As long as ALOST is set, the TxD pin is forced to 1, resulting in a seized transmission.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## Interrupt Status Register 1

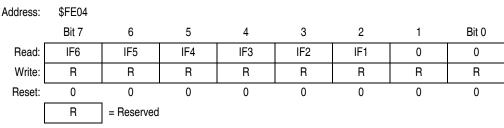

Figure 14-12. Interrupt Status Register 1 (INT1)

## IF6-IF1 — Interrupt Flags 1-6

These flags indicate the presence of interrupt requests from the sources shown in Table 14-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

## Bit 0 and Bit 1 — Always read 0

## Interrupt Status Register 2

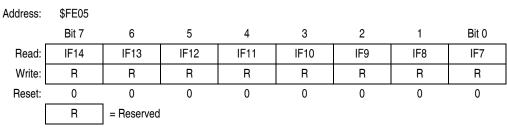

Figure 14-13. Interrupt Status Register 2 (INT2)

## IF14-IF7 — Interrupt Flags 14-7

These flags indicate the presence of interrupt requests from the sources shown in Table 14-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

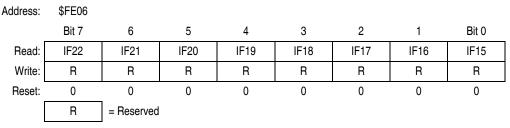

#### Interrupt Status Register 3

Figure 14-14. Interrupt Status Register 3 (INT3)

## IF22-IF15 — Interrupt Flags 22-15

These flags indicate the presence of an interrupt request from the source shown in Table 14-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

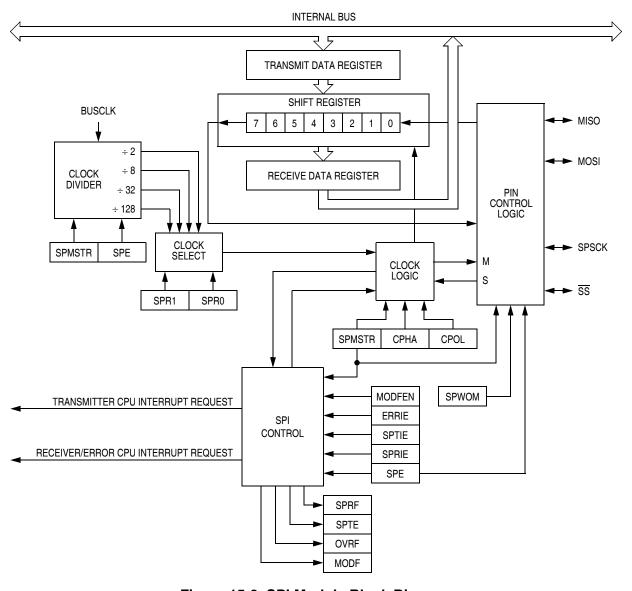

Figure 15-2. SPI Module Block Diagram

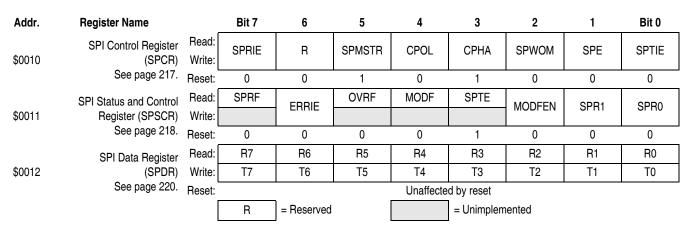

Figure 15-3. SPI I/O Register Summary

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

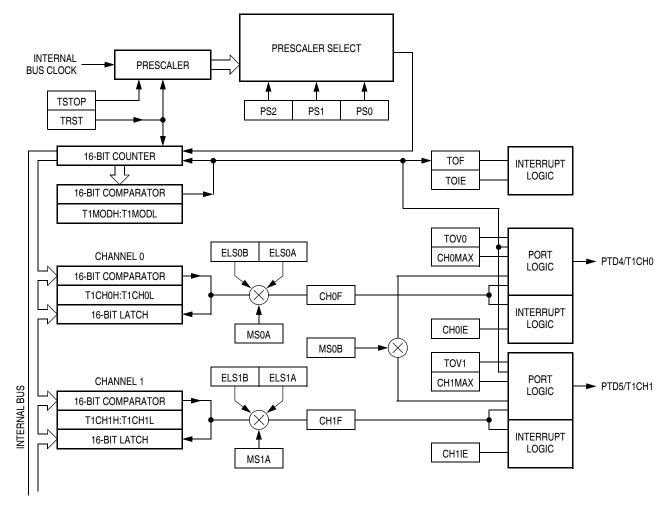

Figure 17-2. TIM1 Block Diagram

| Addr.                                                          | Register Name             |        | Bit 7  | 6          | 5      | 4      | 3      | 2     | 1     | Bit 0 |

|----------------------------------------------------------------|---------------------------|--------|--------|------------|--------|--------|--------|-------|-------|-------|

|                                                                | TIM1 Status and Control   | Read:  | TOF    | TOIE       | TSTOP  | 0      | 0      | PS2   | PS1   | PS0   |

| \$0020                                                         | Register (T1SC)           | Write: | 0      | IOIE       | 13101  | TRST   |        | F32   | 101   | F30   |

| See                                                            | See page 234.             | Reset: | 0      | 0          | 1      | 0      | 0      | 0     | 0     | 0     |

| TIM1 Counter Register High<br>\$0021 (T1CNTH)<br>See page 235. | Read:                     | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |       |

|                                                                | (T1CNTH)                  | Write: |        |            |        |        |        |       |       |       |

|                                                                | See page 235.             | Reset: | 0      | 0          | 0      | 0      | 0      | 0     | 0     | 0     |

|                                                                | TIM1 Counter Register Low | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

| \$0022                                                         | (T1CNTL)                  | Write: |        |            |        |        |        |       |       |       |

|                                                                | See page 235.             | Reset: | 0      | 0          | 0      | 0      | 0      | 0     | 0     | 0     |

|                                                                |                           |        |        | = Unimplen | nented |        |        |       |       |       |

Figure 17-3. TIM1 I/O Register Summary

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## PS[2:0] — Prescaler Select Bits

These read/write bits select one of the seven prescaler outputs as the input to the TIM1 counter as Table 17-1 shows. Reset clears the PS[2:0] bits.

| PS2 | PS1 | PS0 | TIM1 Clock Source       |  |  |  |

|-----|-----|-----|-------------------------|--|--|--|

| 0   | 0   | 0   | Internal bus clock ÷ 1  |  |  |  |

| 0   | 0   | 1   | Internal bus clock ÷ 2  |  |  |  |

| 0   | 1   | 0   | Internal bus clock ÷ 4  |  |  |  |

| 0   | 1   | 1   | Internal bus clock ÷ 8  |  |  |  |

| 1   | 0   | 0   | Internal bus clock ÷ 16 |  |  |  |

| 1   | 0   | 1   | Internal bus clock ÷ 32 |  |  |  |

| 1   | 1   | 0   | Internal bus clock ÷ 64 |  |  |  |

| 1   | 1   | 1   | Not available           |  |  |  |

**Table 17-1. Prescaler Selection**

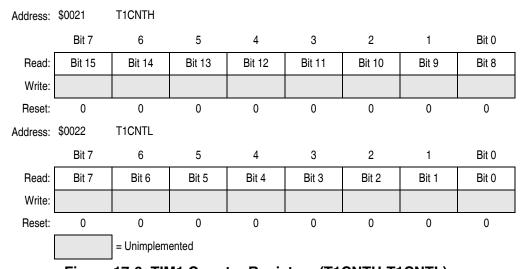

# 17.8.2 TIM1 Counter Registers

The two read-only TIM1 counter registers contain the high and low bytes of the value in the TIM1 counter. Reading the high byte (T1CNTH) latches the contents of the low byte (T1CNTL) into a buffer. Subsequent reads of T1CNTH do not affect the latched T1CNTL value until T1CNTL is read. Reset clears the TIM1 counter registers. Setting the TIM1 reset bit (TRST) also clears the TIM1 counter registers.

#### NOTE

If you read T1CNTH during a break interrupt, be sure to unlatch T1CNTL by reading T1CNTL before exiting the break interrupt. Otherwise, T1CNTL retains the value latched during the break.

Figure 17-6. TIM1 Counter Registers (T1CNTH:T1CNTL)

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

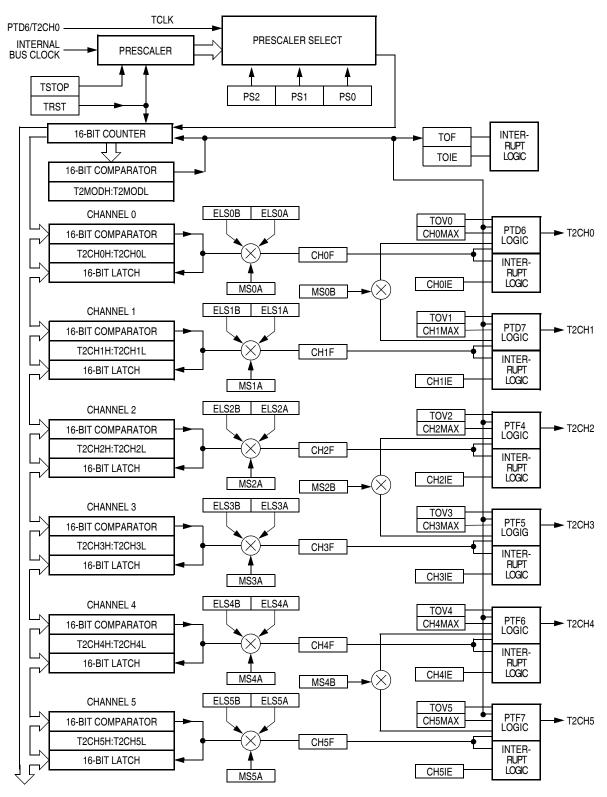

Figure 18-2. TIM2 Block Diagram

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

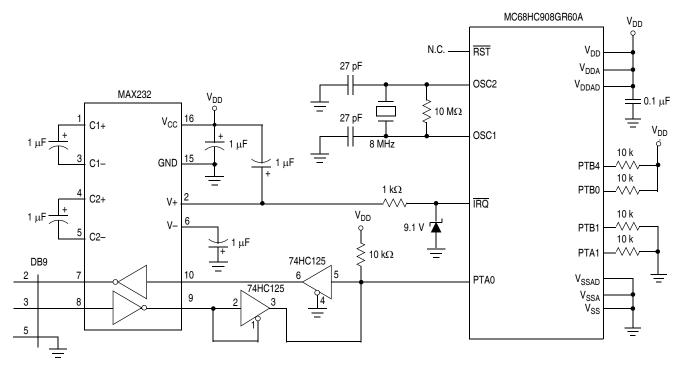

Figure 19-10. Normal Monitor Mode Circuit

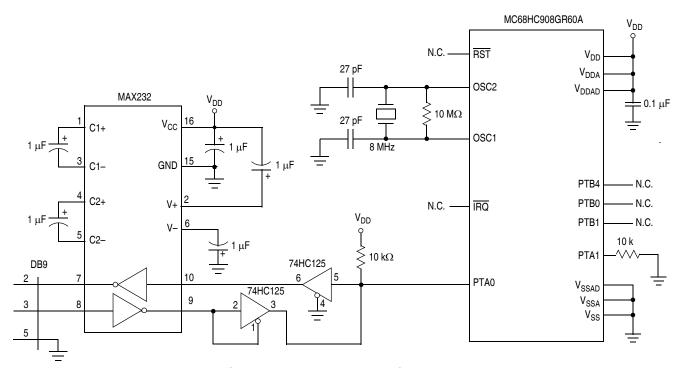

Figure 19-11. Forced Monitor Mode

#### **Electrical Specifications**

# 20.12 5.0-Volt SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                   | Min                                              | Max                                   | Unit             |

|----------------------------------|----------------------------------------------------------------------|------------------------------------------|--------------------------------------------------|---------------------------------------|------------------|

|                                  | Operating frequency<br>Master<br>Slave                               | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub> | f <sub>OP</sub> /128<br>dc                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz       |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub>                      | 2<br>1                                           | 128<br>—                              | t <sub>CYC</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                     | 1                                                | _                                     | t <sub>CYC</sub> |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                      | 1                                                | _                                     | t <sub>CYC</sub> |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub>                     | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns         |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub>                     | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns         |

| 6                                | Data setup time (inputs)  Master  Slave                              | t <sub>SU(M)</sub>                       | 30<br>30                                         |                                       | ns<br>ns         |

| 7                                | Data hold time (inputs) Master Slave                                 | t <sub>H(M)</sub>                        | 30<br>30                                         |                                       | ns<br>ns         |

| 8                                | Access time, slave <sup>(3)</sup> CPHA = 0 CPHA = 1                  | t <sub>A(CP0)</sub>                      | 0<br>0                                           | 40<br>40                              | ns<br>ns         |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                      | _                                                | 40                                    | ns               |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub> t <sub>V(S)</sub>      | _                                                | 50<br>50                              | ns<br>ns         |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub>                       | 0<br>0                                           |                                       | ns<br>ns         |

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5 288 Freescale Semiconductor

Numbers refer to dimensions in Figure 20-2 and Figure 20-3.

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins.

Time to data active from high-impedance state

Hold time to high-impedance state

With 100 pF on all SPI pins

# **Chapter 21 Ordering Information and Mechanical Specifications**

## 21.1 Introduction

This section contains ordering numbers for the MC68HC908GR60A and gives the dimensions for:

- 32-pin low-profile quad flat pack (case 873A)

- 48-pin low-profile quad flat pack (case 932-03)

- 64-pin quad flat pack (case 840B)

The following figures show the latest package drawings at the time of this publication. To make sure that you have the latest package specifications, contact your local Freescale Semiconductor Sales Office.

## 21.2 MC Order Numbers

**Table 21-1. MC Order Numbers**

| MC Order Number | Operating<br>Temperature Range | Package            |

|-----------------|--------------------------------|--------------------|

| MC908GR60ACFJ   | -40°C to +85°C                 | 32-pin low-profile |

| MC908GR60AVFJ   | -40°C to +105°C                | quad flat package  |

| MC908GR60AMFJ   | -40°C to +125°C                | (LQFP)             |

| MC908GR60ACFA   | -40°C to +85°C                 | 48-pin low-profile |

| MC908GR60AVFA   | -40°C to +105°C                | quad flat package  |

| MC908GR60AMFA   | -40°C to +125°C                | (LQFP)             |

| MC908GR60ACFU   | −40°C to +85°C                 | 64-pin guad flat   |

| MC908GR60AVFU   | -40°C to +105°C                | package            |

| MC908GR60AMFU   | -40°C to +125°C                | (QFP)              |

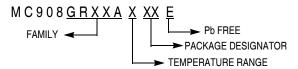

Temperature designators:

C = -40°C to +85°C

$V = -40^{\circ}C \text{ to } +105^{\circ}C$

$M = -40^{\circ}C \text{ to } + 125^{\circ}C$

Figure 21-1. Device Numbering System

# 21.3 Package Dimensions

Refer to the following pages for detailed package dimensions.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5