Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 37                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 24x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr32amfae |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

# Chapter 17 Timer Interface Module (TIM1)

| 17.1    | Introduction                              | 225 |

|---------|-------------------------------------------|-----|

| 17.2    | Features                                  | 225 |

| 17.3    | Functional Description                    | 225 |

| 17.3.1  | TIM1 Counter Prescaler                    |     |

| 17.3.2  | Input Capture                             | 228 |

| 17.3.3  | Output Compare                            |     |

| 17.3.3  |                                           |     |

| 17.3.3  |                                           |     |

| 17.3.4  | Pulse Width Modulation (PWM)              |     |

| 17.3.4  |                                           |     |

| 17.3.4  | 3                                         |     |

| 17.3.4. |                                           |     |

| 17.4    | Interrupts                                |     |

| 17.5    | Wait Mode                                 |     |

| 17.6    | TIM1 During Break Interrupts              | 233 |

| 17.7    | Input/Output Signals                      | 233 |

| 17.8    | Input/Output Registers                    |     |

| 17.8.1  | TIM1 Status and Control Register          |     |

| 17.8.2  | TIM1 Counter Registers                    |     |

| 17.8.3  | TIM1 Counter Modulo Registers             |     |

| 17.8.4  | TIM1 Channel Status and Control Registers |     |

| 17.8.5  | TIM1 Channel Registers                    | 239 |

|         | Chapter 18                                |     |

|         | Timer Interface Module (TIM2)             |     |

| 18.1    | Introduction                              | 241 |

| 18.2    | Features                                  | 241 |

| 18.3    | Functional Description                    | 241 |

| 18.3.1  | TIM2 Counter Prescaler                    |     |

| 18.3.2  | Input Capture                             | 246 |

| 18.3.3  | Output Compare                            | 246 |

| 18.3.3  |                                           |     |

| 18.3.3  | · ·                                       |     |

| 18.3.4  | Pulse Width Modulation (PWM)              |     |

| 18.3.4  | <b>5</b>                                  |     |

| 18.3.4  | 3                                         |     |

| 18.3.4  |                                           |     |

| 18.4    | Interrupts                                |     |

| 18.5    | Low-Power Modes                           |     |

| 18.5.1  | Wait Mode                                 |     |

| 18.5.2  | Stop Mode                                 |     |

| 18.6    | TIM2 During Break Interrupts              | 251 |

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

$V_{REFL}$  is the low reference supply for the ADC, and by default the  $V_{SSAD}/V_{REFL}$  pin should be connected to the same voltage potential as  $V_{SS}$ . See Chapter 3 Analog-to-Digital Converter (ADC).

## 1.5.8 Port A Input/Output (I/O) Pins (PTA7/KBD7/AD15-PTA0/KBD0/AD8)

PTA7–PTA0 are general-purpose, bidirectional I/O port pins. Any or all of the port A pins can be programmed to serve as keyboard interrupt pins or used as analog-to-digital inputs. PTA7–PTA4 are only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 12 Input/Output (I/O) Ports, Chapter 9 Keyboard Interrupt Module (KBI), and Chapter 3 Analog-to-Digital Converter (ADC).

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

## 1.5.9 Port B I/O Pins (PTB7/AD7-PTB0/AD0)

PTB7–PTB0 are general-purpose, bidirectional I/O port pins that can also be used for analog-to-digital converter (ADC) inputs. PTB7–PTB6 are only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 12 Input/Output (I/O) Ports and Chapter 3 Analog-to-Digital Converter (ADC).

## 1.5.10 Port C I/O Pins (PTC6-PTC0)

PTC6 and PTC5 are general-purpose, bidirectional I/O port pins.

PTC4–PTC0 are general-purpose, bidirectional I/O port pins that contain higher current sink/source capability. PTC6–PTC2 are only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 12 Input/Output (I/O) Ports.

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

# 1.5.11 Port D I/O Pins (PTD7/T2CH1-PTD0/SS)

PTD7–PTD0 are special-function, bidirectional I/O port pins. PTD3–PTD0 can be programmed to be serial peripheral interface (SPI) pins, while PTD7–PTD4 can be individually programmed to be timer interface module (TIM1 and TIM2) pins. PTD0 can be used to output a clock, MCLK. PTD7 is only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 17 Timer Interface Module (TIM1), Chapter 18 Timer Interface Module (TIM2), Chapter 15 Serial Peripheral Interface (SPI) Module, Chapter 12 Input/Output (I/O) Ports, and Chapter 5 Configuration Register (CONFIG).

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

#### 1.5.12 Port E I/O Pins (PTE5-PTE2, PTE1/RxD, and PTE0/TxD)

PTE5–PTE0 are general-purpose, bidirectional I/O port pins. PTE1 and PTE0 can also be programmed to be enhanced serial communications interface (ESCI) pins. PTE5–PTE2 are only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 13 Enhanced Serial Communications Interface (ESCI) Module and Chapter 12 Input/Output (I/O) Ports.

## 1.5.13 Port F I/O Pins (PTF7/T2CH5-PTF0)

PTF7–PTF4 are special-function, bidirectional I/O port pins that can be individually programmed to be timer interface module (TIM2) pins.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

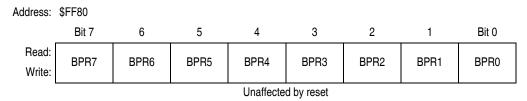

#### 2.6.2.2 FLASH-1 Block Protect Register

The FLASH-1 block protect register (FL1BPR) is implemented as a byte within the FLASH-1 memory; therefore, it can only be written during a FLASH programming sequence. The value in this register determines the starting location of the protected range within the FLASH-1 memory.

Figure 2-4. FLASH-1 Block Protect Register (FL1BPR)

## FL1BPR[7:0] — Block Protect Register Bits 7 to 0

These eight bits represent bits [14:7] of a 16-bit memory address. Bit 15 is a 1 and bits [6:0] are 0s.

The resultant 16-bit address is used for specifying the start address of the FLASH-1 memory for block protection. FLASH-1 is protected from this start address to the end of FLASH-1 memory at \$FFFF. With this mechanism, the protect start address can be \$XX00 and \$XX80 (128 byte page boundaries) within the FLASH-1 array.

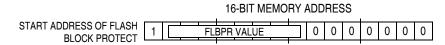

Figure 2-5. FLASH-1 Block Protect Start Address

**Table 2-2. FLASH-1 Protected Ranges**

| FL1BPR[7:0] | Protected Range    |

|-------------|--------------------|

| \$FF        | No protection      |

| \$FE        | \$FF00-\$FFFF      |

| \$FD<br>↓   | \$FE80–\$FFFF<br>↓ |

| \$0B        | \$8580-\$FFFF      |

| \$0A        | \$8500-\$FFFF      |

| \$09        | \$8480-\$FFFF      |

| \$08<br>↓   | \$8400–\$FFFF<br>↓ |

| \$04        | \$8200-\$FFFF      |

| \$03        | \$8180-\$FFFF      |

| \$02        | \$8100-\$FFFF      |

| \$01        | \$8080-\$FFFF      |

| \$00        | \$8000-\$FFFF      |

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

Memory

## 2.7 FLASH-2 Memory (FLASH-2)

This subsection describes the operation of the embedded FLASH-2 memory. This memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

## 2.7.1 Functional Description

The FLASH-2 memory is a non-continuous array consisting of a total of 29,822 bytes. An erased bit reads as a 1 and a programmed bit reads as a 0.

Memory in the FLASH-2 array is organized into rows within pages. There are two rows of memory per page with 64 bytes per row. The minimum erase block size is a single page,128 bytes. Programming is performed on a per-row basis, 64 bytes at a time. Program and erase operations are facilitated through control bits in the FLASH-2 control register (FL2CR). Details for these operations appear later in this subsection.

The FLASH-2 memory map consists of:

- \$0462–\$04FF: user memory (158 bytes)

- \$0980-\$1B7F: user memory (4608 bytes)

- \$1E20-\$7FFF: user memory (25056 bytes)

- \$FF81: FLASH-2 block protect register (FL2BPR)

#### NOTE

FL2BPR physically resides within FLASH-1 memory addressing space

\$FE08: FLASH-2 control register (FL2CR)

Programming tools are available from Freescale Semiconductor. Contact your local representative for more information.

#### NOTE

A security feature prevents viewing of the FLASH contents. (1)

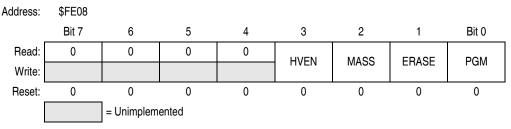

## 2.7.2 FLASH-2 Control and Block Protect Registers

The FLASH-2 array has two registers that control its operation, the FLASH-2 control register (FL2CR) and the FLASH-2 block protect register (FL2BPR).

#### 2.7.2.1 FLASH-2 Control Register

The FLASH-2 control register (FL2CR) controls FLASH-2 program and erase operations.

Figure 2-7. FLASH-2 Control Register (FL2CR)

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### **Clock Generator Module (CGM)**

In cases where desired bus frequency has some tolerance, choose  $f_{RCLK}$  to a value determined either by other module requirements (such as modules which are clocked by CGMXCLK), cost requirements, or ideally, as high as the specified range allows. See Chapter 20 Electrical Specifications. After choosing N, the actual bus frequency can be determined using equation in 2 above.

4. Select a VCO frequency multiplier, N.

$$N = round \left( \frac{f_{VCLKDES}}{f_{RCLK}} \right)$$

Calculate and verify the adequacy of the VCO and bus frequencies f<sub>VCLK</sub> and f<sub>BUS</sub>.

$$f_{VCLK} = (N) \times f_{RCLK}$$

$f_{BUS} = (f_{VCLK})/4$

6. Select the VCO's power-of-two range multiplier E, according to Table 4-2.

Table 4-2. Power-of-Two Range Selectors

| Frequency Range                    | E                |

|------------------------------------|------------------|

| 0 < f <sub>VCLK</sub> ≤ 8 MHz      | 0                |

| 8 MHz< f <sub>VCLK</sub> ≤ 16 MHz  | 1                |

| 16 MHz< f <sub>VCLK</sub> ≤ 32 MHz | 2 <sup>(1)</sup> |

<sup>1.</sup> Do not program E to a value of 3.

Select a VCO linear range multiplier, L, where f<sub>NOM</sub> = 71.4 kHz

$$L = Round \left( \frac{f_{VCLK}}{2^E x f_{NOM}} \right)$$

Calculate and verify the adequacy of the VCO programmed center-of-range frequency, f<sub>VRS</sub>. The

center-of-range frequency is the midpoint between the minimum and maximum frequencies

attainable by the PLL.

$$f_{VBS} = (L \times 2^E) f_{NOM}$$

9. For proper operation,

$$\left|f_{VRS} - f_{VCLK}\right| \le \frac{f_{NOM} \times 2^E}{2}$$

Verify the choice of N, E, and L by comparing f<sub>VCLK</sub> to f<sub>VRS</sub> and f<sub>VCLKDES</sub>. For proper operation, f<sub>VCLK</sub> must be within the application's tolerance of f<sub>VCLKDES</sub>, and f<sub>VRS</sub> must be as close as possible to f<sub>VCLK</sub>.

## NOTE

Exceeding the recommended maximum bus frequency or VCO frequency can crash the MCU.

**Clock Generator Module (CGM)**

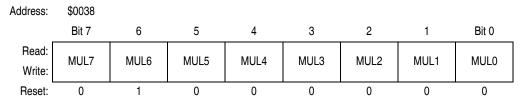

## 4.5.4 PLL Multiplier Select Register Low

The PLL multiplier select register low (PMSL) contains the programming information for the low byte of the modulo feedback divider.

Figure 4-7. PLL Multiplier Select Register Low (PMSL)

#### NOTE

For applications using 1–8 MHz reference frequencies this register must be reprogrammed before enabling the PLL. The reset value of this register will cause applications using 1–8 MHz reference frequencies to become unstable if the PLL is enabled without programming an appropriate value. The programmed value must not allow the VCO clock to exceed 32 MHz. See 4.3.6 Programming the PLL for detailed instructions on choosing the proper value for PMSL.

## MUL7-MUL0 — Multiplier Select Bits

These read/write bits control the low byte of the modulo feedback divider that selects the VCO frequency multiplier, N. (See 4.3.3 PLL Circuits and 4.3.6 Programming the PLL.) MUL7–MUL0 cannot be written when the PLLON bit in the PCTL is set. A value of \$0000 in the multiplier select registers configures the modulo feedback divider the same as a value of \$0001. Reset initializes the register to \$40 for a default multiply value of 64.

#### NOTE

The multiplier select bits have built-in protection such that they cannot be written when the PLL is on (PLLON = 1).

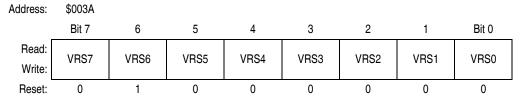

## 4.5.5 PLL VCO Range Select Register

The PLL VCO range select register (PMRS) contains the programming information required for the hardware configuration of the VCO.

Figure 4-8. PLL VCO Range Select Register (PMRS)

#### NOTE

Verify that the value of the PMRS register is appropriate for the given reference and VCO clock frequencies before enabling the PLL. See 4.3.6 Programming the PLL for detailed instructions on selecting the proper value for these control bits.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

# Table 7-1. Instruction Set Summary (Sheet 2 of 6)

| Source                                                                                                | Operation                                         | Description                                                                                                                                                                                                                                                                                                                                                                          |   |   | Effect<br>n CCR |   |   |   | Address<br>Mode                                                                              | Opcode                                       | Operand                                                              | es                                    |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-----------------|---|---|---|----------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|---------------------------------------|

| Form                                                                                                  | Operation                                         | Bescription                                                                                                                                                                                                                                                                                                                                                                          | ٧ | Н | I               | N | z | С | Add                                                                                          | Opc                                          | Ope                                                                  | Cycles                                |

| BHS rel                                                                                               | Branch if Higher or Same (Same as BCC)            | PC ← (PC) + 2 + rel? (C) = 0                                                                                                                                                                                                                                                                                                                                                         | _ | - | _               | - | _ | _ | REL                                                                                          | 24                                           | rr                                                                   | 3                                     |

| BIH rel                                                                                               | Branch if IRQ Pin High                            | PC ← (PC) + 2 + <i>rel</i> ? IRQ = 1                                                                                                                                                                                                                                                                                                                                                 | - | - | -               | - | - | - | REL                                                                                          | 2F                                           | rr                                                                   | 3                                     |

| BIL rel                                                                                               | Branch if IRQ Pin Low                             | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 0$                                                                                                                                                                                                                                                                                                                                  | _ | - | -               | - | _ | _ | REL                                                                                          | 2E                                           | rr                                                                   | 3                                     |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT,X<br>BIT opr,SP<br>BIT opr,SP         | Bit Test                                          | (A) & (M)                                                                                                                                                                                                                                                                                                                                                                            | 0 | _ | ı               | ‡ | 1 | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9ED5     |                                                                      | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5  |

| BLE opr                                                                                               | Branch if Less Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (Z)   (N \oplus V) = 1$                                                                                                                                                                                                                                                                                                                               | _ | - | -               | - | - | - | REL                                                                                          | 93                                           | rr                                                                   | 3                                     |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                     | $PC \leftarrow (PC) + 2 + rel? (C) = 1$                                                                                                                                                                                                                                                                                                                                              | _ | _ | -               | - | _ | _ | REL                                                                                          | 25                                           | rr                                                                   | 3                                     |

| BLS rel                                                                                               | Branch if Lower or Same                           | $PC \leftarrow (PC) + 2 + rel? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                                                                     | _ | - | _               | ı | - | - | REL                                                                                          | 23                                           | rr                                                                   | 3                                     |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                                                                     | - | - | -               | - | - | - | REL                                                                                          | 91                                           | rr                                                                   | 3                                     |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                    | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                                                              | _ | - | -               | - | - | - | REL                                                                                          | 2C                                           | rr                                                                   | 3                                     |

| BMI rel                                                                                               | Branch if Minus                                   | $PC \leftarrow (PC) + 2 + rel? (N) = 1$                                                                                                                                                                                                                                                                                                                                              | _ | - | _               | _ | _ | _ | REL                                                                                          | 2B                                           | rr                                                                   | 3                                     |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                      | $PC \leftarrow (PC) + 2 + rel? (I) = 1$                                                                                                                                                                                                                                                                                                                                              | _ | - | _               | _ | _ | _ | REL                                                                                          | 2D                                           | rr                                                                   | 3                                     |

| BNE rel                                                                                               | Branch if Not Equal                               | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                                                              | _ | _ | _               | _ | _ | _ | REL                                                                                          | 26                                           | rr                                                                   | 3                                     |

| BPL rel                                                                                               | Branch if Plus                                    | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                                                              | _ | - | _               | _ | _ | _ | REL                                                                                          | 2A                                           | rr                                                                   | 3                                     |

| BRA rel                                                                                               | Branch Always                                     | PC ← (PC) + 2 + <i>rel</i>                                                                                                                                                                                                                                                                                                                                                           | _ | - | _               | _ | _ | _ | REL                                                                                          | 20                                           | rr                                                                   | 3                                     |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                 | $PC \leftarrow (PC) + 3 + rel? (Mn) = 0$                                                                                                                                                                                                                                                                                                                                             | _ | _ | _               | _ | _ | 1 | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555                              |

| BRN rel                                                                                               | Branch Never                                      | PC ← (PC) + 2                                                                                                                                                                                                                                                                                                                                                                        | _ | _ | _               | - | _ | _ | REL                                                                                          | 21                                           | rr                                                                   | 3                                     |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                   | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                                                                | _ | _ | _               | _ | _ | ‡ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                             | Mn ← 1                                                                                                                                                                                                                                                                                                                                                                               | _ | _ | _               | _ | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C       | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                         | 4<br>4<br>4<br>4<br>4<br>4<br>4       |

| BSR rel                                                                                               | Branch to Subroutine                              | $ \begin{array}{l} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array} $                                                                                                                                                                                                         | _ | - | -               | - | _ | _ | REL                                                                                          | AD                                           | rr                                                                   | 4                                     |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                       | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel \; ? \; (A) - (M) = \$00 \\ \end{array}$ | _ | _ | -               | - | _ | _ | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 31<br>41<br>51<br>61<br>71<br>9E61           | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                      | 5<br>4<br>4<br>5<br>4<br>6            |

| CLC                                                                                                   | Clear Carry Bit                                   | C ← 0                                                                                                                                                                                                                                                                                                                                                                                | _ | - | _               | _ | _ | 0 | INH                                                                                          | 98                                           |                                                                      | 1                                     |

| CLI                                                                                                   | Clear Interrupt Mask                              | I ← 0                                                                                                                                                                                                                                                                                                                                                                                | _ | - | 0               | - | _ | _ | INH                                                                                          | 9A                                           |                                                                      | 2                                     |

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## 11.3.3 Voltage Hysteresis Protection

Once the LVI has triggered (by having  $V_{DD}$  fall below  $V_{TRIPF}$ ), the LVI will maintain a reset condition until  $V_{DD}$  rises above the rising trip point voltage,  $V_{TRIPR}$ . This prevents a condition in which the MCU is continually entering and exiting reset if  $V_{DD}$  is approximately equal to  $V_{TRIPF}$ .  $V_{TRIPR}$  is greater than  $V_{TRIPF}$  by the hysteresis voltage,  $V_{HYS}$ .

## 11.3.4 LVI Trip Selection

The LVI5OR3 bit in the configuration register selects whether the LVI is configured for 5-V or 3-V protection.

#### NOTE

The microcontroller is guaranteed to operate at a minimum supply voltage. The trip point ( $V_{TRIPF}$  [5 V] or  $V_{TRIPF}$  [3 V]) may be lower than this. See Chapter 20 Electrical Specifications for the actual trip point voltages.

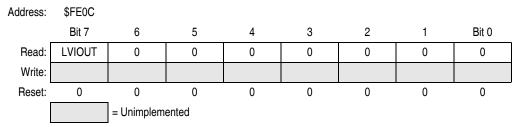

## 11.4 LVI Status Register

The LVI status register (LVISR) indicates if the  $V_{DD}$  voltage was detected below the  $V_{TRIPF}$  level.

Figure 11-3. LVI Status Register (LVISR)

## LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage (see Table 11-1). Reset clears the LVIOUT bit.

**Table 11-1. LVIOUT Bit Indication**

| V <sub>DD</sub>                                           | LVIOUT         |

|-----------------------------------------------------------|----------------|

| V <sub>DD</sub> > V <sub>TRIPR</sub>                      | 0              |

| $V_{DD} < V_{TRIPF}$                                      | 1              |

| V <sub>TRIPF</sub> < V <sub>DD</sub> < V <sub>TRIPR</sub> | Previous value |

# 11.5 LVI Interrupts

The LVI module does not generate interrupt requests.

## Input/Output (I/O) Ports

# **Table 12-1. Port Control Register Bits Summary (Continued)**

| Port | Bit | DDR   | Мо      | dule Control | Mod | lule Control | Pin          |

|------|-----|-------|---------|--------------|-----|--------------|--------------|

|      | 0   | DDRC0 |         |              |     |              | PTC0         |

|      | 1   | DDRC1 |         |              |     |              | PTC1         |

|      | 2   | DDRC2 |         |              |     |              | PTC2         |

| С    | 3   | DDRC3 |         |              | -   | _            | PTC3         |

|      | 4   | DDRC4 |         |              |     |              | PTC4         |

|      | 5   | DDRC5 |         |              |     |              | PTC5         |

|      | 6   | DDRC6 |         |              |     |              | PTC6         |

|      | 0   | DDRD0 |         |              |     |              | PTD0/SS/MCLK |

|      | 1   | DDRD1 | CDI     | CDE.         |     |              | PTD1/MISO    |

|      | 2   | DDRD2 | SPI     | SPE          |     |              | PTD2/MOSI    |

| -    | 3   | DDRD3 |         |              |     |              | PTD3/SPSCK   |

| D    | 4   | DDRD4 | TIN 44  | ELS0B:ELS0A  | _   | _            | PTD4/T1CH0   |

|      | 5   | DDRD5 | TIM1    | ELS1B:ELS1A  |     |              | PTD5/T1CH1   |

|      | 6   | DDRD6 | TIMO    | ELS0B:ELS0A  |     |              | PTD6/T2CH0   |

|      | 7   | DDRD7 | TIM2    | ELS1B:ELS1A  |     |              | PTD7/T2CH1   |

|      | 0   | DDRE0 | 001     | ENICOL       |     |              | PTE0/TxD     |

|      | 1   | DDRE1 | SCI     | ENSCI        |     |              | PTE1/RxD     |

| _    | 2   | DDRE2 |         |              |     |              | PTE2         |

| Е    | 3   | DDRE3 |         |              | _   | _            | PTE3         |

|      | 4   | DDRE4 |         |              |     |              | PTE4         |

|      | 5   | DDRE5 |         |              |     |              | PTE5         |

|      | 0   | DDRF0 |         |              |     |              | PTF0         |

|      | 1   | DDRF1 |         |              |     |              | PTF1         |

|      | 2   | DDRF2 |         |              |     |              | PTF2         |

| _    | 3   | DDRF3 |         |              |     |              | PTF3         |

| F    | 4   | DDRF4 |         | ELS2B:ELS2A  | _   | _            | PTF4/T2CH2   |

|      | 5   | DDRF5 | TIM2    | ELS3B:ELS3A  |     |              | PTF5/T2CH3   |

|      | 6   | DDRF6 | I IIVI∠ | ELS4B:ELS4A  |     |              | PTF6/T2CH4   |

|      | 7   | DDRF7 |         | ELS5B:ELS5A  | 1   |              | PTF7/T2CH5   |

|      | 0   | DDRG0 |         |              |     |              | PTG0/AD16    |

|      | 1   | DDRG1 |         |              |     |              | PTG1/AD17    |

|      | 2   | DDRG2 | ADC     |              |     |              | PTG2/AD18    |

| 0    | 3   | DDRG3 |         | ADCH[00:40]  |     |              | PTG3/AD19    |

| G    | 4   | DDRG4 |         | ADCH[23:16]  | _   | _            | PTG4/AD20    |

|      | 5   | DDRG5 |         |              |     |              | PTG5/AD21    |

|      | 6   | DDRG6 |         |              |     |              | PTG6/AD22    |

|      | 7   | DDRG7 |         |              |     |              | PTG7/AD23    |

## RE — Receiver Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver but does not affect receiver interrupt flag bits. Reset clears the RE bit.

- 1 = Receiver enabled

- 0 = Receiver disabled

#### NOTE

Writing to the RE bit is not allowed when the enable ESCI bit (ENSCI) is clear. ENSCI is in ESCI control register 1.

#### **RWU** — Receiver Wakeup Bit

This read/write bit puts the receiver in a standby state during which receiver interrupts are disabled. The WAKE bit in SCC1 determines whether an idle input or an address mark brings the receiver out of the standby state and clears the RWU bit. Reset clears the RWU bit.

- 1 = Standby state

- 0 = Normal operation

#### SBK — Send Break Bit

Setting and then clearing this read/write bit transmits a break character followed by a 1. The 1 after the break character guarantees recognition of a valid start bit. If SBK remains set, the transmitter continuously transmits break characters with no 1s between them. Reset clears the SBK bit.

- 1 = Transmit break characters

- 0 = No break characters being transmitted

#### NOTE

Do not toggle the SBK bit immediately after setting the SCTE bit. Toggling SBK before the preamble begins causes the ESCI to send a break character instead of a preamble.

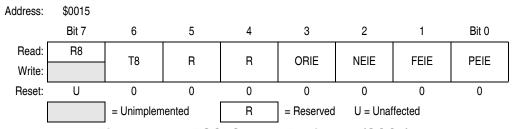

## 13.8.3 ESCI Control Register 3

ESCI control register 3 (SCC3):

- Stores the ninth ESCI data bit received and the ninth ESCI data bit to be transmitted.

- Enables these interrupts:

- Receiver overrun

- Noise error

- Framing error

- Parity error

Figure 13-12. ESCI Control Register 3 (SCC3)

#### R8 — Received Bit 8

When the ESCI is receiving 9-bit characters, R8 is the read-only ninth bit (bit 8) of the received character. R8 is received at the same time that the SCDR receives the other 8 bits.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### **Enhanced Serial Communications Interface (ESCI) Module**

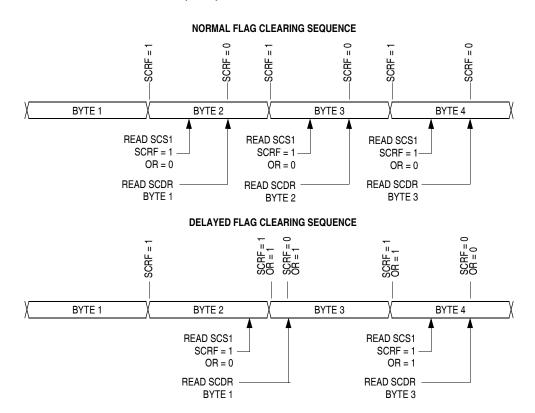

Figure 13-14. Flag Clearing Sequence

In applications that are subject to software latency or in which it is important to know which byte is lost due to an overrun, the flag-clearing routine can check the OR bit in a second read of SCS1 after reading the data register.

#### NF — Receiver Noise Flag Bit

This clearable, read-only bit is set when the ESCI detects noise on the RxD pin. NF generates an NF CPU interrupt request if the NEIE bit in SCC3 is also set. Clear the NF bit by reading SCS1 and then reading the SCDR. Reset clears the NF bit.

- 1 = Noise detected

- 0 = No noise detected

#### FE — Receiver Framing Error Bit

This clearable, read-only bit is set when a 0 is accepted as the stop bit. FE generates an ESCI error CPU interrupt request if the FEIE bit in SCC3 also is set. Clear the FE bit by reading SCS1 with FE set and then reading the SCDR. Reset clears the FE bit.

- 1 = Framing error detected

- 0 = No framing error detected

#### PE — Receiver Parity Error Bit

This clearable, read-only bit is set when the ESCI detects a parity error in incoming data. PE generates a PE CPU interrupt request if the PEIE bit in SCC3 is also set. Clear the PE bit by reading SCS1 with PE set and then reading the SCDR. Reset clears the PE bit.

- 1 = Parity error detected

- 0 = No parity error detected

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## 13.9.1 ESCI Arbiter Control Register

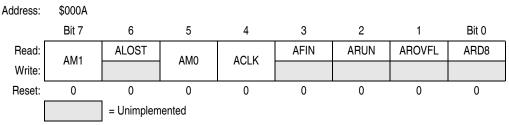

Figure 13-19. ESCI Arbiter Control Register (SCIACTL)

#### AM1 and AM0 — Arbiter Mode Select Bits

These read/write bits select the mode of the arbiter module as shown in Table 13-12. Reset clears AM1 and AM0.

Table 13-12. ESCI Arbiter Selectable Modes

| AM[1:0] | ESCI Arbiter Mode     |

|---------|-----------------------|

| 0 0     | Idle / counter reset  |

| 0 1     | Bit time measurement  |

| 1 0     | Bus arbitration       |

| 1 1     | Reserved / do not use |

## **ALOST** — Arbitration Lost Flag

This read-only bit indicates loss of arbitration. Clear ALOST by writing a 0 to AM1. Reset clears ALOST.

#### **ACLK — Arbiter Counter Clock Select Bit**

This read/write bit selects the arbiter counter clock source. Reset clears ACLK.

- 1 = Arbiter counter is clocked with one half of the ESCI input clock generated by the ESCI prescaler

- 0 = Arbiter counter is clocked with the bus clock divided by four

## NOTE

For ACLK = 1, the arbiter input clock is driven from the ESCI prescaler. The prescaler can be clocked by either the bus clock or CGMXCLK depending on the state of the SCIBDSRC bit in CONFIG2.

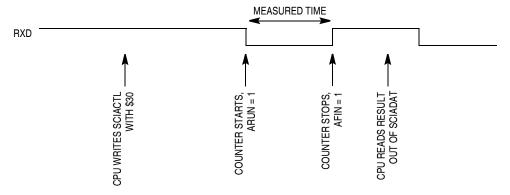

#### **AFIN— Arbiter Bit Time Measurement Finish Flag**

This read-only bit indicates bit time measurement has finished. Clear AFIN by writing any value to SCIACTL. Reset clears AFIN.

- 1 = Bit time measurement has finished

- 0 = Bit time measurement not yet finished

## **ARUN**— Arbiter Counter Running Flag

This read-only bit indicates the arbiter counter is running. Reset clears ARUN.

- 1 = Arbiter counter running

- 0 = Arbiter counter stopped

If SCI\_TxD senses 0 without having sensed a 0 before on RxD, the counter will be reset, arbitration operation will be restarted after the next rising edge of SCI\_TxD.

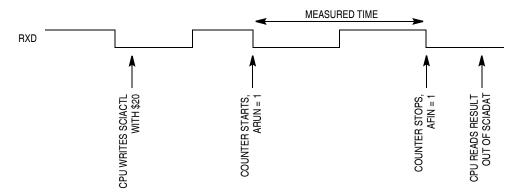

Figure 13-21. Bit Time Measurement with ACLK = 0

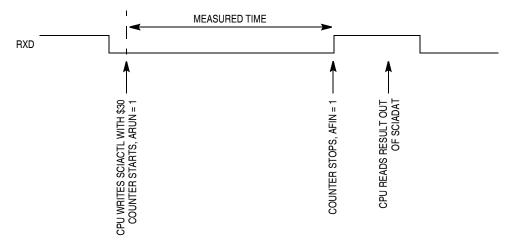

Figure 13-22. Bit Time Measurement with ACLK = 1, Scenario A

Figure 13-23. Bit Time Measurement with ACLK = 1, Scenario B

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

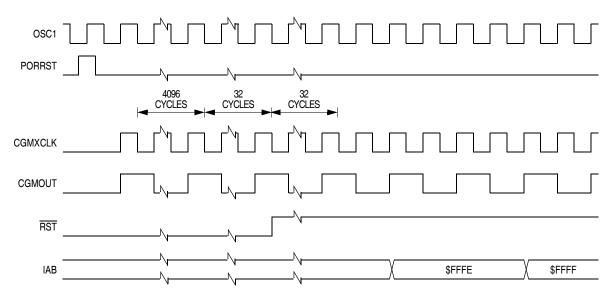

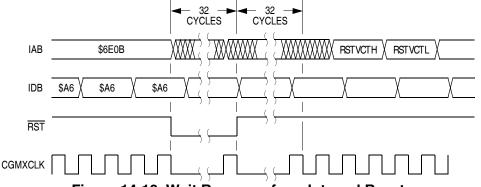

Figure 14-7. POR Recovery

## 14.3.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

If the stop enable bit, STOP, in the CONFIG1 register is 0, the SIM treats the STOP instruction as an illegal opcode and causes an illegal opcode reset. The SIM actively pulls down the  $\overline{RST}$  pin for all internal reset sources.

#### 14.3.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset. The SIM actively pulls down the  $\overline{RST}$  pin for all internal reset sources.

## 14.3.2.5 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the  $V_{TRIPF}$  voltage. The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RST) is asserted if the LVIPWRD and LVIRSTD bits in the CONFIG1 register are 0. The RST pin will be held low while the SIM counter counts out 4096 + 32 CGMXCLK cycles after  $V_{DD}$  rises above  $V_{TRIPR}$ . Thirty-two CGMXCLK cycles later, the CPU is released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the RST pin for all internal reset sources.

## 14.3.2.6 Monitor Mode Entry Module Reset (MODRST)

The monitor mode entry module reset (MODRST) asserts its output to the SIM when monitor mode is entered in the condition where the reset vectors are erased (\$FF) (see 19.3.1.1 Normal Monitor Mode). When MODRST gets asserted, an internal reset occurs. The SIM actively pulls down the RST pin for all internal reset sources.

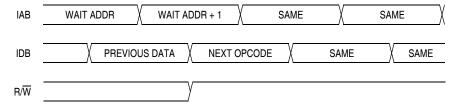

## 14.6.1 Wait Mode

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 14-16 shows the timing for wait mode entry.

A module that is active during wait mode can wakeup the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode also can be exited by a reset or break. A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the SIM break status register (BSR). If the COP disable bit, COPD, in the CONFIG1 register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

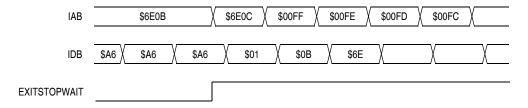

Note: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 14-16. Wait Mode Entry Timing

Figure 14-17 and Figure 14-18 show the timing for WAIT recovery.

Note: EXITSTOPWAIT = RST pin, CPU interrupt, or break interrupt

Figure 14-17. Wait Recovery from Interrupt or Break

Figure 14-18. Wait Recovery from Internal Reset

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### **Development Support**

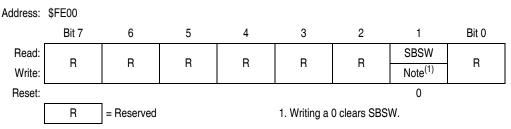

## 19.2.2.3 Break Status Register

The break status register (BSR) contains a flag to indicate that a break caused an exit from wait mode. This register is only used in emulation mode.

Figure 19-7. Break Status Register (BSR)

## SBSW — SIM Break Stop/Wait

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it.

- 1 = Wait mode was exited by break interrupt

- 0 = Wait mode was not exited by break interrupt

## 19.2.2.4 Break Flag Control Register

The break control register (BFCR) contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 19-8. Break Flag Control Register (BFCR)

## **BCFE** — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

#### 19.2.3 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power- consumption standby modes. If enabled, the break module will remain enabled in wait and stop modes. However, since the internal address bus does not increment in these modes, a break interrupt will never be triggered.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

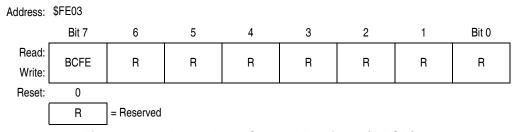

# 20.7 5.0-Volt Control Timing

| Characteristic <sup>(1)</sup>                                              | Symbol                              | Min     | Max     | Unit             |

|----------------------------------------------------------------------------|-------------------------------------|---------|---------|------------------|

| Frequency of operation Crystal option External clock option <sup>(2)</sup> | fosc                                | 1<br>dc | 8<br>32 | MHz              |

| Internal operating frequency                                               | f <sub>OP</sub> (f <sub>Bus</sub> ) | _       | 8       | MHz              |

| Internal clock period (1/f <sub>OP</sub> )                                 | t <sub>CYC</sub>                    | 125     | _       | ns               |

| RESET input pulse width low                                                | t <sub>RL</sub>                     | 100     | _       | ns               |

| IRQ interrupt pulse width low (edge-triggered)                             | t <sub>ILIH</sub>                   | 100     | _       | ns               |

| IRQ interrupt pulse period <sup>(3)</sup>                                  | t <sub>ILIL</sub>                   | Note 3  | _       | t <sub>CYC</sub> |

- 1.  $V_{SS}$  = 0 Vdc; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$  unless otherwise noted. 2. No more than 10% duty cycle deviation from 50%.

- 3. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1 t<sub>CYC</sub>.

# 20.8 3.3-Volt Control Timing

| Characteristic <sup>(1)</sup>                                              | Symbol                              | Min     | Max     | Unit             |

|----------------------------------------------------------------------------|-------------------------------------|---------|---------|------------------|

| Frequency of operation Crystal option External clock option <sup>(2)</sup> | fosc                                | 1<br>dc | 8<br>16 | MHz              |

| Internal operating frequency                                               | f <sub>OP</sub> (f <sub>Bus</sub> ) | _       | 4       | MHz              |

| Internal clock period (1/f <sub>OP</sub> )                                 | t <sub>CYC</sub>                    | 250     | _       | ns               |

| RESET input pulse width low                                                | t <sub>RL</sub>                     | 200     | _       | ns               |

| IRQ interrupt pulse width low (edge-triggered)                             | t <sub>ILIH</sub>                   | 200     | _       | ns               |

| IRQ interrupt pulse period <sup>(3)</sup>                                  | t <sub>ILIL</sub>                   | Note 3  | _       | t <sub>CYC</sub> |

- 1.  $V_{SS}$  = 0 Vdc; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$  unless otherwise noted. 2. No more than 10% duty cycle deviation from 50%.

- 3. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1 t<sub>CYC</sub>.

Figure 20-1. RST and IRQ Timing

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

- 1. Pin contains integrated pullup device.

- 2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

- 3. Higher current drive port pins

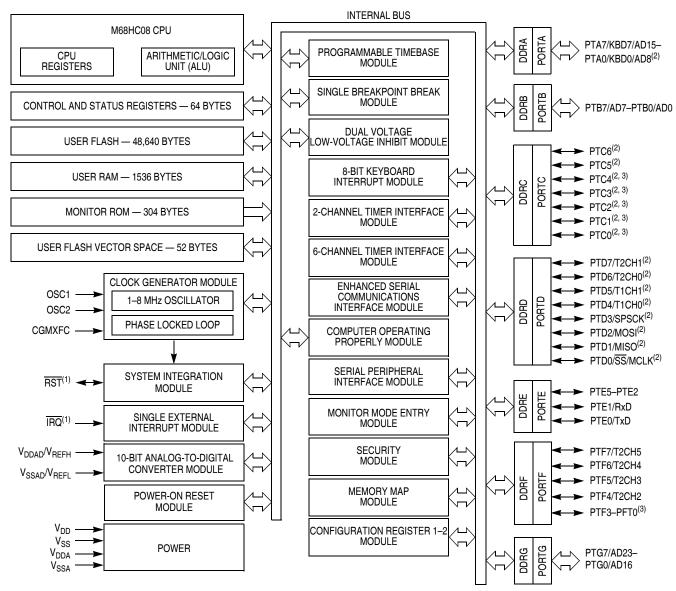

Figure A-1. MC68HC908GR48A Block Diagram