Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 53                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                |                                                                        |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 24x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-QFP                                                                 |

| Supplier Device Package    | 64-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr48amfue |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Chapter 4 Clock Generator Module (CGM)

| 4.1    | Introduction                                     | 71 |

|--------|--------------------------------------------------|----|

| 4.2    | Features                                         | 71 |

| 4.3    | Functional Description                           | 71 |

| 4.3.1  | Crystal Oscillator Circuit                       | 73 |

| 4.3.2  | Phase-Locked Loop Circuit (PLL)                  | 73 |

| 4.3.3  | PLL Circuits                                     |    |

| 4.3.4  | Acquisition and Tracking Modes                   | 74 |

| 4.3.5  | Manual and Automatic PLL Bandwidth Modes         |    |

| 4.3.6  | Programming the PLL                              | 75 |

| 4.3.7  | Special Programming Exceptions                   |    |

| 4.3.8  | Base Clock Selector Circuit                      | 77 |

| 4.3.9  | CGM External Connections                         | 78 |

| 4.4    | I/O Signals                                      |    |

| 4.4.1  | Crystal Amplifier Input Pin (OSC1)               | 79 |

| 4.4.2  | Crystal Amplifier Output Pin (OSC2)              | 79 |

| 4.4.3  | External Filter Capacitor Pin (CGMXFC)           | 79 |

| 4.4.4  | PLL Analog Power Pin (V <sub>DDA</sub> )         |    |

| 4.4.5  | PLL Analog Ground Pin (V <sub>SSA</sub> )        | 79 |

| 4.4.6  | Oscillator Enable Signal (SIMOSCEN)              |    |

| 4.4.7  | Oscillator Enable in Stop Mode Bit (OSCENINSTOP) |    |

| 4.4.8  | Crystal Output Frequency Signal (CGMXCLK)        |    |

| 4.4.9  | CGM Base Clock Output (CGMOUT)                   |    |

| 4.4.10 | CGM CPU Interrupt (CGMINT)                       |    |

| 4.5    | CGM Registers                                    |    |

| 4.5.1  | PLL Control Register                             |    |

| 4.5.2  | PLL Bandwidth Control Register                   |    |

| 4.5.3  | PLL Multiplier Select Register High              |    |

| 4.5.4  | PLL Multiplier Select Register Low               |    |

| 4.5.5  | PLL VCO Range Select Register                    |    |

| 4.6    | Interrupts                                       | 85 |

| 4.7    | Special Modes                                    | 85 |

| 4.7.1  | Wait Mode                                        |    |

| 4.7.2  | Stop Mode                                        |    |

| 4.7.3  | CGM During Break Interrupts                      | 86 |

| 4.8    | Acquisition/Lock Time Specifications             | 86 |

| 4.8.1  | Acquisition/Lock Time Definitions                |    |

| 4.8.2  | Parametric Influences on Reaction Time           | 86 |

| 4.8.3  | Choosing a Filter                                | 87 |

|        | Chapter 5                                        |    |

|        | Configuration Register (CONFIG)                  |    |

| 5.1    | Introduction                                     |    |

| 5.2    | Functional Description                           | 89 |

| 18.7    | I/O Signals                                         |     |

|---------|-----------------------------------------------------|-----|

| 18.7.1  | TIM2 Clock Pin (T2CH0)                              | 252 |

| 18.7.2  | TIM2 Channel I/O Pins (T2CH5:T2CH2 and T2CH1:T2CH0) | 252 |

| 18.8    | I/O Registers                                       | 252 |

| 18.8.1  | TIM2 Status and Control Register                    |     |

| 18.8.2  | TIM2 Counter Registers                              |     |

| 18.8.3  | TIM2 Counter Modulo Registers                       |     |

| 18.8.4  | TIM2 Channel Status and Control Registers           |     |

| 18.8.5  | TIM2 Channel Registers                              |     |

|         | Chantay 10                                          |     |

|         | Chapter 19 Development Support                      |     |

| 19.1    | Introduction                                        | 261 |

| 19.2    | Break Module (BRK)                                  | 261 |

| 19.2.1  | Functional Description                              |     |

| 19.2.1. |                                                     |     |

| 19.2.1. | 2 TIM During Break Interrupts                       | 264 |

| 19.2.1. | 3 COP During Break Interrupts                       | 264 |

| 19.2.2  | Break Module Registers                              | 264 |

| 19.2.2. | 1 Break Status and Control Register                 | 265 |

| 19.2.2. | 2 Break Address Registers                           | 265 |

| 19.2.2. |                                                     |     |

| 19.2.2. |                                                     |     |

| 19.2.3  | Low-Power Modes                                     | 266 |

| 19.3    | Monitor Module (MON)                                | 267 |

| 19.3.1  | Functional Description                              |     |

| 19.3.1. | ·                                                   |     |

| 19.3.1. | 2 Forced Monitor Mode                               | 271 |

| 19.3.1. | 3 Monitor Vectors                                   | 271 |

| 19.3.1. | 4 Data Format                                       | 272 |

| 19.3.1. | 5 Break Signal                                      | 272 |

| 19.3.1. | 6 Baud Rate                                         | 272 |

| 19.3.1. | 7 Commands                                          | 272 |

| 19.3.2  | Security                                            | 276 |

|         | Chapter 20                                          |     |

|         | Electrical Specifications                           |     |

| 20.1    | Introduction                                        | 277 |

| 20.2    | Absolute Maximum Ratings                            | 277 |

| 20.3    | Functional Operating Range                          |     |

| 20.4    |                                                     |     |

|         | Thermal Characteristics                             |     |

| 20.5    | 5.0-Vdc Electrical Characteristics                  |     |

| 20.6    | 3.3-Vdc Electrical Characteristics                  |     |

| 20.7    | 5.0-Volt Control Timing                             | 283 |

| 20.8    | 3.3-Volt Control Timing                             | 283 |

|         |                                                     |     |

- Specific features in 48-pin LQFP are:

- Port A is 8 bits: PTA0-PTA7; shared with ADC and KBI modules

- Port B is 8 bits: PTB0–PTB7; shared with ADC module

- Port C is only 7 bits: PTC0–PTC6

- Port D is 8 bits: PTD0-PTD7; shared with SPI, TIM1, and TIM2 modules

- Port E is only 6 bits: PTE0-PTE5; shared with ESCI module

- Specific features in 64-pin QFP are:

- Port A is 8 bits: PTA0-PTA7; shared with ADC and KBI modules

- Port B is 8 bits: PTB0-PTB7; shared with ADC module

- Port C is only 7 bits: PTC0–PTC6

- Port D is 8 bits: PTD0-PTD7; shared with SPI, TIM1, andTIM2 modules

- Port E is only 6 bits: PTE0-PTE5; shared with ESCI module

- Port F is 8 bits: PTF0-PTF7; shared with TIM2 module

- Port G is 8 bits; PTG0–PTG7; shared with ADC module

## 1.2.2 Features of the CPU08

Features of the CPU08 include:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

## 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HC908GR60A. Refer to Appendix A MC68HC908GR48A and Appendix B MC68HC908GR32A.

## Memory

| Addr.  | Register Name                                               |                 | Bit 7   | 6          | 5       | 4           | 3          | 2            | 1       | Bit 0   |

|--------|-------------------------------------------------------------|-----------------|---------|------------|---------|-------------|------------|--------------|---------|---------|

|        | Data Direction Register E                                   | Read:           | 0       | 0          | DDRE5   | DDRE4       | DDRE3      | DDRE2        | DDRE1   | DDRE0   |

| \$000C | (DDRE)                                                      | Write:          |         |            | DDNES   | DDNE4       | DUNES      | DDNEZ        | DUNEI   | DDNEO   |

|        | See page 146.                                               | Reset:          | 0       | 0          | 0       | 0           | 0          | 0            | 0       | 0       |

| \$000D | Port A Input Pullup Enable<br>Register (PTAPUE)             | Read:<br>Write: | PTAPUE7 | PTAPUE6    | PTAPUE5 | PTAPUE4     | PTAPUE3    | PTAPUE2      | PTAPUE1 | PTAPUE0 |

| ,      | See page 137.                                               | Reset:          | 0       | 0          | 0       | 0           | 0          | 0            | 0       | 0       |

|        | Port C Input Pullup Enable                                  | Read:           | 0       |            |         |             |            |              |         |         |

| \$000E | Register (PTCPUE)                                           | Write:          |         | PTCPUE6    | PTCPUE5 | PTCPUE4     | PTCPUE3    | PTCPUE2      | PTCPUE1 | PTCPUE0 |

|        | See page 142.                                               | Reset:          | 0       | 0          | 0       | 0           | 0          | 0            | 0       | 0       |

| \$000F | Port D Input Pullup Enable<br>Register (PTDPUE)             | Read:<br>Write: | PTDPUE7 | PTDPUE6    | PTDPUE5 | PTDPUE4     | PTDPUE3    | PTDPUE2      | PTDPUE1 | PTDPUE0 |

| 4      | See page 145.                                               | Reset:          | 0       | 0          | 0       | 0           | 0          | 0            | 0       | 0       |

| \$0010 | SPI Control Register<br>(SPCR)                              | Read:<br>Write: | SPRIE   | R          | SPMSTR  | CPOL        | СРНА       | SPWOM        | SPE     | SPTIE   |

|        | See page 217.                                               | Reset:          | 0       | 0          | 1       | 0           | 1          | 0            | 0       | 0       |

|        | SPI Status and Control<br>Register (SPSCR)<br>See page 218. | Read:           | SPRF    | EDDIE      | OVRF    | MODF        | SPTE       | MODEEN       | 0004    | ODDO    |

| \$0011 |                                                             | Write:          |         | ERRIE      |         |             |            | MODFEN       | SPR1    | SPR0    |

|        |                                                             | Reset:          | 0       | 0          | 0       | 0           | 1          | 0            | 0       | 0       |

|        | SPI Data Register<br>(SPDR)<br>See page 220.                | Read:           | R7      | R6         | R5      | R4          | R3         | R2           | R1      | R0      |

| \$0012 |                                                             | Write:          | T7      | T6         | T5      | T4          | T3         | T2           | T1      | T0      |

|        |                                                             | Reset:          |         |            |         | Unaffecte   | d by reset |              |         |         |

| \$0013 | ESCI Control Register 1<br>(SCC1)                           | Read:<br>Write: | LOOPS   | ENSCI      | TXINV   | М           | WAKE       | ILTY         | PEN     | PTY     |

|        | See page 166.                                               | Reset:          | 0       | 0          | 0       | 0           | 0          | 0            | 0       | 0       |

| \$0014 | ESCI Control Register 2<br>(SCC2)<br>See page 168.          | Read:<br>Write: | SCTIE   | TCIE       | SCRIE   | ILIE        | TE         | RE           | RWU     | SBK     |

|        |                                                             | Reset:          | 0       | 0          | 0       | 0           | 0          | 0            | 0       | 0       |

| \$0015 | ESCI Control Register 3<br>(SCC3)<br>See page 169.          | Read:<br>Write: | R8      | Т8         | R       | R           | ORIE       | NEIE         | FEIE    | PEIE    |

| ψοστο  |                                                             | Reset:          | U       | 0          | 0       | 0           | 0          | 0            | 0       | 0       |

|        | 50010:                                                      | Read:           | SCTE    | TC         | SCRF    | IDLE        | OR         | NF           | FE      | PE      |

| \$0016 | ESCI Status Register 1<br>(SCS1)                            | Write:          | 33.1    | . •        |         |             | <b>.</b>   |              | . –     | . =     |

| *****  | See page 170.                                               | Reset:          | 1       | 1          | 0       | 0           | 0          | 0            | 0       | 0       |

|        | ESCI Status Register 2                                      | Read:           | 0       | 0          | 0       | 0           | 0          | 0            | BKF     | RPF     |

| \$0017 | (SCS2)                                                      | Write:          |         |            |         |             |            |              |         |         |

|        | See page 173.                                               | Reset:          | 0       | 0          | 0       | 0           | 0          | 0            | 0       | 0       |

|        |                                                             |                 |         | = Unimplem | ented   | R = Reserve | d          | U = Unaffect | ed      |         |

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 9)

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## **HVEN** — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

Setting this read/write bit configures the FLASH-2 array for mass or page erase operation.

- 1 = Mass erase operation selected

- 0 = Page erase operation selected

## **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be set at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

## **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

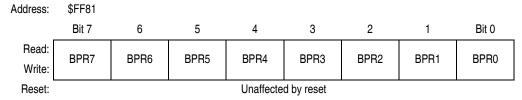

## 2.7.2.2 FLASH-2 Block Protect Register

The FLASH-2 block protect register (FL2BPR) is implemented as a byte within the FLASH-1 memory; therefore, can only be written during a FLASH-1 programming sequence. The value in this register determines the starting location of the protected range within the FLASH-2 memory.

Figure 2-8. FLASH-2 Block Protect Register (FL2BPR)

## NOTE

The FLASH-2 block protect register (FL2BPR) controls the block protection for the FLASH-2 array. However, FL2BPR is implemented within the FLASH-1 memory array and therefore, the FLASH-1 control register (FL1CR) must be used to program/erase FL2BPR.

## FL2BPR[7:0] — Block Protect Register Bits 7 to 0

These eight bits represent bits [14:7] of a 16-bit memory address. Bit 15 is a 0 and bits [6:0] are 0s.

The resultant 16-bit address is used for specifying the start address of the FLASH-2 memory for block protection. FLASH-2 is protected from this start address to the end of FLASH-2 memory at \$7FFF. With this mechanism, the protect start address can be \$XX00 and \$XX80 (128 byte page boundaries) within the FLASH-2 array.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### NOTE

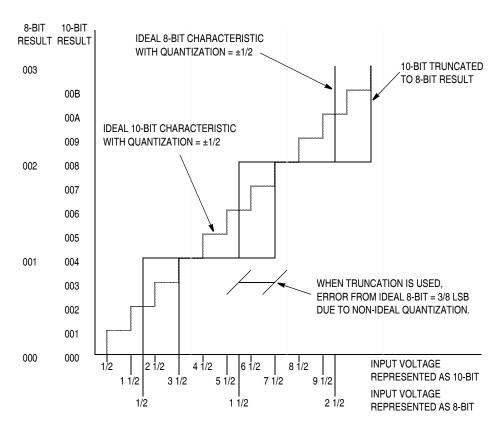

Quantization error is affected when only the most significant eight bits are used as a result. See Figure 3-3.

Figure 3-3. Bit Truncation Mode Error

## 3.4 Monotonicity

The conversion process is monotonic and has no missing codes.

## 3.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating CPU interrupts after each ADC conversion. A CPU interrupt is generated if the COCO bit is a 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

## 3.6 Low-Power Modes

The WAIT and STOP instruction can put the MCU in low power- consumption standby modes.

## 3.6.1 Wait Mode

The ADC continues normal operation during wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## **Clock Generator Module (CGM)**

**Table 4-5. Example Filter Component Values**

| f <sub>RCLK</sub> | C <sub>F1</sub> | C <sub>F2</sub> | R <sub>F1</sub> | C <sub>F</sub> |

|-------------------|-----------------|-----------------|-----------------|----------------|

| 1 MHz             | 8.2 nF          | 820 pF          | 2k              | 18 nF          |

| 2 MHz             | 4.7 nF          | 470 pF          | 2k              | 6.8 nF         |

| 3 MHz             | 3.3 nF          | 330 pF          | 2k              | 5.6 nF         |

| 4 MHz             | 2.2 nF          | 220 pF          | 2k              | 4.7 nF         |

| 5 MHz             | 1.8 nF          | 180 pF          | 2k              | 3.9 nF         |

| 6 MHz             | 1.5 nF          | 150 pF          | 2k              | 3.3 nF         |

| 7 MHz             | 1.2 nF          | 120 pF          | 2k              | 2.7 nF         |

| 8 MHz             | 1 nF            | 100 pF          | 2k              | 2.2 nF         |

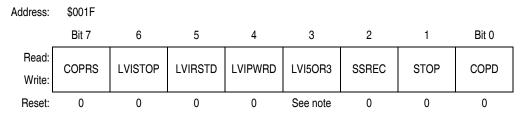

Note: LVI5OR3 is only reset via POR (power-on reset).

Figure 5-2. Configuration Register 1 (CONFIG1)

## COPRS — COP Rate Select Bit

COPRS selects the COP timeout period. Reset clears COPRS. See Chapter 6 Computer Operating Properly (COP) Module

- 1 = COP timeout period = 8176 CGMXCLK cycles

- 0 = COP timeout period = 262,128 CGMXCLK cycles

## LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

- 1 = LVI enabled during stop mode

- 0 = LVI disabled during stop mode

## LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI).

- 1 = LVI module resets disabled

- 0 = LVI module resets enabled

#### LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI).

- 1 = LVI module power disabled

- 0 = LVI module power enabled

## LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

LVI5OR3 selects the voltage operating mode of the LVI module (see Chapter 11 Low-Voltage Inhibit (LVI)). The voltage mode selected for the LVI should match the operating V<sub>DD</sub> (see Chapter 20 Electrical Specifications) for the LVI's voltage trip points for each of the modes.

- 1 = LVI operates in 5-V mode

- 0 = LVI operates in 3-V mode

## **NOTE**

The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

## SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 CGMXCLK cycles instead of a 4096-CGMXCLK cycle delay.

- 1 = Stop mode recovery after 32 CGMXCLK cycles

- 0 = Stop mode recovery after 4096 CGMXCLK cycles

## NOTE

Exiting stop mode by any reset will result in the long stop recovery.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### Computer Operating Properly (COP) Module

The COP counter is a free-running 6-bit counter preceded by the 12-bit SIM counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 CGMXCLK cycles, depending on the state of the COP rate select bit, COPRS, in the configuration register. With a 262,128 CGMXCLK cycle overflow option, a 4.9152-MHz crystal gives a COP timeout period of 53.3 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the RST pin low for 32 CGMXCLK cycles and sets the COP bit in the reset status register (RSR).

In monitor mode, the COP is disabled if the  $\overline{RST}$  pin or the  $\overline{IRQ}$  is held at  $V_{TST}$ . During the break state,  $V_{TST}$  on the  $\overline{RST}$  pin disables the COP.

#### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

## 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

## 6.3.1 CGMXCLK

CGMXCLK is the crystal oscillator output signal. CGMXCLK frequency is equal to the crystal frequency.

## 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

## 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector. See 6.4 COP Control Register.

## 6.3.4 Power-On Reset

The power-on reset (POR) circuit clears the SIM counter 4096 CGMXCLK cycles after power-up.

## 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

## **Low-Power Modes**

## 10.11 Serial Peripheral Interface Module (SPI)

## 10.11.1 Wait Mode

The serial peripheral interface (SPI) module remains active in wait mode. Any enabled CPU interrupt request from the SPI module can bring the MCU out of wait mode.

If SPI module functions are not required during wait mode, reduce power consumption by disabling the SPI module before executing the WAIT instruction.

## 10.11.2 Stop Mode

The SPI module is inactive in stop mode. The STOP instruction does not affect SPI register states. SPI operation resumes after an external interrupt. If stop mode is exited by reset, any transfer in progress is aborted, and the SPI is reset.

## 10.12 Timer Interface Module (TIM1 and TIM2)

## 10.12.1 Wait Mode

The timer interface modules (TIM) remain active in wait mode. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

## 10.12.2 Stop Mode

The TIM is inactive in stop mode. The STOP instruction does not affect register states or the state of the TIM counter. TIM operation resumes when the MCU exits stop mode after an external interrupt.

## 10.13 Timebase Module (TBM)

## 10.13.1 Wait Mode

The timebase module (TBM) remains active after execution of the WAIT instruction. In wait mode, the timebase register is not accessible by the CPU.

If the timebase functions are not required during wait mode, reduce the power consumption by stopping the timebase before enabling the WAIT instruction.

## 10.13.2 Stop Mode

The timebase module may remain active after execution of the STOP instruction if the oscillator has been enabled to operate during stop mode through the OSCENINSTOP bit in the CONFIG2 register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

If the oscillator has not been enabled to operate in stop mode, the timebase module will not be active during stop mode. In stop mode, the timebase register is not accessible by the CPU.

If the timebase functions are not required during stop mode, reduce the power consumption by stopping the timebase before enabling the STOP instruction.

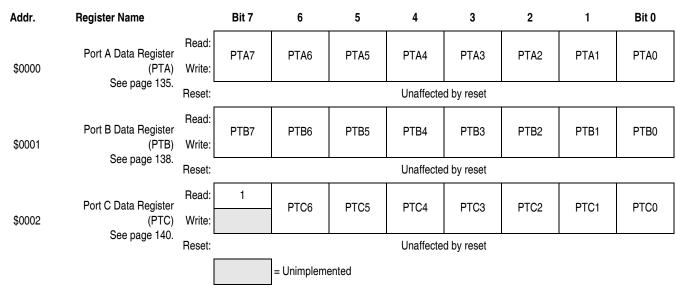

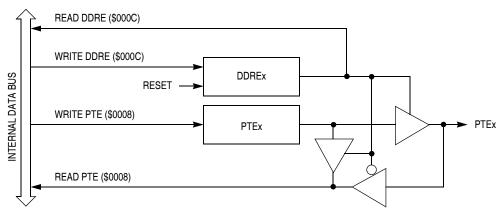

# Chapter 12 Input/Output (I/O) Ports

## 12.1 Introduction

Bidirectional input-output (I/O) pins form seven parallel ports. All I/O pins are programmable as inputs or outputs. All individual bits within port A, port C, port D and port F are software configurable with pullup devices if configured as input port bits. The pullup devices are automatically and dynamically disabled when a port bit is switched to output mode.

## 12.2 Unused Pin Termination

Input pins and I/O port pins that are not used in the application must be terminated. This prevents excess current caused by floating inputs, and enhances immunity during noise or transient events. Termination methods include:

- 1. Configuring unused pins as outputs and driving high or low;

- 2. Configuring unused pins as inputs and enabling internal pull-ups;

- 3. Configuring unused pins as inputs and using external pull-up or pull-down resistors.

Never connect unused pins directly to V<sub>DD</sub> or V<sub>SS</sub>.

Since some general-purpose I/O pins are not available on all packages, these pins must be terminated as well. Either method 1 or 2 above are appropriate.

Figure 12-1. I/O Port Register Summary (Sheet 1 of 3)

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

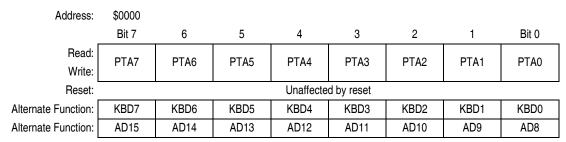

## 12.3 Port A

Port A is an 8-bit special-function port that shares all eight of its pins with the keyboard interrupt (KBI) module and the ADC module. Port A also has software configurable pullup devices if configured as an input port.

## 12.3.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the eight port A pins.

Figure 12-2. Port A Data Register (PTA)

## PTA7-PTA0 — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

## **KBD7-KBD0** — Keyboard Inputs

The keyboard interrupt enable bits, KBIE7–KBIE0, in the keyboard interrupt control register (KBICR) enable the port A pins as external interrupt pins. See Chapter 9 Keyboard Interrupt Module (KBI)

## AD15-AD8 — Analog-to-Digital Input Bits

AD15—AD8 are pins used for the input channels to the analog-to-digital converter module. The channel select bits in the ADC status and control register define which port A pin will be used as an ADC input and overrides any control from the port I/O logic by forcing that pin as the input to the analog circuitry.

#### NOTE

Care must be taken when reading port A while applying analog voltages to AD15–AD8 pins. If the appropriate ADC channel is not enabled, excessive current drain may occur if analog voltages are applied to the PTAx/KBDx/ADx pin, while PTA is read as a digital input during the CPU read cycle. Those ports not selected as analog input channels are considered digital I/O ports.

Figure 12-19. Port E I/O Circuit

**Table 12-6. Port E Pin Functions**

|   | DDRE | PTE              | I/O Pin                    | Accesses to DDRE | Accesses to PTE |                          |

|---|------|------------------|----------------------------|------------------|-----------------|--------------------------|

|   | Bit  | Bit              | Mode                       | Read/Write       | Read            | Write                    |

| Ī | 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRE5-DDRE0      | Pin             | PTE5-PTE0 <sup>(3)</sup> |

|   | 1    | Х                | Output                     | DDRE5-DDRE0      | PTE5-PTE0       | PTE5-PTE0                |

- 1. X = Don't care

- 2. Hi-Z = High impedance

- 3. Writing affects data register, but does not affect input.

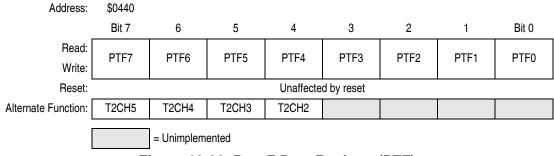

## 12.8 Port F

Port F is an 8-bit special-function port that shares four of its pins with the timer interface (TIM2) module.

## 12.8.1 Port F Data Register

The port F data register (PTF) contains a data latch for each of the eight port F pins.

Figure 12-20. Port F Data Register (PTF)

## PTF7-PTF0 — Port F Data Bits

These read/write bits are software-programmable. Data direction of each port F pin is under the control of the corresponding bit in data direction register F. Reset has no effect on port F data.

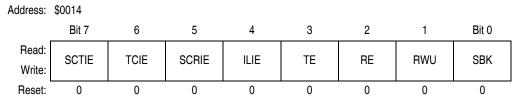

## **Enhanced Serial Communications Interface (ESCI) Module**

- Enables the transmitter

- Enables the receiver

- Enables ESCI wakeup

- Transmits ESCI break characters

Figure 13-11. ESCI Control Register 2 (SCC2)

## SCTIE — ESCI Transmit Interrupt Enable Bit

This read/write bit enables the SCTE bit to generate ESCI transmitter CPU interrupt requests. Setting the SCTIE bit in SCC2 enables the SCTE bit to generate CPU interrupt requests. Reset clears the SCTIE bit.

- 1 = SCTE enabled to generate CPU interrupt

- 0 = SCTE not enabled to generate CPU interrupt

## TCIE — Transmission Complete Interrupt Enable Bit

This read/write bit enables the TC bit to generate ESCI transmitter CPU interrupt requests. Reset clears the TCIE bit.

- 1 = TC enabled to generate CPU interrupt requests

- 0 = TC not enabled to generate CPU interrupt requests

## SCRIE — ESCI Receive Interrupt Enable Bit

This read/write bit enables the SCRF bit to generate ESCI receiver CPU interrupt requests. Setting the SCRIE bit in SCC2 enables the SCRF bit to generate CPU interrupt requests. Reset clears the SCRIE bit.

- 1 = SCRF enabled to generate CPU interrupt

- 0 = SCRF not enabled to generate CPU interrupt

## ILIE — Idle Line Interrupt Enable Bit

This read/write bit enables the IDLE bit to generate ESCI receiver CPU interrupt requests. Reset clears the ILIE bit.

- 1 = IDLE enabled to generate CPU interrupt requests

- 0 = IDLE not enabled to generate CPU interrupt requests

## TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 1s from the transmit shift register to the TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the TxD returns to the idle condition (high). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted. Reset clears the TE bit.

- 1 = Transmitter enabled

- 0 = Transmitter disabled

## NOTE

Writing to the TE bit is not allowed when the enable ESCI bit (ENSCI) is clear. ENSCI is in ESCI control register 1.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## 14.5.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register) and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

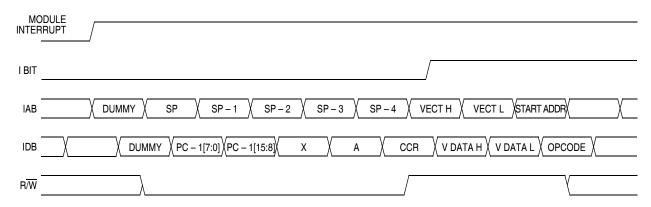

Figure 14-8. Interrupt Entry Timing

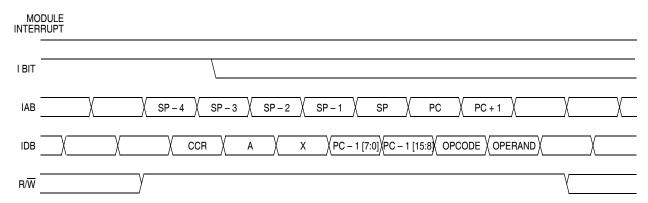

Figure 14-9. Interrupt Recovery Timing

## 15.5 Queuing Transmission Data

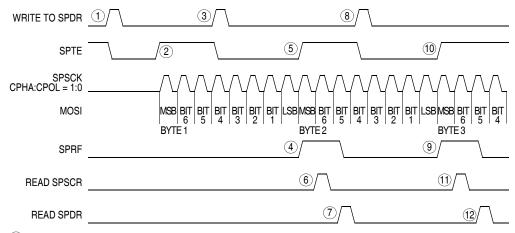

The double-buffered transmit data register allows a data byte to be queued and transmitted. For an SPI configured as a master, a queued data byte is transmitted immediately after the previous transmission has completed. The SPI transmitter empty flag (SPTE) indicates when the transmit data buffer is ready to accept new data. Write to the transmit data register only when SPTE is high. Figure 15-9 shows the timing associated with doing back-to-back transmissions with the SPI (SPSCK has CPHA: CPOL = 1:0).

- CPU WRITES BYTE 1 TO SPDR, CLEARING SPTE BIT.

- ② BYTE 1 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- 3 CPU WRITES BYTE 2 TO SPDR, QUEUEING BYTE 2 AND CLEARING SPTE BIT.

- FIRST INCOMING BYTE TRANSFERS FROM SHIFT REGISTER TO RECEIVE DATA REGISTER, SETTING SPRF BIT.

- (5) BYTE 2 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- (6) CPU READS SPSCR WITH SPRF BIT SET.

- (7) CPU READS SPDR, CLEARING SPRF BIT.

- (8) CPU WRITES BYTE 3 TO SPDR, QUEUEING BYTE 3 AND CLEARING SPTE BIT.

- 9 SECOND INCOMING BYTE TRANSFERS FROM SHIFT REGISTER TO RECEIVE DATA REGISTER, SETTING SPRF BIT.

- (10) BYTE 3 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- 11) CPU READS SPSCR WITH SPRF BIT SET.

- (12) CPU READS SPDR, CLEARING SPRF BIT.

Figure 15-9. SPRF/SPTE CPU Interrupt Timing

The transmit data buffer allows back-to-back transmissions without the slave precisely timing its writes between transmissions as in a system with a single data buffer. Also, if no new data is written to the data buffer, the last value contained in the shift register is the next data word to be transmitted.

For an idle master or idle slave that has no data loaded into its transmit buffer, the SPTE is set again no more than two bus cycles after the transmit buffer empties into the shift register. This allows the user to queue up a 16-bit value to send. For an already active slave, the load of the shift register cannot occur until the transmission is completed. This implies that a back-to-back write to the transmit data register is not possible. SPTE indicates when the next write can occur.

In a slave SPI (MSTR = 0), MODF generates an SPI receiver/error CPU interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by clearing the SPE bit of the slave.

#### NOTE

A high on the  $\overline{SS}$  pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

## 15.7 Interrupts

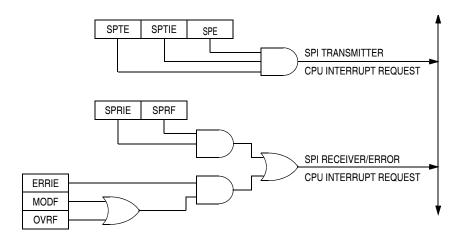

Four SPI status flags can be enabled to generate CPU interrupt requests. See Table 15-1.

| Flag                      | Request                                                    |

|---------------------------|------------------------------------------------------------|

| SPTE<br>Transmitter empty | SPI transmitter CPU interrupt request (SPTIE = 1, SPE = 1) |

| SPRF<br>Receiver full     | SPI receiver CPU interrupt request (SPRIE = 1)             |

| OVRF<br>Overflow          | SPI receiver/error interrupt request (ERRIE = 1)           |

| MODF<br>Mode fault        | SPI receiver/error interrupt request (ERRIE = 1)           |

Table 15-1. SPI Interrupts

Reading the SPI status and control register with SPRF set and then reading the receive data register clears SPRF. The clearing mechanism for the SPTE flag is always just a write to the transmit data register.

The SPI transmitter interrupt enable bit (SPTIE) enables the SPTE flag to generate transmitter CPU interrupt requests, provided that the SPI is enabled (SPE = 1).

The SPI receiver interrupt enable bit (SPRIE) enables SPRF to generate receiver CPU interrupt requests, regardless of the state of SPE. See Figure 15-12.

Figure 15-12. SPI Interrupt Request Generation

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## **Electrical Specifications**

## 20.12 5.0-Volt SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                   | Min                                              | Max                                   | Unit             |

|----------------------------------|----------------------------------------------------------------------|------------------------------------------|--------------------------------------------------|---------------------------------------|------------------|

|                                  | Operating frequency<br>Master<br>Slave                               | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub> | f <sub>OP</sub> /128<br>dc                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz       |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub>                      | 2<br>1                                           | 128<br>—                              | t <sub>CYC</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                     | 1                                                | _                                     | t <sub>CYC</sub> |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                      | 1                                                | _                                     | t <sub>CYC</sub> |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub>                     | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns         |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub>                     | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns         |

| 6                                | Data setup time (inputs)  Master  Slave                              | t <sub>SU(M)</sub>                       | 30<br>30                                         |                                       | ns<br>ns         |

| 7                                | Data hold time (inputs) Master Slave                                 | t <sub>H(M)</sub>                        | 30<br>30                                         |                                       | ns<br>ns         |

| 8                                | Access time, slave <sup>(3)</sup> CPHA = 0 CPHA = 1                  | t <sub>A(CP0)</sub>                      | 0<br>0                                           | 40<br>40                              | ns<br>ns         |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                      | _                                                | 40                                    | ns               |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub> t <sub>V(S)</sub>      | _                                                | 50<br>50                              | ns<br>ns         |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub>                       | 0<br>0                                           |                                       | ns<br>ns         |

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5 288 Freescale Semiconductor

Numbers refer to dimensions in Figure 20-2 and Figure 20-3.

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins.

Time to data active from high-impedance state

Hold time to high-impedance state

With 100 pF on all SPI pins

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUM PLANE -H- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS A-B AND -D- TO BE DETERMINED AT DATUM PLANE -H-.

- $\triangle$  DIMENSIONS TO BE DETERMINED AT SEATING PLANE -C-.

- DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25mm PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE —H—.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDICTION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | L OUTLINE    | PRINT VERSION NO | OT TO SCALE    |        |

|---------------------------------------------------------|--------------|------------------|----------------|--------|

| TITLE:                                                  |              | DOCUMENT NO      | ): 98ASB42844B | REV: A |

| 64LD QFP (14 X                                          | CASE NUMBER  | R: 840B-02       | 06 APR 2005    |        |

|                                                         | STANDARD: NO | N-JEDEC          |                |        |