Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 37                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 24x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr48avfae |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **List of Chapters**

| Chapter 1 General Description                                     | 19  |

|-------------------------------------------------------------------|-----|

| Chapter 2 Memory                                                  | 29  |

| Chapter 3 Analog-to-Digital Converter (ADC)                       | 59  |

| Chapter 4 Clock Generator Module (CGM)                            | 71  |

| Chapter 5 Configuration Register (CONFIG)                         | 89  |

| Chapter 6 Computer Operating Properly (COP) Module                | 93  |

| Chapter 7 Central Processor Unit (CPU)                            | 97  |

| Chapter 8 External Interrupt (IRQ)                                | 109 |

| Chapter 9 Keyboard Interrupt Module (KBI)                         | 113 |

| Chapter 10 Low-Power Modes                                        | 121 |

| Chapter 11 Low-Voltage Inhibit (LVI)                              | 127 |

| Chapter 12 Input/Output (I/O) Ports                               | 131 |

| Chapter 13 Enhanced Serial Communications Interface (ESCI) Module | 151 |

| Chapter 14 System Integration Module (SIM)                        | 183 |

| Chapter 15 Serial Peripheral Interface (SPI) Module               | 201 |

| Chapter 16 Timebase Module (TBM)                                  | 221 |

| Chapter 17 Timer Interface Module (TIM1)                          | 225 |

| Chapter 18 Timer Interface Module (TIM2)                          | 241 |

| Chapter 19 Development Support                                    | 261 |

| Chapter 20 Electrical Specifications                              | 277 |

| Chapter 21 Ordering Information and Mechanical Specifications     | 295 |

| Appendix A MC68HC908GR48A                                         | 305 |

| Appendix B MC68HC908GR32A                                         | 309 |

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

# Chapter 4 Clock Generator Module (CGM)

| 4.1    | Introduction                                     | 71 |

|--------|--------------------------------------------------|----|

| 4.2    | Features                                         | 71 |

| 4.3    | Functional Description                           | 71 |

| 4.3.1  | Crystal Oscillator Circuit                       | 73 |

| 4.3.2  | Phase-Locked Loop Circuit (PLL)                  | 73 |

| 4.3.3  | PLL Circuits                                     |    |

| 4.3.4  | Acquisition and Tracking Modes                   | 74 |

| 4.3.5  | Manual and Automatic PLL Bandwidth Modes         |    |

| 4.3.6  | Programming the PLL                              | 75 |

| 4.3.7  | Special Programming Exceptions                   |    |

| 4.3.8  | Base Clock Selector Circuit                      | 77 |

| 4.3.9  | CGM External Connections                         | 78 |

| 4.4    | I/O Signals                                      |    |

| 4.4.1  | Crystal Amplifier Input Pin (OSC1)               | 79 |

| 4.4.2  | Crystal Amplifier Output Pin (OSC2)              | 79 |

| 4.4.3  | External Filter Capacitor Pin (CGMXFC)           | 79 |

| 4.4.4  | PLL Analog Power Pin (V <sub>DDA</sub> )         |    |

| 4.4.5  | PLL Analog Ground Pin (V <sub>SSA</sub> )        | 79 |

| 4.4.6  | Oscillator Enable Signal (SIMOSCEN)              |    |

| 4.4.7  | Oscillator Enable in Stop Mode Bit (OSCENINSTOP) |    |

| 4.4.8  | Crystal Output Frequency Signal (CGMXCLK)        |    |

| 4.4.9  | CGM Base Clock Output (CGMOUT)                   |    |

| 4.4.10 | CGM CPU Interrupt (CGMINT)                       |    |

| 4.5    | CGM Registers                                    |    |

| 4.5.1  | PLL Control Register                             |    |

| 4.5.2  | PLL Bandwidth Control Register                   |    |

| 4.5.3  | PLL Multiplier Select Register High              |    |

| 4.5.4  | PLL Multiplier Select Register Low               |    |

| 4.5.5  | PLL VCO Range Select Register                    |    |

| 4.6    | Interrupts                                       | 85 |

| 4.7    | Special Modes                                    | 85 |

| 4.7.1  | Wait Mode                                        |    |

| 4.7.2  | Stop Mode                                        |    |

| 4.7.3  | CGM During Break Interrupts                      | 86 |

| 4.8    | Acquisition/Lock Time Specifications             | 86 |

| 4.8.1  | Acquisition/Lock Time Definitions                |    |

| 4.8.2  | Parametric Influences on Reaction Time           | 86 |

| 4.8.3  | Choosing a Filter                                | 87 |

|        | Chapter 5                                        |    |

|        | Configuration Register (CONFIG)                  |    |

| 5.1    | Introduction                                     |    |

| 5.2    | Functional Description                           | 89 |

Memory

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### **Analog-to-Digital Converter (ADC)**

#### 3.3.3 Conversion Time

Conversion starts after a write to the ADC status and control register (ADSCR). One conversion will take between 16 and 17 ADC clock cycles. The ADIVx and ADICLK bits should be set to provide a 1-MHz ADC clock frequency.

Conversion time =

$$\frac{16 \text{ to } 17 \text{ ADC cycles}}{\text{ADC frequency}}$$

Number of bus cycles = conversion time  $\times$  bus frequency

#### 3.3.4 Conversion

In continuous conversion mode, the ADC data register will be filled with new data after each conversion. Data from the previous conversion will be overwritten whether that data has been read or not. Conversions will continue until the ADCO bit is cleared. The COCO bit is set after each conversion and will stay set until the next read of the ADC data register.

In single conversion mode, conversion begins with a write to the ADSCR. Only one conversion occurs between writes to the ADSCR.

When a conversion is in process and the ADSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

## 3.3.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

#### 3.3.6 Result Justification

The conversion result may be formatted in four different ways:

- 1. Left justified

- 2. Right justified

- Left Justified sign data mode

- 4. 8-bit truncation mode

All four of these modes are controlled using MODE0 and MODE1 bits located in the ADC clock register (ADCLK).

Left justification will place the eight most significant bits (MSB) in the corresponding ADC data register high, ADRH. This may be useful if the result is to be treated as an 8-bit result where the two least significant bits (LSB), located in the ADC data register low, ADRL, can be ignored. However, ADRL must be read after ADRH or else the interlocking will prevent all new conversions from being stored.

Right justification will place only the two MSBs in the corresponding ADC data register high, ADRH, and the eight LSBs in ADC data register low, ADRL. This mode of operation typically is used when a 10-bit unsigned result is desired.

Left justified sign data mode is similar to left justified mode with one exception. The MSB of the 10-bit result, AD9 located in ADRH, is complemented. This mode of operation is useful when a result, represented as a signed magnitude from mid-scale, is needed. Finally, 8-bit truncation mode will place the eight MSBs in the ADC data register low, ADRL. The two LSBs are dropped. This mode of operation is used when compatibility with 8-bit ADC designs are required. No interlocking between ADRH and ADRL is present.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## 4.4.1 Crystal Amplifier Input Pin (OSC1)

The OSC1 pin is an input to the crystal oscillator amplifier.

## 4.4.2 Crystal Amplifier Output Pin (OSC2)

The OSC2 pin is the output of the crystal oscillator inverting amplifier.

## 4.4.3 External Filter Capacitor Pin (CGMXFC)

The CGMXFC pin is required by the loop filter to filter out phase corrections. An external filter network is connected to this pin. (See Figure 4-2.)

#### NOTE

To prevent noise problems, the filter network should be placed as close to the CGMXFC pin as possible, with minimum routing distances and no routing of other signals across the network.

## 4.4.4 PLL Analog Power Pin (V<sub>DDA</sub>)

$V_{DDA}$  is a power pin used by the analog portions of the PLL. Connect the  $V_{DDA}$  pin to the same voltage potential as the  $V_{DD}$  pin.

#### NOTE

Route  $V_{DDA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

## 4.4.5 PLL Analog Ground Pin (V<sub>SSA</sub>)

$V_{SSA}$  is a ground pin used by the analog portions of the PLL. Connect the  $V_{SSA}$  pin to the same voltage potential as the  $V_{SS}$  pin.

#### NOTE

Route  $V_{SSA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

## 4.4.6 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and enables the oscillator and PLL.

## 4.4.7 Oscillator Enable in Stop Mode Bit (OSCENINSTOP)

OSCENINSTOP is a bit in the CONFIG2 register that enables the oscillator to continue operating during stop mode. If this bit is set, the oscillator continues running during stop mode. If this bit is not set (default), the oscillator is controlled by the SIMOSCEN signal which will disable the oscillator during stop mode.

## 4.4.8 Crystal Output Frequency Signal (CGMXCLK)

CGMXCLK is the crystal oscillator output signal. It runs at the full speed of the crystal ( $f_{XCLK}$ ) and comes directly from the crystal oscillator circuit. Figure 4-2 shows only the logical relation of CGMXCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of CGMXCLK is unknown and may depend on the crystal and other external factors. Also, the frequency and amplitude of CGMXCLK can be unstable at start up.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

External Interrupt (IRQ)

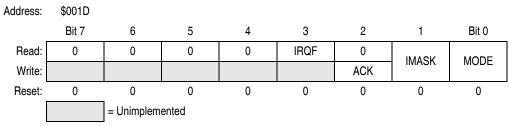

## 8.6 IRQ Status and Control Register

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. The INTSCR:

- · Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

Figure 8-3. IRQ Status and Control Register (INTSCR)

#### IRQF — IRQ Flag Bit

This read-only status bit is high when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- 0 = IRQ interrupt not pending

#### ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0. Reset clears ACK.

## IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables IRQ interrupt requests. Reset clears IMASK.

- 1 = IRQ interrupt requests disabled

- 0 = IRQ interrupt requests enabled

## MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin. Reset clears MODE.

- $1 = \overline{IRQ}$  interrupt requests on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt requests on falling edges only

## Chapter 11 Low-Voltage Inhibit (LVI)

#### 11.1 Introduction

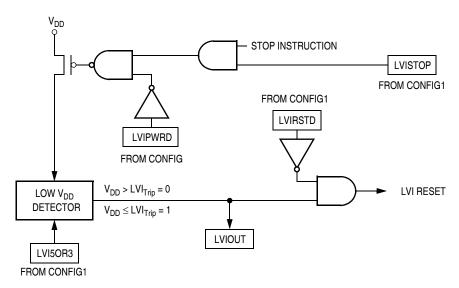

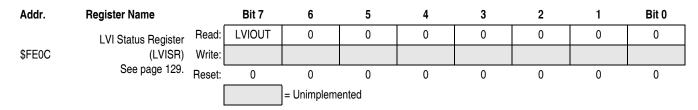

This section describes the low-voltage inhibit (LVI) module, which monitors the voltage on the  $V_{DD}$  pin and can force a reset when the  $V_{DD}$  voltage falls below the LVI trip falling voltage,  $V_{TRIPF}$ .

### 11.2 Features

Features of the LVI module include:

- Programmable LVI reset

- Selectable LVI trip voltage

- Programmable stop mode operation

## 11.3 Functional Description

Figure 11-1 shows the structure of the LVI module. The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit, LVIPWRD, enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit, LVIRSTD, enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,  $V_{TRIPF}$ . Setting the LVI enable in stop mode bit, LVISTOP, enables the LVI to operate in stop mode. Setting the LVI 5-V or 3-V trip point bit, LVI5OR3, enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 5-V operation. Clearing the LVI5OR3 bit enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 3-V operation. The actual trip points are shown in Chapter 20 Electrical Specifications.

#### **NOTE**

After a power-on reset (POR) the LVI's default mode of operation is 3 V. If a 5-V system is used, the user must set the LVI5OR3 bit to raise the trip point to 5-V operation. Note that this must be done after every power-on reset since the default will revert back to 3-V mode after each power-on reset. If the  $V_{DD}$  supply is below the 5-V mode trip voltage but above the 3-V mode trip voltage when POR is released, the part will operate because  $V_{TRIPF}$  defaults to 3-V mode after a POR. So, in a 5-V system care must be taken to ensure that  $V_{DD}$  is above the 5-V mode trip voltage after POR is released.

If the user requires 5-V mode and sets the LVI5OR3 bit after a power-on reset while the  $V_{DD}$  supply is not above the  $V_{TRIPR}$  for 5-V mode, the microcontroller unit (MCU) will immediately go into reset. The LVI in this case will hold the part in reset until either  $V_{DD}$  goes above the rising 5-V trip point,  $V_{TRIPR}$ , which will release reset or  $V_{DD}$  decreases to approximately 0 V which will re-trigger the power-on reset and reset the trip point to 3-V operation.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### Low-Voltage Inhibit (LVI)

LVISTOP, LVIPWRD, LVI5OR3, and LVIRSTD are in the configuration register (CONFIG1). See Figure 5-2. Configuration Register 1 (CONFIG1) for details of the LVI's configuration bits. Once an LVI reset occurs, the MCU remains in reset until  $V_{DD}$  rises above a voltage,  $V_{TRIPR}$ , which causes the MCU to exit reset. See 14.3.2.5 Low-Voltage Inhibit (LVI) Reset for details of the interaction between the SIM and the LVI. The output of the comparator controls the state of the LVIOUT flag in the LVI status register (LVISR).

An LVI reset also drives the RST pin low to provide low-voltage protection to external peripheral devices.

Figure 11-1. LVI Module Block Diagram

Figure 11-2. LVI I/O Register Summary

#### 11.3.1 Polled LVI Operation

In applications that can operate at  $V_{DD}$  levels below the  $V_{TRIPF}$  level, software can monitor  $V_{DD}$  by polling the LVIOUT bit. In the configuration register, the LVIPWRD bit must be 0 to enable the LVI module, and the LVIRSTD bit must be 1 to disable LVI resets.

#### 11.3.2 Forced Reset Operation

In applications that require  $V_{DD}$  to remain above the  $V_{TRIPF}$  level, enabling LVI resets allows the LVI module to reset the MCU when  $V_{DD}$  falls below the  $V_{TRIPF}$  level. In the configuration register, the LVIPWRD and LVIRSTD bits must be cleared to enable the LVI module and to enable LVI resets.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

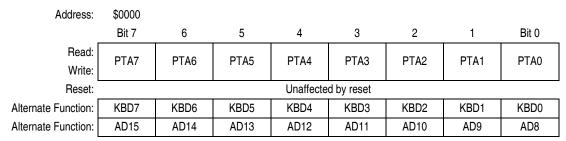

#### 12.3 Port A

Port A is an 8-bit special-function port that shares all eight of its pins with the keyboard interrupt (KBI) module and the ADC module. Port A also has software configurable pullup devices if configured as an input port.

## 12.3.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the eight port A pins.

Figure 12-2. Port A Data Register (PTA)

#### PTA7-PTA0 — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

#### **KBD7-KBD0** — Keyboard Inputs

The keyboard interrupt enable bits, KBIE7–KBIE0, in the keyboard interrupt control register (KBICR) enable the port A pins as external interrupt pins. See Chapter 9 Keyboard Interrupt Module (KBI)

## AD15-AD8 — Analog-to-Digital Input Bits

AD15—AD8 are pins used for the input channels to the analog-to-digital converter module. The channel select bits in the ADC status and control register define which port A pin will be used as an ADC input and overrides any control from the port I/O logic by forcing that pin as the input to the analog circuitry.

#### NOTE

Care must be taken when reading port A while applying analog voltages to AD15–AD8 pins. If the appropriate ADC channel is not enabled, excessive current drain may occur if analog voltages are applied to the PTAx/KBDx/ADx pin, while PTA is read as a digital input during the CPU read cycle. Those ports not selected as analog input channels are considered digital I/O ports.

#### **NOTE**

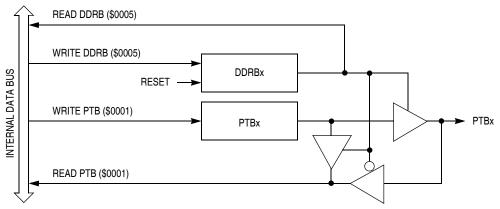

Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1.

Figure 12-8 shows the port B I/O logic.

When bit DDRBx is a 1, reading address \$0001 reads the PTBx data latch. When bit DDRBx is a 0, reading address \$0001 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-3 summarizes the operation of the port B pins.

Figure 12-8. Port B I/O Circuit

**Table 12-3. Port B Pin Functions**

| DDRB | РТВ              | I/O Pin                    | Accesses to DDRB | Access    | ses to PTB               |  |

|------|------------------|----------------------------|------------------|-----------|--------------------------|--|

| Bit  | Bit              | Mode                       | Read/Write       | Read      | Write                    |  |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRB7-DDRB0      | Pin       | PTB7-PTB0 <sup>(3)</sup> |  |

| 1    | Х                | Output                     | DDRB7-DDRB0      | PTB7-PTB0 | PTB7-PTB0                |  |

- 1. X = Don't care

- 2. Hi-Z = High impedance

- 3. Writing affects data register, but does not affect input.

## 13.6 ESCI During Break Module Interrupts

The BCFE bit in the break flag control register (SBFCR) enables software to clear status bits during the break state. See 19.2 Break Module (BRK).

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

## **13.7 I/O Signals**

Port E shares two of its pins with the ESCI module. The two ESCI I/O pins are:

- PTE0/TxD transmit data

- PTE1/RxD receive data

## 13.7.1 PTE0/TxD (Transmit Data)

The PTE0/TxD pin is the serial data output from the ESCI transmitter. The ESCI shares the PTE0/TxD pin with port E. When the ESCI is enabled, the PTE0/TxD pin is an output regardless of the state of the DDRE0 bit in data direction register E (DDRE).

## 13.7.2 PTE1/RxD (Receive Data)

The PTE1/RxD pin is the serial data input to the ESCI receiver. The ESCI shares the PTE1/RxD pin with port E. When the ESCI is enabled, the PTE1/RxD pin is an input regardless of the state of the DDRE1 bit in data direction register E (DDRE).

## 13.8 I/O Registers

These I/O registers control and monitor ESCI operation:

- ESCI control register 1, SCC1

- ESCI control register 2, SCC2

- ESCI control register 3, SCC3

- ESCI status register 1, SCS1

- ESCI status register 2, SCS2

- ESCI data register, SCDR

- ESCI baud rate register, SCBR

- ESCI prescaler register, SCPSC

- ESCI arbiter control register, SCIACTL

- ESCI arbiter data register, SCIADAT

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5 Freescale Semiconductor 165

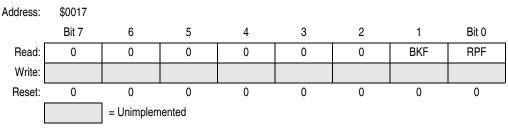

## 13.8.5 ESCI Status Register 2

ESCI status register 2 (SCS2) contains flags to signal these conditions:

- Break character detected

- Incoming data

Figure 13-15. ESCI Status Register 2 (SCS2)

### **BKF** — Break Flag Bit

This clearable, read-only bit is set when the ESCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

- 1 = Break character detected

- 0 = No break character detected

## RPF — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch), or when the receiver detects an idle character. Polling RPF before disabling the ESCI module or entering stop mode can show whether a reception is in progress.

- 1 = Reception in progress

- 0 = No reception in progress

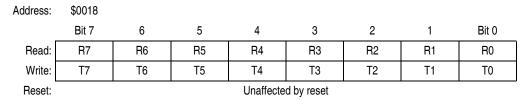

#### 13.8.6 ESCI Data Register

The ESCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the ESCI data register.

Figure 13-16. ESCI Data Register (SCDR)

#### R7/T7:R0/T0 — Receive/Transmit Data Bits

Reading address \$0018 accesses the read-only received data bits, R7:R0. Writing to address \$0018 writes the data to be transmitted, T7:T0. Reset has no effect on the ESCI data register.

#### NOTE

Do not use read-modify-write instructions on the ESCI data register.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

| Addr.  | Register Name                         |                 | Bit 7          | 6           | 5     | 4    | 3          | 2      | 1                           | Bit 0 |

|--------|---------------------------------------|-----------------|----------------|-------------|-------|------|------------|--------|-----------------------------|-------|

| \$FE00 | Break Status Register<br>(BSR)        | Read:<br>Write: | R              | R           | R     | R    | R          | R      | SBSW<br>Note <sup>(1)</sup> | R     |

|        | See page 199.                         | Reset:          | 0              | 0           | 0     | 0    | 0          | 0      | 0                           | 0     |

|        |                                       |                 | 1. Writing a ( | clears SBS\ | V.    |      |            |        |                             |       |

|        | SIM Reset Status Register             | Read:           | POR            | PIN         | COP   | ILOP | ILAD       | MODRST | LVI                         | 0     |

| \$FE01 | (SRSR)                                | Write:          |                |             |       |      |            |        |                             |       |

|        | See page 199.                         | POR:            | 1              | 0           | 0     | 0    | 0          | 0      | 0                           | 0     |

| \$FE03 | Break Flag Control Register<br>(BFCR) | Read:<br>Write: | BCFE           | R           | R     | R    | R          | R      | R                           | R     |

|        | See page 200.                         | Reset:          | 0              |             |       |      |            |        |                             |       |

|        | Interrupt Status Register 1           | Read:           | IF6            | IF5         | IF4   | IF3  | IF2        | IF1    | 0                           | 0     |

| \$FE04 | (INT1)                                | Write:          | R              | R           | R     | R    | R          | R      | R                           | R     |

|        | See page 195.                         | Reset:          | 0              | 0           | 0     | 0    | 0          | 0      | 0                           | 0     |

|        | Interrupt Status Register 2           | Read:           | IF14           | IF13        | IF12  | IF11 | IF10       | IF9    | IF8                         | IF7   |

| \$FE05 | (INT2)                                | Write:          | R              | R           | R     | R    | R          | R      | R                           | R     |

|        | See page 195.                         | Reset:          | 0              | 0           | 0     | 0    | 0          | 0      | 0                           | 0     |

|        | Interrupt Status Register 3           | Read:           | IF22           | IF32        | IF20  | IF19 | IF18       | IF17   | IF16                        | IF15  |

| \$FE06 | (INT3)                                | Write:          | R              | R           | R     | R    | R          | R      | R                           | R     |

|        | See page 195.                         | Reset:          | 0              | 0           | 0     | 0    | 0          | 0      | 0                           | 0     |

|        | Interrupt Status Register 4           | Read:           | 0              | 0           | 0     | 0    | 0          | 0      | IF24                        | IF23  |

| \$FE07 | (INT4)                                | Write:          | R              | R           | R     | R    | R          | R      | R                           | R     |

|        | See page 196.                         | Reset:          | 0              | 0           | 0     | 0    | 0          | 0      | 0                           | 0     |

|        |                                       |                 |                | = Unimplem  | ented | R    | = Reserved |        |                             |       |

Figure 14-2. SIM I/O Register Summary

#### Serial Peripheral Interface (SPI) Module

- 1. Pin contains integrated pullup device.

- 2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

- 3. Higher current drive port pins

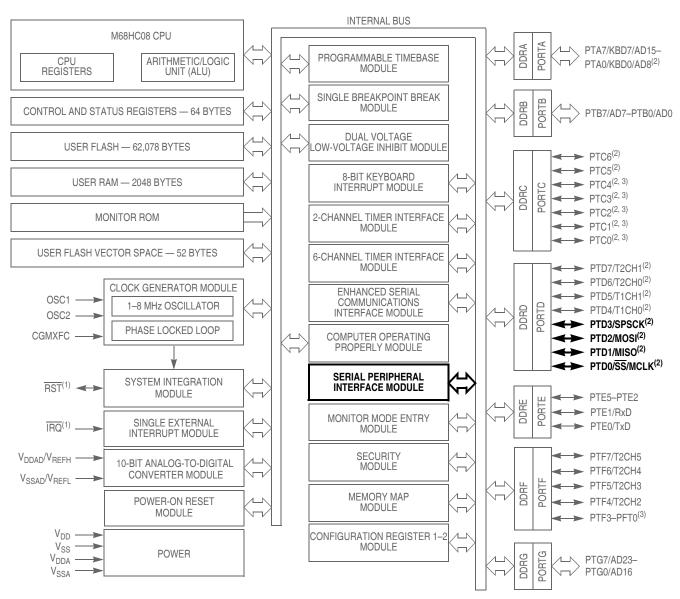

Figure 15-1. Block Diagram Highlighting SPI Block and Pins

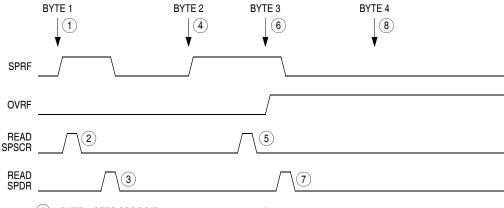

- BYTE 1 SETS SPRF BIT.

- (2) CPU READS SPSCR WITH SPRF BIT SET AND OVRF BIT CLEAR.

- (3) CPU READS BYTE 1 IN SPDR, CLEARING SPRF BIT.

- (4) BYTE 2 SETS SPRF BIT.

- (5) CPU READS SPSCR WITH SPRF BIT SET AND OVRF BIT CLEAR.

- (6) BYTE 3 SETS OVRF BIT. BYTE 3 IS LOST.

- 7 CPU READS BYTE 2 IN SPDR, CLEARING SPRF BIT, BUT NOT OVRF BIT.

- 8 BYTE 4 FAILS TO SET SPRF BIT BECAUSE OVRF BIT IS NOT CLEARED. BYTE 4 IS LOST.

Figure 15-10. Missed Read of Overflow Condition

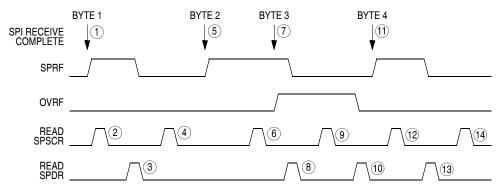

- (1) BYTE 1 SETS SPRF BIT.

- 2 CPU READS SPSCR WITH SPRF BIT SET AND OVRF BIT CLEAR.

- 3 CPU READS BYTE 1 IN SPDR, CLEARING SPRF BIT.

- 4 CPU READS SPSCR AGAIN TO CHECK OVRF BIT.

- (5) BYTE 2 SETS SPRF BIT.

- 6 CPU READS SPSCR WITH SPRF BIT SET AND OVRF BIT CLEAR.

- 7 BYTE 3 SETS OVRF BIT. BYTE 3 IS LOST.

- 8 CPU READS BYTE 2 IN SPDR, CLEARING SPRF BIT.

- 9 CPU READS SPSCR AGAIN TO CHECK OVRF BIT.

- (10) CPU READS BYTE 2 SPDR, CLEARING OVRF BIT.

- (11) BYTE 4 SETS SPRF BIT.

- (12) CPU READS SPSCR.

- (13) CPU READS BYTE 4 IN SPDR, CLEARING SPRF BIT.

- 14) CPU READS SPSCR AGAIN TO CHECK OVRF BIT.

Figure 15-11. Clearing SPRF When OVRF Interrupt Is Not Enabled

**Timebase Module (TBM)**

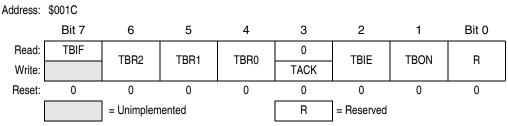

## 16.7 Timebase Control Register

The timebase has one register, the timebase control register (TBCR), which is used to enable the timebase interrupts and set the rate.

Figure 16-2. Timebase Control Register (TBCR)

#### TBIF — Timebase Interrupt Flag

This read-only flag bit is set when the timebase counter has rolled over.

- 1 = Timebase interrupt pending

- 0 = Timebase interrupt not pending

#### TBR2-TBR0 — Timebase Divider Selection Bits

These read/write bits select the tap in the counter to be used for timebase interrupts as shown in Table 16-1.

#### NOTE

Do not change TBR2-TBR0 bits while the timebase is enabled (TBON = 1).

## **TACK— Timebase Acknowledge Bit**

The TACK bit is a write-only bit and always reads as 0. Writing a 1 to this bit clears TBIF, the timebase interrupt flag bit. Writing a 0 to this bit has no effect.

- 1 = Clear timebase interrupt flag

- 0 = No effect

#### TBIE — Timebase Interrupt Enabled Bit

This read/write bit enables the timebase interrupt when the TBIF bit becomes set. Reset clears the TBIE bit.

- 1 = Timebase interrupt is enabled.

- 0 = Timebase interrupt is disabled.

#### **TBON** — Timebase Enabled Bit

This read/write bit enables the timebase. Timebase may be turned off to reduce power consumption when its function is not necessary. The counter can be initialized by clearing and then setting this bit. Reset clears the TBON bit.

- 1 = Timebase is enabled.

- 0 = Timebase is disabled and the counter initialized to 0s.

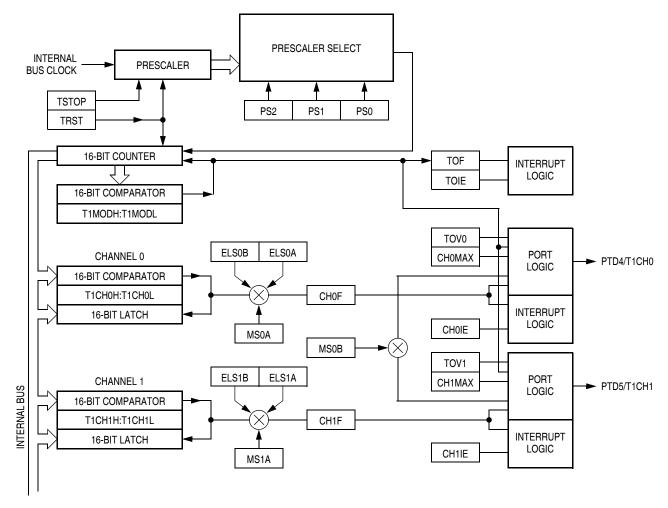

Figure 17-2. TIM1 Block Diagram

| Addr.         | Register Name              |        | Bit 7  | 6          | 5      | 4      | 3      | 2      | 1     | Bit 0 |

|---------------|----------------------------|--------|--------|------------|--------|--------|--------|--------|-------|-------|

|               | • ,                        | Read:  | TOF    | TOIE       | TSTOP  | 0      | 0      | PS2    | PS1   | PS0   |

| \$0020        |                            | -3 (/  | Write: | 0          | TOIL   | 13101  | TRST   |        | F 32  | FOI   |

| See page 234. | Reset:                     | 0      | 0      | 1          | 0      | 0      | 0      | 0      | 0     |       |

|               | TIM1 Counter Register High | Read:  | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| \$0021        |                            | Write: |        |            |        |        |        |        |       |       |

|               |                            | Reset: | 0      | 0          | 0      | 0      | 0      | 0      | 0     | 0     |

|               | TIM1 Counter Register Low  | Read:  | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| \$0022        |                            | Write: |        |            |        |        |        |        |       |       |

|               |                            | Reset: | 0      | 0          | 0      | 0      | 0      | 0      | 0     | 0     |

|               |                            |        |        | = Unimplen | nented |        |        |        |       |       |

Figure 17-3. TIM1 I/O Register Summary

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### **Timer Interface Module (TIM2)**

channel. Writing to the active channel registers is the same as generating unbuffered output compares.

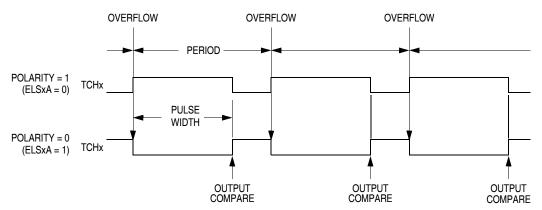

## 18.3.4 Pulse Width Modulation (PWM)

By using the toggle-on-overflow feature with an output compare channel, the TIM2 can generate a PWM signal. The value in the TIM2 counter modulo registers determines the period of the PWM signal. The channel pin toggles when the counter reaches the value in the TIM2 counter modulo registers. The time between overflows is the period of the PWM signal.

As Figure 18-4 shows, the output compare value in the TIM2 channel registers determines the pulse width of the PWM signal. The time between overflow and output compare is the pulse width. Program the TIM2 to clear the channel pin on output compare if the polarity of the PWM pulse is 1 (ELSxA = 0). Program the TIM2 to set the pin if the polarity of the PWM pulse is 0 (ELSxA = 1).

Figure 18-4. PWM Period and Pulse Width

The value in the TIM2 counter modulo registers and the selected prescaler output determines the frequency of the PWM output. The frequency of an 8-bit PWM signal is variable in 256 increments. Writing \$00FF (255) to the TIM2 counter modulo registers produces a PWM period of 256 times the internal bus clock period if the prescaler select value is 000 (see 18.8.1 TIM2 Status and Control Register).

The value in the TIM2 channel registers determines the pulse width of the PWM output. The pulse width of an 8-bit PWM signal is variable in 256 increments. Writing \$0080 (128) to the TIM2 channel registers produces a duty cycle of 128/256 or 50%.

#### 18.3.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 18.3.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the value currently in the TIM2 channel registers.

An unsynchronized write to the TIM2 channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM2 overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM2 may pass the new value before it is written to the timer channel (T2CHxH:T2CHxL) registers.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### **Development Support**

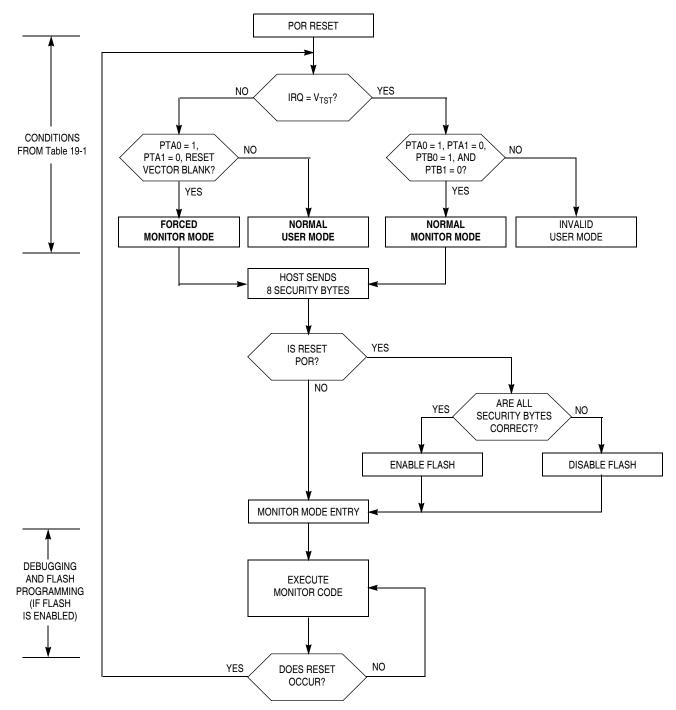

Figure 19-9. Simplified Monitor Mode Entry Flowchart

# **Chapter 20 Electrical Specifications**

## 20.1 Introduction

This section contains electrical and timing specifications.

## 20.2 Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it.

#### NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 20.5 5.0-Vdc Electrical Characteristics for guaranteed operating conditions.

| Characteristic <sup>(1)</sup>                           | Symbol                 | Value                                   | Unit |

|---------------------------------------------------------|------------------------|-----------------------------------------|------|

| Supply voltage                                          | V <sub>DD</sub>        | -0.3 to + 6.0                           | V    |

| Input voltage                                           | V <sub>In</sub>        | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3$ | V    |

| Maximum current per pin excluding those specified below | I                      | ± 15                                    | mA   |

| Maximum current for pins PTC0-PTC4                      | I <sub>PTC0-PTC4</sub> | ± 25                                    | mA   |

| Maximum current into V <sub>DD</sub>                    | I <sub>mvdd</sub>      | 150                                     | mA   |

| Maximum current out of V <sub>SS</sub>                  | I <sub>mvss</sub>      | 150                                     | mA   |

| Storage temperature                                     | T <sub>stg</sub>       | -55 to +150                             | °C   |

Voltages referenced to V<sub>SS</sub>

#### NOTE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{In}$  and  $V_{Out}$  be constrained to the range  $V_{SS} \leq (V_{In} \text{ or } V_{Out}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ ).