Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>-</b>                   |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Details                    |                                                                        |

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 21                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 24x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr48avfje |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 2.6.6   | FLASH-1 Program Operation                           | 47 |

|---------|-----------------------------------------------------|----|

| 2.6.7   | Low-Power Modes                                     | 48 |

| 2.6.7.  | 1 Wait Mode                                         | 48 |

| 2.6.7.2 | Stop Mode                                           | 48 |

| 2.7     | FLASH-2 Memory (FLASH-2)                            | 50 |

| 2.7.1   | Functional Description                              |    |

| 2.7.2   | FLASH-2 Control and Block Protect Registers         | 50 |

| 2.7.2.  |                                                     |    |

| 2.7.2.2 |                                                     |    |

| 2.7.3   | FLASH-2 Block Protection                            |    |

| 2.7.4   | FLASH-2 Mass Erase Operation                        |    |

| 2.7.5   | FLASH-2 Page Erase Operation                        |    |

| 2.7.6   | FLASH-2 Program Operation                           |    |

| 2.7.7   | Low-Power Modes                                     |    |

| 2.7.7.  |                                                     |    |

| 2.7.7.2 | Stop Mode                                           | 56 |

|         | Chamter 2                                           |    |

|         | Chapter 3                                           |    |

|         | Analog-to-Digital Converter (ADC)                   |    |

| 3.1     | Introduction                                        |    |

| 3.2     | Features                                            |    |

| 3.3     | Functional Description                              | 59 |

| 3.3.1   | ADC Port I/O Pins                                   |    |

| 3.3.2   | Voltage Conversion                                  |    |

| 3.3.3   | Conversion Time                                     |    |

| 3.3.4   | Conversion                                          |    |

| 3.3.5   | Accuracy and Precision                              |    |

| 3.3.6   | Result Justification                                |    |

| 3.4     | Monotonicity                                        |    |

| 3.5     | Interrupts                                          | 63 |

| 3.6     | Low-Power Modes                                     | 63 |

| 3.6.1   | Wait Mode                                           |    |

| 3.6.2   | Stop Mode                                           |    |

| 3.7     | I/O Signals                                         | 64 |

| 3.7.1   | ADC Analog Power Pin (V <sub>DDAD</sub> )           |    |

| 3.7.2   | ADC Analog Ground Pin (V <sub>SSAD</sub> )          |    |

| 3.7.3   | ADC Voltage Reference High Pin (V <sub>REFH</sub> ) |    |

| 3.7.4   | ADC Voltage Reference Low Pin (V <sub>REFL</sub> )  | 65 |

| 3.7.5   | ADC Voltage In (V <sub>ADIN</sub> )                 |    |

| 3.8     | I/O Registers                                       |    |

| 3.8.1   | ADC Status and Control Register                     |    |

| 3.8.2   | ADC Data Register High and Data Register Low        |    |

| 3.8.2.  |                                                     |    |

| 3.8.2.2 |                                                     |    |

| 3.8.2.3 | · · · · · · · · · · · · · · · · · · ·               |    |

| 3.8.2.4 |                                                     |    |

| 3.8.3   | ADC Clock Register                                  |    |

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### Analog-to-Digital Converter (ADC)

## ADICLK — ADC Input Clock Select Bit

ADICLK selects either the bus clock or the oscillator output clock (CGMXCLK) as the input clock source to generate the internal ADC clock. Reset selects CGMXCLK as the ADC clock source.

- 1 = Internal bus clock

- 0 = Oscillator output clock (CGMXCLK)

The ADC requires a clock rate of approximately 1 MHz for correct operation. If the selected clock source is not fast enough, the ADC will generate incorrect conversions. See 20.10 5.0-Volt ADC Characteristics.

$$f_{ADIC} = -\frac{f_{CGMXCLK} \text{ or bus frequency}}{ADIV[2:0]} \cong 1 \text{ MHz}$$

#### MODE1 and MODE0 — Modes of Result Justification Bits

MODE1 and MODE0 select among four modes of operation. The manner in which the ADC conversion results will be placed in the ADC data registers is controlled by these modes of operation. Reset returns right-justified mode.

00 = 8-bit truncation mode

01 = Right justified mode

10 = Left justified mode

11 = Left justified signed data mode

The following conditions apply when in manual mode:

- ACQ is a writable control bit that controls the mode of the filter. Before turning on the PLL in manual mode, the ACQ bit must be clear.

- Before entering tracking mode (ACQ = 1), software must wait a given time, t<sub>ACQ</sub> (See 4.8 Acquisition/Lock Time Specifications.), after turning on the PLL by setting PLLON in the PLL control register (PCTL).

- Software must wait a given time, t<sub>AL</sub>, after entering tracking mode before selecting the PLL as the clock source to CGMOUT (BCS = 1).

- The LOCK bit is disabled.

- CPU interrupts from the CGM are disabled.

## 4.3.6 Programming the PLL

Use the following procedure to program the PLL. For reference, the variables used and their meaning are shown in Table 4-1.

| Variable             | Definition                         |

|----------------------|------------------------------------|

| f <sub>BUSDES</sub>  | Desired bus clock frequency        |

| f <sub>VCLKDES</sub> | Desired VCO clock frequency        |

| f <sub>RCLK</sub>    | Chosen reference crystal frequency |

| f <sub>VCLK</sub>    | Calculated VCO clock frequency     |

| f <sub>BUS</sub>     | Calculated bus clock frequency     |

| f <sub>NOM</sub>     | Nominal VCO center frequency       |

| f <sub>VRS</sub>     | Programmed VCO center frequency    |

Table 4-1. Variable Definitions

## NOTE

The round function in the following equations means that the real number should be rounded to the nearest integer number.

- 1. Choose the desired bus frequency, f<sub>BUSDES</sub>.

- 2. Calculate the desired VCO frequency (four times the desired bus frequency).

$$f_{VCLKDES} = 4 \times f_{BUSDES}$$

Choose a practical PLL (crystal) reference frequency, f<sub>RCLK</sub>. Typically, the reference crystal is 1–8 MHz.

Frequency errors to the PLL are corrected at a rate of f<sub>RCLK</sub>.

For stability and lock time reduction, this rate must be as fast as possible. The VCO frequency must be an integer multiple of this rate. The relationship between the VCO frequency,  $f_{VCLK}$ , and the reference frequency,  $f_{RCLK}$ , is:

$$f_{VCLK} = (N) (f_{RCLK})$$

N, the range multiplier, must be an integer.

#### **Clock Generator Module (CGM)**

if the PLL is off. Therefore, PLLON cannot be cleared when BCS is set, and BCS cannot be set when PLLON is clear. If the PLL is off (PLLON = 0), selecting CGMVCLK requires two writes to the PLL control register. (See 4.3.8 Base Clock Selector Circuit.).

### VPR1 and VPR0 — VCO Power-of-Two Range Select Bits

These read/write bits control the VCO's hardware power-of-two range multiplier E that, in conjunction with L controls the hardware center-of-range frequency, f<sub>VRS</sub>. VPR1:VPR0 cannot be written when the PLLON bit is set. Reset clears these bits. (See 4.3.3 PLL Circuits, 4.3.6 Programming the PLL, and 4.5.5 PLL VCO Range Select Register.)

| VPR1 and VPR0 | E                | VCO Power-of-Two<br>Range Multiplier |

|---------------|------------------|--------------------------------------|

| 00            | 0                | 1                                    |

| 01            | 1                | 2                                    |

| 10            | 2 <sup>(1)</sup> | 4                                    |

Table 4-4. VPR1 and VPR0 Programming

#### NOTE

Verify that the value of the VPR1 and VPR0 bits in the PCTL register are appropriate for the given reference and VCO clock frequencies before enabling the PLL. See 4.3.6 Programming the PLL for detailed instructions on selecting the proper value for these control bits.

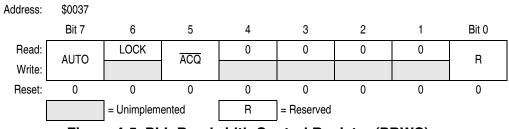

# 4.5.2 PLL Bandwidth Control Register

The PLL bandwidth control register (PBWC):

- Selects automatic or manual (software-controlled) bandwidth control mode

- Indicates when the PLL is locked

- In automatic bandwidth control mode, indicates when the PLL is in acquisition or tracking mode

- In manual operation, forces the PLL into acquisition or tracking mode

Figure 4-5. PLL Bandwidth Control Register (PBWC)

#### **AUTO** — Automatic Bandwidth Control Bit

This read/write bit selects automatic or manual bandwidth control. When initializing the PLL for manual operation (AUTO = 0), clear the  $\overline{ACQ}$  bit before turning on the PLL. Reset clears the AUTO bit.

- 1 = Automatic bandwidth control

- 0 = Manual bandwidth control

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

<sup>1.</sup> Do not program E to a value of 3.

**Clock Generator Module (CGM)**

## 4.7.2 Stop Mode

If the OSCENINSTOP bit in the CONFIG2 register is cleared (default), then the STOP instruction disables the CGM (oscillator and phase locked loop) and holds low all CGM outputs (CGMXCLK, CGMOUT, and CGMINT).

If the OSCENINSTOP bit in the CONFIG2 register is set, then the phase locked loop is shut off but the oscillator will continue to operate in stop mode.

## 4.7.3 CGM During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state. (See 14.7.3 Break Flag Control Register.)

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the PLLF bit during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write the PLL control register during the break state without affecting the PLLF bit.

# 4.8 Acquisition/Lock Time Specifications

The acquisition and lock times of the PLL are, in many applications, the most critical PLL design parameters. Proper design and use of the PLL ensures the highest stability and lowest acquisition/lock times.

# 4.8.1 Acquisition/Lock Time Definitions

Typical control systems refer to the acquisition time or lock time as the reaction time, within specified tolerances, of the system to a step input. In a PLL, the step input occurs when the PLL is turned on or when it suffers a noise hit. The tolerance is usually specified as a percent of the step input or when the output settles to the desired value plus or minus a percent of the frequency change. Therefore, the reaction time is constant in this definition, regardless of the size of the step input. For example, consider a system with a 5 percent acquisition time tolerance. If a command instructs the system to change from 0 Hz to 1 MHz, the acquisition time is the time taken for the frequency to reach 1 MHz  $\pm$ 50 kHz. Fifty kHz = 5% of the 1-MHz step input. If the system is operating at 1 MHz and suffers a  $\pm$ 100-kHz noise hit, the acquisition time is the time taken to return from 900 kHz to 1 MHz  $\pm$ 5 kHz. Five kHz = 5% of the 100-kHz step input.

Other systems refer to acquisition and lock times as the time the system takes to reduce the error between the actual output and the desired output to within specified tolerances. Therefore, the acquisition or lock time varies according to the original error in the output. Minor errors may not even be registered. Typical PLL applications prefer to use this definition because the system requires the output frequency to be within a certain tolerance of the desired frequency regardless of the size of the initial error.

### 4.8.2 Parametric Influences on Reaction Time

Acquisition and lock times are designed to be as short as possible while still providing the highest possible stability. These reaction times are not constant, however. Many factors directly and indirectly affect the acquisition time.

The most critical parameter which affects the reaction times of the PLL is the reference frequency,  $f_{RCLK}$ . This frequency is the input to the phase detector and controls how often the PLL makes corrections. For stability, the corrections must be small compared to the desired frequency, so several corrections are required to reduce the frequency error. Therefore, the slower the reference the longer it takes to make these corrections. This parameter is under user control via the choice of crystal frequency  $f_{XCLK}$ . (See 4.3.3 PLL Circuits and 4.3.6 Programming the PLL.)

Another critical parameter is the external filter network. The PLL modifies the voltage on the VCO by adding or subtracting charge from capacitors in this network. Therefore, the rate at which the voltage changes for a given frequency error (thus change in charge) is proportional to the capacitance. The size of the capacitor also is related to the stability of the PLL. If the capacitor is too small, the PLL cannot make small enough adjustments to the voltage and the system cannot lock. If the capacitor is too large, the PLL may not be able to adjust the voltage in a reasonable time. (See 4.8.3 Choosing a Filter.)

Also important is the operating voltage potential applied to  $V_{DDA}$ . The power supply potential alters the characteristics of the PLL. A fixed value is best. Variable supplies, such as batteries, are acceptable if they vary within a known range at very slow speeds. Noise on the power supply is not acceptable, because it causes small frequency errors which continually change the acquisition time of the PLL.

Temperature and processing also can affect acquisition time because the electrical characteristics of the PLL change. The part operates as specified as long as these influences stay within the specified limits. External factors, however, can cause drastic changes in the operation of the PLL. These factors include noise injected into the PLL through the filter capacitor, filter capacitor leakage, stray impedances on the circuit board, and even humidity or circuit board contamination.

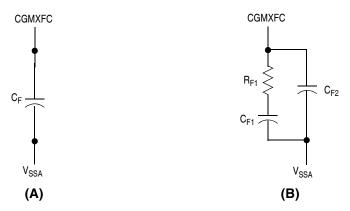

## 4.8.3 Choosing a Filter

As described in 4.8.2 Parametric Influences on Reaction Time, the external filter network is critical to the stability and reaction time of the PLL. The PLL is also dependent on reference frequency and supply voltage.

Figure 4-9 shows two types of filter circuits. In low-cost applications, where stability and reaction time of the PLL are not critical, the three component filter network shown in Figure 4-9 (B) can be replaced by a single capacitor, C<sub>F</sub>, as shown in shown in Figure 4-9 (A). Refer to Table 4-5 for recommended filter components at various reference frequencies. For reference frequencies between the values listed in the table, extrapolate to the nearest common capacitor value. In general, a slightly larger capacitor provides more stability at the expense of increased lock time.

Figure 4-9. PLL Filter

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## **Clock Generator Module (CGM)**

**Table 4-5. Example Filter Component Values**

| f <sub>RCLK</sub> | C <sub>F1</sub> | C <sub>F2</sub> | R <sub>F1</sub> | C <sub>F</sub> |

|-------------------|-----------------|-----------------|-----------------|----------------|

| 1 MHz             | 8.2 nF          | 820 pF          | 2k              | 18 nF          |

| 2 MHz             | 4.7 nF          | 470 pF          | 2k              | 6.8 nF         |

| 3 MHz             | 3.3 nF          | 330 pF          | 2k              | 5.6 nF         |

| 4 MHz             | 2.2 nF          | 220 pF          | 2k              | 4.7 nF         |

| 5 MHz             | 1.8 nF          | 180 pF          | 2k              | 3.9 nF         |

| 6 MHz             | 1.5 nF          | 150 pF          | 2k              | 3.3 nF         |

| 7 MHz             | 1.2 nF          | 120 pF          | 2k              | 2.7 nF         |

| 8 MHz             | 1 nF            | 100 pF          | 2k              | 2.2 nF         |

## **Central Processor Unit (CPU)**

# Table 7-1. Instruction Set Summary (Sheet 5 of 6)

| Source                                                                                          | Operation                                                      | Description                                                                                                                                                                                                                     |          | Effect on CCR |          |   |          |   | Address<br>Mode                                     | Opcode<br>Operand                                | rand                                      | es                                   |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|----------|---|----------|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| Form                                                                                            | Operation                                                      | Boothplion                                                                                                                                                                                                                      | ٧        | Н             | I        | N | z        | С | Add                                                 | Opc                                              | Ope                                       | Cycles                               |

| PULA                                                                                            | Pull A from Stack                                              | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                                              | -        | -             | -        | - | -        | - | INH                                                 | 86                                               |                                           | 2                                    |

| PULH                                                                                            | Pull H from Stack                                              | SP ← (SP + 1); Pull (H)                                                                                                                                                                                                         | -        | -             | -        | - | -        | _ | INH                                                 | 8A                                               |                                           | 2                                    |

| PULX                                                                                            | Pull X from Stack                                              | $SP \leftarrow (SP + 1); Pull(X)$                                                                                                                                                                                               | -        | -             | _        | - | _        | _ | INH                                                 | 88                                               |                                           | 2                                    |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                    | Rotate Left through Carry                                      | b7 b0                                                                                                                                                                                                                           | <b>‡</b> | _             | _        | 1 | 1        | 1 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X<br>ROR opr,SP                                    | Rotate Right through Carry                                     | b7 b0                                                                                                                                                                                                                           | 1        | _             | -        | 1 | 1        | Î | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| RSP                                                                                             | Reset Stack Pointer                                            | SP ← \$FF                                                                                                                                                                                                                       | -        | -             | -        | - | -        | _ | INH                                                 | 9C                                               |                                           | 1                                    |

| RTI                                                                                             | Return from Interrupt                                          | $\begin{array}{l} SP \leftarrow (SP) + 1;  Pull  (CCR) \\ SP \leftarrow (SP) + 1;  Pull  (A) \\ SP \leftarrow (SP) + 1;  Pull  (X) \\ SP \leftarrow (SP) + 1;  Pull  (PCH) \\ SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array}$ | 1        | 1             | <b>‡</b> | ‡ | <b>1</b> | ‡ | INH                                                 | 80                                               |                                           | 7                                    |

| RTS                                                                                             | Return from Subroutine                                         | $SP \leftarrow SP + 1$ ; Pull (PCH)<br>$SP \leftarrow SP + 1$ ; Pull (PCL)                                                                                                                                                      | -        | -             | -        | ı | ı        | _ | INH                                                 | 81                                               |                                           | 4                                    |

| SBC #opr<br>SBC opr<br>SBC opr,<br>SBC opr,X<br>SBC opr,X<br>SBC ,X<br>SBC opr,SP<br>SBC opr,SP | Subtract with Carry                                            | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                  | 1        | _             | _        | 1 | 1        | Î | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A2<br>B2<br>C2<br>D2<br>E2<br>F2<br>9EE2<br>9ED2 |                                           | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| SEC                                                                                             | Set Carry Bit                                                  | C ← 1                                                                                                                                                                                                                           | -        | -             | _        | _ | _        | 1 | INH                                                 | 99                                               |                                           | 1                                    |

| SEI                                                                                             | Set Interrupt Mask                                             | I ← 1                                                                                                                                                                                                                           | -        | -             | 1        | _ | _        | _ | INH                                                 | 9B                                               |                                           | 2                                    |

| STA opr<br>STA opr<br>STA opr,X<br>STA opr,X<br>STA ,X<br>STA opr,SP<br>STA opr,SP              | Store A in M                                                   | M ← (A)                                                                                                                                                                                                                         | 0        | _             | _        | 1 | 1        | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | B7<br>C7<br>D7<br>E7<br>F7<br>9EE7<br>9ED7       | dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 3<br>4<br>4<br>3<br>2<br>4<br>5      |

| STHX opr                                                                                        | Store H:X in M                                                 | (M:M + 1) ← (H:X)                                                                                                                                                                                                               | 0        | -             | -        | 1 | 1        | - | DIR                                                 | 35                                               | dd                                        | 4                                    |

| STOP                                                                                            | Enable Interrupts, Stop Processing, Refer to MCU Documentation | I ← 0; Stop Processing                                                                                                                                                                                                          | _        | -             | 0        | _ | _        | _ | INH                                                 | 8E                                               |                                           | 1                                    |

| STX opr<br>STX opr,<br>STX opr,X<br>STX opr,X<br>STX,X<br>STX opr,SP<br>STX opr,SP              | Store X in M                                                   | $M \leftarrow (X)$                                                                                                                                                                                                              | 0        | _             | _        | ‡ | ‡        | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | BF<br>CF<br>DF<br>EF<br>FF<br>9EEF<br>9EDF       |                                           | 3<br>4<br>4<br>3<br>2<br>4<br>5      |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB,X<br>SUB opr,SP<br>SUB opr,SP   | Subtract                                                       | $A \leftarrow (A) - (M)$                                                                                                                                                                                                        | 1        | -             | _        | ‡ | ‡        | ‡ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 |                                           | 23443245                             |

**Keyboard Interrupt Module (KBI)**

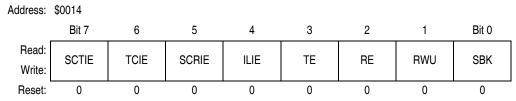

#### **Enhanced Serial Communications Interface (ESCI) Module**

- Enables the transmitter

- Enables the receiver

- Enables ESCI wakeup

- Transmits ESCI break characters

Figure 13-11. ESCI Control Register 2 (SCC2)

### SCTIE — ESCI Transmit Interrupt Enable Bit

This read/write bit enables the SCTE bit to generate ESCI transmitter CPU interrupt requests. Setting the SCTIE bit in SCC2 enables the SCTE bit to generate CPU interrupt requests. Reset clears the SCTIE bit.

- 1 = SCTE enabled to generate CPU interrupt

- 0 = SCTE not enabled to generate CPU interrupt

### TCIE — Transmission Complete Interrupt Enable Bit

This read/write bit enables the TC bit to generate ESCI transmitter CPU interrupt requests. Reset clears the TCIE bit.

- 1 = TC enabled to generate CPU interrupt requests

- 0 = TC not enabled to generate CPU interrupt requests

### SCRIE — ESCI Receive Interrupt Enable Bit

This read/write bit enables the SCRF bit to generate ESCI receiver CPU interrupt requests. Setting the SCRIE bit in SCC2 enables the SCRF bit to generate CPU interrupt requests. Reset clears the SCRIE bit.

- 1 = SCRF enabled to generate CPU interrupt

- 0 = SCRF not enabled to generate CPU interrupt

### ILIE — Idle Line Interrupt Enable Bit

This read/write bit enables the IDLE bit to generate ESCI receiver CPU interrupt requests. Reset clears the ILIE bit.

- 1 = IDLE enabled to generate CPU interrupt requests

- 0 = IDLE not enabled to generate CPU interrupt requests

### TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 1s from the transmit shift register to the TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the TxD returns to the idle condition (high). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted. Reset clears the TE bit.

- 1 = Transmitter enabled

- 0 = Transmitter disabled

### NOTE

Writing to the TE bit is not allowed when the enable ESCI bit (ENSCI) is clear. ENSCI is in ESCI control register 1.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

| PSSB[4:3:2:1:0] | Prescaler Divisor Fine Adjust (PDFA) |

|-----------------|--------------------------------------|

| 1 0 0 0 0       | 16/32 = 0.5                          |

| 1 0 0 0 1       | 17/32 = 0.53125                      |

| 1 0 0 1 0       | 18/32 = 0.5625                       |

| 1 0 0 1 1       | 19/32 = 0.59375                      |

| 1 0 1 0 0       | 20/32 = 0.625                        |

| 1 0 1 0 1       | 21/32 = 0.65625                      |

| 1 0 1 1 0       | 22/32 = 0.6875                       |

| 1 0 1 1 1       | 23/32 = 0.71875                      |

| 1 1 0 0 0       | 24/32 = 0.75                         |

| 1 1 0 0 1       | 25/32 = 0.78125                      |

| 1 1 0 1 0       | 26/32 = 0.8125                       |

| 1 1 0 1 1       | 27/32 = 0.84375                      |

| 1 1 1 0 0       | 28/32 = 0.875                        |

| 1 1 1 0 1       | 29/32 = 0.90625                      |

| 1 1 1 1 0       | 30/32 = 0.9375                       |

| 1 1 1 1 1       | 31/32 = 0.96875                      |

Use the following formula to calculate the ESCI baud rate:

Baud rate =

$$\frac{\text{Frequency of the SCI clock source}}{64 \times \text{BPD} \times \text{BD} \times (\text{PD} + \text{PDFA})}$$

#### where:

Frequency of the SCI clock source =  $f_{Bus}$  or CGMXCLK (selected by SCIBDSRC in the CONFIG2 register)

BPD = Baud rate register prescaler divisor

BD = Baud rate divisor

PD = Prescaler divisor

PDFA = Prescaler divisor fine adjust

Table 13-11 shows the ESCI baud rates that can be generated with a 4.9152-MHz bus frequency.

## 13.9 ESCI Arbiter

The ESCI module comprises an arbiter module designed to support software for communication tasks as bus arbitration, baud rate recovery and break time detection. The arbiter module consists of an 9-bit counter with 1-bit overflow and control logic. The CPU can control operation mode via the ESCI arbiter control register (SCIACTL).

**Enhanced Serial Communications Interface (ESCI) Module**

**System Integration Module (SIM)**

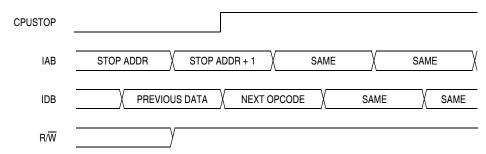

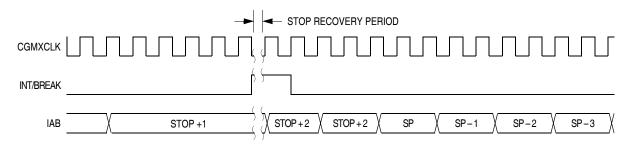

## 14.6.2 Stop Mode

In stop mode, the SIM counter is reset and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset also causes an exit from stop mode.

The SIM disables the clock generator module outputs (CGMOUT and CGMXCLK) in stop mode, stopping the CPU and peripherals. Stop recovery time is selectable using the SSREC bit in CONFIG1. If SSREC is set, stop recovery is reduced from the normal delay of 4096 CGMXCLK cycles down to 32. This is ideal for applications using canned oscillators that do not require long startup times from stop mode.

#### NOTE

External crystal applications should use the full stop recovery time by clearing the SSREC bit unless OSCENINSTOP bit is set in CONFIG2.

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 14-19 shows stop mode entry timing. Figure 14-20 shows stop mode recovery time from interrupt.

#### NOTE

To minimize stop current, all pins configured as inputs should be driven to a 1 or 0.

Note: Previous data can be operand data or the STOP opcode, depending on the last instruction.

Figure 14-19. Stop Mode Entry Timing

Figure 14-20. Stop Mode Recovery from Interrupt

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

an SPI configured as a slave does not have to correspond to any SPI baud rate. The baud rate only controls the speed of the SPSCK generated by an SPI configured as a master. Therefore, the frequency of the SPSCK for an SPI configured as a slave can be any frequency less than or equal to the bus speed.

When the master SPI starts a transmission, the data in the slave shift register begins shifting out on the MISO pin. The slave can load its shift register with a new byte for the next transmission by writing to its transmit data register. The slave must write to its transmit data register at least one bus cycle before the master starts the next transmission. Otherwise, the byte already in the slave shift register shifts out on the MISO pin. Data written to the slave shift register during a transmission remains in a buffer until the end of the transmission.

When the clock phase bit (CPHA) is set, the first edge of SPSCK starts a transmission. When CPHA is clear, the falling edge of  $\overline{SS}$  starts a transmission. See 15.4 Transmission Formats.

#### NOTE

SPSCK must be in the proper idle state before the slave is enabled to prevent SPSCK from appearing as a clock edge.

## 15.4 Transmission Formats

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock synchronizes shifting and sampling on the two serial data lines. A slave select line allows selection of an individual slave SPI device; slave devices that are not selected do not interfere with SPI bus activities. On a master SPI device, the slave select line can optionally be used to indicate multiple-master bus contention.

# 15.4.1 Clock Phase and Polarity Controls

Software can select any of four combinations of serial clock (SPSCK) phase and polarity using two bits in the SPI control register (SPCR). The clock polarity is specified by the CPOL control bit, which selects an active high or low clock and has no significant effect on the transmission format.

The clock phase (CPHA) control bit selects one of two fundamentally different transmission formats. The clock phase and polarity should be identical for the master SPI device and the communicating slave device. In some cases, the phase and polarity are changed between transmissions to allow a master device to communicate with peripheral slaves having different requirements.

#### NOTE

Before writing to the CPOL bit or the CPHA bit, disable the SPI by clearing the SPI enable bit (SPE).

#### 15.4.2 Transmission Format When CPHA = 0

Figure 15-5 shows an SPI transmission in which CPHA = 0. The figure should not be used as a replacement for data sheet parametric information.

Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input ( $\overline{SS}$ ) is low, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$  pin of the master must be high or must be reconfigured as

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

| Addr.                                          | Register Name                                         |                 | Bit 7  | 6                         | 5      | 4                         | 3             | 2      | 1      | Bit 0    |

|------------------------------------------------|-------------------------------------------------------|-----------------|--------|---------------------------|--------|---------------------------|---------------|--------|--------|----------|

| \$0457                                         | TIM2 Channel 2 Register High<br>(T2CH2H)              | Read:<br>Write: | Bit 15 | 14                        | 13     | 12                        | 11            | 10     | 9      | Bit 8    |

|                                                | See page 258.                                         | Reset:          |        | Indeterminate after reset |        |                           |               |        |        |          |

| \$0458                                         | TIM2 Channel 2 Register Low<br>(T2CH2L)               | Read:<br>Write: | Bit 7  | 6                         | 5      | 4                         | 3             | 2      | 1      | Bit 0    |

|                                                | See page 258.                                         | Reset:          |        |                           |        | Indeterminate             | e after reset |        |        |          |

|                                                | TIM2 Channel 3 Status and                             | Read:           | CH3F   | CH3IE                     | 0      | MS3A                      | ELS3B         | ELS3A  | TOV3   | CH3MAX   |

| \$0459                                         | Control Register (T2SC3)                              | Write:          | 0      | OHOLE                     |        | IVISSA                    | ELGOD         | ELSSA  | 1073   | CHOWAX   |

|                                                | See page 255.                                         | Reset:          | 0      | 0                         | 0      | 0                         | 0             | 0      | 0      | 0        |

| \$045A                                         | TIM2 Channel 3 Register High (T2CH3H)                 | Read:<br>Write: | Bit 15 | 14                        | 13     | 12                        | 11            | 10     | 9      | Bit 8    |

|                                                | See page 258.                                         | Reset:          |        |                           |        | Indeterminate             | e after reset |        |        |          |

| \$045B                                         | TIM2 Channel 3 Register Low<br>(T2CH3L)               | Read:<br>Write: | Bit 7  | 6                         | 5      | 4                         | 3             | 2      | 1      | Bit 0    |

|                                                | See page 258.                                         | Reset:          |        | l .                       |        | Indeterminate after reset |               |        |        |          |

|                                                | TIM2 Channel 4 Status and<br>Control Register (T2SC4) | Read:           | CH4F   | CHAIE                     | MC4D   | MC4A                      | EL CAD        | EL C4A | TOV4   | CH4MAX   |

| \$045C                                         |                                                       | Write:          | 0      | CH4IE                     | MS4B   | MS4A                      | ELS4B         | ELS4A  | TOV4   | CH4IVIAX |

|                                                | See page 255.                                         | Reset:          | 0      | 0                         | 0      | 0                         | 0             | 0      | 0      | 0        |

| \$045D                                         | TIM2 Channel 4 Register High<br>(T2CH4H)              | Read:<br>Write: | Bit 15 | 14                        | 13     | 12                        | 11            | 10     | 9      | Bit 8    |

|                                                | See page 258.                                         | Reset:          |        |                           |        | Indeterminate             | e after reset |        |        |          |

| \$045E                                         | TIM2 Channel 4 Register Low<br>(T2CH4L)               | Read:<br>Write: | Bit 7  | 6                         | 5      | 4                         | 3             | 2      | 1      | Bit 0    |

|                                                | See page 258.                                         | Reset:          |        |                           |        | Indeterminate             | e after reset |        |        |          |

|                                                | 045F Control Register (T2SC5) Write:                  | CH5F            | CH5IE  | 0                         | - MS5A | ELS5B                     | ELS5A         | TOV5   | CH5MAX |          |

| \$045F                                         |                                                       | Write:          | 0      | OHOLE                     |        | NCCIVI                    | ELSOB         | ELSSA  | 1005   | CHOIVIAX |

|                                                | See page 255.                                         | Reset:          | 0      | 0                         | 0      | 0                         | 0             | 0      | 0      | 0        |

| \$0460                                         | TIM2 Channel 5 Register High (T2CH5H)                 | Read:<br>Write: | Bit 15 | 14                        | 13     | 12                        | 11            | 10     | 9      | Bit 8    |

| See page 258. Reset: Indeterminate after reset |                                                       |                 |        |                           |        |                           |               |        |        |          |

| \$0461                                         | TIM2 Channel 5 Register Low<br>(T2CH5L)               | Read:<br>Write: | Bit 7  | 6                         | 5      | 4                         | 3             | 2      | 1      | Bit 0    |

|                                                | See page 258.                                         | Reset:          |        |                           |        | Indeterminate after reset |               |        |        |          |

|                                                |                                                       |                 |        | = Unimpler                | mented |                           |               |        |        |          |

Figure 18-3. TIM2 I/O Register Summary (Sheet 2 of 2)

## 18.3.1 TIM2 Counter Prescaler

The TIM2 clock source can be one of the seven prescaler outputs or the TIM2 clock pin, T2CH0. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM2 status and control register select the TIM2 clock source.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

compare value may cause the compare to be missed. The TIM2 may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new

value in the output compare interrupt routine. The output compare interrupt occurs at the end of

the current output compare pulse. The interrupt routine has until the end of the counter overflow

period to write the new value.

- When changing to a larger output compare value, enable TIM2 overflow interrupts and write the

new value in the TIM2 overflow interrupt routine. The TIM2 overflow interrupt occurs at the end of

the current counter overflow period. Writing a larger value in an output compare interrupt routine

(at the end of the current pulse) could cause two output compares to occur in the same counter

overflow period.

### 18.3.3.2 Buffered Output Compare

Channels 0 and 1 can be linked to form a buffered output compare channel whose output appears on the T2CH0 pin. The TIM2 channel registers of the linked pair alternately control the output.

Setting the MS0B bit in TIM2 channel 0 status and control register (T2SC0) links channel 0 and channel 1. The output compare value in the TIM2 channel 0 registers initially controls the output on the T2CH0 pin. Writing to the TIM2 channel 1 registers enables the TIM2 channel 1 registers to synchronously control the output after the TIM2 overflows. At each subsequent overflow, the TIM2 channel registers (0 or 1) that control the output are the ones written to last. T2SC0 controls and monitors the buffered output compare function, and TIM2 channel 1 status and control register (T2SC1) is unused. While the MS0B bit is set, the channel 1 pin, T2CH1, is available as a general-purpose I/O pin.

Channels 2 and 3 can be linked to form a buffered output compare channel whose output appears on the T2CH2 pin. The TIM2 channel registers of the linked pair alternately control the output.

Setting the MS2B bit in TIM2 channel 2 status and control register (T2SC2) links channel 2 and channel 3. The output compare value in the TIM2 channel 2 registers initially controls the output on the T2CH2 pin. Writing to the TIM2 channel 3 registers enables the TIM2 channel 3 registers to synchronously control the output after the TIM2 overflows. At each subsequent overflow, the TIM2 channel registers (2 or 3) that control the output are the ones written to last. T2SC2 controls and monitors the buffered output compare function, and TIM2 channel 3 status and control register (T2SC3) is unused. While the MS2B bit is set, the channel 3 pin, T2CH3, is available as a general-purpose I/O pin.

Channels 4 and 5 can be linked to form a buffered output compare channel whose output appears on the T2CH4 pin. The TIM2 channel registers of the linked pair alternately control the output.

Setting the MS4B bit in TIM2 channel 4 status and control register (T2SC4) links channel 4 and channel 5. The output compare value in the TIM2 channel 4 registers initially controls the output on the T2CH4 pin. Writing to the TIM2 channel 5 registers enables the TIM2 channel 5 registers to synchronously control the output after the TIM2 overflows. At each subsequent overflow, the TIM2 channel registers (4 or 5) that control the output are the ones written to last. T2SC4 controls and monitors the buffered output compare function, and TIM2 channel 5 status and control register (T2SC5) is unused. While the MS4B bit is set, the channel 5 pin, T2CH5, is available as a general-purpose I/O pin.

#### NOTE

In buffered output compare operation, do not write new output compare values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### **Timer Interface Module (TIM2)**

### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM2 counter registers matches the value in the TIM2 channel x registers.

When CHxIE = 1, clear CHxF by reading TIM2 channel x status and control register with CHxF set, and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

# CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM2 CPU interrupts on channel x.

Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

#### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIM2 channel 0, TIM2 channel 2, and TIM2 channel 4 status and control registers.

Setting MS0B disables the channel 1 status and control register and reverts T2CH1 pin to general-purpose I/O.

Setting MS2B disables the channel 3 status and control register and reverts T2CH3 pin to general-purpose I/O.

Setting MS4B disables the channel 5 status and control register and reverts T2CH5 pin to general-purpose I/O.

Reset clears the MSxB bit.

- 1 = Buffered output compare/PWM operation enabled

- 0 = Buffered output compare/PWM operation disabled

### MSxA — Mode Select Bit A

When ELSxB:ELSxA  $\neq$  00, this read/write bit selects either input capture operation or unbuffered output compare/PWM operation. (See Table 18-2.)

- 1 = Unbuffered output compare/PWM operation

- 0 = Input capture operation

When ELSxB:ELSxA = 00, this read/write bit selects the initial output level of the T2CHx pin once PWM, input capture, or output compare operation is enabled. (See Table 18-2.) Reset clears the MSxA bit

- 1 = Initial output level low

- 0 = Initial output level high

### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM2 status and control register (T2SC).

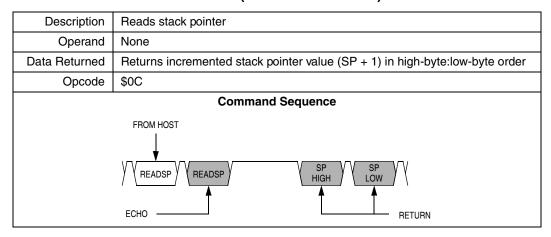

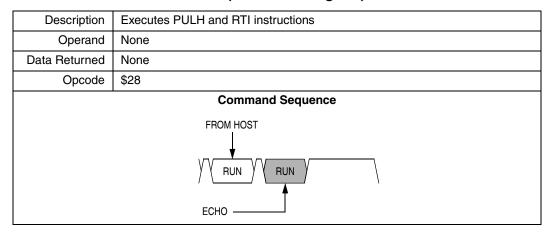

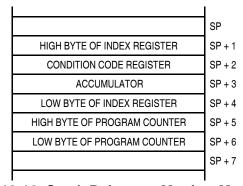

### Table 19-7. READSP (Read Stack Pointer) Command

Table 19-8. RUN (Run User Program) Command

The MCU executes the SWI and PSHH instructions when it enters monitor mode. The RUN command tells the MCU to execute the PULH and RTI instructions. Before sending the RUN command, the host can modify the stacked CPU registers to prepare to run the host program. The READSP command returns the incremented stack pointer value, SP + 1. The high and low bytes of the program counter are at addresses SP + 5 and SP + 6.

Figure 19-16. Stack Pointer at Monitor Mode Entry

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## 20.9.3 CGM Acquisition/Lock Time Information

| Characteristic                                                           | Symbol            | Min                                 | Тур                     | Max                                    | Unit |

|--------------------------------------------------------------------------|-------------------|-------------------------------------|-------------------------|----------------------------------------|------|

| Acquisition mode entry frequency tolerance <sup>(1)</sup>                | $\Delta_{ACQ}$    | ± 3.6                               | _                       | ± 7.2                                  | %    |

| Tracking mode entry frequency tolerance <sup>(2)</sup>                   | $\Delta_{TRK}$    | 0                                   | _                       | ± 3.6                                  | %    |

| LOCK entry frequency tolerance <sup>(3)</sup>                            | $\Delta_{LOCK}$   | 0                                   | _                       | ± 0.9                                  | %    |

| LOCK exit frequency tolerance <sup>(4)</sup>                             | $\Delta_{UNL}$    | ± 0.9                               | _                       | ± 1.8                                  | %    |

| Reference cycles per acquisition mode period                             | n <sub>ACQ</sub>  | _                                   | 32                      | _                                      |      |

| Reference cycles per tracking mode period                                | n <sub>TRK</sub>  | _                                   | 128                     | _                                      |      |

| Automatic mode time to stable                                            | t <sub>ACQ</sub>  | n <sub>ACQ</sub> /f <sub>RCLK</sub> | See note <sup>(5)</sup> | _                                      | s    |

| Automatic stable to lock time                                            | t <sub>AL</sub>   | n <sub>TRK</sub> /f <sub>RCLK</sub> | See note <sup>(6)</sup> | _                                      | s    |

| Automatic lock time (t <sub>ACQ</sub> + t <sub>AL</sub> ) <sup>(7)</sup> | t <sub>LOCK</sub> | _                                   | 5                       | 25                                     | ms   |

| PLL jitter, deviation of average bus frequency over 2 ms period          | f <sub>J</sub>    | 0                                   | _                       | f <sub>RCLK</sub> x<br>0.025% x<br>N/4 | Hz   |

- 1. Deviation between VCO frequency and desired frequency to enter PLL acquisition mode.

- 2. Deviation between VCO frequency and desired frequency to enter PLL tracking mode (stable).

- 3. Deviation between VCO frequency and desired frequency to enter locked mode.

- 4. Deviation between VCO frequency and desired frequency to exit locked mode.

- 5. Acquisition time is an integer multiple of reference cycles divided by reference clock.

- 6. Stable to lock time is an integer multiple of reference cycles divided by reference clock.

- 7. Maximum lock time depends on CGMXFC filter components, power supply filtering, and reference clock stability. PLL may not lock if improper components or poor filtering and layout are used.

### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2, INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

- $\sqrt{3}$ . Datums A, B, and D to be determined at datum plane H.

- 4 dimensions to be determined at seating plane datum c.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THZ LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

- 6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

- A EXACT SHAPE OF EACH CORNER IS OPTIONAL.

- A. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 MM AND 0.25 MM FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NOT TO SCA |             |  |  |  |

|---------------------------------------------------------|-----------|--------------|--------------------------|-------------|--|--|--|

| TITLE:                                                  | ITLE:     |              |                          | REV: C      |  |  |  |

| LOW PROFILE QUAD FLAT PARTY                             |           | CASE NUMBER  | R: 873A-04               | 01 APR 2005 |  |  |  |

| 32 LEAD, 0.8 PITCH (7 X                                 | 7 X 1.4)  | STANDARD: JE | IDEC MS-026 BBA          |             |  |  |  |