Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 53                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 24x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-QFP                                                                 |

| Supplier Device Package    | 64-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr48avfue |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

$V_{REFL}$  is the low reference supply for the ADC, and by default the  $V_{SSAD}/V_{REFL}$  pin should be connected to the same voltage potential as  $V_{SS}$ . See Chapter 3 Analog-to-Digital Converter (ADC).

# 1.5.8 Port A Input/Output (I/O) Pins (PTA7/KBD7/AD15-PTA0/KBD0/AD8)

PTA7–PTA0 are general-purpose, bidirectional I/O port pins. Any or all of the port A pins can be programmed to serve as keyboard interrupt pins or used as analog-to-digital inputs. PTA7–PTA4 are only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 12 Input/Output (I/O) Ports, Chapter 9 Keyboard Interrupt Module (KBI), and Chapter 3 Analog-to-Digital Converter (ADC).

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

## 1.5.9 Port B I/O Pins (PTB7/AD7-PTB0/AD0)

PTB7–PTB0 are general-purpose, bidirectional I/O port pins that can also be used for analog-to-digital converter (ADC) inputs. PTB7–PTB6 are only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 12 Input/Output (I/O) Ports and Chapter 3 Analog-to-Digital Converter (ADC).

## 1.5.10 Port C I/O Pins (PTC6-PTC0)

PTC6 and PTC5 are general-purpose, bidirectional I/O port pins.

PTC4–PTC0 are general-purpose, bidirectional I/O port pins that contain higher current sink/source capability. PTC6–PTC2 are only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 12 Input/Output (I/O) Ports.

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

# 1.5.11 Port D I/O Pins (PTD7/T2CH1-PTD0/SS)

PTD7–PTD0 are special-function, bidirectional I/O port pins. PTD3–PTD0 can be programmed to be serial peripheral interface (SPI) pins, while PTD7–PTD4 can be individually programmed to be timer interface module (TIM1 and TIM2) pins. PTD0 can be used to output a clock, MCLK. PTD7 is only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 17 Timer Interface Module (TIM1), Chapter 18 Timer Interface Module (TIM2), Chapter 15 Serial Peripheral Interface (SPI) Module, Chapter 12 Input/Output (I/O) Ports, and Chapter 5 Configuration Register (CONFIG).

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

## 1.5.12 Port E I/O Pins (PTE5-PTE2, PTE1/RxD, and PTE0/TxD)

PTE5–PTE0 are general-purpose, bidirectional I/O port pins. PTE1 and PTE0 can also be programmed to be enhanced serial communications interface (ESCI) pins. PTE5–PTE2 are only available on the 48-pin LQFP and 64-pin QFP packages. See Chapter 13 Enhanced Serial Communications Interface (ESCI) Module and Chapter 12 Input/Output (I/O) Ports.

## 1.5.13 Port F I/O Pins (PTF7/T2CH5-PTF0)

PTF7–PTF4 are special-function, bidirectional I/O port pins that can be individually programmed to be timer interface module (TIM2) pins.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

#### **General Description**

PTF3-PTF0 are general-purpose, bidirectional I/O port pins that contain higher current sink/source capability.

PTF7–PTF0 are only available on the 64-pin QFP package. See Chapter 17 Timer Interface Module (TIM1), Chapter 18 Timer Interface Module (TIM2), and Chapter 12 Input/Output (I/O) Ports.

## 1.5.14 Port G I/O Pins (PTG7/AD23-PTBG0/AD16)

PTG7–PTG0 are general-purpose, bidirectional I/O port pins that can also be used for analog-to-digital converter (ADC) inputs. PTG7–PTG0 are only available on the 64-pin QFP package. See Chapter 12 Input/Output (I/O) Ports and Chapter 3 Analog-to-Digital Converter (ADC).

## 1.5.15 Unused Pin Termination

Input pins and I/O port pins that are not used in the application must be terminated. This prevents excess current caused by floating inputs, and enhances immunity during noise or transient events. Termination methods include:

- 1. Configuring unused pins as outputs and driving high or low;

- 2. Configuring unused pins as inputs and enabling internal pull-ups;

- 3. Configuring unused pins as inputs and using external pull-up or pull-down resistors.

Never connect unused pins directly to V<sub>DD</sub> or V<sub>SS</sub>.

Since some general-purpose I/O pins are not available on all packages, these pins must be terminated as well. Either method 1 or 2 above are appropriate.

## Memory

**Table 2-1. Vector Addresses (Continued)**

| Vector Priority | Vector            | Address | Vector                       |

|-----------------|-------------------|---------|------------------------------|

|                 | IF14              | \$FFE0  | Keyboard Vector (High)       |

|                 | IF 1 <del>4</del> | \$FFE1  | Keyboard Vector (Low)        |

|                 | IE10              | \$FFE2  | ESCI Transmit Vector (High)  |

|                 | IF13              | \$FFE3  | ESCI Transmit Vector (Low)   |

|                 | IF12              | \$FFE4  | ESCI Receive Vector (High)   |

|                 | IF 12             | \$FFE5  | ESCI Receive Vector (Low)    |

|                 | IF11              | \$FFE6  | ESCI Error Vector (High)     |

|                 | IFII              | \$FFE7  | ESCI Error Vector (Low)      |

|                 | IF10              | \$FFE8  | SPI Transmit Vector (High)   |

|                 | IFIU              | \$FFE9  | SPI Transmit Vector (Low)    |

|                 | IF9               | \$FFEA  | SPI Receive Vector (High)    |

|                 | 11-9              | \$FFEB  | SPI Receive Vector (Low)     |

|                 | IEO               | \$FFEC  | TIM2 Overflow Vector (High)  |

|                 | IF8               | \$FFED  | TIM2 Overflow Vector (Low)   |

|                 | IF7               | \$FFEE  | TIM2 Channel 1 Vector (High) |

|                 | IF7               | \$FFEF  | TIM2 Channel 1 Vector (Low)  |

|                 | IF6               | \$FFF0  | TIM2 Channel 0 Vector (High) |

|                 | IFO               | \$FFF1  | TIM2 Channel 0 Vector (Low)  |

|                 | IF5               | \$FFF2  | TIM1 Overflow Vector (High)  |

|                 | IFS               | \$FFF3  | TIM1 Overflow Vector (Low)   |

|                 | IE4               |         | TIM1 Channel 1 Vector (High) |

|                 | IF4               | \$FFF5  | TIM1 Channel 1 Vector (Low)  |

|                 | IF3               | \$FFF6  | TIM1 Channel 0 Vector (High) |

|                 | IFS               | \$FFF7  | TIM1 Channel 0 Vector (Low)  |

|                 | IF2               | \$FFF8  | PLL Vector (High)            |

|                 | IF2               | \$FFF9  | PLL Vector (Low)             |

|                 | IE1               | \$FFFA  | ĪRQ Vector (High)            |

|                 | IF1               | \$FFFB  | ĪRQ Vector (Low)             |

|                 |                   | \$FFFC  | SWI Vector (High)            |

|                 | _                 | \$FFFD  | SWI Vector (Low)             |

| <b>\</b>        | _                 | \$FFFE  | Reset Vector (High)          |

| Highest         | _                 | \$FFFF  | Reset Vector (Low)           |

#### Analog-to-Digital Converter (ADC)

## ADICLK — ADC Input Clock Select Bit

ADICLK selects either the bus clock or the oscillator output clock (CGMXCLK) as the input clock source to generate the internal ADC clock. Reset selects CGMXCLK as the ADC clock source.

- 1 = Internal bus clock

- 0 = Oscillator output clock (CGMXCLK)

The ADC requires a clock rate of approximately 1 MHz for correct operation. If the selected clock source is not fast enough, the ADC will generate incorrect conversions. See 20.10 5.0-Volt ADC Characteristics.

$$f_{ADIC} = -\frac{f_{CGMXCLK} \text{ or bus frequency}}{ADIV[2:0]} \cong 1 \text{ MHz}$$

#### MODE1 and MODE0 — Modes of Result Justification Bits

MODE1 and MODE0 select among four modes of operation. The manner in which the ADC conversion results will be placed in the ADC data registers is controlled by these modes of operation. Reset returns right-justified mode.

00 = 8-bit truncation mode

01 = Right justified mode

10 = Left justified mode

11 = Left justified signed data mode

# 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register. See Chapter 5 Configuration Register (CONFIG).

# 6.3.7 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the configuration register. See Chapter 5 Configuration Register (CONFIG).

# 6.4 COP Control Register

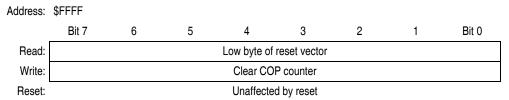

The COP control register (COPCTL) is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 6-2. COP Control Register (COPCTL)

# 6.5 Interrupts

The COP does not generate central processor unit (CPU) interrupt requests.

## 6.6 Monitor Mode

When monitor mode is entered with  $V_{TST}$  on the IRQ pin, the COP is disabled as long as  $V_{TST}$  remains on the IRQ pin or the RST pin. When monitor mode is entered by having blank reset vectors and not having  $V_{TST}$  on the IRQ pin, the COP is automatically disabled until a POR occurs.

## 6.7 Low-Power Modes

The WAIT and STOP instructions put the microcontroller unit (MCU) in low power-consumption standby modes.

#### 6.7.1 Wait Mode

The COP remains active during wait mode. If COP is enabled, a reset will occur at COP timeout.

## 6.7.2 Stop Mode

Stop mode turns off the CGMXCLK input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

External Interrupt (IRQ)

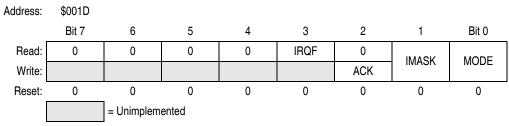

# 8.6 IRQ Status and Control Register

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. The INTSCR:

- · Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

Figure 8-3. IRQ Status and Control Register (INTSCR)

## IRQF — IRQ Flag Bit

This read-only status bit is high when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- 0 = IRQ interrupt not pending

## ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0. Reset clears ACK.

# IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables IRQ interrupt requests. Reset clears IMASK.

- 1 = IRQ interrupt requests disabled

- 0 = IRQ interrupt requests enabled

## MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin. Reset clears MODE.

- $1 = \overline{IRQ}$  interrupt requests on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt requests on falling edges only

#### **Keyboard Interrupt Module (KBI)**

If the MODEK bit is set and depending on the KBIPx bit, the keyboard interrupt pins are both falling (or rising) edge and low (or high) level sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a 1 to the ACKK bit in the keyboard status and control register (INTKBSCR). The ACKK bit is useful in applications that poll the keyboard interrupt pins and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt pins. A falling (or rising) edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the CPU loads the program counter with the vector address at locations \$FFE0 and \$FFE1.

- Return of all enabled keyboard interrupt pins to 1 (or 0) As long as any enabled keyboard interrupt pin is 0 (or 1), the keyboard interrupt remains set.

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to 1 (or 0) may occur in any order.

If the MODEK bit is clear and depending on the KBIPx bit, the keyboard interrupt pin is falling (or rising) edge sensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt pin stays at 0 (or 1).

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

To determine the logic level on a keyboard interrupt pin, use the data direction register to configure the pin as an input and read the data register.

### NOTE

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a 0 for software to read the pin.

# 9.4 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pullup/pulldown device to reach a 1 (or 0). Therefore, a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

- 2. Enable the KBI pins and polarity by setting the appropriate KBIEx bits in the keyboard interrupt enable register and the KBIPx bits in the keyboard interrupt polarity register.

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

- 4. Clear the IMASKK bit.

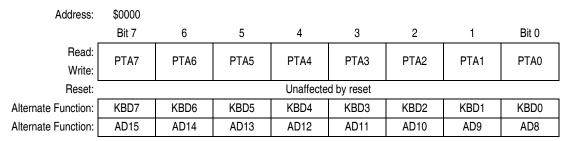

## 12.3 Port A

Port A is an 8-bit special-function port that shares all eight of its pins with the keyboard interrupt (KBI) module and the ADC module. Port A also has software configurable pullup devices if configured as an input port.

## 12.3.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the eight port A pins.

Figure 12-2. Port A Data Register (PTA)

#### PTA7-PTA0 — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

## **KBD7-KBD0** — Keyboard Inputs

The keyboard interrupt enable bits, KBIE7–KBIE0, in the keyboard interrupt control register (KBICR) enable the port A pins as external interrupt pins. See Chapter 9 Keyboard Interrupt Module (KBI)

## AD15-AD8 — Analog-to-Digital Input Bits

AD15—AD8 are pins used for the input channels to the analog-to-digital converter module. The channel select bits in the ADC status and control register define which port A pin will be used as an ADC input and overrides any control from the port I/O logic by forcing that pin as the input to the analog circuitry.

#### NOTE

Care must be taken when reading port A while applying analog voltages to AD15–AD8 pins. If the appropriate ADC channel is not enabled, excessive current drain may occur if analog voltages are applied to the PTAx/KBDx/ADx pin, while PTA is read as a digital input during the CPU read cycle. Those ports not selected as analog input channels are considered digital I/O ports.

#### **Enhanced Serial Communications Interface (ESCI) Module**

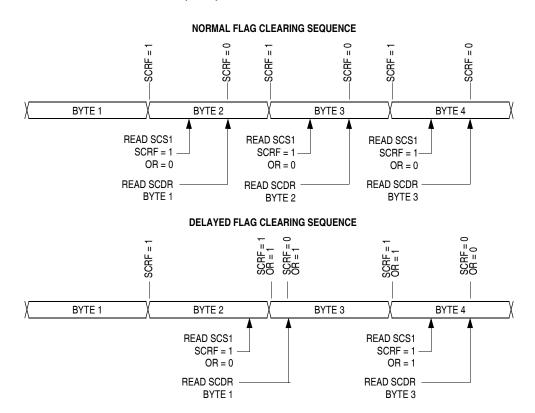

Figure 13-14. Flag Clearing Sequence

In applications that are subject to software latency or in which it is important to know which byte is lost due to an overrun, the flag-clearing routine can check the OR bit in a second read of SCS1 after reading the data register.

## NF — Receiver Noise Flag Bit

This clearable, read-only bit is set when the ESCI detects noise on the RxD pin. NF generates an NF CPU interrupt request if the NEIE bit in SCC3 is also set. Clear the NF bit by reading SCS1 and then reading the SCDR. Reset clears the NF bit.

- 1 = Noise detected

- 0 = No noise detected

#### FE — Receiver Framing Error Bit

This clearable, read-only bit is set when a 0 is accepted as the stop bit. FE generates an ESCI error CPU interrupt request if the FEIE bit in SCC3 also is set. Clear the FE bit by reading SCS1 with FE set and then reading the SCDR. Reset clears the FE bit.

- 1 = Framing error detected

- 0 = No framing error detected

#### PE — Receiver Parity Error Bit

This clearable, read-only bit is set when the ESCI detects a parity error in incoming data. PE generates a PE CPU interrupt request if the PEIE bit in SCC3 is also set. Clear the PE bit by reading SCS1 with PE set and then reading the SCDR. Reset clears the PE bit.

- 1 = Parity error detected

- 0 = No parity error detected

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## 13.8.5 ESCI Status Register 2

ESCI status register 2 (SCS2) contains flags to signal these conditions:

- Break character detected

- Incoming data

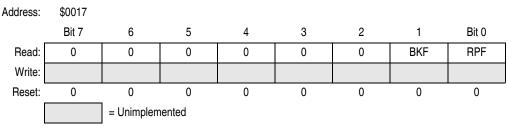

Figure 13-15. ESCI Status Register 2 (SCS2)

## **BKF** — Break Flag Bit

This clearable, read-only bit is set when the ESCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

- 1 = Break character detected

- 0 = No break character detected

## RPF — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch), or when the receiver detects an idle character. Polling RPF before disabling the ESCI module or entering stop mode can show whether a reception is in progress.

- 1 = Reception in progress

- 0 = No reception in progress

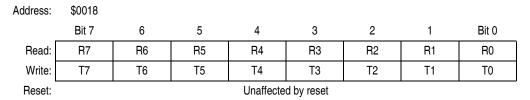

## 13.8.6 ESCI Data Register

The ESCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the ESCI data register.

Figure 13-16. ESCI Data Register (SCDR)

#### R7/T7:R0/T0 — Receive/Transmit Data Bits

Reading address \$0018 accesses the read-only received data bits, R7:R0. Writing to address \$0018 writes the data to be transmitted, T7:T0. Reset has no effect on the ESCI data register.

#### NOTE

Do not use read-modify-write instructions on the ESCI data register.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## **Enhanced Serial Communications Interface (ESCI) Module**

#### PDS2-PDS0 — Prescaler Divisor Select Bits

These read/write bits select the prescaler divisor as shown in Table 13-9. Reset clears PDS2-PDS0.

#### NOTE

The setting of '000' will bypass this prescaler. It is not recommended to bypass the prescaler while ENSCI is set, because the switching is not glitch free.

**Table 13-9. ESCI Prescaler Division Ratio**

| PDS[2:1:0] | Prescaler Divisor (PD) |

|------------|------------------------|

| 0 0 0      | Bypass this prescaler  |

| 0 0 1      | 2                      |

| 0 1 0      | 3                      |

| 0 1 1      | 4                      |

| 1 0 0      | 5                      |

| 1 0 1      | 6                      |

| 1 1 0      | 7                      |

| 1 1 1      | 8                      |

## PSSB4-PSSB0 — Clock Insertion Select Bits

These read/write bits select the number of clocks inserted in each 32 output cycle frame to achieve more timing resolution on the **average** prescaler frequency as shown in Table 13-10. Reset clears PSSB4–PSSB0.

Table 13-10. ESCI Prescaler Divisor Fine Adjust

| PSSB[4:3:2:1:0] | Prescaler Divisor Fine Adjust (PDFA) |

|-----------------|--------------------------------------|

| 0 0 0 0 0       | 0/32 = 0                             |

| 0 0 0 0 1       | 1/32 = 0.03125                       |

| 0 0 0 1 0       | 2/32 = 0.0625                        |

| 0 0 0 1 1       | 3/32 = 0.09375                       |

| 0 0 1 0 0       | 4/32 = 0.125                         |

| 0 0 1 0 1       | 5/32 = 0.15625                       |

| 0 0 1 1 0       | 6/32 = 0.1875                        |

| 0 0 1 1 1       | 7/32 = 0.21875                       |

| 0 1 0 0 0       | 8/32 = 0.25                          |

| 0 1 0 0 1       | 9/32 = 0.28125                       |

| 0 1 0 1 0       | 10/32 = 0.3125                       |

| 0 1 0 1 1       | 11/32 = 0.34375                      |

| 0 1 1 0 0       | 12/32 = 0.375                        |

| 0 1 1 0 1       | 13/32 = 0.40625                      |

| 0 1 1 1 0       | 14/32 = 0.4375                       |

| 0 1 1 1 1       | 15/32 = 0.46875                      |

Continued on next page

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

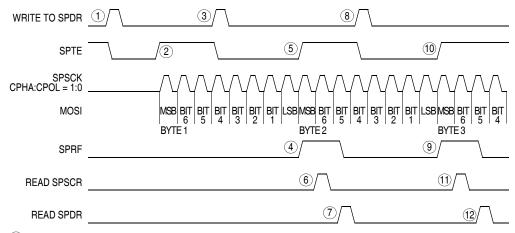

# 15.5 Queuing Transmission Data

The double-buffered transmit data register allows a data byte to be queued and transmitted. For an SPI configured as a master, a queued data byte is transmitted immediately after the previous transmission has completed. The SPI transmitter empty flag (SPTE) indicates when the transmit data buffer is ready to accept new data. Write to the transmit data register only when SPTE is high. Figure 15-9 shows the timing associated with doing back-to-back transmissions with the SPI (SPSCK has CPHA: CPOL = 1:0).

- CPU WRITES BYTE 1 TO SPDR, CLEARING SPTE BIT.

- ② BYTE 1 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- 3 CPU WRITES BYTE 2 TO SPDR, QUEUEING BYTE 2 AND CLEARING SPTE BIT.

- FIRST INCOMING BYTE TRANSFERS FROM SHIFT REGISTER TO RECEIVE DATA REGISTER, SETTING SPRF BIT.

- (5) BYTE 2 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- (6) CPU READS SPSCR WITH SPRF BIT SET.

- (7) CPU READS SPDR, CLEARING SPRF BIT.

- (8) CPU WRITES BYTE 3 TO SPDR, QUEUEING BYTE 3 AND CLEARING SPTE BIT.

- 9 SECOND INCOMING BYTE TRANSFERS FROM SHIFT REGISTER TO RECEIVE DATA REGISTER, SETTING SPRF BIT.

- (10) BYTE 3 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- 11) CPU READS SPSCR WITH SPRF BIT SET.

- (12) CPU READS SPDR, CLEARING SPRF BIT.

Figure 15-9. SPRF/SPTE CPU Interrupt Timing

The transmit data buffer allows back-to-back transmissions without the slave precisely timing its writes between transmissions as in a system with a single data buffer. Also, if no new data is written to the data buffer, the last value contained in the shift register is the next data word to be transmitted.

For an idle master or idle slave that has no data loaded into its transmit buffer, the SPTE is set again no more than two bus cycles after the transmit buffer empties into the shift register. This allows the user to queue up a 16-bit value to send. For an already active slave, the load of the shift register cannot occur until the transmission is completed. This implies that a back-to-back write to the transmit data register is not possible. SPTE indicates when the next write can occur.

#### **Timer Interface Module (TIM1)**

- 4. In TIM1 channel x status and control register (T1SCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB:MSxA. See Table 17-2.

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (polarity 1 to clear output on compare) or 1:1 (polarity 0 to set output on compare) to the edge/level select bits, ELSxB:ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 17-2.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIM1 status control register (T1SC), clear the TIM1 stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM1 channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM1 status control register 0 (TSCR0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM1 overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 17.8.4 TIM1 Channel Status and Control Registers.

# 17.4 Interrupts

The following TIM1 sources can generate interrupt requests:

- TIM1 overflow flag (TOF) The TOF bit is set when the TIM1 counter reaches the modulo value programmed in the TIM1 counter modulo registers. The TIM1 overflow interrupt enable bit, TOIE, enables TIM1 overflow CPU interrupt requests. TOF and TOIE are in the TIM1 status and control register.

- TIM1 channel flags (CH1F:CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIM CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE. Channel x TIM CPU interrupt requests are enabled when CHxIE =1. CHxF and CHxIE are in the TIM1 channel x status and control register.

## 17.5 Wait Mode

The WAIT instruction puts the MCU in low power-consumption standby mode.

The TIM1 remains active after the execution of a WAIT instruction. In wait mode the TIM1 registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM1 can bring the MCU out of wait mode.

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

# **Timer Interface Module (TIM2)**

| Addr.       | Register Name                                                                 |                 | Bit 7                     | 6          | 5     | 4             | 3             | 2     | 1    | Bit 0    |

|-------------|-------------------------------------------------------------------------------|-----------------|---------------------------|------------|-------|---------------|---------------|-------|------|----------|

|             | TIM2 Status and Control                                                       | Read:           | TOF                       | TOIL       | TSTOP | 0             | 0             | DCO   | DC1  | DCO      |

| \$002B      |                                                                               | Write:          | 0                         | 0 TOIE     |       | TRST          |               | PS2   | PS1  | PS0      |

|             | See page 252.                                                                 | Reset:          | 0                         | 0          | 1     | 0             | 0             | 0     | 0    | 0        |

|             | TIM2 Counter Register High                                                    | Read:           | Bit 15                    | 14         | 13    | 12            | 11            | 10    | 9    | Bit 8    |

| \$002C      | (T2CNTH)                                                                      | Write:          |                           |            |       |               |               |       |      |          |

|             | See page 254.                                                                 | Reset:          | 0                         | 0          | 0     | 0             | 0             | 0     | 0    | 0        |

|             | TIM2 Counter Register Low                                                     | Read:           | Bit 7                     | 6          | 5     | 4             | 3             | 2     | 1    | Bit 0    |

| \$002D      | (T2CNTL)                                                                      | Write:          |                           |            |       |               |               |       |      |          |

|             | See page 254.                                                                 | Reset:          | 0                         | 0          | 0     | 0             | 0             | 0     | 0    | 0        |

| \$002E      | TIM2 Modulo Register High<br>(T2MODH)                                         | Read:<br>Write: | Bit 15                    | 14         | 13    | 12            | 11            | 10    | 9    | Bit 8    |

|             | See page 254.                                                                 | Reset:          | 1                         | 1          | 1     | 1             | 1             | 1     | 1    | 1        |

| \$002F      | TIM2 Modulo Register Low<br>(T2MODL)                                          | Read:<br>Write: | Bit 7                     | 6          | 5     | 4             | 3             | 2     | 1    | Bit 0    |

|             | See page 254.                                                                 | Reset:          | 1                         | 1          | 1     | 1             | 1             | 1     | 1    | 1        |

| \$0030      | TIM2 Channel 0 Status and<br>\$0030 Control Register (T2SC0)<br>See page 255. | Read:<br>Write: | CH0F<br>0                 | - CH0IE    | MS0B  | MS0A          | ELS0B         | ELS0A | TOV0 | CHOMAX   |

|             |                                                                               | Reset:          | 0                         | 0          | 0     | 0             | 0             | 0     | 0    | 0        |

| \$0031      | TIM2 Channel 0 Register High (T2CH0H)                                         | Read:<br>Write: | Bit 15                    | 14         | 13    | 12            | 11            | 10    | 9    | Bit 8    |

|             | See page 258.                                                                 | Reset:          | Indeterminate after reset |            |       |               |               |       |      |          |

| \$0032      | TIM2 Channel 0 Register Low<br>(T2CH0L)                                       | Read:<br>Write: | Bit 7                     | 6          | 5     | 4             | 3             | 2     | 1    | Bit 0    |

|             | See page 258.                                                                 | Reset:          |                           |            |       | Indeterminate | e after reset |       |      |          |

|             | TIM2 Channel 1 Status and                                                     | Read:           | CH1F                      | CH1IE      | 0     | MS1A          | ELS1B         | ELS1A | TOV1 | CH1MAX   |

| \$0033      | Control Register (T2SC1)                                                      | Write:          | 0                         | OTTIL      |       | IVIOTA        | LLOID         | LLOIK | 1001 | CITIVIAX |

|             | See page 255.                                                                 | Reset:          | 0                         | 0          | 0     | 0             | 0             | 0     | 0    | 0        |

| \$0034      | TIM2 Channel 1 Register High (T2CH1H)                                         | Read:<br>Write: | Bit 15                    | 14         | 13    | 12            | 11            | 10    | 9    | Bit 8    |

|             | See page 258.                                                                 | Reset:          |                           |            |       | Indeterminate | e after reset |       |      |          |

| \$0035      | TIM2 Channel 1 Register Low<br>(T2CH1L)                                       | Read:<br>Write: | Bit 7                     | 6          | 5     | 4             | 3             | 2     | 1    | Bit 0    |

|             | See page 258.                                                                 | Reset:          |                           |            |       | Indeterminate | e after reset |       |      |          |

| \$0456      | TIM2 Channel 2 Status and<br>Control Register (T2SC2)                         | Read:<br>Write: | CH2F<br>0                 | - CH2IE    | MS2B  | MS2A          | ELS2B         | ELS2A | TOV2 | CH2MAX   |

| See page 25 |                                                                               | Reset:          | 0                         | 0          | 0     | 0             | 0             | 0     | 0    | 0        |

|             |                                                                               |                 | -                         | 1          |       | -             | -             | -     | -    | -        |

|             |                                                                               | 7.0001.         | Ÿ                         | = Unimpler |       | v             | v             | v     | Ŭ    | v        |

Figure 18-3. TIM2 I/O Register Summary (Sheet 1 of 2)

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

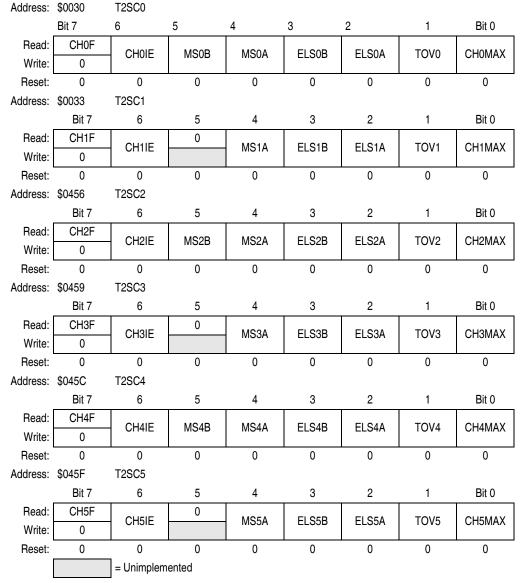

# 18.8.4 TIM2 Channel Status and Control Registers

Each of the TIM2 channel status and control registers:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- · Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM2 overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Figure 18-8. TIM2 Channel Status and Control Registers (T2SC0:T2SC5)

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

## **Development Support**

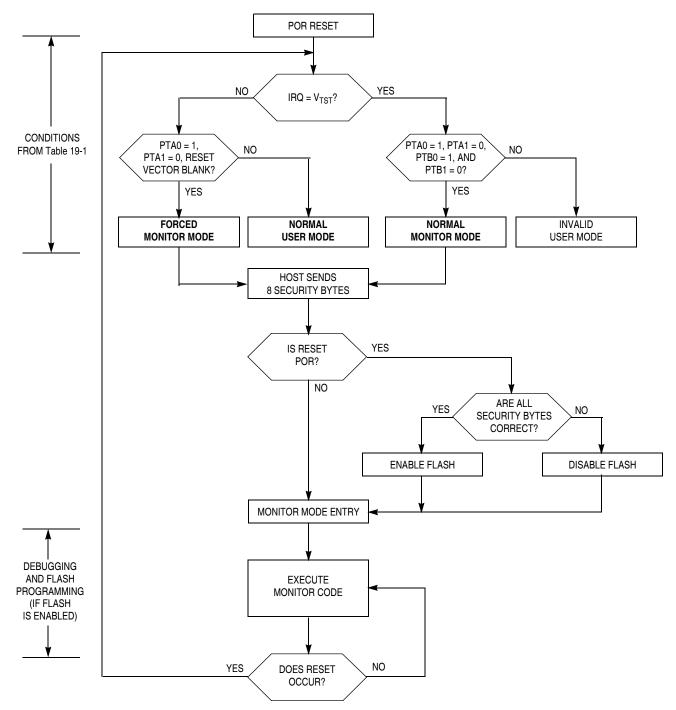

Figure 19-9. Simplified Monitor Mode Entry Flowchart

#### **Development Support**

**Table 19-1. Monitor Mode Signal Requirements and Options**

| Mode                           | ĪRQ                                      | RST                                       | Reset           | Sei<br>Commu |              | -            | ode<br>ction | Divider      | PLL | DI I     | СОР               | Communication<br>Speed |              |  |

|--------------------------------|------------------------------------------|-------------------------------------------|-----------------|--------------|--------------|--------------|--------------|--------------|-----|----------|-------------------|------------------------|--------------|--|

| Wode                           | ing                                      | noi                                       | Vector          | PTA0         | PTA1         | РТВ0         | PTB1         | PTB4         | PLL | 00.      | External<br>Clock | Bus<br>Frequency       | Baud<br>Rate |  |

| Normal                         | V <sub>TST</sub>                         | V <sub>DD</sub><br>or<br>V <sub>TST</sub> | Х               | 1            | 0            | 1            | 0            | 0            | OFF | Disabled | 4.0 MHz           | 2.0 MHz                | 7200         |  |

| Monitor                        | V <sub>TST</sub>                         | V <sub>DD</sub><br>or<br>V <sub>TST</sub> | х               | 1            | 0            | 1            | 0            | 1            | OFF | Disabled | 8.0 MHz           | 2.0 MHz                | 7200         |  |

| Forced<br>Monitor              | V <sub>DD</sub><br>or<br>V <sub>SS</sub> | V <sub>DD</sub>                           | \$FF<br>(blank) | 1            | 0            | х            | х            | Х            | OFF | Disabled | 8.0 MHz           | 2.0 MHz                | 7200         |  |

| User                           | V <sub>DD</sub><br>or<br>V <sub>SS</sub> | V <sub>DD</sub><br>or<br>V <sub>TST</sub> | Not<br>\$FF     | Х            | Х            | х            | х            | Х            | Х   | Enabled  | х                 | Х                      | Х            |  |

| MON08<br>Function<br>[Pin No.] | V <sub>TST</sub><br>[6]                  | RST<br>[4]                                | _               | COM<br>[8]   | SSEL<br>[10] | MOD0<br>[12] | MOD1<br>[14] | DIV4<br>[16] | _   | _        | OSC1<br>[13]      | _                      | _            |  |

- 1. PTA0 must have a pullup resistor to  $V_{DD}$  in monitor mode.

- 2. Communication speed in the table is an example to obtain a baud rate of 7200. Baud rate using external oscillator is bus frequency / 278.

- 3. External clock is a 4.0 MHz or 8.0 MHz crystal on OSC1 and OSC2 or a canned oscillator on OSC1.

- 4. X = don't care

- 5. MON08 pin refers to P&E Microcomputer Systems' MON08-Cyclone 2 by 8-pin connector.

| NC       | 1  | 2  | GND  |

|----------|----|----|------|

| NC       | 3  | 4  | RST  |

| NC       | 5  | 6  | ĪRQ  |

| NC       | 7  | 8  | PTA0 |

| NC       | 9  | 10 | PTA1 |

| NC       | 11 | 12 | PTB0 |

| OSC1     | 13 | 14 | PTB1 |

| $V_{DD}$ | 15 | 16 | PTB4 |

|          |    |    |      |

Enter monitor mode with pin configuration shown in Table 19-1 by pulling RST low and then high. The rising edge of RST latches monitor mode. Once monitor mode is latched, the levels on the port pins except PTA0 can change.

Once out of reset, the MCU waits for the host to send eight security bytes (see 19.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive 0s) to the host, indicating that it is ready to receive a command.

# 20.9.3 CGM Acquisition/Lock Time Information

| Characteristic                                                           | Symbol            | Min                                 | Тур                     | Max                                    | Unit |

|--------------------------------------------------------------------------|-------------------|-------------------------------------|-------------------------|----------------------------------------|------|

| Acquisition mode entry frequency tolerance <sup>(1)</sup>                | $\Delta_{ACQ}$    | ± 3.6                               | _                       | ± 7.2                                  | %    |

| Tracking mode entry frequency tolerance <sup>(2)</sup>                   | $\Delta_{TRK}$    | 0                                   | _                       | ± 3.6                                  | %    |

| LOCK entry frequency tolerance <sup>(3)</sup>                            | $\Delta_{LOCK}$   | 0                                   | _                       | ± 0.9                                  | %    |

| LOCK exit frequency tolerance <sup>(4)</sup>                             | $\Delta_{UNL}$    | ± 0.9                               | _                       | ± 1.8                                  | %    |

| Reference cycles per acquisition mode period                             | n <sub>ACQ</sub>  | _                                   | 32                      | _                                      |      |

| Reference cycles per tracking mode period                                | n <sub>TRK</sub>  | _                                   | 128                     | _                                      |      |

| Automatic mode time to stable                                            | t <sub>ACQ</sub>  | n <sub>ACQ</sub> /f <sub>RCLK</sub> | See note <sup>(5)</sup> | _                                      | s    |

| Automatic stable to lock time                                            | t <sub>AL</sub>   | n <sub>TRK</sub> /f <sub>RCLK</sub> | See note <sup>(6)</sup> | _                                      | s    |

| Automatic lock time (t <sub>ACQ</sub> + t <sub>AL</sub> ) <sup>(7)</sup> | t <sub>LOCK</sub> | _                                   | 5                       | 25                                     | ms   |

| PLL jitter, deviation of average bus frequency over 2 ms period          | f <sub>J</sub>    | 0                                   | _                       | f <sub>RCLK</sub> x<br>0.025% x<br>N/4 | Hz   |

- 1. Deviation between VCO frequency and desired frequency to enter PLL acquisition mode.

- 2. Deviation between VCO frequency and desired frequency to enter PLL tracking mode (stable).

- 3. Deviation between VCO frequency and desired frequency to enter locked mode.

- 4. Deviation between VCO frequency and desired frequency to exit locked mode.

- 5. Acquisition time is an integer multiple of reference cycles divided by reference clock.

- 6. Stable to lock time is an integer multiple of reference cycles divided by reference clock.

- 7. Maximum lock time depends on CGMXFC filter components, power supply filtering, and reference clock stability. PLL may not lock if improper components or poor filtering and layout are used.

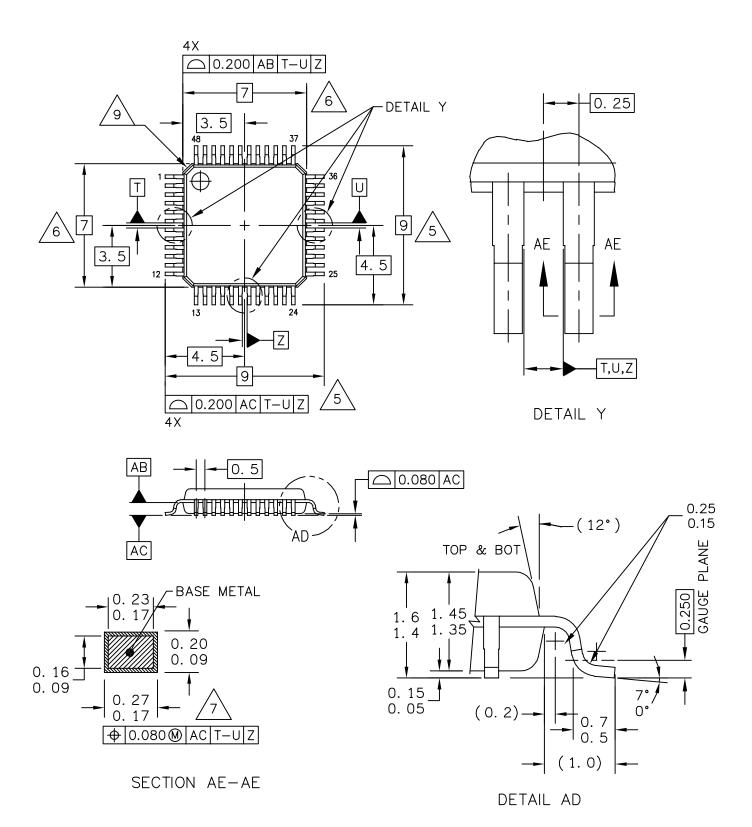

| FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |      |                                |                 | OT TO SCALE |

|-------------------------------------------------------|------|--------------------------------|-----------------|-------------|

| TITLE:                                                |      |                                | ): 98ASH00962A  | REV: G      |

| LQFP, 48 LEAD, 0.50 PITCH<br>(7.0 X 7.0 X 1.4)        |      | CASE NUMBER: 932-03 14 APR 200 |                 |             |

| ( /. U X /. U X                                       | 1.4) | STANDARD: JE                   | EDEC MS-026-BBC |             |

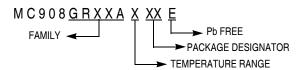

# A.4 Ordering Information

Table A-1. MC Order Numbers

| MC Order Number | Operating<br>Temperature Range | Package            |

|-----------------|--------------------------------|--------------------|

| MC908GR48ACFJ   | -40°C to +85°C                 | 32-pin low-profile |

| MC908GR48AVFJ   | -40°C to +105°C                | quad flat package  |

| MC908GR48AMFJ   | -40°C to +125°C                | (LQFP)             |

| MC908GR48ACFA   | -40°C to +85°C                 | 48-pin low-profile |

| MC908GR48AVFA   | -40°C to +105°C                | quad flat package  |

| MC908GR48AMFA   | -40°C to +125°C                | (LQFP)             |

| MC908GR48ACFU   | -40°C to +85°C                 | 64-pin quad flat   |

| MC908GR48AVFU   | −40°C to +105°C                | package            |

| MC908GR48AMFU   | -40°C to +125°C                | (QFP)              |

Temperature designators:

$C = -40^{\circ}C$  to  $+85^{\circ}C$   $V = -40^{\circ}C$  to  $+105^{\circ}C$   $M = -40^{\circ}C$  to  $+125^{\circ}C$

Figure A-3. Device Numbering System