# E·XFL

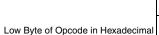

#### NXP USA Inc. - MC908GR60AMFUE Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 53                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 24x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-QFP                                                                 |

| Supplier Device Package    | 64-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr60amfue |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Vector Priority** Vector Address Vector \$FFE0 Keyboard Vector (High) IF14 Keyboard Vector (Low) \$FFE1 \$FFE2 ESCI Transmit Vector (High) IF13 \$FFE3 ESCI Transmit Vector (Low) \$FFE4 ESCI Receive Vector (High) IF12 \$FFE5 ESCI Receive Vector (Low) \$FFE6 ESCI Error Vector (High) IF11 \$FFE7 ESCI Error Vector (Low) \$FFE8 SPI Transmit Vector (High) IF10 \$FFE9 SPI Transmit Vector (Low) \$FFEA SPI Receive Vector (High) IF9 \$FFEB SPI Receive Vector (Low) \$FFEC TIM2 Overflow Vector (High) IF8 \$FFED TIM2 Overflow Vector (Low) \$FFEE TIM2 Channel 1 Vector (High) IF7 \$FFEF TIM2 Channel 1 Vector (Low) TIM2 Channel 0 Vector (High) \$FFF0 IF6 \$FFF1 TIM2 Channel 0 Vector (Low) \$FFF2 TIM1 Overflow Vector (High) IF5 \$FFF3 TIM1 Overflow Vector (Low) \$FFF4 TIM1 Channel 1 Vector (High) IF4 \$FFF5 TIM1 Channel 1 Vector (Low) \$FFF6 TIM1 Channel 0 Vector (High) IF3 \$FFF7 TIM1 Channel 0 Vector (Low) \$FFF8 PLL Vector (High) IF2 \$FFF9 PLL Vector (Low) IRQ Vector (High) \$FFFA IF1 \$FFFB **IRQ** Vector (Low) \$FFFC SWI Vector (High) \$FFFD SWI Vector (Low) \$FFFE Reset Vector (High) Highest \$FFFF Reset Vector (Low)

| Table 2-1. Vector Addresses (C |

|--------------------------------|

|--------------------------------|

Analog-to-Digital Converter (ADC)

# 3.3.3 Conversion Time

Conversion starts after a write to the ADC status and control register (ADSCR). One conversion will take between 16 and 17 ADC clock cycles. The ADIVx and ADICLK bits should be set to provide a 1-MHz ADC clock frequency.

Conversion time =  $\frac{16 \text{ to } 17 \text{ ADC cycles}}{\text{ADC frequency}}$

Number of bus cycles = conversion time  $\times$  bus frequency

# 3.3.4 Conversion

In continuous conversion mode, the ADC data register will be filled with new data after each conversion. Data from the previous conversion will be overwritten whether that data has been read or not. Conversions will continue until the ADCO bit is cleared. The COCO bit is set after each conversion and will stay set until the next read of the ADC data register.

In single conversion mode, conversion begins with a write to the ADSCR. Only one conversion occurs between writes to the ADSCR.

When a conversion is in process and the ADSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

## 3.3.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

#### 3.3.6 Result Justification

The conversion result may be formatted in four different ways:

- 1. Left justified

- 2. Right justified

- 3. Left Justified sign data mode

- 4. 8-bit truncation mode

All four of these modes are controlled using MODE0 and MODE1 bits located in the ADC clock register (ADCLK).

Left justification will place the eight most significant bits (MSB) in the corresponding ADC data register high, ADRH. This may be useful if the result is to be treated as an 8-bit result where the two least significant bits (LSB), located in the ADC data register low, ADRL, can be ignored. However, ADRL must be read after ADRH or else the interlocking will prevent all new conversions from being stored.

Right justification will place only the two MSBs in the corresponding ADC data register high, ADRH, and the eight LSBs in ADC data register low, ADRL. This mode of operation typically is used when a 10-bit unsigned result is desired.

Left justified sign data mode is similar to left justified mode with one exception. The MSB of the 10-bit result, AD9 located in ADRH, is complemented. This mode of operation is useful when a result, represented as a signed magnitude from mid-scale, is needed. Finally, 8-bit truncation mode will place the eight MSBs in the ADC data register low, ADRL. The two LSBs are dropped. This mode of operation is used when compatibility with 8-bit ADC designs are required. No interlocking between ADRH and ADRL is present.

#### **Clock Generator Module (CGM)**

# 4.3.4 Acquisition and Tracking Modes

The PLL filter is manually or automatically configurable into one of two operating modes:

- Acquisition mode In acquisition mode, the filter can make large frequency corrections to the VCO. This mode is used at PLL start up or when the PLL has suffered a severe noise hit and the VCO frequency is far off the desired frequency. When in acquisition mode, the ACQ bit is clear in the PLL bandwidth control register. (See 4.5.2 PLL Bandwidth Control Register.)

- Tracking mode In tracking mode, the filter makes only small corrections to the frequency of the VCO. PLL jitter is much lower in tracking mode, but the response to noise is also slower. The PLL enters tracking mode when the VCO frequency is nearly correct, such as when the PLL is selected as the base clock source. (See 4.3.8 Base Clock Selector Circuit.) The PLL is automatically in tracking mode when not in acquisition mode or when the ACQ bit is set.

#### 4.3.5 Manual and Automatic PLL Bandwidth Modes

The PLL can change the bandwidth or operational mode of the loop filter manually or automatically. Automatic mode is recommended for most users.

In automatic bandwidth control mode (AUTO = 1), the lock detector automatically switches between acquisition and tracking modes. Automatic bandwidth control mode also is used to determine when the VCO clock, CGMVCLK, is safe to use as the source for the base clock, CGMOUT. (See 4.5.2 PLL Bandwidth Control Register.) If PLL interrupts are enabled, the software can wait for a PLL interrupt request and then check the LOCK bit. If interrupts are disabled, software can poll the LOCK bit continuously (for example, during PLL start up) or at periodic intervals. In either case, when the LOCK bit is set, the VCO clock is safe to use as the source for the base clock. (See 4.3.8 Base Clock Selector Circuit.) If the VCO is selected as the source for the base clock and the LOCK bit is clear, the PLL has suffered a severe noise hit and the software must take appropriate action, depending on the application. (See 4.6 Interrupts for information and precautions on using interrupts.)

The following conditions apply when the PLL is in automatic bandwidth control mode:

- The ACQ bit (See 4.5.2 PLL Bandwidth Control Register.) is a read-only indicator of the mode of the filter. (See 4.3.4 Acquisition and Tracking Modes.)

- The ACQ bit is set when the VCO frequency is within a certain tolerance and is cleared when the VCO frequency is out of a certain tolerance. (See 4.8 Acquisition/Lock Time Specifications for more information.)

- The LOCK bit is a read-only indicator of the locked state of the PLL.

- The LOCK bit is set when the VCO frequency is within a certain tolerance and is cleared when the VCO frequency is out of a certain tolerance. (See 4.8 Acquisition/Lock Time Specifications for more information.)

- CPU interrupts can occur if enabled (PLLIE = 1) when the PLL's lock condition changes, toggling the LOCK bit. (See 4.5.1 PLL Control Register.)

The PLL also may operate in manual mode (AUTO = 0). Manual mode is used by systems that do not require an indicator of the lock condition for proper operation. Such systems typically operate well below  $f_{BUSMAX}$ .

| Source<br>Form                                                                                        | Operation                                            | Description                                                                                                                                                                                                                                                                                                                                   |   |    | Effect<br>on CCR |   |   |   | Address<br>Mode                                                                                          | Opcode                                           | Operand                                                                       | sels                                                                                        |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|------------------|---|---|---|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Form                                                                                                  | ·                                                    | •                                                                                                                                                                                                                                                                                                                                             | v | Η  | I                | Ν | z | С | Add<br>Moo                                                                                               | opc                                              | Ope                                                                           | Cycles                                                                                      |

| BHS rel                                                                                               | Branch if Higher or Same<br>(Same as BCC)            | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 0$                                                                                                                                                                                                                                                                                             | - | -  | -                | - | - | - | REL                                                                                                      | 24                                               | rr                                                                            | 3                                                                                           |

| BIH rel                                                                                               | Branch if IRQ Pin High                               | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 1$                                                                                                                                                                                                                                                                                           | - | -  | -                | - | - | - | REL                                                                                                      | 2F                                               | rr                                                                            | 3                                                                                           |

| BIL rel                                                                                               | Branch if IRQ Pin Low                                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? \overline{IRQ} = 0$                                                                                                                                                                                                                                                                                  | - | -  | Ι                | Ι |   | Ι | REL                                                                                                      | 2E                                               | rr                                                                            | 3                                                                                           |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT X<br>BIT opr,SP<br>BIT opr,SP         | Bit Test                                             | (A) & (M)                                                                                                                                                                                                                                                                                                                                     | 0 | _  | _                | ţ | ţ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9EE5<br>9ED5 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff                                     | 2<br>3<br>4<br>3<br>2<br>4<br>5                                                             |

| BLE opr                                                                                               | Branch if Less Than or Equal To<br>(Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 1$                                                                                                                                                                                                                                                                           | - | -  | -                | - | - | - | REL                                                                                                      | 93                                               | rr                                                                            | 3                                                                                           |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                                                                                                                                                                                                                                                                                             | - | -  | -                | - | - | - | REL                                                                                                      | 25                                               | rr                                                                            | 3                                                                                           |

| BLS rel                                                                                               | Branch if Lower or Same                              | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                    | - | -  | -                | - |   | - | REL                                                                                                      | 23                                               | rr                                                                            | 3                                                                                           |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                    | - | -  | -                | - | - | - | REL                                                                                                      | 91                                               | rr                                                                            | 3                                                                                           |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                       | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                                      | 2C                                               | rr                                                                            | 3                                                                                           |

| BMI rel                                                                                               | Branch if Minus                                      | $PC \leftarrow (PC) + 2 + rel? (N) = 1$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                                      | 2B                                               | rr                                                                            | 3                                                                                           |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                         | $PC \leftarrow (PC) + 2 + rel? (I) = 1$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                                      | 2D                                               | rr                                                                            | 3                                                                                           |

| BNE rel                                                                                               | Branch if Not Equal                                  | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                                      | 26                                               | rr                                                                            | 3                                                                                           |

| BPL rel                                                                                               | Branch if Plus                                       | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                                      | 2A                                               | rr                                                                            | 3                                                                                           |

| BRA rel                                                                                               | Branch Always                                        | $PC \leftarrow (PC) + 2 + \mathit{rel}$                                                                                                                                                                                                                                                                                                       | - | -  | Ι                | Ι |   | Ι | REL                                                                                                      | 20                                               | rr                                                                            | 3                                                                                           |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                    | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                         | _ | _  | _                | _ | _ | Ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5555555<br>555555555555555555555555555555                                                   |

| BRN rel                                                                                               | Branch Never                                         | $PC \leftarrow (PC) + 2$                                                                                                                                                                                                                                                                                                                      | - | -  | -                | - | - | - | REL                                                                                                      | 21                                               | rr                                                                            | 3                                                                                           |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                      | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                         | _ | _  | _                | _ | _ | Ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                                | Mn ← 1                                                                                                                                                                                                                                                                                                                                        | _ | _  | _                | _ | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                            | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4                                                        |

| BSR rel                                                                                               | Branch to Subroutine                                 | $\begin{array}{l} PC \leftarrow (PC) + 2;  push \; (PCL) \\ SP \leftarrow (SP) - 1;  push \; (PCH) \\ & SP \leftarrow (SP) - 1 \\ & PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                            | _ | _  | _                | _ | _ | _ | REL                                                                                                      | AD                                               | rr                                                                            | 4                                                                                           |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                          | $\begin{array}{c} PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel ? (A) - (M) = \$00 \end{array}$ | _ | _  | _                | _ | _ | _ | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                                  | 31<br>41<br>51<br>61<br>71<br>9E61               | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                               | 5<br>4<br>4<br>5<br>4<br>6                                                                  |

| CLC                                                                                                   | Clear Carry Bit                                      | C ← 0                                                                                                                                                                                                                                                                                                                                         | - | -  | -                | - | - | 0 | INH                                                                                                      | 98                                               |                                                                               | 1                                                                                           |

| CLI                                                                                                   | Clear Interrupt Mask                                 | l ← 0                                                                                                                                                                                                                                                                                                                                         | - | 1- | 0                | - | - | - | INH                                                                                                      | 9A                                               | 1                                                                             | 2                                                                                           |

| Table 7-1. Instruction Set Summary | (Sheet 2 of 6) |

|------------------------------------|----------------|

|------------------------------------|----------------|

108

MC68HC908GR60A • MC68HC908GR48A • MC68HC908GR32A Data Sheet, Rev. 5

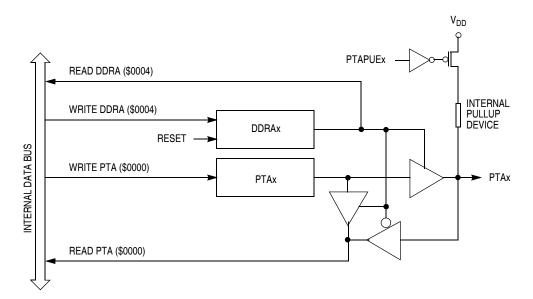

# **Central Processor Unit (CPU)**

|            | Bit Mani             | pulation            | Branch             |                    |                     | Read-Mod            |                     |                    |                    | Cor                |                   |                   |                   |                   | Register          | /Memory           |                   |                   | ]                |

|------------|----------------------|---------------------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR                  | DIR                 | REL                | DIR                | INH                 | INH                 | IX1                 | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                    | 1                   | 2                  | 3                  | 4                   | 5                   | 6                   | 9E6                | 7                  | 8                  | 9                 | Α                 | в                 | С                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | 5<br>BRSET0<br>3 DIR | 4<br>BSET0<br>2 DIR | 3<br>BRA<br>2 REL  | 4<br>NEG<br>2 DIR  | 1<br>NEGA<br>1 INH  | 1<br>NEGX<br>1 INH  |                     | 5<br>NEG<br>3 SP1  |                    | 7<br>RTI<br>1 INH  | 3<br>BGE<br>2 REL | 2<br>SUB<br>2 IMM |                   | 4<br>SUB<br>3 EXT | 4<br>SUB<br>3 IX2 | 5<br>SUB<br>4 SP2 | 3<br>SUB<br>2 IX1 | 4<br>SUB<br>3 SP1 | 2<br>SUB<br>1 IX |

| 1          | 5<br>BRCLR0<br>3 DIR | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL  | 5<br>CBEQ<br>3 DIR | 4<br>CBEQA<br>3 IMM | 3 IMM               | 5<br>CBEQ<br>3 IX1+ | 6<br>CBEQ<br>4 SP1 |                    | 4<br>RTS<br>1 INH  | 3<br>BLT<br>2 REL |                   |                   |                   |                   | 5<br>CMP<br>4 SP2 |                   | 4<br>CMP<br>3 SP1 | 2<br>CMP<br>1 IX |

| 2          | 5<br>BRSET1<br>3 DIR | 4<br>BSET1<br>2 DIR |                    |                    | 5<br>MUL<br>1 INH   | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH   |                    | 2<br>DAA<br>1 INH  |                    | 3<br>BGT<br>2 REL |                   |                   |                   | 4<br>SBC<br>3 IX2 | 5<br>SBC<br>4 SP2 |                   | 4<br>SBC<br>3 SP1 | 2<br>SBC<br>1 IX |

| 3          | 5<br>BRCLR1<br>3 DIR | 4<br>BCLR1<br>2 DIR |                    | 4<br>COM<br>2 DIR  | 1<br>COMA<br>1 INH  | 1<br>COMX<br>1 INH  |                     | 5<br>COM<br>3 SP1  |                    |                    | BLE<br>2 REL      |                   |                   |                   |                   | 5<br>CPX<br>4 SP2 |                   | 4<br>CPX<br>3 SP1 | CPX<br>1 IX      |

| 4          | 5<br>BRSET2<br>3 DIR | 4<br>BSET2<br>2 DIR | 3<br>BCC<br>2 REL  |                    | 1<br>LSRA<br>1 INH  |                     |                     | 5<br>LSR<br>3 SP1  |                    | 2<br>TAP<br>1 INH  |                   | 2<br>AND<br>2 IMM |                   |                   |                   | 5<br>AND<br>4 SP2 |                   | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          | 5<br>BRCLR2<br>3 DIR | 2 DIR               | 3<br>BCS<br>2 REL  | 4<br>STHX<br>2 DIR | 3<br>LDHX<br>3 IMM  | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM  |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH |                   |                   |                   |                   | 5<br>BIT<br>4 SP2 |                   | 4<br>BIT<br>3 SP1 | BIT<br>1 IX      |

| 6          | 5<br>BRSET3<br>3 DIR | 4<br>BSET3<br>2 DIR | 3<br>BNE<br>2 REL  |                    | 1<br>RORA<br>1 INH  |                     |                     | 80R<br>3 SP1       |                    | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM |                   |                   |                   | 5<br>LDA<br>4 SP2 |                   | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          | 5<br>BRCLR3<br>3 DIR | 4<br>BCLR3<br>2 DIR |                    | 4<br>ASR<br>2 DIR  | 1<br>ASRA<br>1 INH  | 1<br>ASRX<br>1 INH  |                     | 5<br>ASR<br>3 SP1  |                    | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH |                   |                   |                   |                   | 5<br>STA<br>4 SP2 |                   | 4<br>STA<br>3 SP1 | STA<br>1 IX      |

| 8          | 5<br>BRSET4<br>3 DIR | 4<br>BSET4<br>2 DIR | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH  | 1<br>LSLX<br>1 INH  | 4<br>LSL<br>2 IX1   | 5<br>LSL<br>3 SP1  |                    | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | 2<br>EOR<br>2 IMM |                   | 4<br>EOR<br>3 EXT | 4<br>EOR<br>3 IX2 | 5<br>EOR<br>4 SP2 |                   | 4<br>EOR<br>3 SP1 | 2<br>EOR<br>1 IX |

| 9          | 5<br>BRCLR4<br>3 DIR | 4<br>BCLR4<br>2 DIR | 3<br>BHCS<br>2 REL | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH  | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1   | 5<br>ROL<br>3 SP1  |                    | 2<br>PSHX<br>1 INH | 1<br>SEC<br>1 INH |                   |                   | ADC<br>3 EXT      | 4<br>ADC<br>3 IX2 | ADC<br>4 SP2      |                   | 4<br>ADC<br>3 SP1 | 2<br>ADC<br>1 IX |

| Α          | 5<br>BRSET5<br>3 DIR |                     |                    | 4<br>DEC<br>2 DIR  | 1<br>DECA<br>1 INH  |                     |                     | 5<br>DEC<br>3 SP1  |                    | 2<br>PULH<br>1 INH | 2<br>CLI<br>1 INH |                   |                   |                   | 4<br>ORA<br>3 IX2 | 5<br>ORA<br>4 SP2 |                   | 4<br>ORA<br>3 SP1 | 2<br>ORA<br>1 IX |

| в          | 5<br>BRCLR5<br>3 DIR | 4<br>BCLR5<br>2 DIR |                    |                    | 3<br>DBNZA<br>2 INH | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1  | 6<br>DBNZ<br>4 SP1 |                    | 2<br>PSHH<br>1 INH | 2<br>SEI<br>1 INH | 2<br>ADD<br>2 IMM |                   |                   | 4<br>ADD<br>3 IX2 | 5<br>ADD<br>4 SP2 |                   | 4<br>ADD<br>3 SP1 | 2<br>ADD<br>1 IX |

| с          | 5<br>BRSET6<br>3 DIR | 4<br>BSET6<br>2 DIR |                    | 4<br>INC<br>2 DIR  | 1<br>INCA<br>1 INH  |                     |                     | 5<br>INC<br>3 SP1  |                    | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR | -                 |                   |                   | 3<br>JMP<br>2 IX1 |                   | 2<br>JMP<br>1 IX |

| D          | 5<br>BRCLR6<br>3 DIR | 4<br>BCLR6<br>2 DIR |                    | 3<br>TST<br>2 DIR  | 1<br>TSTA<br>1 INH  |                     |                     | 4<br>TST<br>3 SP1  |                    |                    | 1<br>NOP<br>1 INH |                   |                   |                   |                   |                   | 5<br>JSR<br>2 IX1 |                   | 4<br>JSR<br>1 IX |

| Е          | 5<br>BRSET7<br>3 DIR | 4<br>BSET7<br>2 DIR | 3<br>BIL<br>2 REL  |                    |                     | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD   |                    | 4<br>MOV<br>2 IX+D | 1<br>STOP<br>1 INH | *                 | 2<br>LDX<br>2 IMM |                   |                   |                   |                   | 3<br>LDX<br>2 IX1 | 4<br>LDX<br>3 SP1 | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7<br>3 DIR | 4<br>BCLR7<br>2 DIR | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH  | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1   | 4<br>CLR<br>3 SP1  | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | 3<br>STX<br>2 DIR | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | 5<br>STX<br>4 SP2 | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | STX<br>1 IX      |

INH Inherent IMM Immediate REL Relative IX Indexed, No Offset DIR Direct EXT Extended IX1 IX2

- Indexed, 8-Bit Offset Indexed, 16-Bit Offset

- DD Direct-Direct IX+D Indexed-Direct IX+D Indexed-Direct

SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with

- Post Increment

- IX1+ Indexed, 1-Byte Offset with Post Increment

0 High Byte of Opcode in Hexadecimal

MSB

LSB

0

5 Cycles BRSET0 Opcode Mnemonic 3 DIR Number of Bytes / Addressing Mode

- \*Pre-byte for stack pointer indexed instructions

- Freescale Semiconductor

# 8.4 IRQ Pin

A falling edge on the IRQ pin can latch an interrupt request into the IRQ latch. A vector fetch, software clear, or reset clears the IRQ latch.

If the MODE bit is set, the IRQ pin is both falling-edge-sensitive and low-level-sensitive. With MODE set, both of the following actions must occur to clear IRQ:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the latch. Software may generate the interrupt acknowledge signal by writing a 1 to the ACK bit in the interrupt status and control register (INTSCR). The ACK bit is useful in applications that poll the IRQ pin and require software to clear the IRQ latch. Writing to the ACK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the IRQ pin. A falling edge that occurs after writing to the ACK bit latches another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the vector address at locations \$FFFA and \$FFFB.

- Return of the  $\overline{IRQ}$  pin to a high level As long as the  $\overline{IRQ}$  pin is low, IRQ remains active.

The vector fetch or software clear and the return of the  $\overline{IRQ}$  pin to a high level may occur in any order. The interrupt request remains pending as long as the  $\overline{IRQ}$  pin is low. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

If the MODE bit is clear, the IRQ pin is falling-edge-sensitive only. With MODE clear, a vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in the INTSCR register can be used to check for pending interrupts. The IRQF bit is not affected by the IMASK bit, which makes it useful in applications where polling is preferred.

Use the BIH or BIL instruction to read the logic level on the  $\overline{IRQ}$  pin.

NOTE

When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

# 8.5 IRQ Module During Break Interrupts

The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear the latch during the break state. See Chapter 19 Development Support.

To allow software to clear the IRQ latch during a break interrupt, write a 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect CPU interrupt flags during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ interrupt flags.

# Chapter 9 Keyboard Interrupt Module (KBI)

# 9.1 Introduction

The keyboard interrupt module (KBI) provides eight independently maskable external interrupts which are accessible via PTA0–PTA7. When a port pin is enabled for keyboard interrupt function, an internal pullup/pulldown device is also enabled on the pin.

# 9.2 Features

Features include:

- Eight keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Hysteresis buffers

- Programmable edge-only or edge- and level- interrupt sensitivity

- Edge detect programmable for rising or falling edges

- Level detect programmable for high or low levels

- Exit from low-power modes

- Pullup/pulldown device automatically configured based on polarity of edge/level selection

# 9.3 Functional Description

Writing to the KBIE7–KBIE0 bits in the keyboard interrupt enable register independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin also enables its internal pullup/pulldown device. On falling edge or low level selection a pullup device is configured. On rising edge or high level selection a pulldown device is configured.

- A falling edge is detected when an enabled keyboard input signal is seen as a 1 (the deasserted level) during one bus cycle and then a 0 (the asserted level) during the next cycle.

- A rising edge is detected when the input signal is seen as a 0 during one bus cycle and then a 1 during the next cycle.

A keyboard interrupt is latched when one or more keyboard pins are asserted. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

#### Keyboard Interrupt Module (KBI)

1. Pin contains integrated pullup device.

2. Ports are software configurable with pullup device if input port or pullup/pulldown device for keyboard input.

3. Higher current drive port pins

#### Figure 9-1. Block Diagram Highlighting KBI Block and Pins

Input/Output (I/O) Ports

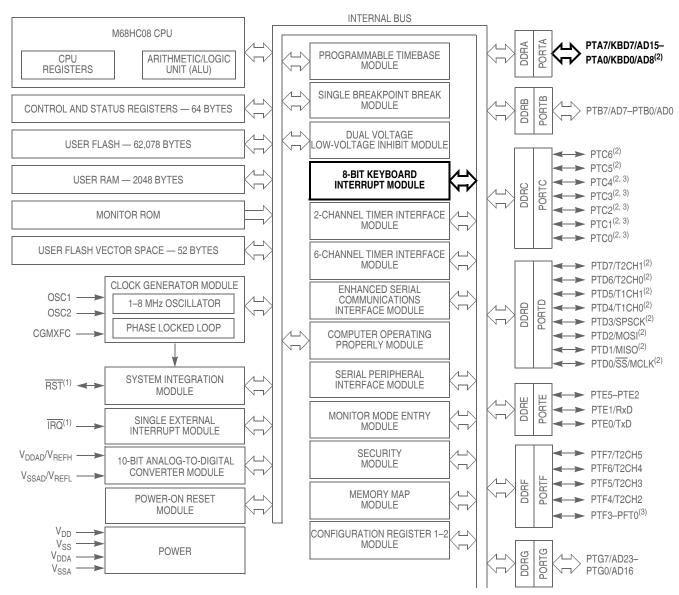

# 12.3.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

Figure 12-3. Data Direction Register A (DDRA)

#### DDRA7–DDRA0 — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA7–DDRA0, configuring all port A pins as inputs.

1 = Corresponding port A pin configured as output

0 = Corresponding port A pin configured as input

#### NOTE

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

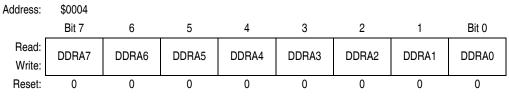

Figure 12-4 shows the port A I/O logic.

When bit DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When bit DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-2 summarizes the operation of the port A pins.

Figure 12-4. Port A I/O Circuit

#### Input/Output (I/O) Ports

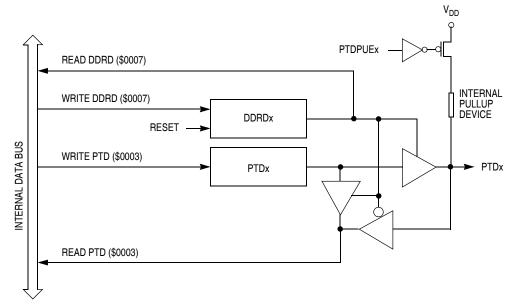

When bit DDRDx is a 1, reading address \$0003 reads the PTDx data latch. When bit DDRDx is a 0, reading address \$0003 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-5 summarizes the operation of the port D pins.

#### Figure 12-15. Port D I/O Circuit

#### Table 12-5. Port D Pin Functions

| PTDPUE | DDRD | PTD              | I/O Pin                               | Accesses to DDRD | Access    | es to PTD                |

|--------|------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    | Bit  | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0    | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRD7-DDRD0      | Pin       | PTD7–PTD0 <sup>(3)</sup> |

| 0      | 0    | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRD7-DDRD0      | Pin       | PTD7–PTD0 <sup>(3)</sup> |

| Х      | 1    | Х                | Output                                | DDRD7-DDRD0      | PTD7–PTD0 | PTD7–PTD0                |

1. X = Don't care

I/O pin pulled up to V<sub>DD</sub> by internal pullup device.

Writing affects data register, but does not affect input.

4. Hi-Z = High imp[edance

#### Enhanced Serial Communications Interface (ESCI) Module

#### 13.4.2.4 Idle Characters

For TXINV = 0 (output not inverted), a transmitted idle character contains all 1s and has no start, stop, or parity bit. Idle character length depends on the M bit in SCC1. The preamble is a synchronizing idle character that begins every transmission.

If the TE bit is cleared during a transmission, the TxD pin becomes idle after completion of the transmission in progress. Clearing and then setting the TE bit during a transmission queues an idle character to be sent after the character currently being transmitted.

#### NOTE

When a break sequence is followed immediately by an idle character, this SCI design exhibits a condition in which the break character length is reduced by one half bit time. In this instance, the break sequence will consist of a valid start bit, eight or nine data bits (as defined by the M bit in SCC1) of 0 and one half data bit length of 0 in the stop bit position followed immediately by the idle character. To ensure a break character of the proper length is transmitted, always queue up a byte of data to be transmitted while the final break sequence is in progress.

When queueing an idle character, return the TE bit to 1 before the stop bit of the current character shifts out to the TxD pin. Setting TE after the stop bit appears on TxD causes data previously written to the SCDR to be lost. A good time to toggle the TE bit for a queued idle character is when the SCTE bit becomes set and just before writing the next byte to the SCDR.

#### 13.4.2.5 Inversion of Transmitted Output

The transmit inversion bit (TXINV) in ESCI control register 1 (SCC1) reverses the polarity of transmitted data. All transmitted values including idle, break, start, and stop bits, are inverted when TXINV is at 1. See 13.8.1 ESCI Control Register 1.

#### 13.4.2.6 Transmitter Interrupts

These conditions can generate CPU interrupt requests from the ESCI transmitter:

- ESCI transmitter empty (SCTE) The SCTE bit in SCS1 indicates that the SCDR has transferred a character to the transmit shift register. SCTE can generate a transmitter CPU interrupt request. Setting the ESCI transmit interrupt enable bit, SCTIE, in SCC2 enables the SCTE bit to generate transmitter CPU interrupt requests.

- Transmission complete (TC) The TC bit in SCS1 indicates that the transmit shift register and the SCDR are empty and that no break or idle character has been generated. The transmission complete interrupt enable bit, TCIE, in SCC2 enables the TC bit to generate transmitter CPU interrupt requests.

#### 13.4.3 Receiver

Figure 13-6 shows the structure of the ESCI receiver. The receiver I/O registers are summarized in Figure 13-4.

System Integration Module (SIM)

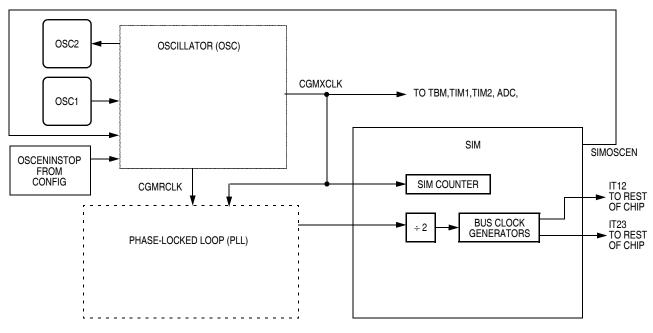

# 14.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 14-3. This clock originates from either an external oscillator or from the on-chip PLL.

# 14.2.1 Bus Timing

In user mode, the internal bus frequency is either the crystal oscillator output (CGMXCLK) divided by four or the PLL output (CGMVCLK) divided by four.

# 14.2.2 Clock Startup from POR or LVI Reset

When the power-on reset module or the low-voltage inhibit module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 CGMXCLK cycle POR timeout has completed. The RST pin is driven low by the SIM during this entire period. The bus clocks start upon completion of the timeout.

## 14.2.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows CGMXCLK to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay timeout. This timeout is selectable as 4096 or 32 CGMXCLK cycles. See 14.6.2 Stop Mode.

#### Figure 14-3. System Clock Signals

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

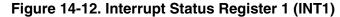

#### Interrupt Status Register 1

| Address: | \$FE04 |            |     |     |     |     |   |       |

|----------|--------|------------|-----|-----|-----|-----|---|-------|

|          | Bit 7  | 6          | 5   | 4   | 3   | 2   | 1 | Bit 0 |

| Read:    | IF6    | IF5        | IF4 | IF3 | IF2 | IF1 | 0 | 0     |

| Write:   | R      | R          | R   | R   | R   | R   | R | R     |

| Reset:   | 0      | 0          | 0   | 0   | 0   | 0   | 0 | 0     |

|          | R      | = Reserved |     |     |     |     |   |       |

#### IF6–IF1 — Interrupt Flags 1–6

These flags indicate the presence of interrupt requests from the sources shown in Table 14-3.

1 = Interrupt request present

0 = No interrupt request present

#### Bit 0 and Bit 1 — Always read 0

#### Interrupt Status Register 2

#### Figure 14-13. Interrupt Status Register 2 (INT2)

#### IF14–IF7 — Interrupt Flags 14–7

These flags indicate the presence of interrupt requests from the sources shown in Table 14-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Interrupt Status Register 3

| Address: | \$FE06 |            |      |      |      |      |      |       |

|----------|--------|------------|------|------|------|------|------|-------|

|          | Bit 7  | 6          | 5    | 4    | 3    | 2    | 1    | Bit 0 |

| Read:    | IF22   | IF21       | IF20 | IF19 | IF18 | IF17 | IF16 | IF15  |

| Write:   | R      | R          | R    | R    | R    | R    | R    | R     |

| Reset:   | 0      | 0          | 0    | 0    | 0    | 0    | 0    | 0     |

|          | R      | = Reserved |      |      |      |      |      |       |

#### Figure 14-14. Interrupt Status Register 3 (INT3)

#### IF22–IF15 — Interrupt Flags 22–15

These flags indicate the presence of an interrupt request from the source shown in Table 14-3.

1 = Interrupt request present

0 = No interrupt request present

#### Serial Peripheral Interface (SPI) Module

#### 15.3.1 Master Mode

The SPI operates in master mode when the SPI master bit, SPMSTR, is set.

NOTE

In a multi-SPI system, configure the SPI modules as master or slave before enabling them. Enable the master SPI before enabling the slave SPI. Disable the slave SPI before disabling the master SPI. See 15.12.1 SPI Control Register.

Only a master SPI module can initiate transmissions. Software begins the transmission from a master SPI module by writing to the transmit data register. If the shift register is empty, the byte immediately transfers to the shift register, setting the SPI transmitter empty bit, SPTE. The byte begins shifting out on the MOSI pin under the control of the serial clock. See Figure 15-4.

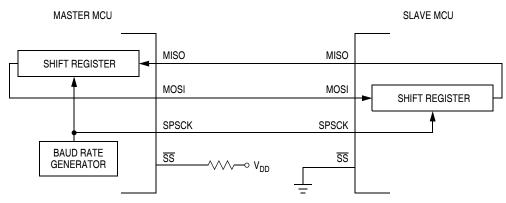

Figure 15-4. Full-Duplex Master-Slave Connections

The SPR1 and SPR0 bits control the baud rate generator and determine the speed of the shift register. (See 15.12.2 SPI Status and Control Register.) Through the SPSCK pin, the baud rate generator of the master also controls the shift register of the slave peripheral.

As the byte shifts out on the MOSI pin of the master, another byte shifts in from the slave on the master's MISO pin. The transmission ends when the receiver full bit, SPRF, becomes set. At the same time that SPRF becomes set, the byte from the slave transfers to the receive data register. In normal operation, SPRF signals the end of a transmission. Software clears SPRF by reading the SPI status and control register with SPRF set and then reading the SPI data register. Writing to the SPI data register (SPDR) clears SPTE.

#### 15.3.2 Slave Mode

The SPI operates in slave mode when SPMSTR is clear. In slave mode, the SPSCK pin is the input for the serial clock from the master MCU. Before a data transmission occurs, the  $\overline{SS}$  pin of the slave SPI must be low.  $\overline{SS}$  must remain low until the transmission is complete. See 15.6.2 Mode Fault Error.

In a slave SPI module, data enters the shift register under the control of the serial clock from the master SPI module. After a byte enters the shift register of a slave SPI, it transfers to the receive data register, and the SPRF bit is set. To prevent an overflow condition, slave software then must read the receive data register before another full byte enters the shift register.

The maximum frequency of the SPSCK for an SPI configured as a slave is the bus clock speed (which is twice as fast as the fastest master SPSCK clock that can be generated). The frequency of the SPSCK for

# 15.5 Queuing Transmission Data

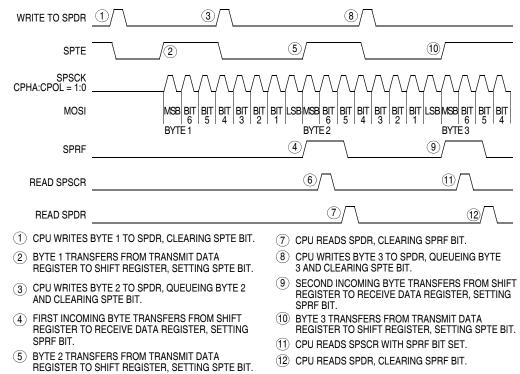

The double-buffered transmit data register allows a data byte to be queued and transmitted. For an SPI configured as a master, a queued data byte is transmitted immediately after the previous transmission has completed. The SPI transmitter empty flag (SPTE) indicates when the transmit data buffer is ready to accept new data. Write to the transmit data register only when SPTE is high. Figure 15-9 shows the timing associated with doing back-to-back transmissions with the SPI (SPSCK has CPHA: CPOL = 1:0).

- (6) CPU READS SPSCR WITH SPRF BIT SET.

- Figure 15-9. SPRF/SPTE CPU Interrupt Timing

The transmit data buffer allows back-to-back transmissions without the slave precisely timing its writes between transmissions as in a system with a single data buffer. Also, if no new data is written to the data buffer, the last value contained in the shift register is the next data word to be transmitted.

For an idle master or idle slave that has no data loaded into its transmit buffer, the SPTE is set again no more than two bus cycles after the transmit buffer empties into the shift register. This allows the user to queue up a 16-bit value to send. For an already active slave, the load of the shift register cannot occur until the transmission is completed. This implies that a back-to-back write to the transmit data register is not possible. SPTE indicates when the next write can occur.

```

Interrupts

```

In a slave SPI (MSTR = 0), MODF generates an SPI receiver/error CPU interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by clearing the SPE bit of the slave.

NOTE

A high on the SS pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

# 15.7 Interrupts

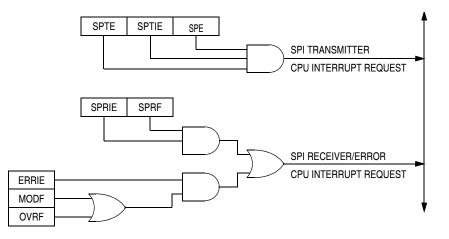

Four SPI status flags can be enabled to generate CPU interrupt requests. See Table 15-1.

| Flag              | Request                               |

|-------------------|---------------------------------------|

| SPTE              | SPI transmitter CPU interrupt request |

| Transmitter empty | (SPTIE = 1, SPE = 1)                  |

| SPRF              | SPI receiver CPU interrupt request    |

| Receiver full     | (SPRIE = 1)                           |

| OVRF              | SPI receiver/error interrupt request  |

| Overflow          | (ERRIE = 1)                           |

| MODF              | SPI receiver/error interrupt request  |

| Mode fault        | (ERRIE = 1)                           |

Table 15-1. SPI Interrupts

Reading the SPI status and control register with SPRF set and then reading the receive data register clears SPRF. The clearing mechanism for the SPTE flag is always just a write to the transmit data register.

The SPI transmitter interrupt enable bit (SPTIE) enables the SPTE flag to generate transmitter CPU interrupt requests, provided that the SPI is enabled (SPE = 1).

The SPI receiver interrupt enable bit (SPRIE) enables SPRF to generate receiver CPU interrupt requests, regardless of the state of SPE. See Figure 15-12.

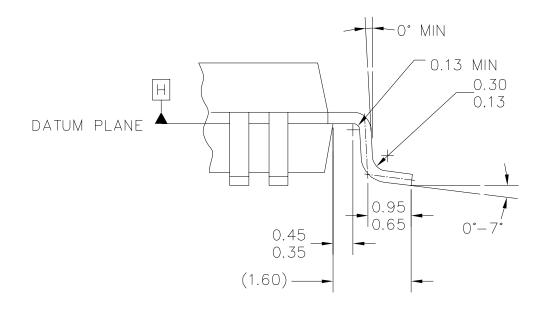

# Chapter 21 Ordering Information and Mechanical Specifications

# 21.1 Introduction

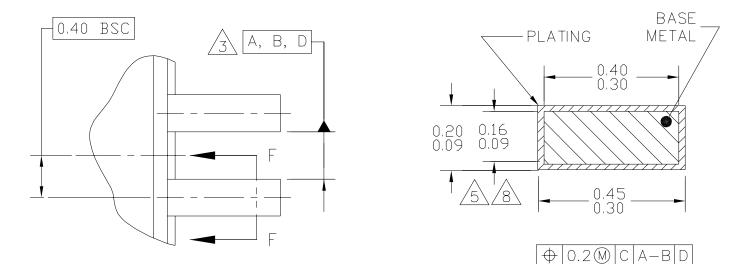

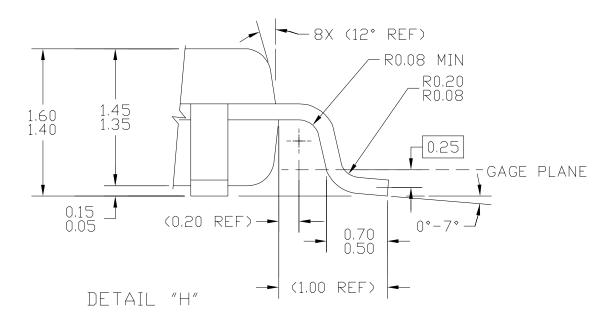

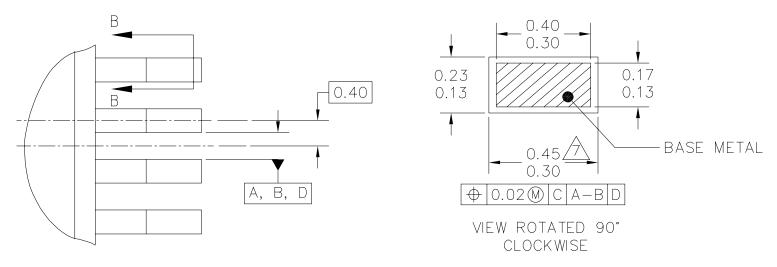

This section contains ordering numbers for the MC68HC908GR60A and gives the dimensions for:

- 32-pin low-profile quad flat pack (case 873A)

- 48-pin low-profile quad flat pack (case 932-03)

- 64-pin quad flat pack (case 840B)

The following figures show the latest package drawings at the time of this publication. To make sure that you have the latest package specifications, contact your local Freescale Semiconductor Sales Office.

# 21.2 MC Order Numbers

| MC Order Number | Operating<br>Temperature Range | Package            |

|-----------------|--------------------------------|--------------------|

| MC908GR60ACFJ   | -40°C to +85°C                 | 32-pin low-profile |

| MC908GR60AVFJ   | -40°C to +105°C                | quad flat package  |

| MC908GR60AMFJ   | -40°C to +125°C                | (LQFP)             |

| MC908GR60ACFA   | -40°C to +85°C                 | 48-pin low-profile |

| MC908GR60AVFA   | -40°C to +105°C                | quad flat package  |

| MC908GR60AMFA   | -40°C to +125°C                | (LQFP)             |

| MC908GR60ACFU   | -40°C to +85°C                 | 64-pin quad flat   |

| MC908GR60AVFU   | -40°C to +105°C                | package            |

| MC908GR60AMFU   | -40°C to +125°C                | (QFP)              |

Table 21-1. MC Order Numbers

Temperature designators:  $C = -40^{\circ}C$  to  $+85^{\circ}C$  $V = -40^{\circ}C$  to  $+105^{\circ}C$

$M = -40^{\circ}C$  to  $+125^{\circ}C$

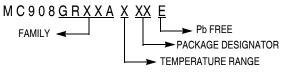

Figure 21-1. Device Numbering System

# 21.3 Package Dimensions

Refer to the following pages for detailed package dimensions.

DETAIL G

SECTION F-F ROTATED 90°CW 32 PLACES

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA                             | L OUTLINE                       | PRINT VERSION NE | IT TO SCALE |  |  |

|---------------------------------------------------------|---------------------------------------|---------------------------------|------------------|-------------|--|--|

| TITLE:                                                  | <i>,</i> , ,                          | DOCUMENT NO: 98ASH70029A REV: C |                  |             |  |  |

| LOW PROFILE QUAD FLAT P<br>32 LEAD, 0.8 PITCH (7 X      | · · · · · · · · · · · · · · · · · · · | CASE NUMBER: 873A-04 01 APR 200 |                  |             |  |  |

| $\begin{bmatrix} 32 \\ 1 \end{bmatrix}$                 | × / / ۱.+)                            | STANDARD: JE                    | IDEC MS-026 BBA  |             |  |  |

NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

$\overline{3}$  datums a, b, and d to be determined at datum plane H.

$\overline{/4.}$  dimensions to be determined at seating plane datum c.

5. DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THZ LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

<u>6</u> DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

/7.\ EXACT SHAPE OF EACH CORNER IS OPTIONAL.

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | L OUTLINE | PRINT VERSION NE                | IT TO SCALE    |  |  |  |  |

|---------------------------------------------------------|-----------|---------------------------------|----------------|--|--|--|--|

| TITLE:                                                  |           | DDCUMENT ND: 98ASH70029A REV: C |                |  |  |  |  |

| LOW PROFILE QUAD FLAT P,                                |           | CASE NUMBER: 873A-04 01 APR 20  |                |  |  |  |  |

| 32 LEAD, 0.8 PITCH (7 X                                 | (7 X 1.4) | STANDARD: JE                    | DEC MS-026 BBA |  |  |  |  |

DETAIL "A"

SECTION B-B

DETAIL "C"

| © FREESCALE SEMICONDUCTOR, INC. MECHANICAL ALL RIGHTS RESERVED. |  | L OUTLINE                | PRINT VERSION NOT TO SCALE |             |

|-----------------------------------------------------------------|--|--------------------------|----------------------------|-------------|

|                                                                 |  | DOCUMENT NO: 98ASB42844B |                            | RE∨: A      |

|                                                                 |  | CASE NUMBER              | 8:840B-02                  | 06 APR 2005 |

|                                                                 |  | STANDARD: NE             | IN-JEDEC                   |             |