#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Obsolete                                                    |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e300c2                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 333MHz                                                      |

| Co-Processors/DSP               | Communications; QUICC Engine, Security; SEC 2.2             |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100Mbps (3)                                              |

| SATA                            | -                                                           |

| USB                             | USB 2.0 (1)                                                 |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | Cryptography                                                |

| Package / Case                  | 516-BBGA                                                    |

| Supplier Device Package         | 516-PBGA (27x27)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8321evrafdc |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.1.2 Serial Interfaces

The MPC8323E serial interfaces are as follows:

- Support for one UL2 interface with 31 multi-PHY addresses (MPC8323E and MPC8323 only)

- Support for up to three 10/100 Mbps Ethernet interfaces using MII or RMII

- Support for up to four T1/E1/J1/E3 or DS-3 serial interfaces (TDM)

- Support for dual UART and SPI interfaces and a single I<sup>2</sup>C interface

# 1.2 QUICC Engine Block

The QUICC Engine block is a versatile communications complex that integrates several communications peripheral controllers. It provides on-chip system design for a variety of applications, particularly in communications and networking systems. The QUICC Engine block has the following features:

- One 32-bit RISC controller for flexible support of the communications peripherals

- Serial DMA channel for receive and transmit on all serial channels

- Five universal communication controllers (UCCs) supporting the following protocols and interfaces (not all of them simultaneously):

- 10/100 Mbps Ethernet/IEEE 802.3® standard

- IP support for IPv4 and IPv6 packets including TOS, TTL, and header checksum processing

- ATM protocol through UTOPIA interface (note that the MPC8321 and MPC8321E do not support the UTOPIA interface)

- HDLC /transparent up to 70-Mbps full-duplex

- HDLC bus up to 10 Mbps

- Asynchronous HDLC

- UART

- BISYNC up to 2 Mbps

- QUICC multi-channel controller (QMC) for 64 TDM channels

- One UTOPIA interface (UPC1) supporting 31 multi-PHYs (MPC8323E- and MPC8323-specific)

- Two serial peripheral interfaces (SPI). SPI2 is dedicated to Ethernet PHY management.

- Four TDM interfaces

- Thirteen independent baud rate generators and 19 input clock pins for supplying clocks to UCC serial channels

- Four independent 16-bit timers that can be interconnected as two 32-bit timers

The UCCs are similar to the PowerQUICC II peripherals: SCC (BISYNC, UART, and HDLC bus) and FCC (fast Ethernet, HDLC, transparent, and ATM).

### **1.3 Security Engine**

The security engine is optimized to handle all the algorithms associated with IPSec, IEEE 802.11i<sup>TM</sup> standard, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are:

- Data encryption standard execution unit (DEU), supporting DES and 3DES

- Advanced encryption standard unit (AESU), supporting AES

- Message digest execution unit (MDEU), supporting MD5, SHA1, SHA-256, and HMAC with any algorithm

- One crypto-channel supporting multi-command descriptor chains

# 1.4 DDR Memory Controller

The MPC8323E DDR1/DDR2 memory controller includes the following features:

- Single 32-bit interface supporting both DDR1 and DDR2 SDRAM

- Support for up to 266-MHz data rate

- Support for two ×16 devices

- Support for up to 16 simultaneous open pages

- Supports auto refresh

- On-the-fly power management using CKE

- 1.8-/2.5-V SSTL2 compatible I/O

- Support for 1 chip select only

- FCRAM, ECC, hardware/software calibration, bit deskew, QIN stage, or atomic logic are not supported.

# 1.5 PCI Controller

The MPC8323E PCI controller includes the following features:

- PCI Specification Revision 2.3 compatible

- Single 32-bit data PCI interface operates up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- Support for host and agent modes

- On-chip arbitration, supporting three external masters on PCI

- Selectable hardware-enforced coherency

# **1.6 Programmable Interrupt Controller (PIC)**

The programmable interrupt controller (PIC) implements the necessary functions to provide a flexible solution for general-purpose interrupt control. The PIC programming model is compatible with the MPC8260 interrupt controller, and it supports 8 external and 35 internal discrete interrupt sources. Interrupts can also be redirected to an external interrupt controller.

| CLKIN input current       | $0 V \le V_{IN} \le OV_{DD}$                                                                                     | I <sub>IN</sub> | — | ±5  | μA |

|---------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|---|-----|----|

| PCI_SYNC_IN input current | $\begin{array}{c} 0 \ V \leq V_{IN} \leq 0.5 \ V \ or \\ OV_{DD} - 0.5 \ V \leq V_{IN} \leq OV_{DD} \end{array}$ | I <sub>IN</sub> | _ | ±5  | μA |

| PCI_SYNC_IN input current | $0.5~V \leq V_{IN} \leq OV_{DD} - 0.5~V$                                                                         | I <sub>IN</sub> | — | ±50 | μA |

| Table 7. | CLKIN DC | Electrical | Characteristics | (continued) |

|----------|----------|------------|-----------------|-------------|

|----------|----------|------------|-----------------|-------------|

### 4.2 AC Electrical Characteristics

The primary clock source for the MPC8323E can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. Table 8 provides the clock input (CLKIN/PCI\_CLK) AC timing specifications for the MPC8323E.

| Parameter/Condition        | Symbol                               | Min | Typical | Max   | Unit | Notes |

|----------------------------|--------------------------------------|-----|---------|-------|------|-------|

| CLKIN/PCI_CLK frequency    | f <sub>CLKIN</sub>                   | 25  | —       | 66.67 | MHz  | 1     |

| CLKIN/PCI_CLK cycle time   | t <sub>CLKIN</sub>                   | 15  | _       | _     | ns   | —     |

| CLKIN rise and fall time   | t <sub>KH</sub> , t <sub>KL</sub>    | 0.6 | 0.8     | 4     | ns   | 2     |

| PCI_CLK rise and fall time | t <sub>PCH</sub> , t <sub>PCL</sub>  | 0.6 | 0.8     | 1.2   | ns   | 2     |

| CLKIN/PCI_CLK duty cycle   | t <sub>KHK</sub> /t <sub>CLKIN</sub> | 40  | —       | 60    | %    | 3     |

| CLKIN/PCI_CLK jitter       | —                                    | _   | —       | ±150  | ps   | 4, 5  |

**Table 8. CLKIN AC Timing Specifications**

Notes:

1. **Caution:** The system, core, security, and QUICC Engine block must not exceed their respective maximum or minimum operating frequencies.

2. Rise and fall times for CLKIN/PCI\_CLK are measured at 0.4 and 2.7 V.

3. Timing is guaranteed by design and characterization.

4. This represents the total input jitter—short term and long term—and is guaranteed by design.

5. The CLKIN/PCI\_CLK driver's closed loop jitter bandwidth should be < 500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track CLKIN drivers with the specified jitter.

# 5 **RESET Initialization**

This section describes the AC electrical specifications for the reset initialization timing requirements of the MPC8323E. Table 9 provides the reset initialization AC timing specifications for the reset component(s).

| Table 9. RESET | <b>Initialization</b> | Timing | <b>Specifications</b> |

|----------------|-----------------------|--------|-----------------------|

|----------------|-----------------------|--------|-----------------------|

| Parameter/Condition                                                                                                | Min | Мах | Unit                     | Notes |

|--------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|-------|

| Required assertion time of $\overline{\text{HRESET}}$ or $\overline{\text{SRESET}}$ (input) to activate reset flow | 32  | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Required assertion time of PORESET with stable clock applied to CLKIN when the MPC8323E is in PCI host mode        | 32  | —   | <sup>t</sup> CLKIN       | 2     |

| Required assertion time of PORESET with stable clock applied to PCI_SYNC_IN when the MPC8323E is in PCI agent mode | 32  | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

### 6.2 DDR1 and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR1 and DDR2 SDRAM interface.

### 6.2.1 DDR1 and DDR2 SDRAM Input AC Timing Specifications

Table 16 provides the input AC timing specifications for the DDR2 SDRAM ( $Dn_GV_{DD}(typ) = 1.8 \text{ V}$ ).

#### Table 16. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions with  $Dn_GV_{DD}$  of 1.8 ± 5%.

| Parameter             | Symbol          | Min                                  | Мах                          | Unit | Notes |

|-----------------------|-----------------|--------------------------------------|------------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | —                                    | MVREFn <sub>REF</sub> – 0.25 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MVREF <i>n</i> <sub>REF</sub> + 0.25 | _                            | V    | —     |

Table 17 provides the input AC timing specifications for the DDR1 SDRAM ( $Dn_GV_{DD}(typ) = 2.5 V$ ).

Table 17. DDR1 SDRAM Input AC Timing Specifications for 2.5 V Interface

At recommended operating conditions with  $Dn_GV_{DD}$  of 2.5 ± 5%.

| Parameter             | Symbol          | Min                                  | Мах                          | Unit | Notes |

|-----------------------|-----------------|--------------------------------------|------------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | —                                    | MVREFn <sub>REF</sub> – 0.31 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MVREF <i>n</i> <sub>REF</sub> + 0.31 | _                            | V    | —     |

Table 18 provides the input AC timing specifications for the DDR1 and DDR2 SDRAM interface.

#### Table 18. DDR1 and DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions with  $Dn_GV_{DD}$  of (1.8 or 2.5 V) ± 5%.

| Parameter                        | Symbol              | Min   | Мах  | Unit | Notes |

|----------------------------------|---------------------|-------|------|------|-------|

| Controller skew for MDQS—MDQ/MDM | t <sub>CISKEW</sub> |       |      | ps   | 1, 2  |

| 266 MHz                          |                     | -750  | 750  |      |       |

| 200 MHz                          |                     | -1250 | 1250 |      |       |

#### Notes:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ±(T/4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

#### DDR1 and DDR2 SDRAM

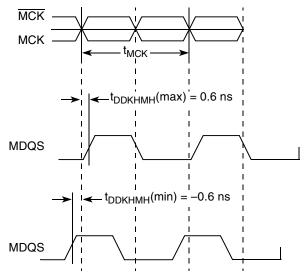

Figure 5 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 5. Timing Diagram for t<sub>DDKHMH</sub>

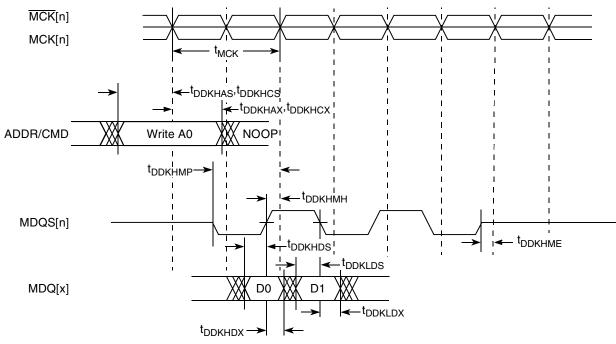

Figure 6 shows the DDR1 and DDR2 SDRAM output timing diagram.

Figure 6. DDR1 and DDR2 SDRAM Output Timing Diagram

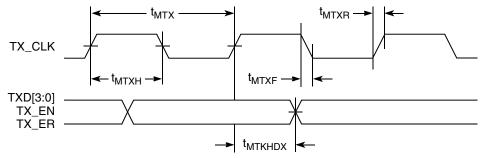

#### Table 23. MII Transmit AC Timing Specifications (continued)

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V  $\pm$  10%.

| Parameter/Condition         | Symbol <sup>1</sup> | Min | Typical | Мах | Unit |

|-----------------------------|---------------------|-----|---------|-----|------|

| TX_CLK data clock fall time | t <sub>MTXF</sub>   | 1.0 |         | 4.0 | ns   |

#### Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

#### Figure 7 shows the MII transmit AC timing diagram.

Figure 7. MII Transmit AC Timing Diagram

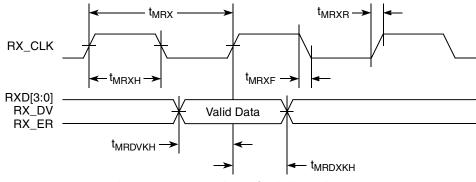

### 8.2.1.2 MII Receive AC Timing Specifications

Table 24 provides the MII receive AC timing specifications.

#### Table 24. MII Receive AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Typical | Мах | Unit |

|---------------------------------------------|-------------------------------------|------|---------|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub>                    | —    | 400     | —   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | _    | 40      | _   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _       | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _       | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _       | _   | ns   |

| RX_CLK clock rise time                      | t <sub>MRXR</sub>                   | 1.0  |         | 4.0 | ns   |

#### **Ethernet and MII Management**

#### Table 24. MII Receive AC Timing Specifications (continued)

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V  $\pm$  10%.

| Parameter/Condition    | Symbol <sup>1</sup> | Min | Typical | Мах | Unit |

|------------------------|---------------------|-----|---------|-----|------|

| RX_CLK clock fall time | t <sub>MRXF</sub>   | 1.0 | _       | 4.0 | ns   |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

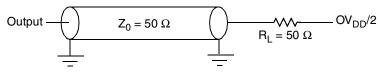

Figure 8 provides the AC test load.

Figure 8. AC Test Load

Figure 9 shows the MII receive AC timing diagram.

Figure 9. MII Receive AC Timing Diagram

### 8.2.2 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

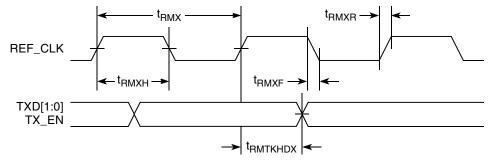

### 8.2.2.1 RMII Transmit AC Timing Specifications

Table 23 provides the RMII transmit AC timing specifications.

#### Table 25. RMII Transmit AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Typical | Мах | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| REF_CLK clock                                                          | t <sub>RMX</sub>                    | _   | 20      | _   | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _       | 65  | %    |

| REF_CLK to RMII data TXD[1:0], TX_EN delay                             | <sup>t</sup> RMTKHDX                | 2   | _       | 10  | ns   |

| REF_CLK data clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>                   | 1.0 | _       | 4.0 | ns   |

| REF_CLK data clock fall $V_{IH}(max)$ to $V_{IL}(min)$                 | t <sub>RMXF</sub>                   | 1.0 | _       | 4.0 | ns   |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMTKHDX</sub> symbolizes RMII transmit timing (RMT) for the time t<sub>RMX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII(RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

#### Figure 10 shows the RMII transmit AC timing diagram.

Figure 10. RMII Transmit AC Timing Diagram

### 8.2.2.2 RMII Receive AC Timing Specifications

Table 24 provides the RMII receive AC timing specifications.

#### Table 26. RMII Receive AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                               | Symbol <sup>1</sup>                 | Min | Typical | Мах | Unit |

|-------------------------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| REF_CLK clock period                                              | t <sub>RMX</sub>                    | _   | 20      | _   | ns   |

| REF_CLK duty cycle                                                | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _       | 65  | %    |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                     | t <sub>RMRDVKH</sub>                | 4.0 | _       | _   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                      | t <sub>RMRDXKH</sub>                | 2.0 | _       | _   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>                   | 1.0 | _       | 4.0 | ns   |

### 8.3.1 MII Management DC Electrical Characteristics

MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 27.

| Parameter              | Symbol           | Conditions                   |                        | Min  | Мах                    | Unit |

|------------------------|------------------|------------------------------|------------------------|------|------------------------|------|

| Supply voltage (3.3 V) | OV <sub>DD</sub> | —                            |                        | 2.97 | 3.63                   | V    |

| Output high voltage    | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA    | OV <sub>DD</sub> = Min | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage     | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA     | OV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage     | V <sub>IH</sub>  | -                            | _                      | 2.00 | —                      | V    |

| Input low voltage      | V <sub>IL</sub>  | —                            |                        | —    | 0.80                   | V    |

| Input current          | I <sub>IN</sub>  | $0 V \le V_{IN} \le OV_{DD}$ |                        | —    | ±5                     | μΑ   |

Table 27. MII Management DC Electrical Characteristics When Powered at 3.3 V

### 8.3.2 MII Management AC Electrical Specifications

Table 28 provides the MII management AC timing specifications.

#### Table 28. MII Management AC Timing Specifications

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  is 3.3 V  $\pm$  10%.

| Parameter/Condition        | Symbol <sup>1</sup> | Min | Typical | Мах | Unit | Notes |

|----------------------------|---------------------|-----|---------|-----|------|-------|

| MDC frequency              | f <sub>MDC</sub>    | —   | 2.5     | —   | MHz  | _     |

| MDC period                 | t <sub>MDC</sub>    | —   | 400     | —   | ns   | _     |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32  | —       | —   | ns   | _     |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | 10  | —       | 70  | ns   | _     |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5   | —       | —   | ns   | _     |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0   | —       | —   | ns   | _     |

| MDC rise time              | t <sub>MDCR</sub>   | —   | _       | 10  | ns   | _     |

| MDC fall time              | t <sub>MDHF</sub>   | —   | _       | 10  | ns   | —     |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

| Parameter                                                                              | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|----------------------------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| LALE output fall to LAD output transition (LATCH hold time)                            | t <sub>LBOTOT2</sub> | 3   | _   | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time)                            | t <sub>LBOTOT3</sub> | 2.5 | _   | ns   | 7     |

| Local bus clock (LCLK <i>n</i> ) to output valid                                       | t <sub>LBKHOV</sub>  | —   | 3   | ns   | 3     |

| Local bus clock (LCLKn) to output high impedance for LAD/LDP                           | t <sub>LBKHOZ</sub>  | —   | 4   | ns   | 8     |

| Local bus clock (LCLK <i>n</i> ) duty cycle                                            | t <sub>LBDC</sub>    | 47  | 53  | %    | _     |

| Local bus clock (LCLKn) jitter specification                                           | t <sub>LBRJ</sub>    | —   | 400 | ps   | _     |

| Delay between the input clock (PCI_SYNC_IN) of local bus output clock (LCLK <i>n</i> ) | t <sub>lbcdl</sub>   | —   | 1.7 | ns   |       |

#### Table 30. Local Bus General Timing Parameters (continued)

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1).

2. All timings are in reference to falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or rising edge of LCLK0 (for all other inputs).

All signals are measured from OV<sub>DD</sub>/2 of the rising/falling edge of LCLK0 to 0.4 × OV<sub>DD</sub> of the signal in question for 3.3-V signaling levels.

4. Input timings are measured at the pin.

5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

6. t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and the load on LALE output pin equals to the load on LAD output pins.

8. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

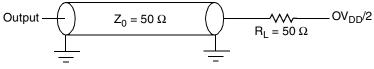

Figure 14 provides the AC test load for the local bus.

Figure 14. Local Bus C Test Load

# 11 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interface of the MPC8323E.

# 11.1 I<sup>2</sup>C DC Electrical Characteristics

Table 33 provides the DC electrical characteristics for the I<sup>2</sup>C interface of the MPC8323E.

### Table 33. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V  $\pm$  10%.

| Parameter                                                                                       | Symbol              | Min                   | Мах                              | Unit | Notes |

|-------------------------------------------------------------------------------------------------|---------------------|-----------------------|----------------------------------|------|-------|

| Input high voltage level                                                                        | V <sub>IH</sub>     | $0.7 \times OV_{DD}$  | OV <sub>DD</sub> + 0.3           | V    | —     |

| Input low voltage level                                                                         | V <sub>IL</sub>     | -0.3                  | $0.3\times\text{OV}_{\text{DD}}$ | V    | —     |

| Low level output voltage                                                                        | V <sub>OL</sub>     | 0                     | 0.4                              | V    | 1     |

| Output fall time from $V_{IH}$ (min) to $V_{IL}$ (max) with a bus capacitance from 10 to 400 pF | <sup>t</sup> I2KLKV | $20 + 0.1 \times C_B$ | 250                              | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                              | t <sub>I2KHKL</sub> | 0                     | 50                               | ns   | 3     |

| Capacitance for each I/O pin                                                                    | Cl                  | —                     | 10                               | pF   | —     |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ OV <sub>DD</sub> )                             | I <sub>IN</sub>     | —                     | ±5                               | μA   | 4     |

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2.  $C_B$  = capacitance of one bus line in pF.

3. Refer to the MPC8323E PowerQUICC II Pro Integrated Communications Processor Reference Manual for information on the digital filter used.

4. I/O pins obstructs the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

# 11.2 I<sup>2</sup>C AC Electrical Specifications

Table 34 provides the AC timing parameters for the  $I^2C$  interface of the MPC8323E.

### Table 34. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 33).

| Parameter                                                                                    |                     | Min              | Мах                  | Unit |

|----------------------------------------------------------------------------------------------|---------------------|------------------|----------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0                | 400                  | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3              | _                    | μs   |

| High period of the SCL clock                                                                 |                     | 0.6              | —                    | μs   |

| Setup time for a repeated START condition                                                    |                     | 0.6              | —                    | μs   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) |                     | 0.6              | —                    | μs   |

| Data setup time                                                                              | t <sub>i2DVKH</sub> | 100              | —                    | ns   |

| Data hold time: CBUS compatible masters I <sup>2</sup> C bus devices                         | t <sub>i2DXKL</sub> | $\overline{0^2}$ | <br>0.9 <sup>3</sup> | μs   |

PCI

#### Table 37 shows the PCI AC timing specifications at 33 MHz.

| Table 37. PCI AC Timing S | Specifications at 33 MHz |

|---------------------------|--------------------------|

|---------------------------|--------------------------|

| Parameter                      | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|--------------------------------|---------------------|-----|-----|------|-------|

| Clock to output valid          | <sup>t</sup> PCKHOV | _   | 11  | ns   | 2     |

| Output hold from clock         | t <sub>PCKHOX</sub> | 2   | _   | ns   | 2     |

| Clock to output high impedence | t <sub>РСКНО</sub>  | —   | 14  | ns   | 2, 3  |

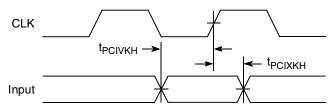

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns   | 2, 4  |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | _   | ns   | 2, 4  |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub>

- 2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

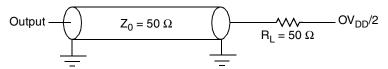

Figure 25 provides the AC test load for PCI.

Figure 25. PCI AC Test Load

Figure 26 shows the PCI input AC timing conditions.

Figure 26. PCI Input AC Timing Measurement Conditions

# 21.3 Pinout Listings

Table 55 shows the pin list of the MPC8323E.

#### Table 55. MPC8323E PBGA Pinout Listing

| Signal                          | Package Pin Number | Pin Type | Power<br>Supply  | Notes |  |  |  |  |  |

|---------------------------------|--------------------|----------|------------------|-------|--|--|--|--|--|

| DDR Memory Controller Interface |                    |          |                  |       |  |  |  |  |  |

| MEMC_MDQ0                       | AE9                | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ1                       | AD10               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ2                       | AF10               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ3                       | AF9                | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ4                       | AF7                | IO       | GV <sub>DD</sub> | _     |  |  |  |  |  |

| MEMC_MDQ5                       | AE10               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ6                       | AD9                | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ7                       | AF8                | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ8                       | AE6                | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ9                       | AD7                | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ10                      | AF6                | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ11                      | AC7                | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ12                      | AD8                | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ13                      | AE7                | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ14                      | AD6                | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ15                      | AF5                | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ16                      | AD18               | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ17                      | AE19               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ18                      | AF17               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ19                      | AF19               | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ20                      | AF18               | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ21                      | AE18               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ22                      | AF20               | IO       | GV <sub>DD</sub> |       |  |  |  |  |  |

| MEMC_MDQ23                      | AD19               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ24                      | AD21               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ25                      | AF22               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ26                      | AC21               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ27                      | AF21               | IO       | GV <sub>DD</sub> | —     |  |  |  |  |  |

| MEMC_MDQ28                      | AE21               | Ю        | GV <sub>DD</sub> | —     |  |  |  |  |  |

Package and Pin Listings

#### Table 55. MPC8323E PBGA Pinout Listing (continued)

| Signal                                                        | Package Pin Number | Pin Type | Power<br>Supply  | Notes |

|---------------------------------------------------------------|--------------------|----------|------------------|-------|

|                                                               | CE/GPIO            |          | 1                |       |

| GPIO_PA0/SER1_TXD[0]/TDMA_TXD[0]/USBTXN                       | G3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA1/SER1_TXD[1]/TDMA_TXD[1]/USBTXP                       | F3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA2/SER1_TXD[2]/TDMA_TXD[2]                              | F2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA3/SER1_TXD[3]/TDMA_TXD[3]                              | E3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA4/SER1_RXD[0]/TDMA_RXD[0]/USBRXP                       | E2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA5/SER1_RXD[1]/TDMA_RXD[1]/USBRXN                       | E1                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA6/SER1_RXD[2]/TDMA_RXD[2]/USBRXD                       | D3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA7/SER1_RXD[3]/TDMA_RXD[3]                              | D2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA8/SER1_CD/TDMA_REQ/USBOE                               | D1                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA9 TDMA_CLKO                                            | C3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA10/SER1_CTS/TDMA_RSYNC                                 | C2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA11/TDMA_STROBE                                         | C1                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA12/SER1_RTS/TDMA_TSYNC                                 | B1                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA13/CLK9/BRGO9                                          | H4                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA14/CLK11/BRGO10                                        | G4                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA15/BRGO7                                               | J4                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA16/ LA0 (LBIU)                                         | K24                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA17/ LA1 (LBIU)                                         | K26                | IO       | OV <sub>DD</sub> |       |

| GPIO_PA18/Enet2_TXD[0]/SER2_TXD[0]/<br>TDMB_TXD[0]/LA2 (LBIU) | G25                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA19/Enet2_TXD[1]/SER2_TXD[1]/<br>TDMB_TXD[1]/LA3 (LBIU) | G26                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA20/Enet2_TXD[2]/SER2_TXD[2]/<br>TDMB_TXD[2]/LA4 (LBIU) | H25                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA21/Enet2_TXD[3]/SER2_TXD[3]/<br>TDMB_TXD[3]/LA5 (LBIU) | H26                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA22/Enet2_RXD[0]/SER2_RXD[0]/<br>TDMB_RXD[0]/LA6 (LBIU) | C25                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA23/Enet2_RXD[1]/SER2_RXD[1]/<br>TDMB_RXD[1]/LA7 (LBIU) | C26                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA24/Enet2_RXD[2]/SER2_RXD[2]/<br>TDMB_RXD[2]/LA8 (LBIU) | D25                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA25/Enet2_RXD[3]/SER2_RXD[3]/<br>TDMB_RXD[3]/LA9 (LBIU) | D26                | IO       | OV <sub>DD</sub> | _     |

| Signal                                | Package Pin Number | Pin Type | Power<br>Supply  | Notes |

|---------------------------------------|--------------------|----------|------------------|-------|

| GPIO_PC10/UPC1_RxDATA[2]/SER5_RXD[2]  | B21                | IO       | OV <sub>DD</sub> |       |

| GPIO_PC11/UPC1_RxDATA[3]/SER5_RXD[3]  | A20                | IO       | OV <sub>DD</sub> |       |

| GPIO_PC12/UPC1_RxDATA[4]              | D19                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC13/UPC1_RxDATA[5]/LSRCID0      | C18                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC14/UPC1_RxDATA[6]/LSRCID1      | D18                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC15/UPC1_RxDATA[7]/LSRCID2      | A25                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC16/UPC1_TxADDR[0]              | C21                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC17/UPC1_TxADDR[1]/LSRCID3      | D22                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC18/UPC1_TxADDR[2]/LSRCID4      | C23                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC19/UPC1_TxADDR[3]/LDVAL        | D23                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC20/UPC1_RxADDR[0]              | C17                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PC21/UPC1_RxADDR[1]              | D17                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PC22/UPC1_RxADDR[2]              | C16                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC23/UPC1_RxADDR[3]              | D16                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC24/UPC1_RxSOC/SER5_CD          | A16                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC25/UPC1_RxCLAV                 | D20                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC26/UPC1_RxPRTY/CE_EXT_REQ2     | E23                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC27/UPC1_RxEN                   | B17                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC28/UPC1_TxSOC                  | B22                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC29/UPC1_TxCLAV/SER5_CTS        | A17                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC30/UPC1_TxPRTY                 | A22                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PC31/UPC1_TxEN/SER5_RTS          | C20                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD0/SPIMOSI                      | A2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD1/SPIMISO                      | B2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD2/SPICLK                       | B3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD3/SPISEL                       | A3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD4/SPI_MDIO/CE_MUX_MDIO         | A4                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD5/SPI_MDC/CE_MUX_MDC           | B4                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD6/CLK8/BRGO16/CE_EXT_REQ3      | F24                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD7/GTM1_TIN1/GTM2_TIN2/CLK5     | G24                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD8/GTM1_TGATE1/GTM2_TGATE2/CLK6 | H24                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PD9/GTM1_TOUT1                   | D24                | IO       | OV <sub>DD</sub> | —     |

### Table 55. MPC8323E PBGA Pinout Listing (continued)

### 22.1 Clocking in PCI Host Mode

When the MPC8323E is configured as a PCI host device (RCWH[PCIHOST] = 1), CLKIN is its primary input clock. CLKIN feeds the PCI clock divider ( $\div$ 2) and the PCI\_SYNC\_OUT and PCI\_CLK\_OUT multiplexors. The CFG\_CLKIN\_DIV configuration input selects whether CLKIN or CLKIN/2 is driven out on the PCI\_SYNC\_OUT signal.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system.

### 22.1.1 PCI Clock Outputs (PCI\_CLK\_OUT[0:2])

When the MPC8323E is configured as a PCI host, it provides three separate clock output signals, PCI\_CLK\_OUT[0:2], for external PCI agents.

When the device comes out of reset, the PCI clock outputs are disabled and are actively driven to a steady low state. Each of the individual clock outputs can be enabled (enable toggling of the clock) by setting its corresponding OCCR[PCICOEn] bit. All output clocks are phase-aligned to each other.

# 22.2 Clocking in PCI Agent Mode

When the MPC8323E is configured as a PCI agent device, PCI\_CLK is the primary input clock. In agent mode, the CLKIN signal should be tied to GND, and the clock output signals, PCI\_CLK\_OUT*n* and PCI\_SYNC\_OUT, are not used.

# 22.3 System Clock Domains

As shown in Figure 43, the primary clock input (frequency) is multiplied up by the system phase-locked loop (PLL) and the clock unit to create three major clock domains:

- The coherent system bus clock (*csb\_clk*)

- The QUICC Engine clock (*ce\_clk*)

- The internal clock for the DDR controller (*ddr\_clk*)

- The internal clock for the local bus controller (*lb\_clk*)

The *csb\_clk* frequency is derived from a complex set of factors that can be simplified into the following equation:

$csb_clk = [PCI_SYNC_IN \times (1 + \sim \overline{CFG_CLKIN_DIV})] \times SPMF$

In PCI host mode, PCI\_SYNC\_IN  $\times$  (1 +  $\sim \overline{CFG}_{CLKIN}_{DIV}$ ) is the CLKIN frequency.

The *csb\_clk* serves as the clock input to the e300c2 core. A second PLL inside the core multiplies up the *csb\_clk* frequency to create the internal clock for the core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL) which is loaded at power-on reset or by one of the hard-coded reset options. See the "Reset Configuration" section in the *MPC8323E PowerQUICC II Pro Communications Processor Reference Manual* for more information.

#### Clocking

shows the expected frequency values for the CSB frequency for select *csb\_clk* to CLKIN/PCI\_SYNC\_IN ratios.

|                                          | SPMF | <i>csb_clk</i> :<br>Input Clock<br>Ratio <sup>2</sup> | Input Clo | Input Clock Frequency (MHz) <sup>2</sup> |       |  |

|------------------------------------------|------|-------------------------------------------------------|-----------|------------------------------------------|-------|--|

| CFG_CLKIN_DIV_B<br>at Reset <sup>1</sup> |      |                                                       | 25        | 33.33                                    | 66.67 |  |

|                                          |      |                                                       | csb_cl    | <i>csb_clk</i> Frequency (MHz)           |       |  |

| High                                     | 0010 | 2 : 1                                                 |           |                                          | 133   |  |

| High                                     | 0011 | 3 : 1                                                 |           | 100                                      |       |  |

| High                                     | 0100 | 4 : 1                                                 | 100       | 133                                      |       |  |

| High                                     | 0101 | 5 : 1                                                 | 125       |                                          |       |  |

| High                                     | 0110 | 6 : 1                                                 |           |                                          |       |  |

| High                                     | 0111 | 7:1                                                   |           |                                          |       |  |

| High                                     | 1000 | 8 : 1                                                 |           |                                          |       |  |

| High                                     | 1001 | 9:1                                                   |           |                                          |       |  |

| High                                     | 1010 | 10 : 1                                                | -         |                                          |       |  |

| High                                     | 1011 | 11:1                                                  | -         |                                          |       |  |

| High                                     | 1100 | 12 : 1                                                | -         |                                          |       |  |

| High                                     | 1101 | 13 : 1                                                | -         |                                          |       |  |

| High                                     | 1110 | 14 : 1                                                | -         |                                          |       |  |

| High                                     | 1111 | 15 : 1                                                | -         |                                          |       |  |

| High                                     | 0000 | 16 : 1                                                | -         |                                          |       |  |

| Low                                      | 0010 | 2:1                                                   |           |                                          | 133   |  |

| Low                                      | 0011 | 3 : 1                                                 | -         | 100                                      |       |  |

| Low                                      | 0100 | 4 : 1                                                 | -         | 133                                      |       |  |

| Low                                      | 0101 | 5 : 1                                                 | -         |                                          |       |  |

| Low                                      | 0110 | 6 : 1                                                 | -         |                                          |       |  |

| Low                                      | 0111 | 7:1                                                   | -         |                                          |       |  |

| Low                                      | 1000 | 8 : 1                                                 | -         |                                          |       |  |

| Low                                      | 1001 | 9:1                                                   | -         |                                          |       |  |

| Low                                      | 1010 | 10 : 1                                                | -         |                                          |       |  |

| Low                                      | 1011 | 11 : 1                                                |           |                                          |       |  |

| Low                                      | 1100 | 12 : 1                                                |           |                                          |       |  |

| Low                                      | 1101 | 13 : 1                                                |           |                                          |       |  |

| Low                                      | 1110 | 14 : 1                                                |           |                                          |       |  |

| Low                                      | 1111 | 15 : 1                                                |           |                                          |       |  |

| Low                                      | 0000 | 16 : 1                                                |           |                                          |       |  |

#### Table 59. CSB Frequency Options

<sup>1</sup> CFG\_CLKIN\_DIV\_B is only used for host mode; CLKIN must be tied low and

CFG\_CLKIN\_DIV\_B must be pulled up (high) in agent mode.

<sup>2</sup> CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode.

Thermal

where:

$R_{\theta IA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device.

To illustrate the thermal performance of the devices with heat sinks, the thermal performance has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, air flow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

Accurate thermal design requires thermal modeling of the application environment using computational fluid dynamics software which can model both the conduction cooling and the convection cooling of the air moving through the application. Simplified thermal models of the packages can be assembled using the junction-to-case and junction-to-board thermal resistances listed in the thermal resistance table. More detailed thermal models can be made available on request.

Heat sink vendors include the following list:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                              | 603-224-9988 |

|------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #12<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                             | 408-567-8082 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com | 818-842-7277 |

| Millennium Electronics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-thermal.com  | 408-436-8770 |

| Tyco Electronics<br>Chip Coolers <sup>™</sup><br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com | 800-522-2800 |

NP

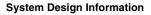

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of package, without the inductance of vias.

Figure 44 shows the PLL power supply filter circuit.

Figure 44. PLL Power Supply Filter Circuit

### 24.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the MPC8323E can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8323E system, and the MPC8323E itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ , and  $GV_{DD}$  pins of the MPC8323E. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and GND power planes in the PCB, utilizing short traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ , and  $GV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330 µF (AVX TPS tantalum or Sanyo OSCON).

# 24.4 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ , or  $GV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $GV_{DD}$ ,  $OV_{DD}$ , and GND pins of the MPC8323E.

# 24.5 Output Buffer DC Impedance

The MPC8323E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 45). The

Document Revision History

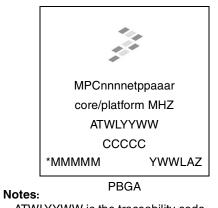

### 25.2 Part Marking

Parts are marked as in the example shown in Figure 46.

ATWLYYWW is the traceability code. CCCCC is the country code. MMMMM is the mask number. YWWLAZ is the assembly traceability code.

Figure 46. Freescale Part Marking for PBGA Devices

# 26 Document Revision History

Table 67 provides a revision history for this hardware specification.

#### Table 67. Document Revision History

| Rev.<br>No. | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4           | 09/2010 | <ul> <li>Replaced all instances of "LCCR" with "LCRR" throughout.</li> <li>Added footnotes 3 and 4 in Table 2, "Recommended Operating Conditions<sup>3</sup>."</li> <li>Modified Section 8.1.1, "DC Electrical Characteristics."</li> <li>Modified Table 23, "MII Transmit AC Timing Specifications."</li> <li>Modified Table 24, "MII Receive AC Timing Specifications."</li> <li>Added footnote 7 and 8, and modified some signal names in Table 55, "MPC8323E PBGA Pinout Listing."</li> </ul>                                                                                                                                                                                                                                                                          |  |

| 3           | 12/2009 | <ul> <li>Removed references for note 4 from Table 1.</li> <li>Added Figure 2 in Section 2.1.2, "Power Supply Voltage Specification.</li> <li>Added symbol T<sub>A</sub> in Table 2.</li> <li>Added footnote 2 in Table 2.</li> <li>Added a note in Section 4, "Clock Input Timing for rise/fall time of QE input pins.</li> <li>Modified CLKIN, PCI_CLK rise/fall time parameters in Table 8. Modified min value of t<sub>MCK</sub> in Table 19.</li> <li>Modified Figure 43.</li> <li>Modified formula for ce_clk calculation in Section 22.3, "System Clock Domains.</li> <li>Added a note in Section 22.4, "System PLL Configuration.</li> <li>Removed the signal ECID_TMODE_IN from Table 55.</li> <li>Removed all references of RST signals from Table 55.</li> </ul> |  |