#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Active                                                      |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e300c2                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 266MHz                                                      |

| Co-Processors/DSP               | Communications; QUICC Engine                                |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100Mbps (3)                                              |

| SATA                            | -                                                           |

| USB                             | USB 2.0 (1)                                                 |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | -                                                           |

| Package / Case                  | 516-BBGA                                                    |

| Supplier Device Package         | 516-PBGA (27x27)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8323vraddca |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

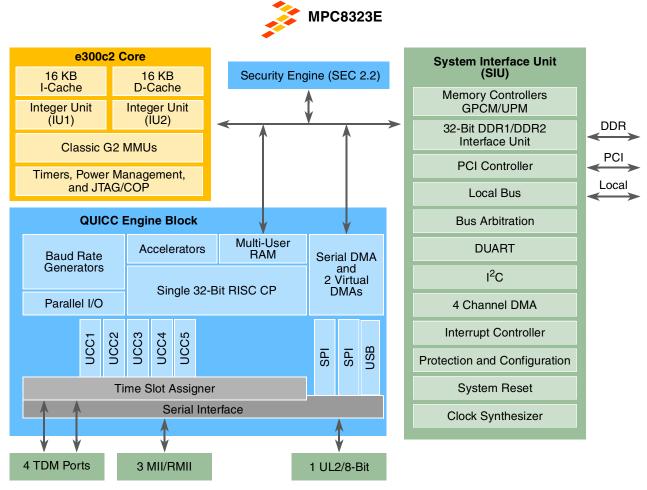

## 1 Overview

The MPC8323E incorporates the e300c2 (MPC603e-based) core built on Power Architecture® technology, which includes 16 Kbytes of L1 instruction and data caches, dual integer units, and on-chip memory management units (MMUs). The e300c2 core does not contain a floating point unit (FPU). The MPC8323E also includes a 32-bit PCI controller, four DMA channels, a security engine, and a 32-bit DDR1/DDR2 memory controller.

A new communications complex based on QUICC Engine technology forms the heart of the networking capability of the MPC8323E. The QUICC Engine block contains several peripheral controllers and a 32-bit RISC controller. Protocol support is provided by the main workhorses of the device—the unified communication controllers (UCCs). Note that the MPC8321 and MPC8321E do not support UTOPIA. A block diagram of the MPC8323E is shown in Figure 1.

Figure 1. MPC8323E Block Diagram

Each of the five UCCs can support a variety of communication protocols: 10/100 Mbps Ethernet, serial ATM, HDLC, UART, and BISYNC—and, in the MPC8323E and MPC8323, multi-PHY ATM and ATM support for up to OC-3 speeds.

Electrical Characteristics

## 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8323E. The MPC8323E is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

### 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

### 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

|                                                                |                                                                                                       | •                                               |                                                  |      |       |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------|------|-------|

| Char                                                           | acteristic                                                                                            | Symbol                                          | Max Value                                        | Unit | Notes |

| Core supply voltage                                            |                                                                                                       | V <sub>DD</sub>                                 | -0.3 to 1.26                                     | V    | —     |

| PLL supply voltage                                             |                                                                                                       | AV <sub>DDn</sub>                               | -0.3 to 1.26                                     | V    | —     |

| DDR1 and DDR2 DRAM I/O vo                                      | Itage                                                                                                 | GV <sub>DD</sub> -0.3 to 2.75 V<br>-0.3 to 1.98 |                                                  | V    | —     |

| PCI, local bus, DUART, system of SPI, MII, RMII, MII managemen | control and power management, I <sup>2</sup> C,<br>ht, and JTAG I/O voltage                           | $OV_{DD}$                                       | -0.3 to 3.6                                      | V    | —     |

| Input voltage                                                  | DDR1/DDR2 DRAM signals                                                                                | MV <sub>IN</sub>                                | V <sub>IN</sub> -0.3 to (GV <sub>DD</sub> + 0.3) |      | 2     |

|                                                                | DDR1/DDR2 DRAM reference                                                                              | MV <sub>REF</sub>                               | –0.3 to (GV <sub>DD</sub> + 0.3)                 | V    | 2     |

|                                                                | Local bus, DUART, CLKIN, system control and power management, I <sup>2</sup> C, SPI, and JTAG signals | OV <sub>IN</sub>                                | -0.3 to (OV <sub>DD</sub> + 0.3)                 | V    | 3     |

|                                                                | PCI                                                                                                   | OV <sub>IN</sub>                                | -0.3 to (OV <sub>DD</sub> + 0.3)                 | V    | 5     |

| Storage temperature range                                      | ·                                                                                                     | T <sub>STG</sub>                                | -55 to 150                                       | °C   | —     |

### Table 1. Absolute Maximum Ratings<sup>1</sup>

Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during power-on reset and power-down sequences.

3. Caution: OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during power-on reset and power-down sequences.

### 2.1.2 Power Supply Voltage Specification

Table 2 provides the recommended operating conditions for the MPC8323E. Note that these values are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Characteristic                                                                                    | Symbol                         | Recommended<br>Value            | Unit | Notes |

|---------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------|------|-------|

| Core supply voltage                                                                               | V <sub>DD</sub>                | 1.0 V ± 50 mV                   | V    | 1     |

| PLL supply voltage                                                                                | AV <sub>DD</sub>               | 1.0 V ± 50 mV                   | V    | 1     |

| DDR1 and DDR2 DRAM I/O voltage                                                                    | GV <sub>DD</sub>               | 2.5 V ± 125 mV<br>1.8 V ± 90 mV | V    | 1     |

| PCI, local bus, DUART, system control and power management, $\rm I^2C,$ SPI, and JTAG I/O voltage | OV <sub>DD</sub>               | 3.3 V ± 300 mV                  | V    | 1     |

| Junction temperature                                                                              | T <sub>A</sub> /T <sub>J</sub> | 0 to 105                        | °C   | 2     |

#### Table 2. Recommended Operating Conditions<sup>3</sup>

Note:

1. GV<sub>DD</sub>, OV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

2. Minimum temperature is specified with T<sub>A</sub>; maximum temperature is specified with T<sub>J</sub>.

3. All IO pins should be interfaced with peripherals operating at same voltage level.

4. This voltage is the input to the filter discussed in Section 24.2, "PLL Power Supply Filtering" and not necessarily the voltage at the AVDD pin, which may be reduced due to voltage drop across the filter.

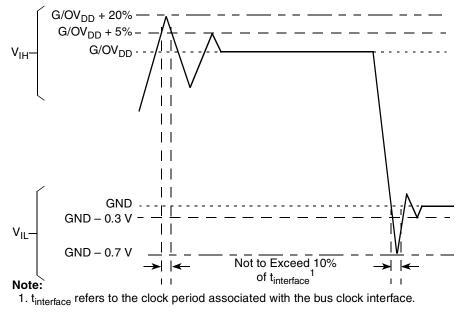

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8323E

Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>

**Ethernet and MII Management**

(management data clock). The MII and RMII are defined for 3.3 V. The electrical characteristics for MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 DC Electrical Characteristics

All MII and RMII drivers and receivers comply with the DC parametric attributes specified in Table 22.

| Parameter            | Symbol           | Conditions                |                        | Min  | Мах                    | Unit |

|----------------------|------------------|---------------------------|------------------------|------|------------------------|------|

| Supply voltage 3.3 V | OV <sub>DD</sub> | —                         |                        | 2.97 | 3.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -4.0 mA | OV <sub>DD</sub> = Min | 2.40 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 4.0 mA  | OV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                         | —                      | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                         | —                      | -0.3 | 0.90                   | V    |

| Input current        | I <sub>IN</sub>  | 0 V ≤ V <sub>IN</sub>     | $V \le ON^{DD}$        | —    | ±5                     | μA   |

Table 22. MII and RMII DC Electrical Characteristics

## 8.2 MII and RMII AC Timing Specifications

The AC timing specifications for MII and RMII are presented in this section.

### 8.2.1 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.1.1 MII Transmit AC Timing Specifications

Table 23 provides the MII transmit AC timing specifications.

### Table 23. MII Transmit AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                             | Symbol <sup>1</sup>                 | Min | Typical | Max | Unit |

|-------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub>                    | _   | 400     | _   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                    | _   | 40      | _   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _       | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                 | 1   | 5       | 15  | ns   |

| TX_CLK data clock rise time                     | t <sub>MTXR</sub>                   | 1.0 | —       | 4.0 | ns   |

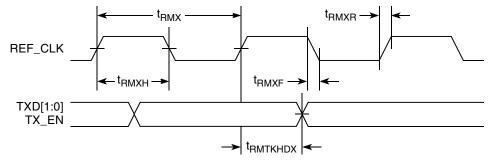

### 8.2.2.1 RMII Transmit AC Timing Specifications

Table 23 provides the RMII transmit AC timing specifications.

#### **Table 25. RMII Transmit AC Timing Specifications**

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Typical | Мах | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| REF_CLK clock                                                          | t <sub>RMX</sub>                    | _   | 20      | _   | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _       | 65  | %    |

| REF_CLK to RMII data TXD[1:0], TX_EN delay                             | <sup>t</sup> RMTKHDX                | 2   | _       | 10  | ns   |

| REF_CLK data clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>                   | 1.0 | _       | 4.0 | ns   |

| REF_CLK data clock fall $V_{IH}(max)$ to $V_{IL}(min)$                 | t <sub>RMXF</sub>                   | 1.0 | _       | 4.0 | ns   |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMTKHDX</sub> symbolizes RMII transmit timing (RMT) for the time t<sub>RMX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII(RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

### Figure 10 shows the RMII transmit AC timing diagram.

Figure 10. RMII Transmit AC Timing Diagram

### 8.2.2.2 RMII Receive AC Timing Specifications

Table 24 provides the RMII receive AC timing specifications.

### Table 26. RMII Receive AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                               | Symbol <sup>1</sup>                 | Min | Typical | Мах | Unit |

|-------------------------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| REF_CLK clock period                                              | t <sub>RMX</sub>                    | _   | 20      | _   | ns   |

| REF_CLK duty cycle                                                | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _       | 65  | %    |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                     | t <sub>RMRDVKH</sub>                | 4.0 | _       | _   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                      | t <sub>RMRDXKH</sub>                | 2.0 | _       | _   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>                   | 1.0 | _       | 4.0 | ns   |

### 8.3.1 MII Management DC Electrical Characteristics

MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 27.

| Parameter              | Symbol           | Conditions                   |                        | Min  | Мах                    | Unit |

|------------------------|------------------|------------------------------|------------------------|------|------------------------|------|

| Supply voltage (3.3 V) | OV <sub>DD</sub> | —                            |                        | 2.97 | 3.63                   | V    |

| Output high voltage    | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA    | OV <sub>DD</sub> = Min | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage     | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA     | OV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage     | V <sub>IH</sub>  | -                            | _                      |      | —                      | V    |

| Input low voltage      | V <sub>IL</sub>  | _                            |                        | —    | 0.80                   | V    |

| Input current          | I <sub>IN</sub>  | $0 V \le V_{IN} \le OV_{DD}$ |                        | —    | ±5                     | μΑ   |

Table 27. MII Management DC Electrical Characteristics When Powered at 3.3 V

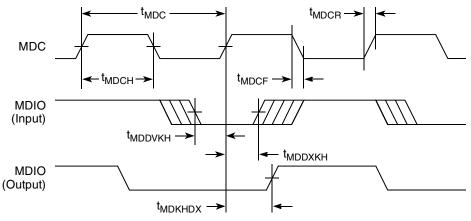

### 8.3.2 MII Management AC Electrical Specifications

Table 28 provides the MII management AC timing specifications.

#### Table 28. MII Management AC Timing Specifications

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  is 3.3 V  $\pm$  10%.

| Parameter/Condition        | Symbol <sup>1</sup> | Min | Typical | Мах | Unit | Notes |

|----------------------------|---------------------|-----|---------|-----|------|-------|

| MDC frequency              | f <sub>MDC</sub>    | —   | 2.5     | —   | MHz  | _     |

| MDC period                 | t <sub>MDC</sub>    | —   | 400     | —   | ns   | _     |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32  | —       | —   | ns   | _     |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | 10  | —       | 70  | ns   | _     |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5   | —       | —   | ns   | _     |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0   | —       | —   | ns   | _     |

| MDC rise time              | t <sub>MDCR</sub>   | —   | —       | 10  | ns   | _     |

| MDC fall time              | t <sub>MDHF</sub>   | —   | _       | 10  | ns   | —     |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

Local Bus

Figure 13 shows the MII management AC timing diagram.

Figure 13. MII Management Interface Timing Diagram

## 9 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8323E.

## 9.1 Local Bus DC Electrical Characteristics

Table 29 provides the DC electrical characteristics for the local bus interface.

| Table 29. Local Bus DC Electrical Characteristics |

|---------------------------------------------------|

|---------------------------------------------------|

| Parameter                                          | Symbol          | Min                    | Мах                    | Unit |

|----------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                           | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$ | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | _                      | V    |

| Low-level output voltage, I <sub>OL</sub> = 100 μA | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current                                      | I <sub>IN</sub> | —                      | ±5                     | μA   |

## 9.2 Local Bus AC Electrical Specifications

Table 30 describes the general timing parameters of the local bus interface of the MPC8323E.

Table 30. Local Bus General Timing Parameters

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 15  | —   | ns   | 2     |

| Input setup to local bus clock (LCLKn)                      | t <sub>LBIVKH</sub>  | 7   | —   | ns   | 3, 4  |

| Input hold from local bus clock (LCLKn)                     | t <sub>LBIXKH</sub>  | 1.0 | —   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | —   | ns   | 5     |

# 11 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interface of the MPC8323E.

## 11.1 I<sup>2</sup>C DC Electrical Characteristics

Table 33 provides the DC electrical characteristics for the I<sup>2</sup>C interface of the MPC8323E.

### Table 33. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V  $\pm$  10%.

| Parameter                                                                                       | Symbol              | Min                   | Мах                              | Unit | Notes |

|-------------------------------------------------------------------------------------------------|---------------------|-----------------------|----------------------------------|------|-------|

| Input high voltage level                                                                        | V <sub>IH</sub>     | $0.7 \times OV_{DD}$  | OV <sub>DD</sub> + 0.3           | V    | —     |

| Input low voltage level                                                                         | V <sub>IL</sub>     | -0.3                  | $0.3\times\text{OV}_{\text{DD}}$ | V    | —     |

| Low level output voltage                                                                        | V <sub>OL</sub>     | 0                     | 0.4                              | V    | 1     |

| Output fall time from $V_{IH}$ (min) to $V_{IL}$ (max) with a bus capacitance from 10 to 400 pF | <sup>t</sup> I2KLKV | $20 + 0.1 \times C_B$ | 250                              | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                              | t <sub>I2KHKL</sub> | 0                     | 50                               | ns   | 3     |

| Capacitance for each I/O pin                                                                    | Cl                  | —                     | 10                               | pF   | —     |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ OV <sub>DD</sub> )                             | I <sub>IN</sub>     | —                     | ±5                               | μA   | 4     |

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2.  $C_B$  = capacitance of one bus line in pF.

3. Refer to the MPC8323E PowerQUICC II Pro Integrated Communications Processor Reference Manual for information on the digital filter used.

4. I/O pins obstructs the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

## 11.2 I<sup>2</sup>C AC Electrical Specifications

Table 34 provides the AC timing parameters for the  $I^2C$  interface of the MPC8323E.

### Table 34. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 33).

| Parameter                                                                                    | Symbol <sup>1</sup> | Min              | Мах                  | Unit |

|----------------------------------------------------------------------------------------------|---------------------|------------------|----------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0                | 400                  | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3              | _                    | μs   |

| High period of the SCL clock                                                                 | t <sub>l2CH</sub>   | 0.6              | —                    | μs   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6              | —                    | μs   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6              | —                    | μs   |

| Data setup time                                                                              | t <sub>i2DVKH</sub> | 100              | —                    | ns   |

| Data hold time: CBUS compatible masters I <sup>2</sup> C bus devices                         | t <sub>i2DXKL</sub> | $\overline{0^2}$ | <br>0.9 <sup>3</sup> | μs   |

PCI

### Table 37 shows the PCI AC timing specifications at 33 MHz.

| Table 37. PCI AC Timing S | Specifications at 33 MHz |

|---------------------------|--------------------------|

|---------------------------|--------------------------|

| Parameter                      | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|--------------------------------|---------------------|-----|-----|------|-------|

| Clock to output valid          | <sup>t</sup> PCKHOV | _   | 11  | ns   | 2     |

| Output hold from clock         | t <sub>PCKHOX</sub> | 2   | —   | ns   | 2     |

| Clock to output high impedence | t <sub>PCKHOZ</sub> | -   | 14  | ns   | 2, 3  |

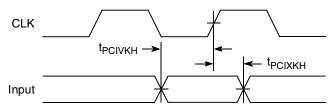

| Input setup to clock           | t <sub>PCIVKH</sub> | 3.0 | _   | ns   | 2, 4  |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | _   | ns   | 2, 4  |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub>

- 2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

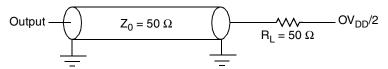

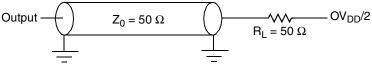

Figure 25 provides the AC test load for PCI.

Figure 25. PCI AC Test Load

Figure 26 shows the PCI input AC timing conditions.

Figure 26. PCI Input AC Timing Measurement Conditions

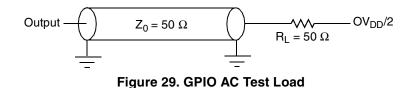

Figure 29 provides the AC test load for the GPIO.

## 15 IPIC

This section describes the DC and AC electrical specifications for the external interrupt pins of the MPC8323E.

### **15.1 IPIC DC Electrical Characteristics**

Table 42 provides the DC electrical characteristics for the external interrupt pins of the MPC8323E.

| Characteristic     | Symbol          | Condition                | Min  | Мах                    | Unit |

|--------------------|-----------------|--------------------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | _                        | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | _                        | -0.3 | 0.8                    | V    |

| Input current      | I <sub>IN</sub> | _                        | —    | ±5                     | μA   |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA | —    | 0.5                    | V    |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | —    | 0.4                    | V    |

Table 42. IPIC DC Electrical Characteristics<sup>1,2</sup>

#### Notes:

1. This table applies for pins IRQ[0:7], IRQ\_OUT, MCP\_OUT, and CE ports Interrupts.

2. IRQ\_OUT and MCP\_OUT are open drain pins, thus V<sub>OH</sub> is not relevant for those pins.

### 15.2 IPIC AC Timing Specifications

Table 43 provides the IPIC input and output AC timing specifications.

### Table 43. IPIC Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs-minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

#### Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when working

in edge triggered mode.

SPI

## 16 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8323E.

### **16.1 SPI DC Electrical Characteristics**

Table 44 provides the DC electrical characteristics for the MPC8323E SPI.

| Characteristic      | Symbol          | Condition                        | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA        | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA         | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA         | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                                | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \ V \leq V_{IN} \leq OV_{DD}$ | —    | ±5                     | μA   |

### Table 44. SPI DC Electrical Characteristics

### 16.2 SPI AC Timing Specifications

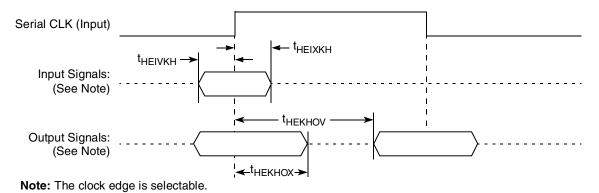

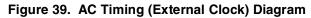

Table 45 and provide the SPI input and output AC timing specifications.

Table 45. SPI AC Timing Specifications<sup>1</sup>

| Characteristic                                           | Symbol <sup>2</sup> | Min | Мах | Unit |

|----------------------------------------------------------|---------------------|-----|-----|------|

| SPI outputs—Master mode (internal clock) delay           | t <sub>NIKHOV</sub> | 0.5 | 6   | ns   |

| SPI outputs—Slave mode (external clock) delay            | t <sub>NEKHOV</sub> | 2   | 8   | ns   |

| SPI inputs—Master mode (internal clock) input setup time | t <sub>NIIVKH</sub> | 6   | —   | ns   |

| SPI inputs—Master mode (internal clock) input hold time  | t <sub>NIIXKH</sub> | 0   | —   | ns   |

| SPI inputs—Slave mode (external clock) input setup time  | t <sub>NEIVKH</sub> | 4   | —   | ns   |

| SPI inputs—Slave mode (external clock) input hold time   | t <sub>NEIXKH</sub> | 2   | —   | ns   |

Notes:

1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

</sub></sub>

Figure 30 provides the AC test load for the SPI.

Figure 30. SPI AC Test Load

Figure 39 shows the timing with external clock.

Figure 40 shows the timing with internal clock.

Figure 40. AC Timing (Internal Clock) Diagram

| Signal                              | Package Pin Number         | Pin Type | Power<br>Supply  | Notes |

|-------------------------------------|----------------------------|----------|------------------|-------|

| LCS1                                | AB25                       | 0        | OV <sub>DD</sub> | 4     |

| LCS2                                | AA23                       | 0        | OV <sub>DD</sub> | 4     |

| LCS3                                | AA24                       | 0        | OV <sub>DD</sub> | 4     |

| <u>LWE0</u>                         | Y23                        | 0        | OV <sub>DD</sub> | 4     |

| LWE1                                | W25                        | 0        | OV <sub>DD</sub> | 4     |

| LBCTL                               | V25                        | 0        | OV <sub>DD</sub> | 4     |

| LALE                                | V24                        | 0        | OV <sub>DD</sub> | 7     |

| CFG_RESET_SOURCE[0]/LSDA10/LGPL0    | L23                        | IO       | OV <sub>DD</sub> |       |

| CFG_RESET_SOURCE[1]/LSDWE/LGPL1     | K23                        | IO       | OV <sub>DD</sub> |       |

| LSDRAS/LGPL2/LOE                    | J23                        | 0        | OV <sub>DD</sub> | 4     |

| CFG_RESET_SOURCE[2]/LSDCAS/LGPL3    | H23                        | IO       | OV <sub>DD</sub> |       |

| LGPL4/LGTA/LUPWAIT/LPBSE            | G23                        | IO       | OV <sub>DD</sub> | 4, 8  |

| LGPL5                               | AC22                       | 0        | OV <sub>DD</sub> | 4     |

| LCLK0                               | Y24                        | 0        | OV <sub>DD</sub> | 7     |

| LCLK1                               | Y25                        | 0        | OV <sub>DD</sub> | 7     |

|                                     | DUART                      | 1        |                  |       |

| UART_SOUT1/MSRCID0 (DDR ID)/LSRCID0 | G1                         | IO       | OV <sub>DD</sub> | _     |

| UART_SIN1/MSRCID1 (DDR ID)/LSRCID1  | G2                         | IO       | OV <sub>DD</sub> | —     |

| UART_CTS1/MSRCID2 (DDR ID)/LSRCID2  | H3                         | IO       | OV <sub>DD</sub> | —     |

| UART_RTS1/MSRCID3 (DDR ID)/LSRCID3  | К3                         | IO       | OV <sub>DD</sub> | —     |

| UART_SOUT2/MSRCID4 (DDR ID)/LSRCID4 | H2                         | IO       | OV <sub>DD</sub> | —     |

| UART_SIN2/MDVAL (DDR ID)/LDVAL      | H1                         | IO       | OV <sub>DD</sub> | —     |

| UART_CTS2                           | J3                         | IO       | OV <sub>DD</sub> | —     |

| UART_RTS2                           | K4                         | IO       | OV <sub>DD</sub> | —     |

|                                     | I <sup>2</sup> C interface | -        |                  |       |

| IIC_SDA/CKSTOP_OUT                  | AE24                       | IO       | OV <sub>DD</sub> | 2     |

| IIC_SCL/CKSTOP_IN                   | AF24                       | IO       | OV <sub>DD</sub> | 2     |

| Program                             | mable Interrupt Controller | •        |                  |       |

| MCP_OUT                             | AD25                       | 0        | OV <sub>DD</sub> | _     |

| IRQ0/MCP_IN                         | AD26                       | Ι        | OV <sub>DD</sub> | —     |

| ĪRQ1                                | K1                         | IO       | OV <sub>DD</sub> | -     |

| ĪRQ2                                | K2                         | I        | OV <sub>DD</sub> | -     |

|                                     |                            |          |                  |       |

### Table 55. MPC8323E PBGA Pinout Listing (continued)

#### Table 55. MPC8323E PBGA Pinout Listing (continued)

| Signal                                                        | Package Pin Number | Pin Type | Power<br>Supply  | Notes |

|---------------------------------------------------------------|--------------------|----------|------------------|-------|

|                                                               | CE/GPIO            |          | 1                |       |

| GPIO_PA0/SER1_TXD[0]/TDMA_TXD[0]/USBTXN                       | G3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA1/SER1_TXD[1]/TDMA_TXD[1]/USBTXP                       | F3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA2/SER1_TXD[2]/TDMA_TXD[2]                              | F2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA3/SER1_TXD[3]/TDMA_TXD[3]                              | E3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA4/SER1_RXD[0]/TDMA_RXD[0]/USBRXP                       | E2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA5/SER1_RXD[1]/TDMA_RXD[1]/USBRXN                       | E1                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA6/SER1_RXD[2]/TDMA_RXD[2]/USBRXD                       | D3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA7/SER1_RXD[3]/TDMA_RXD[3]                              | D2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA8/SER1_CD/TDMA_REQ/USBOE                               | D1                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA9 TDMA_CLKO                                            | C3                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA10/SER1_CTS/TDMA_RSYNC                                 | C2                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA11/TDMA_STROBE                                         | C1                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA12/SER1_RTS/TDMA_TSYNC                                 | B1                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA13/CLK9/BRGO9                                          | H4                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA14/CLK11/BRGO10                                        | G4                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA15/BRGO7                                               | J4                 | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA16/ LA0 (LBIU)                                         | K24                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA17/ LA1 (LBIU)                                         | K26                | IO       | OV <sub>DD</sub> |       |

| GPIO_PA18/Enet2_TXD[0]/SER2_TXD[0]/<br>TDMB_TXD[0]/LA2 (LBIU) | G25                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA19/Enet2_TXD[1]/SER2_TXD[1]/<br>TDMB_TXD[1]/LA3 (LBIU) | G26                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA20/Enet2_TXD[2]/SER2_TXD[2]/<br>TDMB_TXD[2]/LA4 (LBIU) | H25                | IO       | OV <sub>DD</sub> | —     |

| GPIO_PA21/Enet2_TXD[3]/SER2_TXD[3]/<br>TDMB_TXD[3]/LA5 (LBIU) | H26                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA22/Enet2_RXD[0]/SER2_RXD[0]/<br>TDMB_RXD[0]/LA6 (LBIU) | C25                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA23/Enet2_RXD[1]/SER2_RXD[1]/<br>TDMB_RXD[1]/LA7 (LBIU) | C26                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA24/Enet2_RXD[2]/SER2_RXD[2]/<br>TDMB_RXD[2]/LA8 (LBIU) | D25                | IO       | OV <sub>DD</sub> | _     |

| GPIO_PA25/Enet2_RXD[3]/SER2_RXD[3]/<br>TDMB_RXD[3]/LA9 (LBIU) | D26                | IO       | OV <sub>DD</sub> | _     |

| Signal                              | Package Pin Number                                                                                                                                                                                                                                                               | Pin Type         | Power<br>Supply  | Notes |  |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------|--|--|--|--|

| GPIO_PD10/GTM1_TIN2/GTM2_TIN1/CLK17 | J24                                                                                                                                                                                                                                                                              | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD11/GTM1_TGATE2/GTM2_TGATE1   | B25                                                                                                                                                                                                                                                                              | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD12/GTM1_TOUT2/GTM2_TOUT1     | C4                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD13/GTM1_TIN3/GTM2_TIN4/BRGO8 | D4                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD14/GTM1_TGATE3/GTM2_TGATE4   | D5                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD15/GTM1_TOUT3                | A5                                                                                                                                                                                                                                                                               | IO               | OV <sub>DD</sub> |       |  |  |  |  |

| GPIO_PD16/GTM1_TIN4/GTM2_TIN3       | B5                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD17/GTM1_TGATE4/GTM2_TGATE3   | C5                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD18/GTM1_TOUT4/GTM2_TOUT3     | A6                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD19/CE_RISC1_INT/CE_EXT_REQ4  | B6                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD20/CLK18/BRGO6               | D21                                                                                                                                                                                                                                                                              | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD21/CLK16/BRGO5/UPC1_CLKO     | C19                                                                                                                                                                                                                                                                              | IO               | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD22/CLK4/BRGO9/UCC2_CLKO      | A7                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD23/CLK3/BRGO10/UCC3_CLKO     | B7                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD24/CLK10/BRGO2/UCC4_CLKO     | A12                                                                                                                                                                                                                                                                              | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD25/CLK13/BRGO16/UCC5_CLKO    | B10                                                                                                                                                                                                                                                                              | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD26/CLK2/BRGO4/UCC1_CLKO      | E4                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD27/CLK1/BRGO3                | F4                                                                                                                                                                                                                                                                               | IO               | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD28/CLK19/BRGO11              | D15                                                                                                                                                                                                                                                                              | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD29/CLK15/BRGO8               | C6                                                                                                                                                                                                                                                                               | IO               | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD30/CLK14                     | D6                                                                                                                                                                                                                                                                               | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| GPIO_PD31/CLK7/BRGO15               | E24                                                                                                                                                                                                                                                                              | Ю                | OV <sub>DD</sub> | —     |  |  |  |  |

| Power                               | and Ground Supplies                                                                                                                                                                                                                                                              |                  | I                | I     |  |  |  |  |

| GV <sub>DD</sub>                    | AA8, AA10, AA11, AA13,<br>AA14, AA16, AA17, AA19,<br>AA21, AB9, AB10, AB11,<br>AB12, AB14, AB18, AB20,<br>AB21, AC6, AC8, AC14, AC18                                                                                                                                             | GV <sub>DD</sub> |                  | _     |  |  |  |  |

| OV <sub>DD</sub>                    | E5, E6, E8, E9, E10, E12, E14,<br>E15, E16, E18, E19, E20, E22,<br>F5, F6, F8, F10, F14, F16, F19,<br>F22, G22, H5, H6, H21, J5,<br>J22, K21, K22, L5, L6, L22, M5,<br>M22, N5, N21, N22, P6, P22,<br>P23, R5, R23, T5, T21, T22,<br>U6, U22, V5, V22, W22, Y5,<br>AB5, AB6, AC5 | OV <sub>DD</sub> | _                | _     |  |  |  |  |

### Table 55. MPC8323E PBGA Pinout Listing (continued)

### MPC8323E PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 4

| Signal          | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin Type        | Power<br>Supply | Notes |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-------|

| V <sub>DD</sub> | K10, K11, K12, K13, K14, K15,<br>K16, K17, L10, L17, M10, M17,<br>N10, N17, P10, P17, R10, R17,<br>T10, T17, U10, U11, U12, U13,<br>U14, U15, U16, U17                                                                                                                                                                                                                                                                                     | V <sub>DD</sub> | _               | _     |

| V <sub>SS</sub> | B23, E7, E11, E13, E17, E21,<br>F11, F13, F17, F21, F23, G5,<br>H22, K5, K6, L11, L12, L13,<br>L14, L15, L16, L21, M11, M12,<br>M13, M14, M15, M16, N6, N11,<br>N12, N13, N14, N15, N16, P5,<br>P11, P12, P13, P14, P15, P16,<br>P21, R11, R12, R13, R14, R15,<br>R16, R22, T6, T11, T12, T13,<br>T14, T15, T16, U5, U21, V23,<br>W5, W6, W21, W23, W24, Y22,<br>AA5, AA6, AA22, AA25, AB7,<br>AB13, AB19, AB22, AC10,<br>AC12, AC16, AC20 | V <sub>SS</sub> | _               | _     |

|                 | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                 |       |

| NC              | C22                                                                                                                                                                                                                                                                                                                                                                                                                                        | _               | —               | —     |

#### Table 55. MPC8323E PBGA Pinout Listing (continued)

#### Notes:

1. This pin is an open drain signal. A weak pull-up resistor (1 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

2. This pin is an open drain signal. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

3. This output is actively driven during reset rather than being three-stated during reset.

4. These JTAG and local bus pins have weak internal pull-up P-FETs that are always enabled.

5. This pin should have a weak pull up if the chip is in PCI host mode. Follow the PCI specification's recommendation.

6. This pin must always be tied to GND. 7. This pin has weak internal pull-down N-FET that is always enabled.8. Though this pin has weak internal pull-up yet it is recommended to apply an external pull-up.

### 22.1 Clocking in PCI Host Mode

When the MPC8323E is configured as a PCI host device (RCWH[PCIHOST] = 1), CLKIN is its primary input clock. CLKIN feeds the PCI clock divider ( $\div$ 2) and the PCI\_SYNC\_OUT and PCI\_CLK\_OUT multiplexors. The CFG\_CLKIN\_DIV configuration input selects whether CLKIN or CLKIN/2 is driven out on the PCI\_SYNC\_OUT signal.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system.

### 22.1.1 PCI Clock Outputs (PCI\_CLK\_OUT[0:2])

When the MPC8323E is configured as a PCI host, it provides three separate clock output signals, PCI\_CLK\_OUT[0:2], for external PCI agents.

When the device comes out of reset, the PCI clock outputs are disabled and are actively driven to a steady low state. Each of the individual clock outputs can be enabled (enable toggling of the clock) by setting its corresponding OCCR[PCICOEn] bit. All output clocks are phase-aligned to each other.

### 22.2 Clocking in PCI Agent Mode

When the MPC8323E is configured as a PCI agent device, PCI\_CLK is the primary input clock. In agent mode, the CLKIN signal should be tied to GND, and the clock output signals, PCI\_CLK\_OUT*n* and PCI\_SYNC\_OUT, are not used.

### 22.3 System Clock Domains

As shown in Figure 43, the primary clock input (frequency) is multiplied up by the system phase-locked loop (PLL) and the clock unit to create three major clock domains:

- The coherent system bus clock (*csb\_clk*)

- The QUICC Engine clock (*ce\_clk*)

- The internal clock for the DDR controller (*ddr\_clk*)

- The internal clock for the local bus controller (*lb\_clk*)

The *csb\_clk* frequency is derived from a complex set of factors that can be simplified into the following equation:

$csb_clk = [PCI_SYNC_IN \times (1 + \sim \overline{CFG_CLKIN_DIV})] \times SPMF$

In PCI host mode, PCI\_SYNC\_IN  $\times$  (1 +  $\sim \overline{CFG}_{CLKIN}_{DIV}$ ) is the CLKIN frequency.

The *csb\_clk* serves as the clock input to the e300c2 core. A second PLL inside the core multiplies up the *csb\_clk* frequency to create the internal clock for the core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL) which is loaded at power-on reset or by one of the hard-coded reset options. See the "Reset Configuration" section in the *MPC8323E PowerQUICC II Pro Communications Processor Reference Manual* for more information.

| Characteristic <sup>1</sup>                        | Max Operating Frequency | Unit |

|----------------------------------------------------|-------------------------|------|

| DDR1/DDR2 memory bus frequency (MCLK) <sup>2</sup> | 133                     | MHz  |

| Local bus frequency (LCLKn) <sup>3</sup>           | 66                      | MHz  |

| PCI input frequency (CLKIN or PCI_CLK)             | 66                      | MHz  |

#### Table 57. Operating Frequencies for PBGA (continued)

<sup>1</sup> The CLKIN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen such that the resulting *csb\_clk*, MCLK, LCLK[0:2], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies.

<sup>2</sup> The DDR1/DDR2 data rate is 2× the DDR1/DDR2 memory bus frequency.

<sup>3</sup> The local bus frequency is 1/2, 1/4, or 1/8 of the *lb\_clk* frequency (depending on LCRR[CLKDIV]) which is in turn 1× or 2× the *csb\_clk* frequency (depending on RCWL[LBCM]).

### 22.4 System PLL Configuration

The system PLL is controlled by the RCWL[SPMF] parameter. Table 58 shows the multiplication factor encodings for the system PLL.

#### NOTE

System PLL VCO frequency =  $2 \times (CSB \text{ frequency}) \times (System PLL VCO divider})$ .

The VCO divider needs to be set properly so that the System PLL VCO frequency is in the range of 300–600 MHz.

| RCWL[SPMF] | System PLL<br>Multiplication Factor |  |

|------------|-------------------------------------|--|

| 0000       | Reserved                            |  |

| 0001       | Reserved                            |  |

| 0010       | × 2                                 |  |

| 0011       | × 3                                 |  |

| 0100       | × 4                                 |  |

| 0101       | × 5                                 |  |

| 0110       | × 6                                 |  |

| 0111–1111  | Reserved                            |  |

### Table 58. System PLL Multiplication Factors

As described in Section 22, "Clocking," the LBCM, DDRCM, and SPMF parameters in the reset configuration word low and the CFG\_CLKIN\_DIV configuration input signal select the ratio between the primary clock input (CLKIN or PCI\_CLK) and the internal coherent system bus clock (*csb\_clk*). Table 59

#### Clocking

shows the expected frequency values for the CSB frequency for select *csb\_clk* to CLKIN/PCI\_SYNC\_IN ratios.

|                                          | <i>csb_clk</i> :<br>SPMF Input Clock | Input Clo          | Input Clock Frequency (MHz) <sup>2</sup> |                                |       |  |

|------------------------------------------|--------------------------------------|--------------------|------------------------------------------|--------------------------------|-------|--|

| CFG_CLKIN_DIV_B<br>at Reset <sup>1</sup> |                                      | Input Clock        | 25                                       | 33.33                          | 66.67 |  |

|                                          |                                      | Ratio <sup>2</sup> | csb_cl                                   | <i>csb_clk</i> Frequency (MHz) |       |  |

| High                                     | 0010                                 | 2 : 1              |                                          |                                | 133   |  |

| High                                     | 0011                                 | 3 : 1              |                                          | 100                            |       |  |

| High                                     | 0100                                 | 4 : 1              | 100                                      | 133                            |       |  |

| High                                     | 0101                                 | 5 : 1              | 125                                      |                                |       |  |

| High                                     | 0110                                 | 6 : 1              |                                          |                                |       |  |

| High                                     | 0111                                 | 7:1                |                                          |                                |       |  |

| High                                     | 1000                                 | 8 : 1              |                                          |                                |       |  |

| High                                     | 1001                                 | 9:1                |                                          |                                |       |  |

| High                                     | 1010                                 | 10 : 1             | -                                        |                                |       |  |

| High                                     | 1011                                 | 11:1               | -                                        |                                |       |  |

| High                                     | 1100                                 | 12 : 1             | -                                        |                                |       |  |

| High                                     | 1101                                 | 13 : 1             | -                                        |                                |       |  |

| High                                     | 1110                                 | 14 : 1             | -                                        |                                |       |  |

| High                                     | 1111                                 | 15 : 1             | -                                        |                                |       |  |

| High                                     | 0000                                 | 16 : 1             | -                                        |                                |       |  |

| Low                                      | 0010                                 | 2:1                |                                          |                                | 133   |  |

| Low                                      | 0011                                 | 3 : 1              | -                                        | 100                            |       |  |

| Low                                      | 0100                                 | 4 : 1              | -                                        | 133                            |       |  |

| Low                                      | 0101                                 | 5 : 1              | -                                        |                                |       |  |

| Low                                      | 0110                                 | 6 : 1              | -                                        |                                |       |  |

| Low                                      | 0111                                 | 7:1                | -                                        |                                |       |  |

| Low                                      | 1000                                 | 8 : 1              | -                                        |                                |       |  |

| Low                                      | 1001                                 | 9:1                | -                                        |                                |       |  |

| Low                                      | 1010                                 | 10 : 1             | -                                        |                                |       |  |

| Low                                      | 1011                                 | 11 : 1             |                                          |                                |       |  |

| Low                                      | 1100                                 | 12 : 1             |                                          |                                |       |  |

| Low                                      | 1101                                 | 13 : 1             |                                          |                                |       |  |

| Low                                      | 1110                                 | 14 : 1             |                                          |                                |       |  |

| Low                                      | 1111                                 | 15 : 1             |                                          |                                |       |  |

| Low                                      | 0000                                 | 16 : 1             |                                          |                                |       |  |

### Table 59. CSB Frequency Options

<sup>1</sup> CFG\_CLKIN\_DIV\_B is only used for host mode; CLKIN must be tied low and

CFG\_CLKIN\_DIV\_B must be pulled up (high) in agent mode.

<sup>2</sup> CLKIN is the input clock in host mode; PCI\_CLK is the input clock in agent mode.

Document Revision History

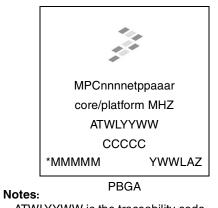

### 25.2 Part Marking

Parts are marked as in the example shown in Figure 46.

ATWLYYWW is the traceability code. CCCCC is the country code. MMMMM is the mask number. YWWLAZ is the assembly traceability code.

Figure 46. Freescale Part Marking for PBGA Devices

## 26 Document Revision History

Table 67 provides a revision history for this hardware specification.

### Table 67. Document Revision History

| Rev.<br>No. | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4           | 09/2010 | <ul> <li>Replaced all instances of "LCCR" with "LCRR" throughout.</li> <li>Added footnotes 3 and 4 in Table 2, "Recommended Operating Conditions<sup>3</sup>."</li> <li>Modified Section 8.1.1, "DC Electrical Characteristics."</li> <li>Modified Table 23, "MII Transmit AC Timing Specifications."</li> <li>Modified Table 24, "MII Receive AC Timing Specifications."</li> <li>Added footnote 7 and 8, and modified some signal names in Table 55, "MPC8323E PBGA Pinout Listing."</li> </ul>                                                                                                                                                                                                                                                                          |

| 3           | 12/2009 | <ul> <li>Removed references for note 4 from Table 1.</li> <li>Added Figure 2 in Section 2.1.2, "Power Supply Voltage Specification.</li> <li>Added symbol T<sub>A</sub> in Table 2.</li> <li>Added footnote 2 in Table 2.</li> <li>Added a note in Section 4, "Clock Input Timing for rise/fall time of QE input pins.</li> <li>Modified CLKIN, PCI_CLK rise/fall time parameters in Table 8. Modified min value of t<sub>MCK</sub> in Table 19.</li> <li>Modified Figure 43.</li> <li>Modified formula for ce_clk calculation in Section 22.3, "System Clock Domains.</li> <li>Added a note in Section 22.4, "System PLL Configuration.</li> <li>Removed the signal ECID_TMODE_IN from Table 55.</li> <li>Removed all references of RST signals from Table 55.</li> </ul> |