Welcome to E-XFL.COM

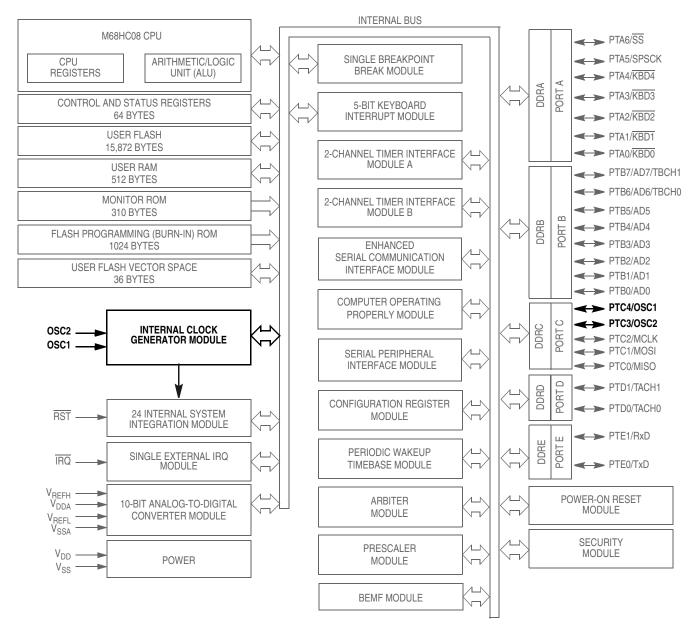

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2012.1.2                   |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | LINbus, SCI, SPI                                           |

| Peripherals                | POR, PWM                                                   |

| Number of I/O              | 24                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 512 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 32-LQFP                                                    |

| Supplier Device Package    | 32-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908ey16mfae |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Memory

| Addr.                                       | Register Name                                    |                 | Bit 7                     | 6      | 5      | 4           | 3               | 2        | 1     | Bit 0                                        |

|---------------------------------------------|--------------------------------------------------|-----------------|---------------------------|--------|--------|-------------|-----------------|----------|-------|----------------------------------------------|

| \$0023                                      | Timer A Counter Modulo<br>Register High (TAMODH) | Read:<br>Write: | BIT 15                    | BIT 14 | BIT 13 | BIT 12      | BIT 11          | BIT 10   | BIT 9 | BIT 8                                        |

|                                             | See page 203.                                    | Reset:          | 1                         | 1      | 1      | 1           | 1               | 1        | 1     | 1                                            |

| \$0024                                      | Timer A Counter Modulo<br>Register Low (TAMODL)  | Read:<br>Write: | BIT 7                     | BIT 6  | BIT 5  | BIT 4       | BIT 3           | BIT 2    | BIT 1 | BIT 0                                        |

|                                             | See page 203.                                    | Reset:          | 1                         | 1      | 1      | 1           | 1               | 1        | 1     | 1                                            |

|                                             | Timer A Channel 0 Status                         | Read:           | CH0F                      | CH0IE  | MS0B   | MS0A        | ELS0B           | ELS0A    | TOV0  | CH0MAX                                       |

| \$0025                                      | and Control Register<br>(TASC0)                  | Write:          | 0                         | ONIOL  | WOOD   | WOON        | LLOOD           | LLOUN    | 1000  |                                              |

|                                             | See page 204.                                    | Reset:          | 0                         | 0      | 0      | 0           | 0               | 0        | 0     | 0                                            |

| \$0026                                      | Timer A Channel 0<br>Register High (TACH0H)      | Read:<br>Write: | BIT 15                    | BIT 14 | BIT 13 | BIT 12      | BIT 11          | BIT 10   | BIT 9 | BIT 8                                        |

|                                             | See page 207.                                    | Reset:          |                           | •      | •      | Indetermina | te after reset  |          |       | <u>.                                    </u> |

| \$0027                                      | Timer A Channel 0<br>Register Low (TACH0L)       | Read:<br>Write: | BIT 7                     | BIT 6  | BIT 5  | BIT 4       | BIT 3           | BIT 2    | BIT 1 | BIT 0                                        |

|                                             | See page 207.                                    | Reset:          |                           |        |        | Indetermina | ite after reset |          |       |                                              |

|                                             | Timer A Channel 1 Status                         | Read:           | CH1F                      | CH1IE  | 0      | MS1A        | ELS1B           | ELS1A    | TOV1  | CH1MAX                                       |

| \$0028                                      | \$0028 and Control Register<br>(TASC1)           | Write:          | 0                         | OTTIL  | R      | Mont        | LLOID           | LLOW     | 1011  | OTTIME OT                                    |

|                                             | See page 207.                                    | Reset:          | 0                         | 0      | 0      | 0           | 0               | 0        | 0     | 0                                            |

| \$0029                                      | Timer A Channel 1<br>Register High (TACH1H)      | Read:<br>Write: | BIT 15                    | BIT 14 | BIT 13 | BIT 12      | BIT 11          | BIT 10   | BIT 9 | BIT 8                                        |

|                                             | See page 207.                                    | Reset:          |                           |        |        | Indetermina | ite after reset |          |       |                                              |

| \$002A                                      | <b>č</b>                                         |                 | BIT 7                     | BIT 6  | BIT 5  | BIT 4       | BIT 3           | BIT 2    | BIT 1 | BIT 0                                        |

|                                             | See page 207.                                    | Reset:          | Indeterminate after reset |        |        |             |                 |          |       |                                              |

|                                             | Timer B Status and Control                       | Read:           | TOF                       | TOIE   | TSTOP  | 0           | R               | PS2      | PS1   | PS0                                          |

| \$002B                                      | Register (TBSC)                                  | Write:          | 0                         | TOIL   | 10101  | TRST        |                 | 102      | 101   | 100                                          |

|                                             | See page 217.                                    | Reset:          | 0                         | 0      | 1      | 0           | 0               | 0        | 0     | 0                                            |

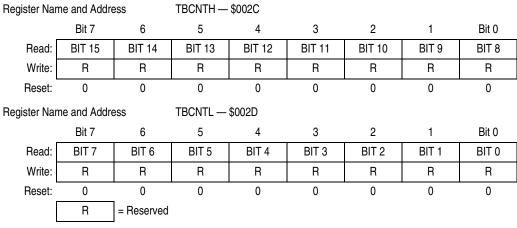

|                                             | Timer B Counter Register                         | Read:           | BIT 15                    | BIT 14 | BIT 13 | BIT 12      | BIT 11          | BIT 10   | BIT 9 | BIT 8                                        |

| \$002C                                      | High (TBCNTH)<br>See page 219.                   | Write:          |                           |        |        |             |                 |          |       |                                              |

|                                             | 0ee page 219.                                    | Reset:          | 0                         | 0      | 0      | 0           | 0               | 0        | 0     | 0                                            |

|                                             | Timer B Counter Register                         | Read:           | BIT 7                     | BIT 6  | BIT 5  | BIT 4       | BIT 3           | BIT 2    | BIT 1 | BIT 0                                        |

| \$002D                                      | Low (TBCNTL)<br>See page 219.                    | Write:          |                           | _      | _      | _           |                 |          | _     |                                              |

|                                             | 000 page 210.                                    | Reset:          | 0                         | 0      | 0      | 0           | 0               | 0        | 0     | 0                                            |

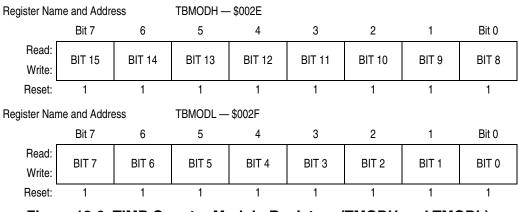

| \$002E                                      | Timer B Counter Modulo<br>Register High (TBMODH) | Read:<br>Write: | BIT 15                    | BIT 14 | BIT 13 | BIT 12      | BIT 11          | BIT 10   | BIT 9 | BIT 8                                        |

|                                             | See page 219.                                    | Reset:          | 1                         | 1      | 1      | 1           | 1               | 1        | 1     | 1                                            |

| = Unimplemented R = Reserved U = Unaffected |                                                  |                 |                           |        |        |             |                 | affected |       |                                              |

## Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 7)

#### Input/Output (I/O) Section

| Addr.  | Register Name                                   |                 | Bit 7                        | 6                         | 5      | 4           | 3               | 2      | 1        | Bit 0    |  |  |  |

|--------|-------------------------------------------------|-----------------|------------------------------|---------------------------|--------|-------------|-----------------|--------|----------|----------|--|--|--|

| \$002F | Timer B Counter Modulo<br>Register Low (TBMODL) | Read:<br>Write: | BIT 7                        | BIT 6                     | BIT 5  | BIT 4       | BIT 3           | BIT 2  | BIT 1    | BIT 0    |  |  |  |

|        | See page 219.                                   | Reset:          | 1                            | 1                         | 1      | 1           | 1               | 1      | 1        | 1        |  |  |  |

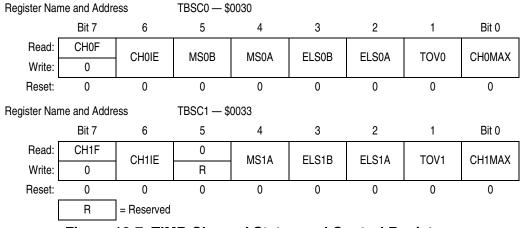

|        | Timer B Channel 0 Status                        | Read:           | CH0F                         |                           | MS0B   | MOOA        |                 |        |          | CHOMAX   |  |  |  |

| \$0030 | 0030 and Control Register<br>(TBSC0)            |                 | 0                            | 0 CHOIE                   |        | MS0A        | ELS0B           | ELS0A  | TOV0     | CH0MAX   |  |  |  |

|        | See page 220.                                   | Reset:          | 0                            | 0                         | 0      | 0           | 0               | 0      | 0        | 0        |  |  |  |

| \$0031 | Timer B Channel 0<br>Register High (TBCH0H)     | Read:<br>Write: | BIT 15                       | BIT 14                    | BIT 13 | BIT 12      | BIT 11          | BIT 10 | BIT 9    | BIT 8    |  |  |  |

|        | See page 223.                                   | Reset:          |                              |                           |        | Indetermina | ate after reset |        |          |          |  |  |  |

| \$0032 | Timer B Channel 0<br>Register Low (TBCH0L)      | Read:<br>Write: | BIT 7                        | BIT 6                     | BIT 5  | BIT 4       | BIT 3           | BIT 2  | BIT 1    | BIT 0    |  |  |  |

|        | See page 223.                                   | Reset:          |                              | •                         | •      | Indetermina | ate after reset |        |          |          |  |  |  |

|        | Timer B Channel 1 Status                        | Read:           | CH1F                         | CH1IE                     | 0      | - MS1A      | ELS1B           | ELS1A  | TOV1     | CH1MAX   |  |  |  |

| \$0033 | and Control Register<br>(TBSC1)                 | Write:          | 0                            | Onne                      | R      | MOTA        | LLOID           | LLOIA  | 1001     | CITIVIAX |  |  |  |

|        | See page 220.                                   | Reset:          | 0                            | 0                         | 0      | 0           | 0               | 0      | 0        | 0        |  |  |  |

| \$0034 | Timer B Channel 1<br>Register High (TBCH1H)     | Read:<br>Write: | BIT 15                       | BIT 14                    | BIT 13 | BIT 12      | BIT 11          | BIT 10 | BIT 9    | BIT 8    |  |  |  |

|        | See page 223.                                   | Reset:          |                              | Indeterminate after reset |        |             |                 |        |          |          |  |  |  |

| \$0035 | Timer B Channel 1<br>Register Low (TBCH1L)      | Read:<br>Write: | BIT 7                        | BIT 6                     | BIT 5  | BIT 4       | BIT 3           | BIT 2  | BIT 1    | BIT 0    |  |  |  |

|        | See page 223.                                   | Reset:          |                              | Indeterminate after reset |        |             |                 |        |          |          |  |  |  |

| \$0036 | ICG Control Register<br>(ICGCR)                 | Read:<br>Write: | CMIE                         | CMF<br>0                  | CMON   | CS          | ICGON           | ICGS   | ECGON    | ECGS     |  |  |  |

|        | See page 97.                                    | Reset:          | 0                            | 0                         | 0      | 0           | 1               | 0      | 0        | 0        |  |  |  |

| \$0037 | ICG Multiplier Register<br>(ICGMR)              | Read:<br>Write: |                              | N6                        | N5     | N4          | N3              | N2     | N1       | NO       |  |  |  |

|        | See page 98.                                    | Reset:          | 0                            | 0                         | 0      | 1           | 0               | 1      | 0        | 1        |  |  |  |

| \$0038 | ICG Trim Register (ICGTR)<br>See page 99.       | Read:<br>Write: | TRIM7                        | TRIM6                     | TRIM5  | TRIM4       | TRIM3           | TRIM2  | TRIM1    | TRIM0    |  |  |  |

|        | Oee page 55.                                    | Reset:          | 1                            | 0                         | 0      | 0           | 0               | 0      | 0        | 0        |  |  |  |

|        | ICG Divider Control                             | Read:           |                              |                           |        |             | DDIV3           | DDIV2  | DDIV1    | DDIV0    |  |  |  |

| \$0039 | Register (ICGDVR)                               | Write:          |                              |                           |        |             |                 |        |          |          |  |  |  |

|        | See page 99.                                    | Reset:          | 0                            | 0                         | 0      | 0           | U               | U      | U        | U        |  |  |  |

|        | ICG DCO Stage Control                           | Read:           | DSTG7                        | DSTG6                     | DSTG5  | DSTG4       | DDSTG3          | DSTG2  | DSTG1    | DSTG0    |  |  |  |

| \$003A | Register (ICGDSR)                               | Write:          | R                            | R                         | R      | R           | R               | R      | R        | R        |  |  |  |

|        | See page 100.                                   | Reset:          | U                            | U                         | U      | U           | U               | U      | U        | U        |  |  |  |

|        |                                                 |                 | = Unimplemented R = Reserved |                           |        |             |                 | U = Un | affected |          |  |  |  |

## Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 7)

### 3.6.6.1 V<sub>REFH</sub> and V<sub>REFL</sub>

Both ac and dc current are drawn through the  $V_{REFH}$  and  $V_{REFL}$  loop. The AC current is in the form of current spikes required to supply charge to the capacitor array at each successive approximation step. The current flows through the internal resistor string. The best external component to meet both these current demands is a capacitor in the 0.01  $\mu$ F to 1  $\mu$ F range with good high frequency characteristics. This capacitor is connected between  $V_{REFH}$  and  $V_{REFL}$  and must be placed as close as possible to the package pins. Resistance in the path is not recommended because the dc current will cause a voltage drop which could result in conversion errors.

### 3.6.6.2 ANx

Empirical data shows that capacitors from the analog inputs to  $V_{REFL}$  improve ADC performance. 0.01- $\mu$ F and 0.1- $\mu$ F capacitors with good high-frequency characteristics are sufficient. These capacitors must be placed as close as possible to the package pins.

### 3.6.6.3 Grounding

In cases where separate power supplies are used for analog and digital power, the ground connection between these supplies should be at the V<sub>SSA</sub> pin. This should be the only ground connection between these supplies if possible. The V<sub>SSA</sub> pin makes a good single point ground location. Connect the V<sub>REFL</sub> pin to the same potential as V<sub>SSA</sub> at the single point ground location.

## 3.7 I/O Registers

These I/O registers control and monitor operation of the ADC:

- ADC status and control register, ADSCR

- ADC data registers, ADRH and ARDL

- ADC clock register, ADCLK

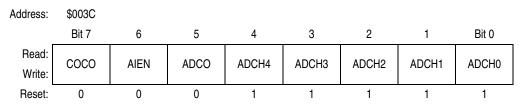

## 3.7.1 ADC Status and Control Register

This section describes the function of the ADC status and control register (ADSCR). Writing ADSCR aborts the current conversion and initiates a new conversion.

Figure 3-4. ADC Status and Control Register (ADSCR)

#### COCO — Conversions Complete Bit

When AIEN bit is 0, the COCO is a read-only bit which is set each time a conversion is completed except in the continuous conversion mode where it is set after the first conversion. This bit is cleared whenever the ADC status and control register is written or whenever the ADC data register is read.

If AIEN bit is 1, the COCO is a read/write bit. Reset clears this bit.

1 = Conversion completed (AIEN = 0)

0 = Conversion not completed (AIEN = 0)/CPU interrupt (AIEN = 1)

#### Analog-to-Digital Converter (ADC) Module

#### AIEN — ADC Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when the data register is read or the status/control register is written. Reset clears the AIEN bit.

- 1 = ADC interrupt enabled

- 0 = ADC interrupt disabled

#### ADCO — ADC Continuous Conversion Bit

When set, the ADC will convert samples continuously and update the ADR register at the end of each conversion. Only one conversion is allowed when this bit is cleared. Reset clears the ADCO bit.

1 = Continuous ADC conversion

0 = One ADC conversion

#### ADCH[4:0] — ADC Channel Select Bits

ADCH4, ADCH3, ADCH2, ADCH1, and ADCH0 form a 5-bit field which is used to select one of 8 ADC channels. The ADC channels are detailed in Table 3-1.

#### NOTE

Take care to prevent switching noise from corrupting the analog signal when simultaneously using a port pin as both an analog and digital input.

The ADC subsystem is turned off when the channel select bits are all set to 1. This feature allows for reduced power consumption for the MCU when the ADC is not used.

#### NOTE

Recovery from the disabled state requires one conversion cycle to stabilize.

The voltage levels supplied from internal reference nodes as specified in Table 3-1 are used to verify the operation of the ADC both in production test and for user applications.

| ADCH4 | ADCH3 | ADCH2 | ADCH1 | ADCH0 | Input Select      |

|-------|-------|-------|-------|-------|-------------------|

| 0     | 0     | 0     | 0     | 0     | PTB0              |

| 0     | 0     | 0     | 0     | 1     | PTB1              |

| 0     | 0     | 0     | 1     | 0     | PTB2              |

| 0     | 0     | 0     | 1     | 1     | PTB3              |

| 0     | 0     | 1     | 0     | 0     | PTB4              |

| 0     | 0     | 1     | 0     | 1     | PTB5              |

| 0     | 0     | 1     | 1     | 0     | PTB6              |

| 0     | 0     | 1     | 1     | 1     | PTB7              |

| 0     | 1     | 0     | 0     | 0     |                   |

|       |       | to    |       |       | Unused *          |

| 1     | 1     | 0     | 1     | 0     |                   |

| 1     | 1     | 0     | 1     | 1     | Reserved **       |

| 1     | 1     | 1     | 0     | 0     | Unused *          |

| 1     | 1     | 1     | 0     | 1     | V <sub>REFH</sub> |

| 1     | 1     | 1     | 1     | 0     | V <sub>REFL</sub> |

| 1     | 1     | 1     | 1     | 1     | ADC power off     |

#### Table 3-1. Mux Channel Select

\* If any unused channels are selected, the resulting ADC conversion will be unknown.

\*\* Used for factory testing.

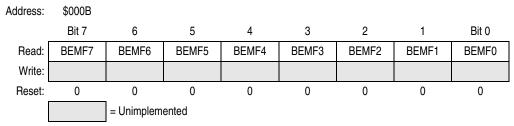

# Chapter 4 BEMF Counter Module (BEMF)

## 4.1 Introduction

This section describes the BEMF module. The BEMF counter integrates over time, while the PTD0/TACH0 pin is active. This function is useful for measuring recirculation currents in motors occurring on switching of inductive loads.

BEMF is the abbreviation for Back ElectroMagnetic Force.

## 4.2 Functional Description

The 8-bit BEMF counter runs at the internal bus frequency divided by 64. Whenever PTD0/TACH0 is a logic 1, the counter increments by 1 with each period.

## 4.3 **BEMF Register**

The BEMF register contains the eight read-only bits of the BEMF counter, showing its actual value. A read access to the BEMF register resets all counter bits to 0.

## 4.4 Input Signal

Port D shares the PTD0/TACH0 pin with the BEMF module. To measure an external signal with the BEMF module, PTD0/TACH0 must be configured as an input (DDRD0 = 0).

## 4.5 Low Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 4.5.1 Wait Mode

The BEMF module remains active after execution of the WAIT instruction. In WAIT mode the BEMF register is not accessible by the CPU.

### Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

## C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

1 = Carry out of bit 7

0 = No carry out of bit 7

## 7.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (document order number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about the architecture of the CPU.

## 7.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 7.5.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

## 7.5.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

## 7.6 CPU During Break Interrupts

If a break module is present on the MCU, the CPU starts a break interrupt by:

- · Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD or with \$FEFC:\$FEFD in monitor mode

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the MCU to normal operation if the break interrupt has been deasserted.

| Source                                                                                                | Operation                                         | Description                                                                                                                                                                                                                                                                                                                                   |   |   | Effect<br>on CCR |   |   |   | Address<br>Mode                                                                                          | Opcode                                           | Operand                                                              | les                                       |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------------------|---|---|---|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------|

| Form                                                                                                  | ·                                                 | •                                                                                                                                                                                                                                                                                                                                             | v | н | I                | Ν | z | С | Add                                                                                                      | Opc                                              | Ope                                                                  | Cycles                                    |

| BHS rel                                                                                               | Branch if Higher or Same<br>(Same as BCC)         | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 0$                                                                                                                                                                                                                                                                                             | - | - | I                | I | _ | - | REL                                                                                                      | 24                                               | rr                                                                   | 3                                         |

| BIH rel                                                                                               | Branch if IRQ Pin High                            | $PC \leftarrow (PC) + 2 + rel? \overline{IRQ} = 1$                                                                                                                                                                                                                                                                                            | - | - | -                | - | - | - | REL                                                                                                      | 2F                                               | rr                                                                   | 3                                         |

| BIL rel                                                                                               | Branch if IRQ Pin Low                             | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 0$                                                                                                                                                                                                                                                                                           | - | - | -                | - | - | - | REL                                                                                                      | 2E                                               | rr                                                                   | 3                                         |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT,X<br>BIT opr,SP<br>BIT opr,SP         | Bit Test                                          | (A) & (M)                                                                                                                                                                                                                                                                                                                                     | 0 | _ |                  | ţ | ţ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9ED5<br>9ED5 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff                            | 23443245                                  |

| BLE opr                                                                                               | Branch if Less Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 1$                                                                                                                                                                                                                                                                           | 1 | 1 | I                | I | I | - | REL                                                                                                      | 93                                               | rr                                                                   | 3                                         |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                     | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                                                                                                                                                                                                                                                                                             | - | — | I                | I | - | - | REL                                                                                                      | 25                                               | rr                                                                   | 3                                         |

| BLS rel                                                                                               | Branch if Lower or Same                           | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                    | _ | - | _                | - | - | - | REL                                                                                                      | 23                                               | rr                                                                   | 3                                         |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                    | - | - | -                | - | - | - | REL                                                                                                      | 91                                               | rr                                                                   | 3                                         |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                    | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                       | _ | _ | -                | - | _ | - | REL                                                                                                      | 2C                                               | rr                                                                   | 3                                         |

| BMI rel                                                                                               | Branch if Minus                                   | $PC \leftarrow (PC) + 2 + rel? (N) = 1$                                                                                                                                                                                                                                                                                                       | - | - | -                | - | - | - | REL                                                                                                      | 2B                                               | rr                                                                   | 3                                         |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                      | $PC \leftarrow (PC) + 2 + rel? (I) = 1$                                                                                                                                                                                                                                                                                                       | - | - | -                | - | - | - | REL                                                                                                      | 2D                                               | rr                                                                   | 3                                         |

| BNE rel                                                                                               | Branch if Not Equal                               | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                       | - | - | -                | - | - | - | REL                                                                                                      | 26                                               | rr                                                                   | 3                                         |

| BPL rel                                                                                               | Branch if Plus                                    | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                       | - | - | -                | - | - | - | REL                                                                                                      | 2A                                               | rr                                                                   | 3                                         |

| BRA rel                                                                                               | Branch Always                                     | $PC \leftarrow (PC) + 2 + rel$                                                                                                                                                                                                                                                                                                                | - | - | -                | - | - | - | REL                                                                                                      | 20                                               | rr                                                                   | 3                                         |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                 | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                         | _ | _ | _                | _ | _ | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555<br>55555555555555555555555555555 |

| BRN rel                                                                                               | Branch Never                                      | $PC \leftarrow (PC) + 2$                                                                                                                                                                                                                                                                                                                      | - | - | -                | - | - | - | REL                                                                                                      | 21                                               | rr                                                                   | 3                                         |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                   | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                         | _ | _ | _                | _ | _ | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5555555<br>555555555555555555555555555555 |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                             | Mn ← 1                                                                                                                                                                                                                                                                                                                                        | _ | _ | _                | _ | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                   | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |

| BSR rel                                                                                               | Branch to Subroutine                              | $\begin{array}{l} PC \leftarrow (PC) + 2;  push \; (PCL) \\ SP \leftarrow (SP) - 1;  push \; (PCH) \\ & SP \leftarrow (SP) - 1 \\ & PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                            | _ | _ | _                | _ | _ | _ | REL                                                                                                      | AD                                               | rr                                                                   | 4                                         |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                       | $\begin{array}{c} PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel ? (A) - (M) = \$00 \end{array}$ | _ | _ | _                | _ | _ | _ | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                                  | 31<br>41<br>51<br>61<br>71<br>9E61               | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                      | 5<br>4<br>4<br>5<br>4<br>6                |

| CLC                                                                                                   | Clear Carry Bit                                   | $C \leftarrow 0$                                                                                                                                                                                                                                                                                                                              | - | - | -                | - | - | 0 | INH                                                                                                      | 98                                               |                                                                      | 1                                         |

| CLI                                                                                                   | Clear Interrupt Mask                              | I ← 0                                                                                                                                                                                                                                                                                                                                         | - | - | 0                | - | - | - | INH                                                                                                      | 9A                                               |                                                                      | 2                                         |

## Table 7-1. Instruction Set Summary (Sheet 2 of 6)

#### Internal Clock Generator (ICG) Module

Figure 8-1. Block Diagram Highlighting ICG Block and Pins

#### Enhanced Serial Communications Interface (ESCI) Module

does not set the receiver idle bit, IDLE, or the ESCI receiver full bit, SCRF. The idle line type bit, ILTY, determines whether the receiver begins counting 1s as idle character bits after the start bit or after the stop bit.

### NOTE

With the WAKE bit clear, setting the RWU bit after the RxD pin has been idle will cause the receiver to wake up.

#### 13.4.3.7 Receiver Interrupts

These sources can generate CPU interrupt requests from the ESCI receiver:

- ESCI receiver full (SCRF) The SCRF bit in SCS1 indicates that the receive shift register has transferred a character to the SCDR. SCRF can generate a receiver CPU interrupt request. Setting the ESCI receive interrupt enable bit, SCRIE, in SCC2 enables the SCRF bit to generate receiver CPU interrupts.

- Idle input (IDLE) The IDLE bit in SCS1 indicates that 10 or 11 consecutive 1s shifted in from the RxD pin. The idle line interrupt enable bit, ILIE, in SCC2 enables the IDLE bit to generate CPU interrupt requests.

### 13.4.3.8 Error Interrupts

These receiver error flags in SCS1 can generate CPU interrupt requests:

- Receiver overrun (OR) The OR bit indicates that the receive shift register shifted in a new character before the previous character was read from the SCDR. The previous character remains in the SCDR, and the new character is lost. The overrun interrupt enable bit, ORIE, in SCC3 enables OR to generate ESCI error CPU interrupt requests.

- Noise flag (NF) The NF bit is set when the ESCI detects noise on incoming data or break characters, including start, data, and stop bits. The noise error interrupt enable bit, NEIE, in SCC3 enables NF to generate ESCI error CPU interrupt requests.

- Framing error (FE) The FE bit in SCS1 is set when a 0 occurs where the receiver expects a stop bit. The framing error interrupt enable bit, FEIE, in SCC3 enables FE to generate ESCI error CPU interrupt requests.

- Parity error (PE) The PE bit in SCS1 is set when the ESCI detects a parity error in incoming data. The parity error interrupt enable bit, PEIE, in SCC3 enables PE to generate ESCI error CPU interrupt requests.

## 13.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 13.5.1 Wait Mode

The ESCI module remains active in wait mode. Any enabled CPU interrupt request from the ESCI module can bring the MCU out of wait mode.

If ESCI module functions are not required during wait mode, reduce power consumption by disabling the module before executing the WAIT instruction.

### 13.5.2 Stop Mode

The ESCI module is inactive in stop mode. The STOP instruction does not affect ESCI register states. ESCI module operation resumes after the MCU exits stop mode.

#### Enhanced Serial Communications Interface (ESCI) Module

receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

### **OR** — Receiver Overrun Bit

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error CPU interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR. Reset clears the OR bit.

1 = Receive shift register full and SCRF = 1

0 = No receiver overrun

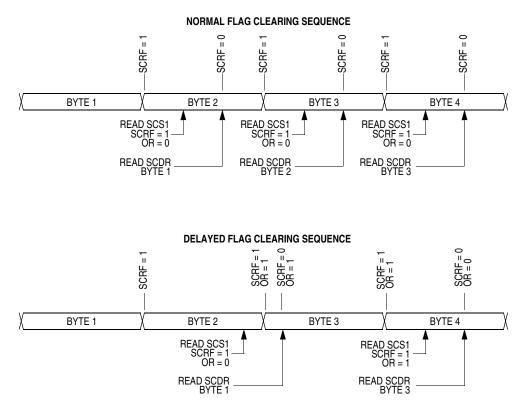

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 13-13 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

Figure 13-13. Flag Clearing Sequence

In applications that are subject to software latency or in which it is important to know which byte is lost due to an overrun, the flag-clearing routine can check the OR bit in a second read of SCS1 after reading the data register.

### 14.5.1 Interrupts

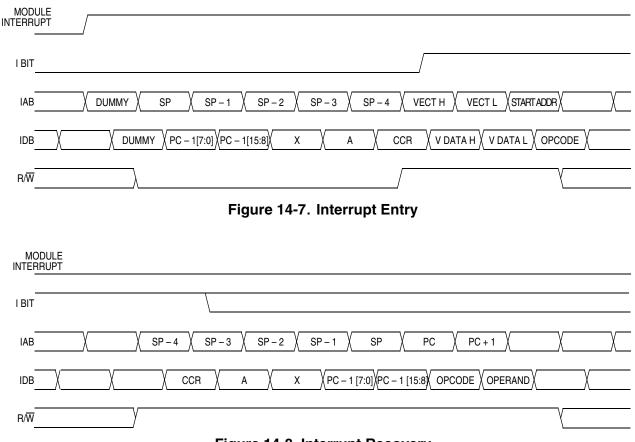

At the beginning of an interrupt, the CPU saves the CPU register contents on the stack and sets the interrupt mask (I bit) to prevent additional interrupts. At the end of an interrupt, the return-from-interrupt (RTI) instruction recovers the CPU register contents from the stack so that normal processing can resume. Figure 14-7 shows interrupt entry timing. Figure 14-8 shows interrupt recovery timing.

#### Figure 14-8. Interrupt Recovery

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. As shown in Figure 14-9, once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced or the I bit is cleared.

Serial Peripheral Interface (SPI) Module

## 15.10 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 15.10.1 Wait Mode

The SPI module remains active after the execution of a WAIT instruction. In wait mode, the SPI module registers are not accessible by the CPU. Any enabled CPU interrupt request from the SPI module can bring the MCU out of wait mode.

If SPI module functions are not required during wait mode, reduce power consumption by disabling the SPI module before executing the WAIT instruction.

To exit wait mode when an overflow condition occurs, enable the OVRF bit to generate CPU interrupt requests by setting the error interrupt enable bit (ERRIE). (See 15.7 Interrupts.)

### 15.10.2 Stop Mode

The SPI module is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions. SPI operation resumes after the MCU exits stop mode. If stop mode is exited by reset, any transfer in progress is aborted and the SPI is reset.

## 15.11 SPI During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR, \$FE03) enables software to clear status bits during the break state. (See 19.2.1.1 Flag Protection During Break Interrupts.)

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

Since the SPTE bit cannot be cleared during a break with the BCFE bit cleared, a write to the data register in break mode will not initiate a transmission nor will this data be transferred into the shift register. Therefore, a write to the SPDR in break mode with the BCFE bit cleared has no effect.

## 15.12 I/O Signals

The SPI module has four I/O pins and shares three of them with a parallel I/O port.

- MISO Data received

- MOSI Data transmitted

- SPSCK Serial clock

- SS Slave select

- V<sub>SS</sub> Clock ground

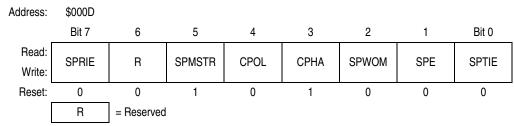

Figure 15-12. SPI Control Register (SPCR)

### SPRIE — SPI Receiver Interrupt Enable Bit

This read/write bit enables CPU interrupt requests generated by the SPRF bit. The SPRF bit is set when a byte transfers from the shift register to the receive data register. Reset clears the SPRIE bit.

1 = SPRF CPU interrupt requests enabled

0 = SPRF CPU interrupt requests disabled

#### SPMSTR — SPI Master Bit

This read/write bit selects master mode operation or slave mode operation. Reset sets the SPMSTR bit.

1 = Master mode

0 = Slave mode

#### **CPOL** — Clock Polarity Bit

This read/write bit determines the logic state of the SPSCK pin between transmissions. (See Figure 15-4 and Figure 15-5.) To transmit data between SPI modules, the SPI modules must have identical CPOL bits. Reset clears the CPOL bit.

#### **CPHA** — Clock Phase Bit

This read/write bit controls the timing relationship between the serial clock and SPI data. (See Figure 15-4 and Figure 15-5.) To transmit data between SPI modules, the SPI modules must have identical CPHA bits. When CPHA = 0, the  $\overline{SS}$  pin of the slave SPI module must be set to logic 1 between bytes. (See Figure 15-11). Reset sets the CPHA bit.

When CPHA = 0 for a slave, the falling edge of  $\overline{SS}$  indicates the beginning of the transmission. This causes the SPI to leave its idle state and begin driving the MISO pin with the MSB of its data. Once the transmission begins, no new data is allowed into the shift register from the data register. Therefore, the slave data register must be loaded with the desired transmit data before the falling edge of  $\overline{SS}$ . Any data written after the falling edge is stored in the data register and transferred to the shift register at the current transmission.

When CPHA = 1 for a slave, the first edge of the SPSCK indicates the beginning of the transmission. The same applies when  $\overline{SS}$  is high for a slave. The MISO pin is held in a high-impedance state, and the incoming SPSCK is ignored. In certain cases, it may also cause the MODF flag to be set. (See 15.6.2 Mode Fault Error). A logic 1 on the  $\overline{SS}$  pin does not in any way affect the state of the SPI state machine.

#### SPWOM — SPI Wired-OR Mode Bit

This read/write bit disables the pullup devices on pins SPSCK, MOSI, and MISO so that those pins become open-drain outputs.

1 = Wired-OR SPSCK, MOSI, and MISO pins

0 = Normal push-pull SPSCK, MOSI, and MISO pins

Serial Peripheral Interface (SPI) Module

#### SPR1 and SPR0 — SPI Baud Rate Select Bits

In master mode, these read/write bits select one of four baud rates as shown in Table 15-5. SPR1 and SPR0 have no effect in slave mode. Reset clears SPR1 and SPR0.

| SPR1:SPR0 | Baud Rate Divisor (BD) |

|-----------|------------------------|

| 00        | 2                      |

| 01        | 8                      |

| 10        | 32                     |

| 11        | 128                    |

#### Table 15-5. SPI Master Baud Rate Selection

Use this formula to calculate the SPI baud rate:

Baud rate =

$$\frac{CGMOUT}{2 \times BD}$$

where:

CGMOUT = base clock output of the internal clock generator module (ICG),

see Chapter 8 Internal Clock Generator (ICG) Module.

BD = baud rate divisor

## 15.13.3 SPI Data Register

The SPI data register is the read/write buffer for the receive data register and the transmit data register. Writing to the SPI data register writes data into the transmit data register. Reading the SPI data register reads data from the receive data register. The transmit data and receive data registers are separate buffers that can contain different values. See Figure 15-2

| Address: | \$000F                    |    |    |    |    |    |    |       |  |  |

|----------|---------------------------|----|----|----|----|----|----|-------|--|--|

|          | Bit 7                     | 6  | 5  | 4  | 3  | 2  | 1  | Bit 0 |  |  |

| Read:    | R7                        | R6 | R5 | R4 | R3 | R2 | R1 | R0    |  |  |

| Write:   | T7                        | T6 | T5 | T4 | Т3 | T2 | T1 | T0    |  |  |

| Reset:   | Indeterminate after Reset |    |    |    |    |    |    |       |  |  |

Reset:

### Figure 15-14. SPI Data Register (SPDR)

### R7–R0/T7–T0 — Receive/Transmit Data Bits

NOTE

Do not use read-modify-write instructions on the SPI data register since the buffer read is not the same as the buffer written.

#### Timebase Module (TBM)

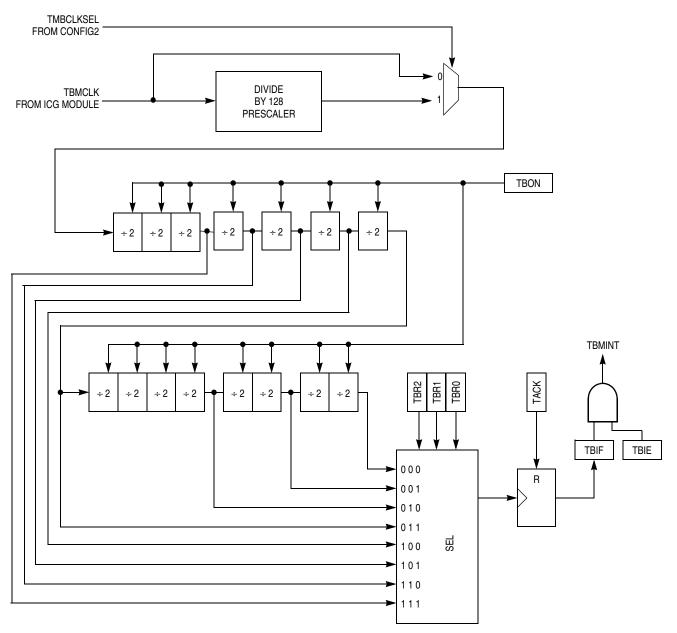

Figure 16-1. Timebase Block Diagram

## 16.4 Interrupts

The timebase module can periodically interrupt the CPU with a rate defined by the selected TBMCLK and the select bits TBR2–TBR0. When the timebase counter chain rolls over, the TBIF flag is set. If the TBIE bit is set, enabling the timebase interrupt, the counter chain overflow will generate a CPU interrupt request.

Interrupts must be acknowledged by writing a 1 to the TACK bit.

### **18.8.2 TIMB Counter Registers**

The two read-only TIMB counter registers contain the high and low bytes of the value in the TIMB counter. Reading the high byte (TBCNTH) latches the contents of the low byte (TBCNTL) into a buffer. Subsequent reads of TBCNTH do not affect the latched TBCNTL value until TBCNTL is read. Reset clears the TIMB counter registers. Setting the TIMB reset bit (TRST) also clears the TIMB counter registers.

#### NOTE

If TBCNTH is read during a break interrupt, be sure to unlatch TBCNTL by reading TBCNTL before exiting the break interrupt. Otherwise, TBCNTL retains the value latched during the break.

## 18.8.3 TIMB Counter Modulo Registers

The read/write TIMB modulo registers contain the modulo value for the TIMB counter. When the TIMB counter reaches the modulo value, the overflow flag (TOF) becomes set, and the TIMB counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIMB counter modulo registers.

Figure 18-6. TIMB Counter Modulo Registers (TMODH and TMODL)

**NOTE** Reset the TIMB counter before writing to the TIMB counter modulo registers.

Timer Interface B (TIMB) Module

## 18.8.4 TIMB Channel Status and Control Registers

Each of the TIMB channel status and control registers:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIMB overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIMB counter registers matches the value in the TIMB channel x registers.

When CHxIE = 1, clear CHxF by reading TIMB channel x status and control register with CHxF set, and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

## CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIMB CPU interrupts on channel x.

Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIMB channel 0.

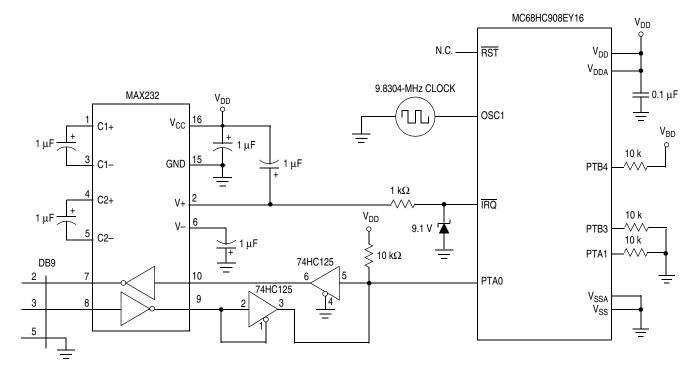

Figure 19-10. Forced Monitor Mode ( $\overline{IRQ} = V_{DD}$ )

**Development Support**

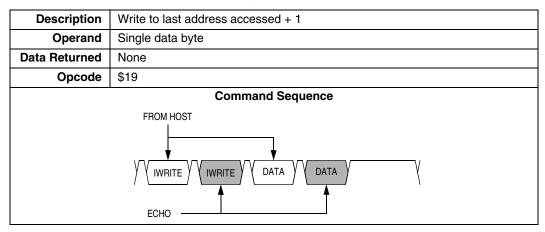

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

| Description   | Reads stack pointer                                                          |  |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| Operand       | None                                                                         |  |  |  |  |  |  |

| Data Returned | Returns incremented stack pointer value (SP + 1) in high-byte:low-byte order |  |  |  |  |  |  |

| Opcode        | \$0C                                                                         |  |  |  |  |  |  |

|               | Command Sequence                                                             |  |  |  |  |  |  |

|               | FROM HOST                                                                    |  |  |  |  |  |  |

|               | V     READSP     V     SP     V     SP       HIGH     V     LOW     V        |  |  |  |  |  |  |

|               | ECHO RETURN                                                                  |  |  |  |  |  |  |

#### Table 19-8. RUN (Run User Program) Command

| Description   | Executes PULH and RTI instructions |

|---------------|------------------------------------|

| Operand       | None                               |

| Data Returned | None                               |

| Opcode        | \$28                               |

|               | Command Sequence                   |

|               |                                    |

# Chapter 20 Electrical Specifications

## 20.1 Introduction

This section contains preliminary electrical and timing specifications.

## 20.2 Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the microcontroller unit (MCU) can be exposed without permanently damaging it.

NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 20.5 DC Electrical Characteristics for guaranteed operating conditions.

| Characteristic <sup>(1)</sup>                                                                           | Symbol                                                                         | Value                                        | Unit |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------|------|

| Supply voltage                                                                                          | V <sub>DD</sub>                                                                | -0.3 to +6.0                                 | V    |

| Input voltage                                                                                           | V <sub>In</sub>                                                                | V <sub>SS</sub> –0.3 to V <sub>DD</sub> +0.3 | V    |

| Maximum current per pin<br>excluding V <sub>DD</sub> , V <sub>SS</sub> ,<br>and PTA0–PTA6 and PTC0-PTC1 | I                                                                              | ±15                                          | mA   |

| Maximum current for pins<br>PTA0–PTA6 and PTC0-PTC1                                                     | І <sub>РТА0</sub> –І <sub>РТА6</sub> ,<br>І <sub>РТС0</sub> –І <sub>РТС1</sub> | ±25                                          | mA   |

| Maximum current out of V <sub>SS</sub>                                                                  | I <sub>MVSS</sub>                                                              | 100                                          | mA   |

| Maximum current into V <sub>DD</sub>                                                                    | I <sub>MVDD</sub>                                                              | 100                                          | mA   |

| Storage temperature                                                                                     | T <sub>STG</sub>                                                               | -55 to +150                                  | °C   |

1. Voltages referenced to  $V_{SS}$

## NOTE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{In}$  and  $V_{Out}$  be constrained to the range  $V_{SS} \leq (V_{In} \text{ or } V_{Out}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ ).