Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | LINbus, SCI, SPI                                           |

| Peripherals                | POR, PWM                                                   |

| Number of I/O              | 24                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 512 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 32-LQFP                                                    |

| Supplier Device Package    | 32-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908ey16vfae |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

List of Chapters

**Table of Contents**

Chapter 12 Input/Output (I/O) Ports (PORTS)

| 12.1   | Introduction               | 115 |

|--------|----------------------------|-----|

| 12.2   | Port A.                    | 115 |

| 12.2.1 | Port A Data Register       | 115 |

| 12.2.2 | Data Direction Register A. | 115 |

| 12.3   | Port B.                    | 117 |

| 12.3.1 | Port B Data Register       | 117 |

| 12.3.2 | Data Direction Register B  | 118 |

| 12.4   | Port C.                    | 119 |

| 12.4.1 | Port C Data Register       | 119 |

| 12.4.2 | Data Direction Register C  | 119 |

| 12.5   | Port D.                    | 120 |

| 12.5.1 | Port D Data Register       | 120 |

| 12.5.2 | Data Direction Register D  | 121 |

| 12.6   | Port E.                    | 122 |

| 12.6.1 | Port E Data Register       | 122 |

| 12.6.2 | Data Direction Register E  | 123 |

# Chapter 13 Enhanced Serial Communications Interface (ESCI) Module

| 13.3 Pin Name Conventions 125   13.4 Functional Description 127   13.4.1 Data Format 128   13.4.2 Transmitter 128   13.4.2 Transmitter 128   13.4.2 Character Length 129   13.4.2.2 Character Transmission 129   13.4.2.3 Break Characters 129   13.4.2.4 Idle Characters 130   13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.1 Character Reception 132   13.4.3.2 Character Reception 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.4.3.8 Error Int | 13.1 Introduction           | 125 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|

| 13.4 Functional Description 127   13.4.1 Data Format 128   13.4.2 Transmitter 128   13.4.2 Transmitter 129   13.4.2.1 Character Length 129   13.4.2.2 Character Transmission 129   13.4.2.3 Break Characters 129   13.4.2.4 Idle Characters 130   13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.3.1 Character Length 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wa | 13.2 Features               | 125 |

| 13.4.1 Data Format 128   13.4.2 Transmitter 128   13.4.2 Transmitter 129   13.4.2.1 Character Length 129   13.4.2.2 Character Transmission 129   13.4.2.3 Break Characters 129   13.4.2.4 Idle Characters 129   13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.1 Character Reception 132   13.4.3.2 Character Reception 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136                                                           | 13.3 Pin Name Conventions   | 125 |

| 13.4.2 Transmitter. 128   13.4.2.1 Character Length 129   13.4.2.2 Character Transmission 129   13.4.2.3 Break Characters 129   13.4.2.4 Idle Characters 129   13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136                                                                                  | 13.4 Functional Description | 127 |

| 13.4.2.1 Character Length 129   13.4.2.2 Character Transmission 129   13.4.2.3 Break Characters 129   13.4.2.4 Idle Characters 129   13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.1 Character Reception 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                  | 13.4.1 Data Format          | 128 |

| 13.4.2.2 Character Transmission 129   13.4.2.3 Break Characters 129   13.4.2.4 Idle Characters 130   13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.1 Character Reception 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                  | 13.4.2 Transmitter          | 128 |

| 13.4.2.3 Break Characters 129   13.4.2.4 Idle Characters 130   13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.1 Character Reception 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                            | $\mathbf{v}$                |     |

| 13.4.2.4 Idle Characters 130   13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.1 Character Reception 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                  |                             |     |

| 13.4.2.5 Inversion of Transmitted Output 130   13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.1 Character Reception 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                       |                             |     |

| 13.4.2.6 Transmitter Interrupts 130   13.4.3 Receiver 131   13.4.3 Character Length 132   13.4.3.1 Character Reception 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                            |                             |     |

| 13.4.3 Receiver. 131   13.4.3.1 Character Length 132   13.4.3.2 Character Reception. 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 132   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                                                                                                 |                             |     |

| 13.4.3.1 Character Length 132   13.4.3.2 Character Reception 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                                                                                                                         |                             |     |

| 13.4.3.2 Character Reception. 132   13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |     |

| 13.4.3.3 Data Sampling 132   13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |     |

| 13.4.3.4 Framing Errors 134   13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |     |

| 13.4.3.5 Baud Rate Tolerance 134   13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |     |

| 13.4.3.6 Receiver Wakeup 135   13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                           |     |

| 13.4.3.7 Receiver Interrupts 136   13.4.3.8 Error Interrupts 136   13.5 Low-Power Modes 136   13.5.1 Wait Mode 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |     |

| 13.4.3.8   Error Interrupts   136     13.5   Low-Power Modes   136     13.5.1   Wait Mode   136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |     |

| 13.5   Low-Power Modes   136     13.5.1   Wait Mode   136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |     |

| 13.5.1 Wait Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |     |

| 13.5.2 Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13.5.2 Stop Mode            | 136 |

### Input/Output (I/O) Section

| Addr.         | Register Name                                                  |        | Bit 7  | 6          | 5       | 4           | 3                      | 2      | 1        | Bit 0 |

|---------------|----------------------------------------------------------------|--------|--------|------------|---------|-------------|------------------------|--------|----------|-------|

|               | ESCII Arbiter Control                                          | Read:  |        | ALOST      | 4140    |             | AFIN                   | ARUN   | AROVFL   | ARD8  |

| \$0018        | Register<br>(SCIACTL)                                          | Write: | AM1    |            | AM0     | ACLK        |                        |        |          |       |

|               | See page 151.                                                  | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

|               | ESCI Arbiter Data Register                                     | Read:  | ARD7   | ARD6       | ARD5    | ARD4        | ARD3                   | ARD2   | ARD1     | ARD0  |

| \$0019        | (SCIACTL)                                                      | Write: |        |            |         |             |                        |        |          |       |

|               | See page 152.                                                  | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

|               | Keyboard Status                                                | Read:  | 0      | 0          | 0       | 0           | KEYF                   | 0      | IMASKK   | MODEK |

| \$001A        | and Control Register<br>(INTKBSCR)                             | Write: |        |            |         |             |                        | ACKK   | IWASKK   | MODER |

|               | See page 109.                                                  | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

|               | Keyboard Interrupt Enable                                      | Read:  | 0      | 0          | 0       | KBIE4       | KBIE3                  | KBIE2  | KBIE1    | KBIE0 |

| \$001B        | Register (INTKBIER)                                            | Write: |        |            |         | NDIE4       | NDIE5                  | NDIEZ  | NDIE I   | KDIEU |

|               | See page 110.                                                  | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

|               | <b>T</b>                                                       | Read:  | TBIF   | TBR2       | TBR1    | TBR0        | 0                      | TBIE   | TBON     | R     |

| \$001C        | Timebase Control Register<br>(TBCR)                            | Write: |        | TDTIZ      | TBITT   | TBHO        | TACK                   | IDIE   | TBOIN    |       |

|               | See page 192.                                                  | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

|               | IRQ Status and Control                                         | Read:  | 0      | 0          | 0       | 0           | IRQF                   | 0      | IMASK    | MODE  |

| \$001D        | Register (INTSCR)                                              | Write: |        |            |         |             |                        | ACK    |          | MODE  |

| See h         | See page 104.                                                  | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

|               | Configuration Pagistar 2                                       | Read:  | R      | ESCI       | EXT-    | EXT-        | EXT-                   | TMB-   | OSCENIN- | SSB-  |

|               | (CONFIG2)                                                      | Write: |        | BDSRC      | XTALEN  | SLOW        | CLKEN                  | CLKSEL | STOP     | PUENB |

|               | See page 57.                                                   | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 1     |

|               | Configuration Register 1                                       | Read:  | COPRS  | LVISTOP    | LVIRSTD | LVIPWRD     | LVI5OR3 <sup>(1)</sup> | SSREC  | STOP     | COPD  |

| \$001F        | (CONFIG1)<br>See page 58.                                      | Write: |        |            |         |             |                        |        |          |       |

|               |                                                                | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

| 1. The L      | VI5OR3 bit is cleared only by                                  |        |        | R).        | 1       | 1           |                        |        | 1 1      |       |

|               | Timer A Status and Control<br>Register (TASC)<br>See page 201. | Read:  | TOF    | TOIE       | TSTOP   | 0           | R                      | PS2    | PS1      | PS0   |

| \$0020        |                                                                | Write: | 0      |            |         | TRST        |                        |        |          |       |

|               | 000 page 2011                                                  | Reset: | 0      | 0          | 1       | 0           | 0                      | 0      | 0        | 0     |

| Tin<br>\$0021 | Timer A Counter Register                                       | Read:  | BIT 15 | BIT 14     | BIT 13  | BIT 12      | BIT 11                 | BIT 10 | BIT 9    | BIT 8 |

|               | High (TACNTH)<br>See page 203.                                 | Write: | -      | _          | -       | -           |                        | _      |          | -     |

|               | 000 page 200.                                                  | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

| <b>**</b>     | Timer A Counter Register                                       | Read:  | BIT 7  | BIT 6      | BIT 5   | BIT 4       | BIT 3                  | BIT 2  | BIT 1    | BIT 0 |

| \$0022        | Low (TACNTL)<br>See page 203.                                  | Write: |        |            |         |             |                        | -      |          |       |

|               | 000 page 200.                                                  | Reset: | 0      | 0          | 0       | 0           | 0                      | 0      | 0        | 0     |

|               |                                                                |        |        | = Unimplem | ented   | R = Reserve | D                      | U = Un | affected |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 7)

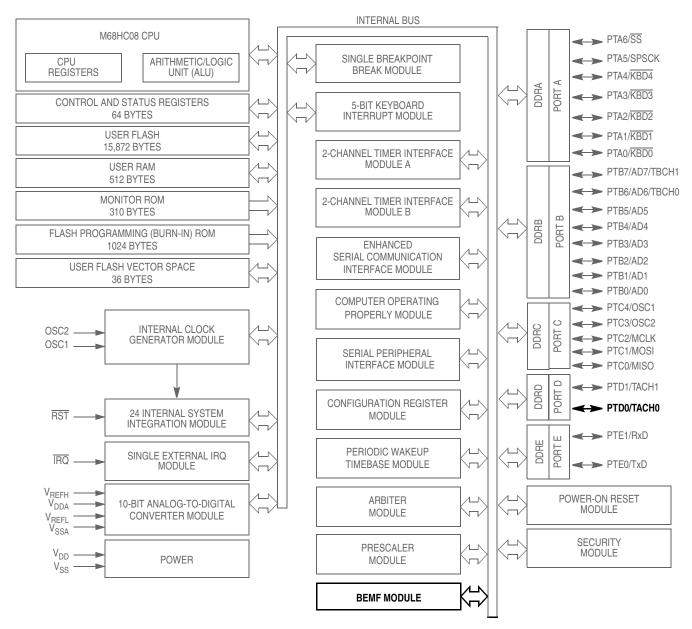

#### **BEMF Counter Module (BEMF)**

### 4.5.2 Stop Mode

The BEMF module is inactive after execution of the STOP instruction. In STOP mode the BEMF register is not accessible by the CPU.

Figure 4-2. Block Diagram Highlighting BEMF Block and Pins

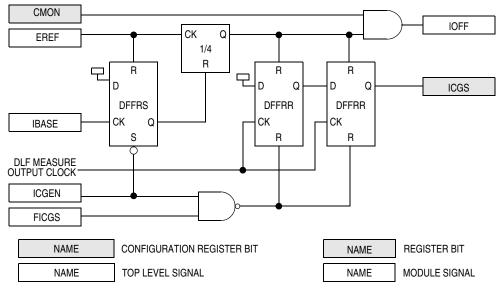

#### Internal Clock Generator (ICG) Module

Figure 8-6. Internal Clock Activity Detector

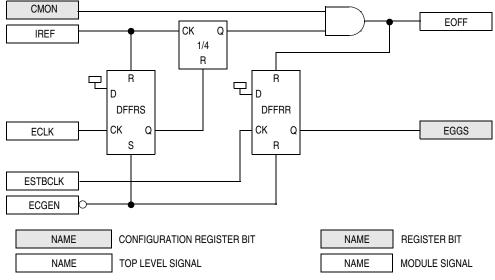

### 8.3.4.3 External Clock Activity Detector

The external clock activity detector, shown in Figure 8-7, looks for at least one falling edge on the external clock (ECLK) every time the internal reference (IREF) is low. Since IREF is less than half the frequency of ECLK, this should occur every time. If it does not occur two consecutive times, the external clock inactivity indicator (EOFF) is set. EOFF will be cleared the next time there is a falling edge of ECLK while IREF is low.

The external clock stable bit (ECGS) is also generated in the external clock activity detector. ECGS is set on a falling edge of the external stabilization clock (ESTBCLK). This will be 4096 ECLK cycles after the external clock generator on bit is set, or the MCU exits stop mode (ECGEN = 1) if the external crystal enable (EXTXTALEN) in the CONFIG is set, or 16 cycles when EXTXTALEN is clear. ECGS is cleared when the external clock generator is turned off or in stop mode (ECGEN is clear) or when EOFF is set.

Figure 8-7. External Clock Activity Detector

External Interrupt (IRQ)

### 9.5 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ interrupt latch can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear the latches during the break state.

To allow software to clear the IRQ latch during a break interrupt, write a 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ latch.

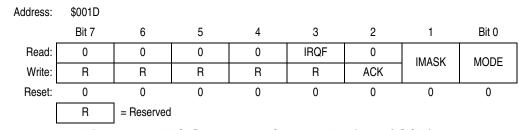

### 9.6 IRQ Status and Control Register

The IRQ status and control register (ISCR) controls and monitors operation of the IRQ module. The ISCR has these functions:

- Shows the state of the IRQ interrupt flag

- Clears the IRQ interrupt latch

- Masks IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

### Figure 9-3. IRQ Status and Control Register (ISCR)

### IRQF — IRQ Flag Bit

This read-only status bit is high when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- $0 = \overline{IRQ}$  interrupt not pending

### ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0. Reset clears ACK.

### IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables IRQ interrupt requests. Reset clears IMASK.

- 1 = IRQ interrupt requests disabled

- 0 = IRQ interrupt requests enabled

### MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin. Reset clears MODE.

- $1 = \overline{IRQ}$  interrupt requests on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt requests on falling edges only

#### Keyboard Interrupt (KBD) Module

### **10.4 Keyboard Initialization**

When a keyboard interrupt pin is enabled, it takes time for the internal pullup to reach a logic 1. Therefore, a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register

- 2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts

- 4. Clear the IMASKK bit.

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that depends on the external load.

Another way to avoid a false interrupt:

- 1. Configure the keyboard pins as outputs by setting the appropriate DDRA bits in data direction register A.

- 2. Write 1s to the appropriate port A data register bits.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

### 10.5 Low-Power Modes

The WAIT and STOP instructions put the microcontroller unit (MCU) in low power-consumption standby modes.

### 10.5.1 Wait Mode

The keyboard module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

### 10.5.2 Stop Mode

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

### **10.6 Keyboard Module During Break Interrupts**

The BCFE bit in the break flag control register (SBFCR) enables software to clear status bits during the break state.

To allow software to clear the KEYF bit during a break interrupt, write a 1 to the BCFE bit. If KEYF is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the KEYF bit during the break state, write a 0 to the BCFE bit. With BCFE at 0, writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect. See 10.7.1 Keyboard Status and Control Register.

#### System Integration Module (SIM)

### 14.3.2.6 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the V<sub>DD</sub> voltage falls to the V<sub>TRIPF</sub> voltage. The LVI bit in the SIM reset status register (SRSR) is set and a chip reset is asserted if the LVIPWRD and LVIRSTD bits in the CONFIG register are at 0. The MCU is held in reset until V<sub>DD</sub> rises above V<sub>TRIPR</sub>. The MCU remains in reset until the SIM counts 4096 CGMXCLK to begin a reset recovery. Another 64 CGMXCLK cycles later, the CPU is released from reset to allow the reset vector sequence to occur. See Chapter 11 Low-Voltage Inhibit (LVI) Module.

### 14.4 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as a prescaler for the computer operating properly module (COP). The SIM counter overflow supplies the clock for the COP module. The SIM counter is 12 bits long and is clocked by the falling edge of CGMXCLK.

### 14.4.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit asserts the signal PORRST. Once the SIM is initialized, it enables the internal clock generator to drive the bus clock state machine.

### 14.4.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the configuration register. If the SSREC bit is a 1, then the stop recovery is reduced from the normal delay of 4096 CGMXCLK cycles down to 32 CGMXCLK cycles.

### 14.4.3 SIM Counter and Reset States

The SIM counter is free-running after all reset states. See 14.3.2 Active Resets from Internal Sources for counter control and internal reset recovery sequences.

### 14.5 Program Exception Control

Normal, sequential program execution can be changed in two ways:

- 1. Interrupts

- a. Maskable hardware CPU interrupts

- b. Non-maskable software interrupt instruction (SWI)

- 2. Reset

#### **Transmission Formats**

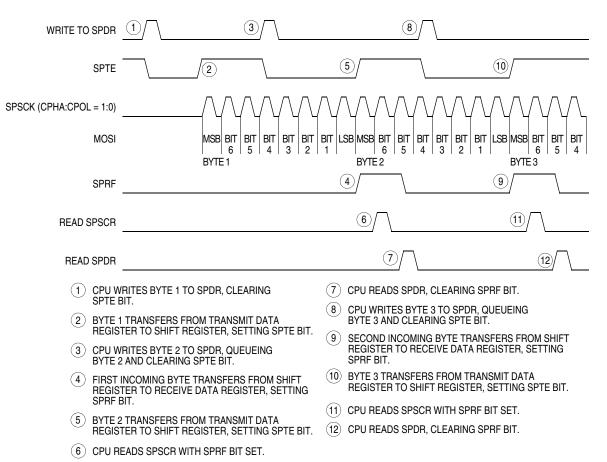

In a slave SPI module, data enters the shift register under the control of the serial clock from the master SPI module. After a byte enters the shift register of a slave SPI, it is transferred to the receive data register, and the SPRF bit (SPSCR) is set. To prevent an overflow condition, slave software then must read the SPI data register before another byte enters the shift register.

The maximum frequency of the SPSCK for an SPI configured as a slave is the bus clock speed, which is twice as fast as the fastest master SPSCK clock that can be generated. The frequency of the SPSCK for an SPI configured as a slave does not have to correspond to any SPI baud rate. The baud rate only controls the speed of the SPSCK generated by an SPI configured as a master. Therefore, the frequency of the SPSCK for an SPI configured as a slave can be any frequency less than or equal to the bus speed.

When the master SPI starts a transmission, the data in the slave shift register begins shifting out on the MISO pin. The slave can load its shift register with a new byte for the next transmission by writing to its transmit data register. The slave must write to its transmit data register at least one bus cycle before the master starts the next transmission. Otherwise the byte already in the slave shift register shifts out on the MISO pin. Data written to the slave shift register during a a transmission remains in a buffer until the end of the transmission.

When the clock phase bit (CPHA) is set, the first edge of SPSCK starts a transmission. When CPHA is clear, the falling edge of SS starts a transmission. (See 15.5 Transmission Formats.)

If the write to the data register is late, the SPI transmits the data already in the shift register from the previous transmission.

### NOTE

To prevent SPSCK from appearing as a clock edge, SPSCK must be in the proper idle state before the slave is enabled.

### **15.5 Transmission Formats**

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line synchronizes shifting and sampling on the two serial data lines. A slave select line allows individual selection of a slave SPI device; slave devices that are not selected do not interfere with SPI bus activities. On a master SPI device, the slave select line can be used optionally to indicate a multiple-master bus contention.

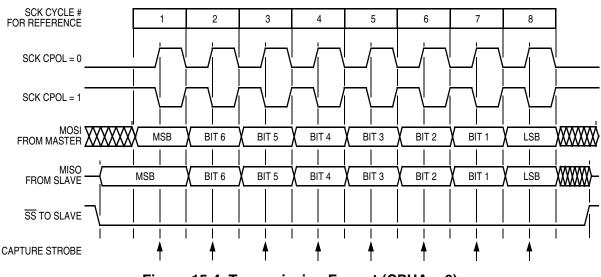

### 15.5.1 Clock Phase and Polarity Controls

Software can select any of four combinations of serial clock (SCK) phase and polarity using two bits in the SPI control register (SPCR). The clock polarity is specified by the CPOL control bit, which selects an active high or low clock and has no significant effect on the transmission format.

The clock phase (CPHA) control bit (SPCR) selects one of two fundamentally different transmission formats. The clock phase and polarity should be identical for the master SPI device and the communicating slave device. In some cases, the phase and polarity are changed between transmissions to allow a master device to communicate with peripheral slaves having different requirements.

#### NOTE

Before writing to the CPOL bit or the CPHA bit (SPCR), disable the SPI by clearing the SPI enable bit (SPE).

#### Serial Peripheral Interface (SPI) Module

### 15.5.2 Transmission Format When CPHA = 0

Figure 15-4 shows an SPI transmission in which CPHA (SPCR) is 0. The figure should not be used as a replacement for data sheet parametric information. Two waveforms are shown for SCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input ( $\overline{SS}$ ) is at logic 0, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$  pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI (see 15.6.2 Mode Fault Error). When CPHA = 0, the first SPSCK edge is the MSB capture strobe. Therefore, the slave must begin driving its data before the first SPSCK edge, and a falling edge on the  $\overline{SS}$  pin is used to start the transmission. The  $\overline{SS}$  pin must be toggled high and then low again between each byte transmitted.

Figure 15-4. Transmission Format (CPHA = 0)

### 15.5.3 Transmission Format When CPHA = 1

Figure 15-5 shows an SPI transmission in which CPHA (SPCR) is 1. The figure should not be used as a replacement for data sheet parametric information. Two waveforms are shown for SCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input ( $\overline{SS}$ ) is at logic 0, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$  pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 15.6.2 Mode Fault Error.) When CPHA = 1, the master begins driving its MOSI pin on the first SPSCK edge. Therefore, the slave uses the first SPSCK edge as a start transmission signal. The  $\overline{SS}$  pin can remain low between transmissions. This format may be preferable in systems having only one master and only one slave driving the MISO data line.

### Figure 15-10. SPRF/SPTE CPU Interrupt Timing

### 15.9 Resetting the SPI

Any system reset completely resets the SPI. Partial reset occurs whenever the SPI enable bit (SPE) is low. Whenever SPE is low, the following occurs:

- The SPTE flag is set.

- Any transmission currently in progress is aborted.

- The shift register is cleared.

- The SPI state counter is cleared, making it ready for a new complete transmission.

- All the SPI port logic is defaulted back to being general-purpose I/O.

The following additional items are reset only by a system reset:

- All control bits in the SPCR register

- All control bits in the SPSCR register (MODFEN, ERRIE, SPR1, and SPR0)

- The status flags SPRF, OVRF, and MODF

By not resetting the control bits when SPE is low, the user can clear SPE between transmissions without having to reset all control bits when SPE is set back to high for the next transmission.

By not resetting the SPRF, OVRF, and MODF flags, the user can still service these interrupts after the SPI has been disabled. The user can disable the SPI by writing a 0 to the SPE bit. The SPI also can be disabled by a mode fault occurring in an SPI that was configured as a master with the MODFEN bit set.

### **OVRF** — Overflow Bit

This clearable, read-only flag is set if software does not read the byte in the receive data register before the next byte enters the shift register. In an overflow condition, the byte already in the receive data register is unaffected, and the byte that shifted in last is lost. Clear the OVRF bit by reading the SPI status and control register with OVRF set and then reading the SPI data register. Reset clears the OVRF flag.

- 1 = Overflow

- 0 = No overflow

### MODF — Mode Fault Bit

This clearable, read-only flag is set in a slave SPI if the  $\overline{SS}$  pin goes high during a transmission. In a master SPI, the MODF flag is set if the  $\overline{SS}$  pin goes low at any time. Clear the MODF bit by reading the SPI status and control register with MODF set and then writing to the SPI data register. Reset clears the MODF bit.

- $1 = \overline{SS}$  pin at inappropriate logic level

- $0 = \overline{SS}$  pin at appropriate logic level

### SPTE — SPI Transmitter Empty Bit

This clearable, read-only flag is set each time the transmit data register transfers a byte into the shift register. SPTE generates an SPTE CPU interrupt request if the SPTIE bit in the SPI control register is set also.

### NOTE

### Do not write to the SPI data register unless the SPTE bit is high.

For an idle master or idle slave that has no data loaded into its transmit buffer, the SPTE will be set again within two bus cycles since the transmit buffer empties into the shift register. This allows the user to queue up a 16-bit value to send. For an already active slave, the load of the shift register cannot occur until the transmission is completed. This implies that a back-to-back write to the transmit data register is not possible. The SPTE indicates when the next write can occur.

### Reset sets the SPTE bit.

1 = Transmit data register empty

0 = Transmit data register not empty

### MODFEN — Mode Fault Enable Bit

This read/write bit, when set to 1, allows the MODF flag to be set. If the MODF flag is set, clearing the MODFEN does not clear the MODF flag. If the SPI is enabled as a master and the MODFEN bit is low, then the  $\overline{SS}$  pin is available as a general-purpose I/O.

If the MODFEN bit is set, then this pin is not available as a general purpose I/O. When the SPI is enabled as a slave, the  $\overline{SS}$  pin is not available as a general-purpose I/O regardless of the value of MODFEN. (See 15.12.4 SS (Slave Select)).

If the MODFEN bit is low, the level of the  $\overline{SS}$  pin does not affect the operation of an enabled SPI configured as a master. For an enabled SPI configured as a slave, having MODFEN low only prevents the MODF flag from being set. It does not affect any other part of SPI operation. (See 15.6.2 Mode Fault Error).

#### Timer Interface A (TIMA) Module

The value in the TIMA counter modulo registers and the selected prescaler output determines the frequency of the PWM output. The frequency of an 8-bit PWM signal is variable in 256 increments. Writing \$00FF (255) to the TIMA counter modulo registers produces a PWM period of 256 times the internal bus clock period if the prescaler select value is \$000 (see 17.8.1 TIMA Status and Control Register).

The value in the TIMA channel registers determines the pulse width of the PWM output. The pulse width of an 8-bit PWM signal is variable in 256 increments. Writing \$0080 (128) to the TIMA channel registers produces a duty cycle of 128/256 or 50%.

### 17.3.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 17.3.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the value currently in the TIMA channel registers.

An unsynchronized write to the TIMA channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIMA overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIMA may pass the new value before it is written to the TIMA channel registers.

Use these methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- When changing to a longer pulse width, enable TIMA overflow interrupts and write the new value in the TIMA overflow interrupt routine. The TIMA overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

### 17.3.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the PTD0/TACH0 pin. The TIMA channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIMA channel 0 status and control register (TASC0) links channel 0 and channel 1. The TIMA channel 0 registers initially control the pulse width on the PTD0/TACH0 pin. Writing to the TIMA channel 1 registers enables the TIMA channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIMA channel registers (0 or 1) that control the pulse width are the ones written to last. TASC0 controls and monitors the buffered

### 17.4 Interrupts

These TIMA sources can generate interrupt requests:

- TIMA overflow flag (TOF) The TOF bit is set when the TIM counter reaches the modulo value programmed in the TIMA counter modulo registers. The TIMA overflow interrupt enable bit, TOIE, enables TIMA overflow CPU interrupt requests. TOF and TOIE are in the TIMA status and control register.

- TIMA channel flags (CH1F–CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIMA CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE.

### 17.5 Low-Power Modes

The WAIT and STOP instructions put the microcontroller unit (MCU) in low power-consumption standby modes.

### 17.5.1 Wait Mode

The TIMA remains active after the execution of a WAIT instruction. In wait mode, the TIMA registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIMA can bring the MCU out of wait mode.

If TIMA functions are not required during wait mode, reduce power consumption by stopping the TIMA before executing the WAIT instruction.

### 17.5.2 Stop Mode

The TIMA is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions or the state of the TIMA counter. TIMA operation resumes when the MCU exits stop mode.

### 17.6 TIMA During Break Interrupts

A break interrupt stops the TIMA counter and inhibits input captures.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state.

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a 2-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

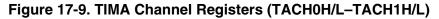

### 17.8.5 TIMA Channel Registers

These read/write registers contain the captured TIMA counter value of the input capture function or the output compare value of the output compare function. The state of the TIMA channel registers after reset is unknown.

In input capture mode (MSxB-MSxA = 0:0), reading the high byte of the TIMA channel x registers (TACHxH) inhibits input captures until the low byte (TACHxL) is read.

In output compare mode (MSxB–MSxA  $\neq$  0:0), writing to the high byte of the TIMA channel x registers (TACHxH) inhibits output compares and the CHxF bit until the low byte (TACHxL) is written.

| Register Name and Address |              |        | TACH0H — \$0026 |                 |               |        |       |       |  |

|---------------------------|--------------|--------|-----------------|-----------------|---------------|--------|-------|-------|--|

|                           | Bit 7        | 6      | 5               | 4               | 3             | 2      | 1     | Bit 0 |  |

| Read:<br>Write:           | BIT 15       | BIT 14 | BIT 13          | BIT 12          | BIT 11        | BIT 10 | BIT 9 | BIT 8 |  |

| Reset:                    |              |        |                 | Indeterminat    | e after reset |        |       |       |  |

| Register Nar              | me and Addre | ess    | TACHOL -        | TACH0L — \$0027 |               |        |       |       |  |

|                           | Bit 7        | 6      | 5               | 4               | 3             | 2      | 1     | Bit 0 |  |

| Read:<br>Write:           | BIT 7        | BIT 6  | BIT 5           | BIT 4           | BIT 3         | BIT 2  | BIT 1 | BIT 0 |  |

| Reset:                    |              |        |                 | Indeterminat    |               |        |       |       |  |

| Register Nar              | me and Addre | ess    | TACH1H — \$0029 |                 |               |        |       |       |  |

|                           | Bit 7        | 6      | 5               | 4               | 3             | 2      | 1     | Bit 0 |  |

| Read:<br>Write:           | BIT 15       | BIT 14 | BIT 13          | BIT 12          | BIT 11        | BIT 10 | BIT 9 | BIT 8 |  |

| Reset:                    |              |        |                 | Indeterminat    | e after reset |        |       |       |  |

| Register Nar              | me and Addre | ess    | TACH1L — \$002A |                 |               |        |       |       |  |

| _                         | Bit 7        | 6      | 5               | 4               | 3             | 2      | 1     | Bit 0 |  |

| Read:<br>Write:           | BIT 7        | BIT 6  | BIT 5           | BIT 4           | BIT 3         | BIT 2  | BIT 1 | BIT 0 |  |

| Reset:                    |              |        |                 | Indeterminat    | e after reset |        |       |       |  |

Setting MS0B disables the channel 1 status and control register and reverts TBCH1 to general-purpose I/O.

Reset clears the MSxB bit.

- 1 = Buffered output compare/PWM operation enabled

- 0 = Buffered output compare/PWM operation disabled

### MSxA — Mode Select Bit A

When ELSxB:A  $\neq$  00, this read/write bit selects either input capture operation or unbuffered output compare/PWM operation. See Table 18-2.

1 = Unbuffered output compare/PWM operation

0 = Input capture operation

When ELSxB:A = 00, this read/write bit selects the initial output level of the TCHx pin once PWM, input capture, or output compare operation is enabled. See Table 18-2. Reset clears the MSxA bit.

1 = Initial output level low

0 = Initial output level high

### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIMB status and control register (TBSC).

### ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to port B, and pin PTBx/TBCHx is available as a general-purpose I/O pin. However, channel x is at a state determined by these bits and becomes transparent to the respective pin when PWM, input capture, or output compare mode is enabled. Table 18-2 shows how ELSxB and ELSxA work. Reset clears the ELSxB and ELSxA bits.

| MSxB | MSxA | ELSxB | ELSxA | Mode            | Configuration                                     |

|------|------|-------|-------|-----------------|---------------------------------------------------|

| Х    | 0    | 0     | 0     | Output preset   | Pin under port control; initial output level high |

| Х    | 1    | 0     | 0     | Output preset   | Pin under port control; initial output level low  |

| 0    | 0    | 0     | 1     |                 | Capture on rising edge only                       |

| 0    | 0    | 1     | 0     | Input capture   | Capture on falling edge only                      |

| 0    | 0    | 1     | 1     |                 | Capture on rising or falling edge                 |

| 0    | 1    | 0     | 0     |                 | Software compare only                             |

| 0    | 1    | 0     | 1     | Output compare  | Toggle output on compare                          |

| 0    | 1    | 1     | 0     | or PWM          | Clear output on compare                           |

| 0    | 1    | 1     | 1     |                 | Set output on compare                             |

| 1    | Х    | 0     | 1     | Buffered output | Toggle output on compare                          |

| 1    | Х    | 1     | 0     | compare or      | Clear output on compare                           |

| 1    | Х    | 1     | 1     | buffered PWM    | Set output on compare                             |

### Table 18-2. Mode, Edge, and Level Selection

### NOTE

Before enabling a TIMB channel register for input capture operation, make sure that the PTBx/TBCHx pin is stable for at least two bus clocks.

Timer Interface B (TIMB) Module

#### **Development Support**

Table 19-1 also lists external frequencies required to achieve a standard baud rate of 7200 bps. The effective baud rate is the bus frequency divided by 278. If using a crystal as the clock source, be aware of the upper frequency limit that the internal clock module can handle. See 20.6 Control Timing for this limit.

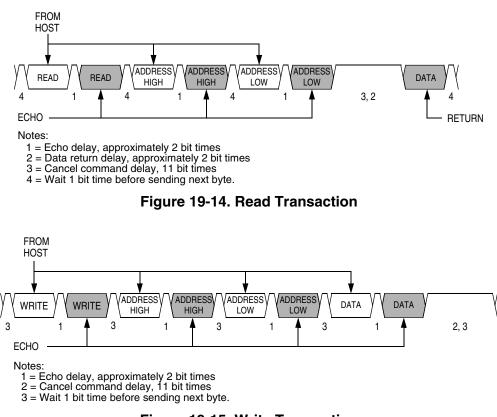

### 19.3.1.7 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

The monitor ROM firmware echoes each received byte back to the PTA0 pin for error checking. An 11-bit delay at the end of each command allows the host to send a break character to cancel the command. A delay of two bit times occurs before each echo and before READ, IREAD, or READSP data is returned. The data returned by a read command appears after the echo of the last byte of the command.

**NOTE** Wait one bit time after each echo before sending the next byte.

Figure 19-15. Write Transaction

#### Monitor Module (MON)

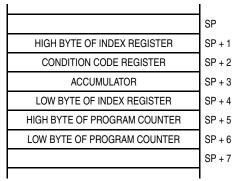

The MCU executes the SWI and PSHH instructions when it enters monitor mode. The RUN command tells the MCU to execute the PULH and RTI instructions. Before sending the RUN command, the host can modify the stacked CPU registers to prepare to run the host program. The READSP command returns the incremented stack pointer value, SP + 1. The high and low bytes of the program counter are at addresses SP + 5 and SP + 6.

Figure 19-16. Stack Pointer at Monitor Mode Entry

### 19.3.2 Security

A security feature discourages unauthorized reading of FLASH locations while in monitor mode. The host can bypass the security feature at monitor mode entry by sending eight security bytes that match the bytes at locations \$FFF6–\$FFFD. Locations \$FFF6–\$FFFD contain user-defined data.

### NOTE

Do not leave locations \$FFF6-\$FFFD blank. For security reasons, program locations \$FFF6-\$FFFD even if they are not used for vectors.

During monitor mode entry, the MCU waits after the power-on reset for the host to send the eight security bytes on pin PTA0. If the received bytes match those at locations \$FFF6-\$FFFD, the host bypasses the security feature and can read all FLASH locations and execute code from FLASH. Security remains bypassed until a power-on reset occurs. If the reset was not a power-on reset, security remains bypassed and security code entry is not required. See Figure 19-17.

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6-\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a FLASH location returns an invalid value and trying to execute code from FLASH causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

### NOTE

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$40 is set. If it is, then the correct security code has been entered and FLASH can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the FLASH module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

## **Revision History**

### Changes from Rev 9.0 published in August 2005 to Rev 10 published in October 2005

| Section                                             | Page (in Rev 10) | Description of change                                                                         |

|-----------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|

| Configuration<br>Registers (CONFIG1<br>and CONFIG2) | 57               | Figure 5-1. Configuration Register 2 (CONFIG2) — Corrected name for bit 6 to ESCIBDSRC.       |

| System Integration<br>Module (SIM)                  | 159              | 14.3.2.5 Forced Monitor Mode Entry Reset (MENRST) — Corrected erased value from \$00 to \$FF. |

| Timebase Module<br>(TBM)                            | 189              | Figure 16-1. Timebase Block Diagram — Corrected label from TBMCLKSEL to TMBCLKSEL.            |

### Changes from Rev 8.0 published in July 2005 to Rev 9 published in August 2005

| Section                                                         | Page (in Rev 9) | Description of change                                                                                                                             |

|-----------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout                                                      | N/A             | Updated to meet Freescale identity guidelines.                                                                                                    |

| Memory                                                          | 32              | Changed ADRH register bit names at address location \$003D from ADCH9 and ADCH8 to AD9 and AD8 respectively.                                      |

| Analog-to-Digital<br>Converter (ADC)<br>Module                  | 53              | Table 3-2. ADC Clock Divide Ratio — Changed last table entry under ADC Clock Rate from ADC input clock ÷ 6 to ADC input clock ÷ 16.               |

| Computer Operating<br>Properly (COP)<br>Module                  | 63              | 6.6 Monitor Mode — changed $V_{DD} = V_{TST}$ is present to $V_{TST}$ is present.                                                                 |

| Keyboard Interrupt<br>(KBD) Module                              | 110             | 10.7.2 Keyboard Interrupt Enable Register — In bit definition changed PDx to KBDx.                                                                |

|                                                                 | 112             | 11.3.1 Polled LVI Operation — Changed LVIRSTD bit must be at 0 to enable LVI resets to LVIRSTD bit must be at 1 to disable LVI resets             |

| Low-Voltage Inhibit<br>(LVI) Module                             | 113             | 11.5.2 Stop Mode — Changed LVIPWRD bit in the configuration register programmed to 0 to LVIPWRD bit in the configuration register programmed to 1 |

| Input/Output (I/O)<br>Ports (PORTS)                             | 117             | Figure 12-4. Port B Data Register (PTB) — Changed ATD7–ATD0 to AD7–AD0 in both the bit descriptions and alternative function blocks.              |

| Enhanced Serial<br>Communications<br>Interface (ESCI)<br>Module | 142             | 13.8.3 ESCI Control Register 3 — In the bit description for PEIE, changed ESCI receiver CPU interrupt request to ESCI error CPU interrupt request |

|                                                                 | 143             | 13.8.4 ESCI Status Register 1 — In the bit description for IDLE, changed ESCI error CPU interrupt request to ESCI receiver CPU interrupt request. |