### NXP USA Inc. - MC908EY16VFAR2 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | LINbus, SCI, SPI                                                       |

| Peripherals                | POR, PWM                                                               |

| Number of I/O              | 24                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908ey16vfar2 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

## Chapter 1 General Description

| 1.1    | Introduction                                                                                                        |    |

|--------|---------------------------------------------------------------------------------------------------------------------|----|

| 1.2    | Features                                                                                                            | 19 |

| 1.3    | MCU Block Diagram                                                                                                   | 21 |

| 1.4    | Pin Assignments                                                                                                     | 22 |

| 1.5    | Pin Functions                                                                                                       | 22 |

| 1.5.1  | Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> )                                                            | 22 |

| 1.5.2  | Oscillator Pins (PTC4/OSC1 and PTC3/OSC2)                                                                           |    |

| 1.5.3  | External Reset Pin (RST)                                                                                            | 23 |

| 1.5.4  | External Interrupt Pin (IRQ)                                                                                        | 23 |

| 1.5.5  | Analog Power Supply/Reference Pins (V <sub>DDA</sub> , V <sub>REFH</sub> , V <sub>SSA</sub> and V <sub>REFL</sub> ) | 23 |

| 1.5.6  | Port A I/O Pins (PTA6/SS, PTA5/SPSCK, PTA4/KBD4–PTA0/KBD0)                                                          | 24 |

| 1.5.7  | Port B I/O Pins (PTB7/AD7/TBCH1, PTB6/AD6/TBCH0, PTB5/AD5–PTB0/AD0)                                                 | 24 |

| 1.5.8  | Port C I/O Pins (PTC4/OSC1, PTC3/OSC2, PTC2/MCLK, PTC1/MOSI, PTC0/MISO)                                             | 24 |

| 1.5.9  | Port D I/O Pins (PTD1/TACH1–PTD0/TACH0)                                                                             | 24 |

| 1.5.10 | Port E I/O Pins (PTE1/RxD–PTE0/TxD)                                                                                 | 24 |

## Chapter 2 Memory

|       |                                | 25 |

|-------|--------------------------------|----|

| 2.2   | Unimplemented Memory Locations | 25 |

| 2.3   | Reserved Memory Locations      | 25 |

| 2.4   | Input/Output (I/O) Section     | 25 |

| 2.5   | Random Access Memory (RAM)     | 35 |

| 2.6   | FLASH Memory (FLASH)           | 35 |

| 2.6.1 | FLASH Control Register.        | 36 |

| 2.6.2 | FLASH Page Erase Operation     | 37 |

| 2.6.3 | FLASH Mass Erase Operation.    | 38 |

| 2.6.4 | FLASH Program/Read Operation   | 39 |

| 2.6.5 | FLASH Block Protection.        | 41 |

| 2.6.6 | FLASH Block Protect Register   | 41 |

| 2.6.7 | Wait Mode                      | 42 |

| 2.6.8 | Stop Mode                      | 42 |

#### Analog-to-Digital Converter (ADC) Module

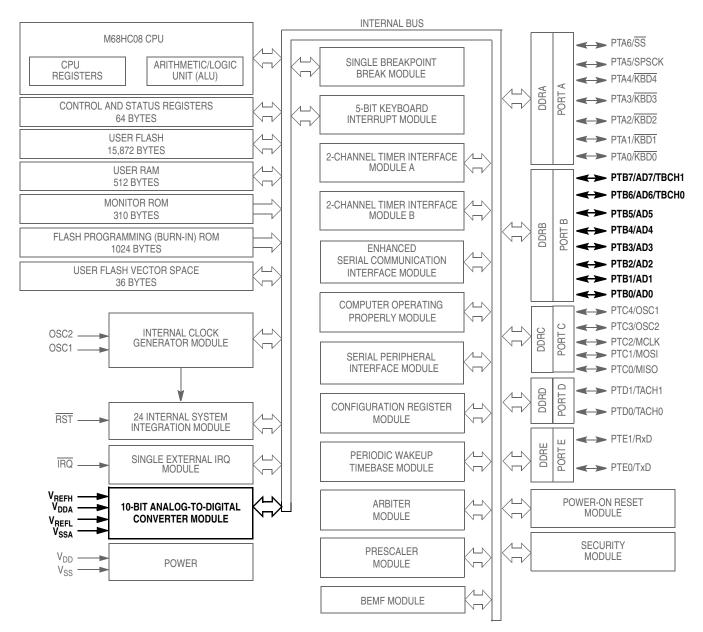

Figure 3-1. Block Diagram Highlighting ADC Block and Pins

Analog-to-Digital Converter (ADC) Module

## 3.5 Wait Mode

The WAIT instruction can put the MCU in low power-consumption standby mode.

The ADC continues normal operation during wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting ADCH[4:0] in the ADC status and control register before executing the WAIT instruction.

## 3.6 I/O Signals

The ADC module has eight input signals.

## 3.6.1 ADC Analog Power Pin (V<sub>DDA</sub>)

The ADC analog portion uses  $V_{DDA}$  as its power pin. Connect the  $V_{DDA}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDA}$  for good results.

NOTE

Route  $V_{DDA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

## 3.6.2 ADC Analog Ground Pin (V<sub>SSA</sub>)

The ADC analog portion uses  $V_{SSA}$  as its ground pin. Connect the  $V_{SSA}$  pin to the same voltage potential as  $V_{SS}$ .

## 3.6.3 ADC Voltage Reference Pin (V<sub>REFH</sub>)

$V_{REFH}$  is the power supply for setting the reference voltage  $V_{REFH}$ . Connect the  $V_{REFH}$  pin to the same voltage potential as  $V_{DDA}$ . There will be a finite current associated with  $V_{REFH}$ . See Chapter 20 Electrical Specifications.

### NOTE

Route  $V_{REFH}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

## 3.6.4 ADC Voltage Reference Low Pin (V<sub>REFL</sub>)

$V_{REFL}$  is the lower reference supply for the ADC. Connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSA}$ . A finite current will be associated with  $V_{REFL}$ . See Chapter 20 Electrical Specifications.

## 3.6.5 ADC Voltage In (ADVIN)

ADVIN is the input voltage signal from one of the 8 ADC channels to the ADC module.

## 3.6.6 ADC External Connections

This section describes the ADC external connections:  $V_{REFH}$  and  $V_{REFL}$ , ANx, and grounding.

**Central Processor Unit (CPU)**

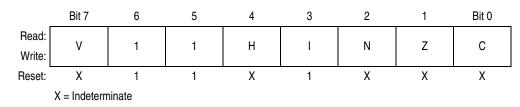

### Figure 7-6. Condition Code Register (CCR)

### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

1 = Overflow

0 = No overflow

### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

1 = Carry between bits 3 and 4

0 = No carry between bits 3 and 4

#### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

1 = Interrupts disabled

0 = Interrupts enabled

### NOTE

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

1 = Negative result

0 = Non-negative result

#### Internal Clock Generator (ICG) Module

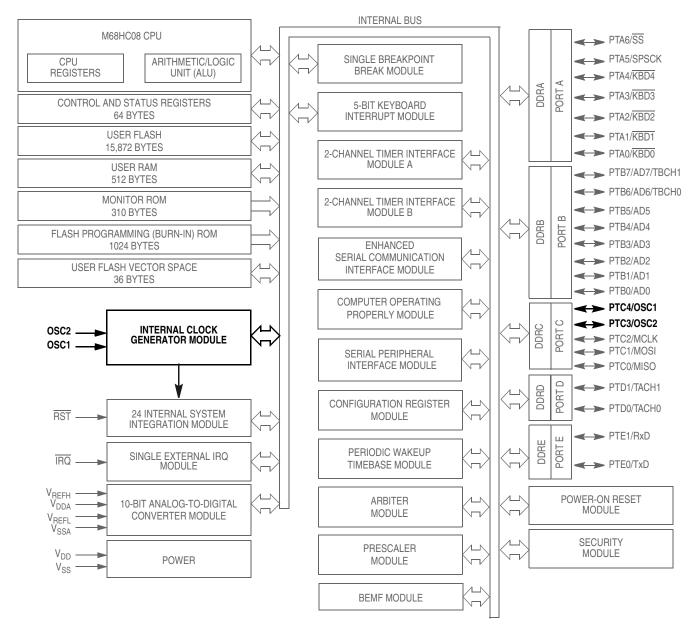

Figure 8-1. Block Diagram Highlighting ICG Block and Pins

## 8.3.5 Clock Selection Circuit

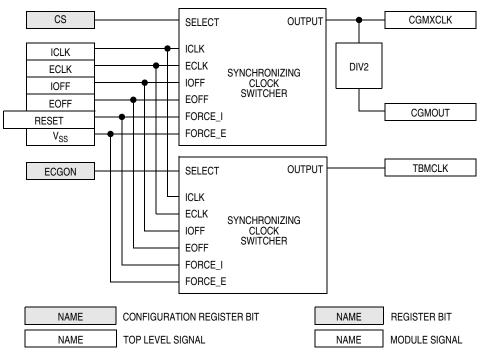

The clock selection circuit, shown in Figure 8-8, contains two clock switches which generate the oscillator output clock (CGMXCLK) and the timebase clock (TBMCLK) from either the internal clock (ICLK) or the external clock (ECLK). The clock selection circuit also contains a divide-by-two circuit which creates the clock generator output clock (CGMOUT), which generates the bus clocks.

Figure 8-8. Clock Selection Circuit Block Diagram

### 8.3.5.1 Clock Selection Switches

The first switch creates the oscillator output clock (CGMXCLK) from either the internal clock (ICLK) or the external clock (ECLK), based on the clock select bit (CS; set selects ECLK, clear selects ICLK). When switching the CS bit, both ICLK and ECLK must be on (ICGON and ECGON set). The clock being switched to also must be stable (ICGS or ECGS set).

The second switch creates the timebase clock (TBMCLK) from ICLK or ECLK based on the external clock on bit. When ECGON is set, the switch automatically selects the external clock, regardless of the state of the ECGS bit.

## 8.3.5.2 Clock Switching Circuit

To robustly switch between the internal clock (ICLK) and the external clock (ECLK), the switch assumes the clocks are completely asynchronous, so a synchronizing circuit is required to make the transition. When the select input (the clock select bit for the oscillator output clock switch or the external clock on bit for the timebase clock switch) is changed, the switch will continue to operate off the original clock for between one and two cycles as the select input is transitioned through one side of the synchronizer. Next, the output will be held low for between one and two cycles of the new clock as the select input transitions through the other side. Then the output starts switching at the new clock's frequency. This transition guarantees that no glitches will be seen on the output even though the select input may change

#### Internal Clock Generator (ICG) Module

asynchronously to the clocks. The unpredictably of the transition period is a necessary result of the asynchronicity.

The switch automatically selects ICLK during reset. When the clock monitor is on (CMON is set) and it determines one of the clock sources is inactive (as indicated by the IOFF or EOFF signals), the circuit is forced to select the active clock. There are no clocks for the inactive side of the synchronizer to properly operate, so that side is forced deselected. However, the active side will not be selected until one to two clock cycles after the IOFF or EOFF signal transitions.

## 8.4 Usage Notes

The ICG has several features which can provide protection to the microcontroller if properly used. Other features can greatly simplify usage of the ICG if certain techniques are employed. This section describes several possible ways to use the ICG and its features. These techniques are not the only ways to use the ICG and may not be optimum for all environments. In any case, these techniques should be used only as a template, and the user should modify them according to the application's requirements.

These notes include:

- Switching clock sources

- Enabling the clock monitor

- Using clock monitor interrupts

- Quantization error in digitally controlled oscillator (DCO) output

- Switching internal clock frequencies

- Nominal frequency settling time

- Improving frequency settling time

- Trimming frequency

## 8.4.1 Switching Clock Sources

Switching from one clock source to another requires both clock sources to be enabled and stable. A simple flow requires:

- Enable desired clock source

- Wait for it to become stable

- Switch clocks

- Disable previous clock source

The key point to remember in this flow is that the clock source cannot be switched (CS cannot be written) unless the desired clock is on and stable. A short assembly code example of how to employ this flow is shown in Figure 8-9. This code is for illustrative purposes only and does not represent valid syntax for any particular assembler.

#### Internal Clock Generator (ICG) Module

#### ICGON — Internal Clock Generator On Bit

This read/write bit enables the internal clock generator. ICGON can be cleared when the CS bit has been set and the CMON bit has been clear for at least one bus cycle. ICGON is forced set when the CMON bit is set, the CS bit is clear, or during reset.

- 1 = Internal clock generator enabled

- 0 = Internal clock generator disabled

#### ICGS — Internal Clock Generator Stable Bit

This read-only bit indicates when the internal clock generator has determined that the internal clock (ICLK) is within about 5 percent of the desired value. This bit is forced clear when the clock monitor determines the ICLK is inactive, when ICGON is clear, when the ICG multiplier register (ICGMR) is written, when the ICG TRIM register (ICGTR) is written, during stop mode with OSCENINSTOP low, or during reset.

- 1 = Internal clock is within 5 percent of the desired value.

- 0 = Internal clock may not be within 5 percent of the desired value.

#### ECGON — External Clock Generator On Bit

This read/write bit enables the external clock generator. ECGON can be cleared when the CS and CMON bits have been clear for at least one bus cycle. ECGON is forced set when the CMON bit or the CS bit is set. ECGON is forced clear during reset.

- 1 = External clock generator enabled

- 0 = External clock generator disabled

#### ECGS — External Clock Generator Stable Bit

This read-only bit indicates when at least 4096 external clock (ECLK) cycles have elapsed since the external clock generator was enabled. This is not an assurance of the stability of ECLK but is meant to provide a startup delay. This bit is forced clear when the clock monitor determines ECLK is inactive, when ECGON is clear, during stop mode with OSCENINSTOP low, or during reset.

1 = 4096 ECLK cycles have elapsed since ECGON was set.

0 = External clock is unstable, inactive, or disabled.

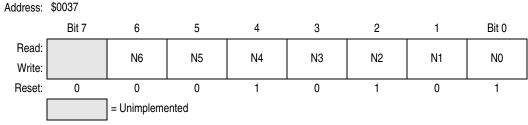

### 8.7.2 ICG Multiplier Register

Figure 8-12. ICG Multiplier Register (ICGMR)

#### N6:N0 — ICG Multiplier Factor Bits

These read/write bits change the multiplier used by the internal clock generator. The internal clock (ICLK) will be:

(307.2 kHz ± 25 percent) \* N

A value of \$00 in this register is interpreted the same as a value of \$01. This register cannot be written when the CMON bit is set. Reset sets this factor to \$15 (decimal 21) for default frequency of 6.45 MHz  $\pm$  25 percent (1.613 MHz  $\pm$  25 percent bus).

Keyboard Interrupt (KBD) Module

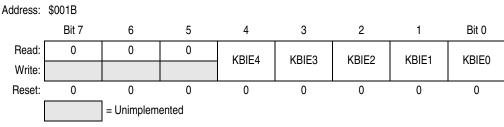

## 10.7.2 Keyboard Interrupt Enable Register

The keyboard interrupt enable register enables or disables each port A pin to operate as a keyboard interrupt pin.

Figure 10-4. Keyboard Interrupt Enable Register (KBIER)

## KBIE4–KBIE0 — Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch interrupt requests. Reset clears the keyboard interrupt enable register.

1 = KBDx pin enabled as keyboard interrupt pin

0 = KBDx pin not enabled as keyboard interrupt pin

**I/O Registers**

### NF — Receiver Noise Flag Bit

This clearable, read-only bit is set when the ESCI detects noise on the RxD pin. NF generates an NF CPU interrupt request if the NEIE bit in SCC3 is also set. Clear the NF bit by reading SCS1 and then reading the SCDR. Reset clears the NF bit.

1 = Noise detected

0 = No noise detected

### FE — Receiver Framing Error Bit

This clearable, read-only bit is set when a 0 is accepted as the stop bit. FE generates an ESCI error CPU interrupt request if the FEIE bit in SCC3 also is set. Clear the FE bit by reading SCS1 with FE set and then reading the SCDR. Reset clears the FE bit.

1 = Framing error detected

0 = No framing error detected

### PE — Receiver Parity Error Bit

This clearable, read-only bit is set when the ESCI detects a parity error in incoming data. PE generates a PE CPU interrupt request if the PEIE bit in SCC3 is also set. Clear the PE bit by reading SCS1 with PE set and then reading the SCDR. Reset clears the PE bit.

1 = Parity error detected

0 = No parity error detected

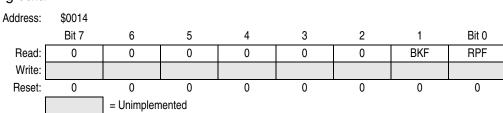

### 13.8.5 ESCI Status Register 2

ESCI status register 2 (SCS2) contains flags to signal these conditions:

- Break character detected

- Incoming data

Figure 13-14. ESCI Status Register 2 (SCS2)

#### **BKF** — Break Flag Bit

This clearable, read-only bit is set when the ESCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

1 = Break character detected

0 = No break character detected

### **RPF** — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch), or when the receiver detects an idle character. Polling RPF before disabling the ESCI module or entering stop mode can show whether a reception is in progress.

1 = Reception in progress

0 = No reception in progress

## 13.9 ESCI Arbiter

The ESCI module comprises an arbiter module designed to support software for communication tasks as bus arbitration, baud rate recovery and break time detection. The arbiter module consists of an 9-bit counter with 1-bit overflow and control logic. The CPU can control operation mode via the ESCI arbiter control register (SCIACTL).

## 13.9.1 ESCI Arbiter Control Register

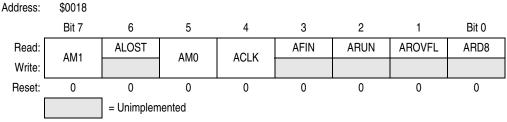

Figure 13-18. ESCI Arbiter Control Register (SCIACTL)

#### AM1 and AM0 — Arbiter Mode Select Bits

As shown in Table 13-12, these read/write bits select the mode of the arbiter module. Reset clears AM1 and AM0.

#### Table 13-12. ESCI Arbiter Selectable Modes

| AM[1:0] | ESCI Arbiter Mode     |

|---------|-----------------------|

| 0 0     | Idle / counter reset  |

| 0 1     | Bit time measurement  |

| 1 0     | Bus arbitration       |

| 1 1     | Reserved / do not use |

### ALOST — Arbitration Lost Flag

This read-only bit indicates loss of arbitration. Clear ALOST by writing a 0 to AM1. Reset clears ALOST.

### ACLK — Arbiter Counter Clock Select Bit

This read/write bit selects the arbiter counter clock source. Reset clears ACLK.

- 1 = Arbiter counter is clocked with one quarter of the ESCI input clock generated by the ESCI prescaler.

- 0 = Arbiter counter is clocked with the bus clock divided by four

#### NOTE

For ACLK=1, the Arbiter input clock is driven from the ESCI prescaler. The prescaler can be clocked by either the bus clock or CGMXCLK depending on the state of the ESCIBDSRC bit in CONFIG2.

### AFIN— Arbiter Bit Time Measurement Finish Flag

This read-only bit indicates bit time measurement has finished. Clear AFIN by writing any value to SCIACTL. Reset clears AFIN.

1 = Bit time measurement has finished

0 = Bit time measurement not yet finished

#### System Integration Module (SIM)

### 14.3.2.6 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the V<sub>DD</sub> voltage falls to the V<sub>TRIPF</sub> voltage. The LVI bit in the SIM reset status register (SRSR) is set and a chip reset is asserted if the LVIPWRD and LVIRSTD bits in the CONFIG register are at 0. The MCU is held in reset until V<sub>DD</sub> rises above V<sub>TRIPR</sub>. The MCU remains in reset until the SIM counts 4096 CGMXCLK to begin a reset recovery. Another 64 CGMXCLK cycles later, the CPU is released from reset to allow the reset vector sequence to occur. See Chapter 11 Low-Voltage Inhibit (LVI) Module.

## 14.4 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as a prescaler for the computer operating properly module (COP). The SIM counter overflow supplies the clock for the COP module. The SIM counter is 12 bits long and is clocked by the falling edge of CGMXCLK.

## 14.4.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit asserts the signal PORRST. Once the SIM is initialized, it enables the internal clock generator to drive the bus clock state machine.

## 14.4.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the configuration register. If the SSREC bit is a 1, then the stop recovery is reduced from the normal delay of 4096 CGMXCLK cycles down to 32 CGMXCLK cycles.

### 14.4.3 SIM Counter and Reset States

The SIM counter is free-running after all reset states. See 14.3.2 Active Resets from Internal Sources for counter control and internal reset recovery sequences.

## 14.5 Program Exception Control

Normal, sequential program execution can be changed in two ways:

- 1. Interrupts

- a. Maskable hardware CPU interrupts

- b. Non-maskable software interrupt instruction (SWI)

- 2. Reset

#### System Integration Module (SIM)

### 14.5.3 Break Interrupts

The break module can stop normal program flow at a software-programmable break point by asserting its break interrupt output. See 19.2 Break Module (BRK). The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

## 14.5.4 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the SIM break flag control register (SBFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

## 14.6 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur. Low-power modes are exited via an interrupt or reset.

### 14.6.1 Wait Mode

In wait mode, the CPU clocks are inactive while one set of peripheral clocks continues to run. Figure 14-11 shows the timing for wait mode entry.

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset. If the COP disable bit, COPD, in the configuration register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

| IAB | WAIT ADDR | WAIT ADDR + 1  | SAME  | χ    | SAME |

|-----|-----------|----------------|-------|------|------|

| IDB | PREVIOU   | IS DATA NEXT O | PCODE | SAME | SAME |

| R/W |           | Y              |       |      |      |

Note: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 14-11. Wait Mode Entry Timing

# Chapter 16 Timebase Module (TBM)

## 16.1 Introduction

This section describes the timebase module (TBM). The TBM will generate periodic interrupts at user selectable rates using a counter clocked by either the internal or external clock sources. This TBM version uses 15 divider stages, eight of which are user selectable.

### NOTE

The TBM on this device differs from that of the MC68HC908KX8 in that it has an additional divide-by-128 at the front end of the divider chain.

For further information regarding timers on M68HC08 family devices, please consult the *HC08 Timer Reference Manual*, Freescale order number TIM08RM/AD.

## 16.2 Features

Features of the TBM module include:

- Software configurable periodic interrupts with divide-by-1024, 2048, 4096, 8192, 16384, 262144, 1048576, and 4194304 taps of the selected clock source

- Configurable for operation during stop mode to allow periodic wake up from stop

## **16.3 Functional Description**

This module can generate a periodic interrupt by dividing the clock source supplied from the internal clock generator module, TBMCLK. Note that this clock source is the external clock ECLK when the ECGON bit in the ICG control register (ICGCR) is set. Otherwise, TBMCLK is driven at the internally generated clock frequency (ICLK). In other words, if the external clock is enabled it will be used as the TBMCLK, even if the MCU bus clock is based on the internal clock.

The counter is initialized to all 0s when TBON bit is cleared. The counter, shown in Figure 16-1, starts counting when the TBON bit is set. When the counter overflows at the tap selected by TBR2–TBR0, the TBIF bit gets set. If the TBIE bit is set, an interrupt request is sent to the CPU. The TBIF flag is cleared by writing a 1 to the TACK bit. The first time the TBIF flag is set after enabling the timebase module, the interrupt is generated at approximately half of the overflow period. Subsequent events occur at the exact period.

The timebase module may remain active after execution of the STOP instruction if the internal clock generator has been enabled to operate during stop mode through the OSCENINSTOP bit in the configuration register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

#### Timer Interface B (TIMB) Module

occurs, user software can respond to this event at a later time and determine the actual time of the event. However, this must be done prior to another input capture on the same pin; otherwise, the previous time value will be lost.

By recording the times for successive edges on an incoming signal, software can determine the period and/or pulse width of the signal. To measure a period, two successive edges of the same polarity are captured. To measure a pulse width, two alternate polarity edges are captured. Software should track the overflows at the 16-bit module counter to extend its range.

Another use for the input capture function is to establish a time reference. In this case, an input capture function is used in conjunction with an output compare function. For example, to activate an output signal a specified number of clock cycles after detecting an input event (edge), use the input capture function to record the time at which the edge occurred. A number corresponding to the desired delay is added to this captured value and stored to an output compare register (see 18.8.5 TIMB Channel Registers). Because both input captures and output compares are referenced to the same 16-bit modulo counter, the delay can be controlled to the resolution of the counter independent of software latencies.

Reset does not affect the contents of the input capture channel register (TBCHxH-TBCHxL).

## 18.3.3 Output Compare

With the output compare function, the TIMB can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIMB can set, clear, or toggle the channel pin. Output compares can generate TIMB CPU interrupt requests.

### 18.3.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 18.3.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIMB channel registers.

An unsynchronized write to the TIMB channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIMB overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIMB may pass the new value before it is written.

Use these methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current output compare pulse. The interrupt routine has until the end of the counter overflow period to write the new value.

- When changing to a larger output compare value, enable TIMB overflow interrupts and write the new value in the TIMB overflow interrupt routine. The TIMB overflow interrupt occurs at the end of the current counter overflow period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same counter overflow period.

### 18.3.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use this initialization procedure:

- 1. In the TIMB status and control register (TBSC):

- a. Stop the TIMB counter by setting the TIMB stop bit, TSTOP.

- b. Reset the TIMB counter prescaler by setting the TIMB reset bit, TRST.

- 2. In the TIMB counter modulo registers (TBMODH–TBMODL), write the value for the required PWM period.

- 3. In the TIMB channel x registers (TBCHxH–TBCHxL), write the value for the required pulse width.

- 4. In TIMB channel x status and control register (TBSCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB–MSxA. See Table 18-2.

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (to clear output on compare) or 1:1 (to set output on compare) to the edge/level select bits, ELSxB–ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 18-2.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIMB status control register (TBSC), clear the TIMB stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIMB channel 0 registers (TBCH0H–TBCH0L) initially control the buffered PWM output. TIMB status control register 0 (TBSC0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIMB overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 18.8.4 TIMB Channel Status and Control Registers.

## 18.4 Interrupts

These TIMB sources can generate interrupt requests:

- TIMB overflow flag (TOF) The TOF bit is set when the TIMB counter reaches the modulo value programmed in the TIMB counter modulo registers. The TIMB overflow interrupt enable bit, TOIE, enables TIMB overflow CPU interrupt requests. TOF and TOIE are in the TIMB status and control register.

- TIMB channel flags (CH1F–CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIMB CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE.

#### **Monitor Module (MON)**

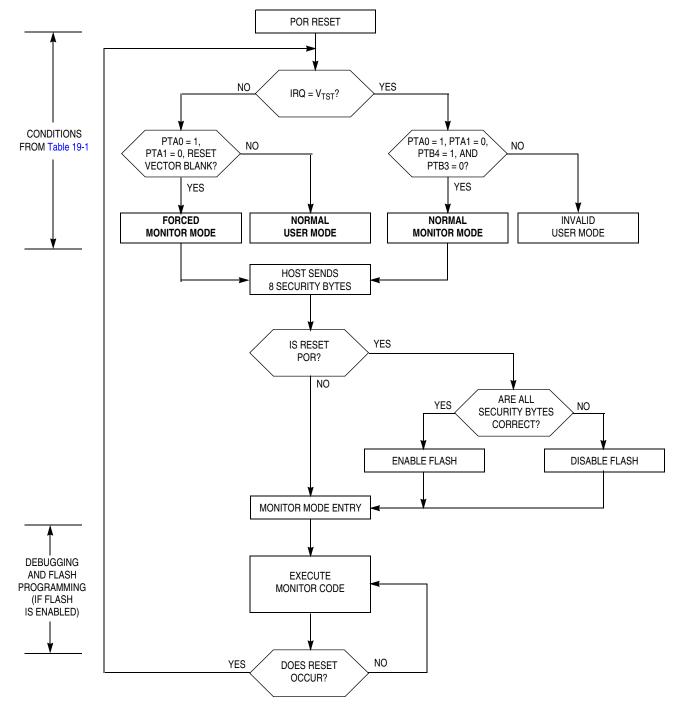

Figure 19-8. Simplified Monitor Mode Entry Flowchart

- **logic 0** A voltage level approximately equal to the ground voltage ( $V_{SS}$ ).

- **Iow byte** The least significant eight bits of a word.

- **low voltage inhibit module (LVI)** A module in the M68HC08 Family that monitors power supply voltage.

- LVI See "low voltage inhibit module (LVI)."

- M68HC08 A Freescale family of 8-bit MCUs.

- mark/space The logic 1/logic 0 convention used in formatting data in serial communication.

- **mask** 1. A logic circuit that forces a bit or group of bits to a desired state. 2. A photomask used in integrated circuit fabrication to transfer an image onto silicon.

- mask option A optional microcontroller feature that the customer chooses to enable or disable.

- **mask option register (MOR)** An EPROM location containing bits that enable or disable certain MCU features.

- MCU Microcontroller unit. See "microcontroller."

- memory location Each M68HC08 memory location holds one byte of data and has a unique address. To store information in a memory location, the CPU places the address of the location on the address bus, the data information on the data bus, and asserts the write signal. To read information from a memory location, the CPU places the address of the location on the address bus and asserts the read signal. In response to the read signal, the selected memory location places its data onto the data bus.

- memory map A pictorial representation of all memory locations in a computer system.

- **microcontroller** Microcontroller unit (MCU). A complete computer system, including a CPU, memory, a clock oscillator, and input/output (I/O) on a single integrated circuit.

- **modulo counter** A counter that can be programmed to count to any number from zero to its maximum possible modulus.

- **monitor ROM** A section of ROM that can execute commands from a host computer for testing purposes.

- MOR See "mask option register (MOR)."

- most significant bit (MSB) The leftmost digit of a binary number.

- **multiplexer** A device that can select one of a number of inputs and pass the logic level of that input on to the output.

- N The negative bit in the condition code register of the CPU08. The CPU sets the negative bit when an arithmetic operation, logical operation, or data manipulation produces a negative result.

- **nibble** A set of four bits (half of a byte).

- **object code** The output from an assembler or compiler that is itself executable machine code, or is suitable for processing to produce executable machine code.

## Changes from Rev 7.0 published in March 2004 to Rev 8 published in July 2005

| Section                                                        | Page (in Rev 8)                                                       | Description of change                                                                                                                                                                      |

|----------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory                                                         | 26 on                                                                 | Added ICGT at \$FF80 in Figure 2-1 and Figure 2-2.                                                                                                                                         |

| Internal Clock                                                 | 80                                                                    | Removed overbars from OSC1 and OSC2 in Figure 8-1.                                                                                                                                         |

| Generator (ICG)<br>Module                                      | 103                                                                   | Added 8.7.4 ICG Trim Value.                                                                                                                                                                |

|                                                                | 117                                                                   | New introductory paragraph in 11.3 Functional Description. Modified sections 11.3.1, 11.3.2, 11.5.1, 11.5.2.                                                                               |

| Low-Voltage Inhibit<br>(LVI) Module                            | 118                                                                   | Changed "to disable LVI resets" to "to enable LVI resets" in 11.3.1 Polled LVI<br>Operation.<br>Deleted "for 32 to 40 CGMXCLK cycles" from last sentence in 11.3.4 LVI<br>Status Register. |

| Input/Output (I/O)<br>Ports (PORTS) 129 Modified Figure 12-13. |                                                                       | Modified Figure 12-13.                                                                                                                                                                     |

| Enhanced Serial                                                | 158                                                                   | Changed "11-bit" to "13-bit" and "12-bit" to "14-bit" in Table 13-6.                                                                                                                       |

| Communications<br>Interface (ESCI)<br>Module                   | 163, 164                                                              | Changed "is clocked with one half to " is clocked with one quarter "                                                                                                                       |

| System Integration                                             | 170                                                                   | New introductory paragraph in 14.3.1 External Pin Reset.                                                                                                                                   |

| Module (SIM)                                                   | 170                                                                   | Updated and moved Table 14-2.                                                                                                                                                              |

| Serial Peripheral<br>Interface (SPI)<br>Module                 | 186 Changed SS pin to from input/output to input only in Figure 15-2. |                                                                                                                                                                                            |

|                                                                | 216                                                                   | Changed PTEx/TCHx to PTDx/TCHx in Figure 17-3.                                                                                                                                             |

| Timer Interface A<br>(TIMA) Module                             | 221                                                                   | Added para to note after TSTOP — TIMA Stop Bit                                                                                                                                             |

|                                                                | 225                                                                   | New Table 17-2.                                                                                                                                                                            |

|                                                                | 232                                                                   | Changed "TCHxH-TCHxL" to "TBCHxH-TBCHxL" in 18.3.2 Input Capture.                                                                                                                          |

| Timer Interface B                                              | 234                                                                   | Changed PTEx/TCHx to PTBx/TCHx in Figure 18-3.                                                                                                                                             |

| (TIMB) Module                                                  | 239                                                                   | Added para to note after TSTOP — TIMB Stop Bit                                                                                                                                             |

|                                                                | 243                                                                   | New Table 18-2.                                                                                                                                                                            |

| Development Support                                            | 247                                                                   | Whole chapter replaced with new version.                                                                                                                                                   |

| Flootrical                                                     | 267                                                                   | Changed values of Hi-Z leakage current in 20.5 DC Electrical Characteristics.                                                                                                              |

| Electrical<br>Specifications                                   | 269                                                                   | Changed specification for resistance and capacitance values for<br>EXTSLOW = 1 and EXTSLOW = 0, in 20.8 External Oscillator<br>Characteristics.                                            |

| Appendix A<br>MC68HC908EY8                                     | 279                                                                   | Added appendix describing the MC68HC908EY8                                                                                                                                                 |