Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Data ila                   |                                                           |

|----------------------------|-----------------------------------------------------------|

| Details                    |                                                           |

| Product Status             | Active                                                    |

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | LINbus, SCI, SPI                                          |

| Peripherals                | POR, PWM                                                  |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 32-LQFP                                                   |

| Supplier Device Package    | 32-LQFP (7x7)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908ey8cfae |

## **List of Chapters**

| Chapter 1    | General Description19                                     |

|--------------|-----------------------------------------------------------|

| Chapter 2    | Memory                                                    |

| Chapter 3    | Analog-to-Digital Converter (ADC) Module                  |

| Chapter 4    | BEMF Counter Module (BEMF)55                              |

| Chapter 5    | Configuration Registers (CONFIG1 and CONFIG2)             |

| Chapter 6    | Computer Operating Properly (COP) Module                  |

| Chapter 7    | Central Processor Unit (CPU)                              |

| Chapter 8    | Internal Clock Generator (ICG) Module77                   |

| Chapter 9    | External Interrupt (IRQ)101                               |

| Chapter 10   | Keyboard Interrupt (KBD) Module                           |

| Chapter 11   | Low-Voltage Inhibit (LVI) Module111                       |

| Chapter 12   | Input/Output (I/O) Ports (PORTS)                          |

| Chapter 13   | Enhanced Serial Communications Interface (ESCI) Module125 |

| Chapter 14   | System Integration Module (SIM)155                        |

| Chapter 15   | Serial Peripheral Interface (SPI) Module169               |

| Chapter 16   | Timebase Module (TBM)189                                  |

| Chapter 17   | Timer Interface A (TIMA) Module193                        |

| Chapter 18   | Timer Interface B (TIMB) Module209                        |

| Chapter 19   | Development Support                                       |

| Chapter 20   | Electrical Specifications241                              |

| Chapter 21   | Ordering Information and Mechanical Specifications        |

| Appendix A   | MC68HC908EY8255                                           |

| Glossary     | 259                                                       |

| Revision His | story                                                     |

MC68HC908EY16 • MC68HC908EY8 Data Sheet, Rev. 10

## Chapter 5 Configuration Registers (CONFIG1 and CONFIG2)

| 5.1            | Introduction                             | 57  |

|----------------|------------------------------------------|-----|

| 5.2            | Functional Description                   | 57  |

|                | Chapter 6                                |     |

|                | Computer Operating Properly (COP) Module |     |

| 6.1            | Introduction                             | 61  |

| 6.2            | Functional Description                   | 61  |

| 6.3            | I/O Signals                              | 62  |

| 6.3.1          | CGMXCLK                                  |     |

| 6.3.2          | STOP Instruction                         |     |

| 6.3.3          | COPCTL Write                             |     |

| 6.3.4          | Power-On Reset.                          |     |

| 6.3.5          | Internal Reset                           |     |

| 6.3.6<br>6.3.7 | Reset Vector Fetch                       |     |

| 6.3.8          | COPRS                                    |     |

| 6.4            | COP Control Register                     |     |

| 6.5            | Interrupts                               |     |

| 6.6            | Monitor Mode                             |     |

| 6.7            | Low-Power Modes                          |     |

| 6.7.1          | Wait Mode                                |     |

| 6.7.2          | Stop Mode                                |     |

| 6.8            | COP Module During Break Interrupts       | 63  |

|                | Chapter 7                                |     |

|                | Central Processor Unit (CPU)             |     |

| 7.1            | Introduction                             | 65  |

| 7.2            | Features                                 | 65  |

| 7.3            | CPU Registers                            | 65  |

| 7.3.1          | Accumulator                              |     |

| 7.3.2          | Index Register                           |     |

| 7.3.3          | Stack Pointer                            | 67  |

| 7.3.4          | Program Counter                          |     |

| 7.3.5          | Condition Code Register                  |     |

| 7.4            | Arithmetic/Logic Unit (ALU)              |     |

| 7.5<br>7.5.1   | Low-Power Modes                          |     |

| 7.5.1          | Stop Mode                                |     |

| 7.6            | CPU During Break Interrupts              |     |

| 7.7            | Instruction Set Summary                  |     |

| 7.7            | Opcode Map                               |     |

| 7.0            | Opocoo Map                               | , 5 |

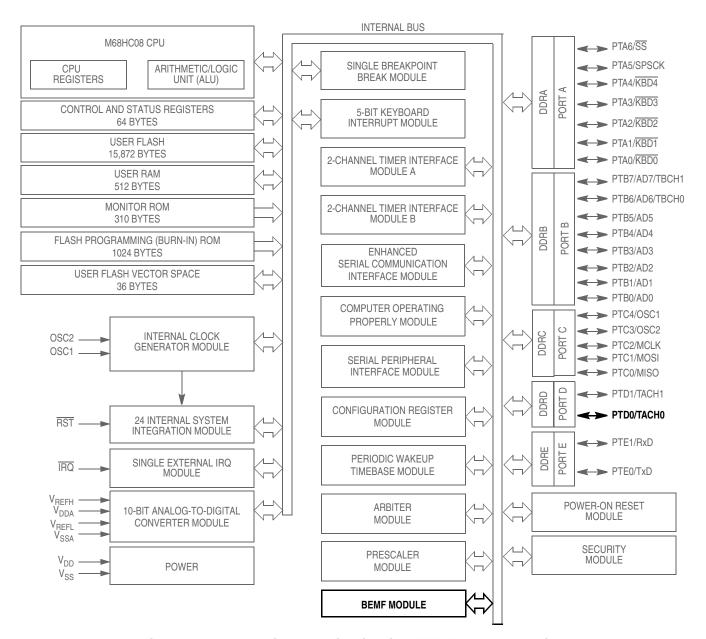

**General Description**

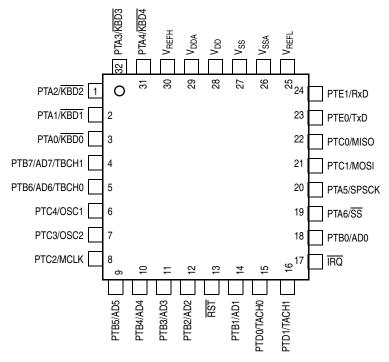

## 1.4 Pin Assignments

Figure 1-2 shows the pin assignments for the MC68HC908EY16.

Figure 1-2. Pin Assignments

#### 1.5 Pin Functions

Descriptions of the pin functions are provided here.

## 1.5.1 Power Supply Pins ( $V_{DD}$ and $V_{SS}$ )

$V_{DD}$  and  $V_{SS}$  are the power supply and ground pins. The MCU operates from a single power supply.

Fast signal transitions on MCU pins place high, short-duration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU as Figure 1-3 shows. Place the C1 bypass capacitor as close to the MCU as possible. Use a high-frequency-response ceramic capacitor for C1. C2 is an optional bulk current bypass capacitor for use in applications that require the port pins to source high current levels.

#### **BEMF Counter Module (BEMF)**

#### 4.5.2 Stop Mode

The BEMF module is inactive after execution of the STOP instruction. In STOP mode the BEMF register is not accessible by the CPU.

Figure 4-2. Block Diagram Highlighting BEMF Block and Pins

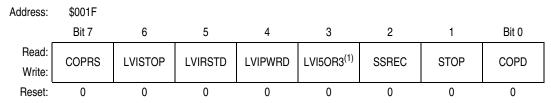

#### **Configuration Registers (CONFIG1 and CONFIG2)**

1. The LVI5OR3 bit is cleared only by a power-on reset (POR).

Figure 5-2. Configuration Register 1 (CONFIG1)

#### ESCIBDSRC — ESCI Baud Rate Clock Source Bit

ESCIBDSRC controls the clock source used for the ESCI. The setting of the bit affects the frequency at which the ESCI operates.

- 1 = Internal data bus clock used as clock source for ESCI

- 0 = CGMXCLK used as clock source for ESCI

#### **EXTXTALEN** — External Crystal Enable Bit

EXTXTALEN enables the external oscillator circuits to be configured for a crystal configuration where the PTC4/OSC1 and PTC3/OSC2 pins are the connections for an external crystal.

#### NOTE

This bit does not function without setting the EXTCLKEN bit also.

Clearing the EXTXTALEN bit (default setting) allows the PTC3/OSC2 pin to function as a general-purpose I/O pin. Refer to Table 5-1 for configuration options for the external source. See Chapter 8 Internal Clock Generator (ICG) Module for a more detailed description of the external clock operation.

|          | al Clock<br>ation Bits | Pin Fu    | nction    | Description                                                                                                                                            |

|----------|------------------------|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTCLKEN | EXTXTALEN              | PTC4/OSC1 | PTC3/OSC2 | ·                                                                                                                                                      |

| 0        | 0                      | PTC4      | PTC3      | Default setting — external oscillator disabled                                                                                                         |

| 0        | 1                      | PTC4      | PTC3      | External oscillator disabled since EXTCLKEN not set                                                                                                    |

| 1        | 0                      | OSC1      | PTC3      | External oscillator configured for an external clock source input (square wave) on OSC1                                                                |

| 1        | 1                      | OSC1      | OSC2      | External oscillator configured for an external crystal configuration on OSC1 and OSC2. System will also operate with square-wave clock source in OSC1. |

**Table 5-1. External Clock Option Settings**

EXTXTALEN, when set, also configures the clock monitor to expect an external clock source in the valid range of crystals (30 kHz to 100 kHz or 1 MHz to 8 MHz). When EXTXTALEN is clear, the clock monitor will expect an external clock source in the valid range for externally generated clocks when using the clock monitor (60 Hz to 32 MHz).

EXTXTALEN, when set, also configures the external clock stabilization divider in the clock monitor for a 4096-cycle timeout to allow the proper stabilization time for a crystal. When EXTXTALEN is clear, the stabilization divider is configured to 16 cycles since an external clock source does not need a startup time.

- 1 = Allows PTC3/OSC2 to be an external crystal connection.

- 0 = PTC3/OSC2 functions as an I/O port pin (default).

#### MC68HC908EY16 • MC68HC908EY8 Data Sheet, Rev. 10

#### **Computer Operating Properly (COP) Module**

an overflow occurs prevents a COP reset by clearing the COP counter and stages 4–12 of the SIM counter.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the RST pin low for 32 CGMXCLK cycles and sets the COP bit in the reset status register (RSR).

In monitor mode, the COP is disabled if the  $\overline{RST}$  pin or the  $\overline{IRQ}$  pin is held at  $V_{TST}$ . During the break state,  $V_{TST}$  on the  $\overline{RST}$  pin disables the COP.

#### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

### 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

#### 6.3.1 CGMXCLK

CGMXCLK is the crystal oscillator output signal. CGMXCLK frequency is equal to the crystal frequency.

#### 6.3.2 STOP Instruction

The STOP instruction signal clears the COP prescaler.

#### 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see 6.4 COP Control Register) clears the COP counter and clears stages 12 through 4 of the COP prescaler. Reading the COP control register returns the reset vector.

#### 6.3.4 Power-On Reset

The power-on reset (POR) circuit clears the COP prescaler 4096 CGMXCLK cycles after power-up.

#### 6.3.5 Internal Reset

An internal reset clears the COP prescaler and the COP counter.

#### 6.3.6 Reset Vector Fetch

A reset vector fetch occurs when the vector address appears on the data bus. A reset vector fetch clears the COP prescaler.

#### 6.3.7 COPD

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register. See Chapter 5 Configuration Registers (CONFIG1 and CONFIG2).

MC68HC908EY16 • MC68HC908EY8 Data Sheet, Rev. 10

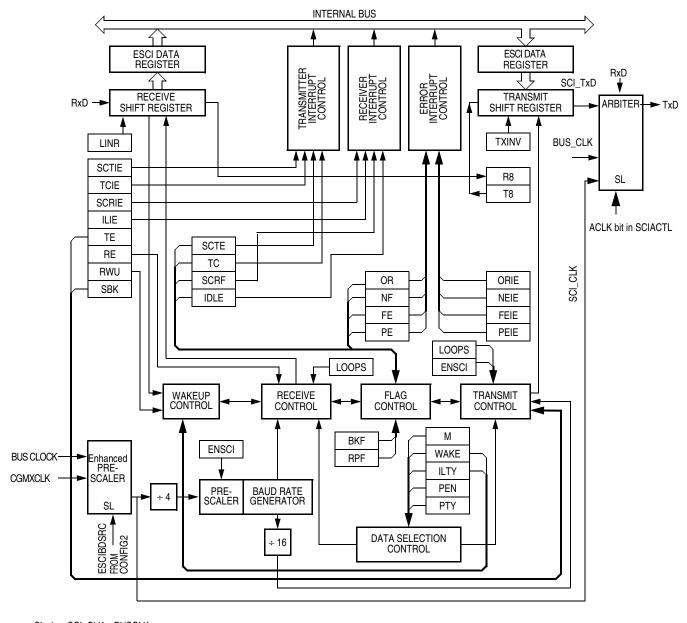

# **Chapter 13 Enhanced Serial Communications Interface (ESCI) Module**

#### 13.1 Introduction

The enhanced serial communications interface (ESCI) module allows asynchronous communications with peripheral devices and other microcontroller units (MCU).

#### 13.2 Features

Features include:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- Programmable baud rates

- Programmable 8-bit or 9-bit character length

- Separately enabled transmitter and receiver

- Separate receiver and transmitter central processor unit (CPU) interrupt requests

- Programmable transmitter output polarity

- Two receiver wakeup methods:

- Idle line wakeup

- address mark wakeup

- Interrupt-driven operation with eight interrupt flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

#### 13.3 Pin Name Conventions

The generic names of the ESCI input/output (I/O) pins are:

- RxD (receive data)

- TxD (transmit data)

125

### 13.4 Functional Description

Figure 13-2 shows the structure of the ESCI module. The ESCI allows full-duplex, asynchronous, NRZ serial communication between the MCU and remote devices, including other MCUs. The transmitter and receiver of the ESCI operate independently, although they use the same baud rate generator. During normal operation, the CPU monitors the status of the ESCI, writes the data to be transmitted, and processes received data.

The baud rate clock source for the ESCI can be selected via the configuration bit, ESCIBDSRC, of the CONFIG2 register (\$001E).

SL=1 -> SCI\_CLK = BUSCLK SL=0 -> SCI\_CLK = CGMXCLK (4x BUSCLK)

Figure 13-2. ESCI Module Block Diagram

MC68HC908EY16 • MC68HC908EY8 Data Sheet, Rev. 10

#### **Enhanced Serial Communications Interface (ESCI) Module**

Receiving a break character has these effects on ESCI registers:

- Sets the framing error bit (FE) in SCS1

- Sets the ESCI receiver full bit (SCRF) in SCS1

- Clears the ESCI data register (SCDR)

- Clears the R8 bit in SCC3

- Sets the break flag bit (BKF) in SCS2

- May set the overrun (OR), noise flag (NF), parity error (PE), or reception in progress flag (RPF) bits

#### 13.4.2.4 Idle Characters

For TXINV = 0 (output not inverted), a transmitted idle character contains all 1s and has no start, stop, or parity bit. Idle character length depends on the M bit in SCC1. The preamble is a synchronizing idle character that begins every transmission.

If the TE bit is cleared during a transmission, the TxD pin becomes idle after completion of the transmission in progress. Clearing and then setting the TE bit during a transmission queues an idle character to be sent after the character currently being transmitted.

#### NOTE

When a break sequence is followed immediately by an idle character, this SCI design exhibits a condition in which the break character length is reduced by one half bit time. In this instance, the break sequence will consist of a valid start bit, eight or nine data bits (as defined by the M bit in SCC1) of 0 and one half data bit length of 0 in the stop bit position followed immediately by the idle character. To ensure a break character of the proper length is transmitted, always queue up a byte of data to be transmitted while the final break sequence is in progress.

When queueing an idle character, return the TE bit to 1 before the stop bit of the current character shifts out to the TxD pin. Setting TE after the stop bit appears on TxD causes data previously written to the SCDR to be lost. A good time to toggle the TE bit for a queued idle character is when the SCTE bit becomes set and just before writing the next byte to the SCDR.

#### 13.4.2.5 Inversion of Transmitted Output

The transmit inversion bit (TXINV) in ESCI control register 1 (SCC1) reverses the polarity of transmitted data. All transmitted values including idle, break, start, and stop bits, are inverted when TXINV is at 1. See 13.8.1 ESCI Control Register 1.

#### 13.4.2.6 Transmitter Interrupts

These conditions can generate CPU interrupt requests from the ESCI transmitter:

- ESCI transmitter empty (SCTE) The SCTE bit in SCS1 indicates that the SCDR has transferred a character to the transmit shift register. SCTE can generate a transmitter CPU interrupt request. Setting the ESCI transmit interrupt enable bit, SCTIE, in SCC2 enables the SCTE bit to generate transmitter CPU interrupt requests.

- Transmission complete (TC) The TC bit in SCS1 indicates that the transmit shift register and the SCDR are empty and that no break or idle character has been generated. The transmission complete interrupt enable bit, TCIE, in SCC2 enables the TC bit to generate transmitter CPU interrupt requests.

MC68HC908EY16 • MC68HC908EY8 Data Sheet, Rev. 10

| Table 13-5. Character Format Selecti | ıon | า |

|--------------------------------------|-----|---|

|--------------------------------------|-----|---|

| Control Bits |         | Character Format |           |        |           |                  |

|--------------|---------|------------------|-----------|--------|-----------|------------------|

| М            | PEN:PTY | Start Bits       | Data Bits | Parity | Stop Bits | Character Length |

| 0            | 0 X     | 1                | 8         | None   | 1         | 10 bits          |

| 1            | 0 X     | 1                | 9         | None   | 1         | 11 bits          |

| 0            | 1 0     | 1                | 7         | Even   | 1         | 10 bits          |

| 0            | 1 1     | 1                | 7         | Odd    | 1         | 10 bits          |

| 1            | 1 0     | 1                | 8         | Even   | 1         | 11 bits          |

| 1            | 1 1     | 1                | 8         | Odd    | 1         | 11 bits          |

#### **WAKE** — Wakeup Condition Bit

This read/write bit determines which condition wakes up the ESCI: a 1 (address mark) in the MSB position of a received character or an idle condition on the RxD pin. Reset clears the WAKE bit.

- 1 = Address mark wakeup

- 0 = Idle line wakeup

#### ILTY — Idle Line Type Bit

This read/write bit determines when the ESCI starts counting 1s as idle character bits. The counting begins either after the start bit or after the stop bit. If the count begins after the start bit, then a string of 1s preceding the stop bit may cause false recognition of an idle character. Beginning the count after the stop bit avoids false idle character recognition, but requires properly synchronized transmissions. Reset clears the ILTY bit.

- 1 = Idle character bit count begins after stop bit

- 0 = Idle character bit count begins after start bit

#### PEN — Parity Enable Bit

This read/write bit enables the ESCI parity function (see Table 13-5). When enabled, the parity function inserts a parity bit in the MSB position (see Table 13-3). Reset clears the PEN bit.

- 1 = Parity function enabled

- 0 = Parity function disabled

#### PTY — Parity Bit

This read/write bit determines whether the ESCI generates and checks for odd parity or even parity (see Table 13-5). Reset clears the PTY bit.

- 1 = Odd parity

- 0 = Even parity

#### **NOTE**

Changing the PTY bit in the middle of a transmission or reception can generate a parity error.

System Integration Module (SIM)

#### 14.5.3 Break Interrupts

The break module can stop normal program flow at a software-programmable break point by asserting its break interrupt output. See 19.2 Break Module (BRK). The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

#### 14.5.4 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the SIM break flag control register (SBFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

#### 14.6 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur. Low-power modes are exited via an interrupt or reset.

#### 14.6.1 Wait Mode

In wait mode, the CPU clocks are inactive while one set of peripheral clocks continues to run. Figure 14-11 shows the timing for wait mode entry.

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset. If the COP disable bit, COPD, in the configuration register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

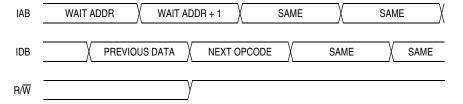

Note: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 14-11. Wait Mode Entry Timing

MC68HC908EY16 • MC68HC908EY8 Data Sheet, Rev. 10

# **Chapter 15 Serial Peripheral Interface (SPI) Module**

#### 15.1 Introduction

This section describes the serial peripheral interface (SPI) module, which allows full-duplex, synchronous, serial communications with peripheral devices.

#### 15.2 Features

Features of the SPI module include:

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four master mode frequencies (maximum = bus frequency ÷ 2)

- Maximum slave mode frequency = bus frequency

- Serial clock with programmable polarity and phase

- Two separately enabled interrupts with CPU service:

- SPRF (SPI receiver full)

- SPTE (SPI transmitter empty)

- Mode fault error flag with CPU interrupt capability

- · Overflow error flag with CPU interrupt capability

- Programmable wired-OR mode

- I<sup>2</sup>C (inter-integrated circuit) compatibility

## 15.3 Pin Name and Register Name Conventions

The generic names of the SPI input/output (I/O) pins are:

- SS (slave select)

- SPSCK (SPI serial clock)

- MOSI (master out slave in)

- MISO (master in slave out)

The SPI shares four I/O pins with a parallel I/O port. The full name of an SPI pin reflects the name of the shared port pin. Table 15-1 shows the full names of the SPI I/O pins. The generic pin names appear in the text that follows.

**Table 15-1. Pin Name Conventions**

| SPI Generic Pin Name | MISO      | MOSI      | SS      | SPSCK      |  |

|----------------------|-----------|-----------|---------|------------|--|

| Full SPI Pin Name    | PTC0/MISO | PTC1/MOSI | PTA6/SS | PTA5/SPSCK |  |

MC68HC908EY16 • MC68HC908EY8 Data Sheet, Rev. 10

Table 15-2. I/O Register Addresses

| Register Name                           | Address |

|-----------------------------------------|---------|

| SPI control register (SPCR)             | \$000D  |

| SPI status and control register (SPSCR) | \$000E  |

| SPI data register (SPDR)                | \$000F  |

## 15.4 Functional Description

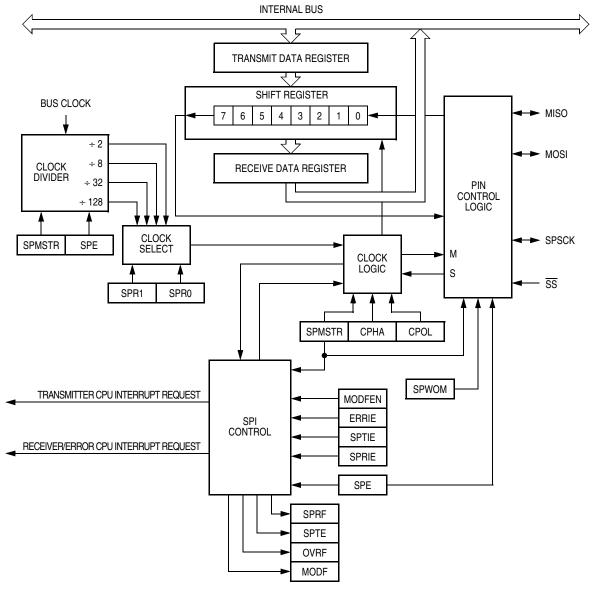

Figure 15-2 shows the structure of the SPI module.

Figure 15-2. SPI Module Block Diagram

MC68HC908EY16 • MC68HC908EY8 Data Sheet, Rev. 10

## Chapter 16 Timebase Module (TBM)

#### 16.1 Introduction

This section describes the timebase module (TBM). The TBM will generate periodic interrupts at user selectable rates using a counter clocked by either the internal or external clock sources. This TBM version uses 15 divider stages, eight of which are user selectable.

#### NOTE

The TBM on this device differs from that of the MC68HC908KX8 in that it has an additional divide-by-128 at the front end of the divider chain.

For further information regarding timers on M68HC08 family devices, please consult the *HC08 Timer Reference Manual*, Freescale order number TIM08RM/AD.

#### 16.2 Features

Features of the TBM module include:

- Software configurable periodic interrupts with divide-by-1024, 2048, 4096, 8192, 16384, 262144, 1048576, and 4194304 taps of the selected clock source

- Configurable for operation during stop mode to allow periodic wake up from stop

## 16.3 Functional Description

This module can generate a periodic interrupt by dividing the clock source supplied from the internal clock generator module, TBMCLK. Note that this clock source is the external clock ECLK when the ECGON bit in the ICG control register (ICGCR) is set. Otherwise, TBMCLK is driven at the internally generated clock frequency (ICLK). In other words, if the external clock is enabled it will be used as the TBMCLK, even if the MCU bus clock is based on the internal clock.

The counter is initialized to all 0s when TBON bit is cleared. The counter, shown in Figure 16-1, starts counting when the TBON bit is set. When the counter overflows at the tap selected by TBR2–TBR0, the TBIF bit gets set. If the TBIE bit is set, an interrupt request is sent to the CPU. The TBIF flag is cleared by writing a 1 to the TACK bit. The first time the TBIF flag is set after enabling the timebase module, the interrupt is generated at approximately half of the overflow period. Subsequent events occur at the exact period.

The timebase module may remain active after execution of the STOP instruction if the internal clock generator has been enabled to operate during stop mode through the OSCENINSTOP bit in the configuration register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

PWM function, and TIMA channel 1 status and control register (TASC1) is unused. While the MS0B bit is set, the channel 1 pin, PTD1/TACH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

#### 17.3.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use this initialization procedure:

- 1. In the TIMA status and control register (TASC):

- a. Stop the TIMA counter by setting the TIMA stop bit, TSTOP.

- b. Reset the TIMA counter prescaler by setting the TIMA reset bit, TRST.

- 2. In the TIMA counter modulo registers (TAMODH–TAMODL), write the value for the required PWM period.

- 3. In the TIMA channel x registers (TACHxH-TACHxL), write the value for the required pulse width.

- 4. In TIMA channel x status and control register (TASCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB–MSxA. See Table 17-2.

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (to clear output on compare) or 1:1 (to set output on compare) to the edge/level select bits, ELSxB–ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 17-2.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIMA status control register (TASC), clear the TIMA stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIMA channel 0 registers (TACH0H–TACH0L) initially control the buffered PWM output. TIMA status control register 0 (TASC0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIMA overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 17.8.4 TIMA Channel Status and Control Registers.

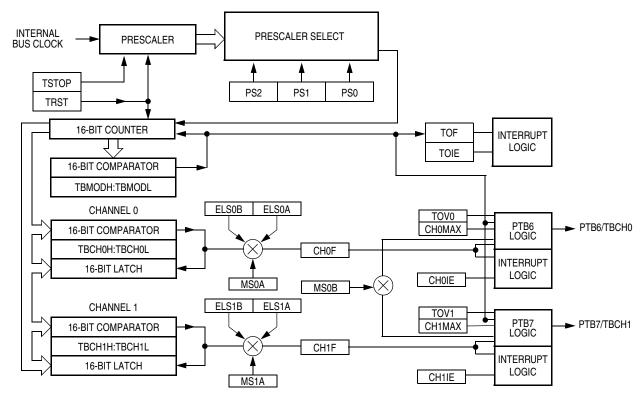

Figure 18-2. TIMB Block Diagram

#### 18.3.1 TIMB Counter Prescaler

The TIMB clock source can be one of the seven prescaler outputs. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIMB status and control register select the TIMB clock source.

#### 18.3.2 Input Capture

An input capture function has three basic parts: edge select logic, an input capture latch, and a 16-bit counter. Two 8-bit registers, which make up the 16-bit input capture register, are used to latch the value of the free-running counter after the corresponding input capture edge detector senses a defined transition. The polarity of the active edge is programmable. The level transition which triggers the counter transfer is defined by the corresponding input edge bits (ELSxB and ELSxA in TBSC0 through TBSC1 control registers with x referring to the active channel number). When an active edge occurs on the pin of an input capture channel, the TIMB latches the contents of the TIMB counter into the TIMB channel registers, TBCHxH–TBCHxL. Input captures can generate TIMB CPU interrupt requests. Software can determine that an input capture event has occurred by enabling input capture interrupts or by polling the status flag bit.

The free-running counter contents are transferred to the TIMB channel status and control register (TBCHxH–TBCHxL, see 18.8.5 TIMB Channel Registers) on each proper signal transition regardless of whether the TIMB channel flag (CH0F–CH1F in TBSC0–TBSC1 registers) is set or clear. When the status flag is set, a CPU interrupt is generated if enabled. The value of the count latched or "captured" is the time of the event. Because this value is stored in the input capture register 2 bus cycles after the actual event

## 18.8 I/O Registers

These I/O registers control and monitor TIMB operation:

- TIMB status and control register, TBSC

- TIMB control registers, TBCNTH-TBCNTL

- TIMB counter modulo registers, TBMODH–TBMODL

- TIMB channel status and control registers, TBSC0 and TBSC1

- TIMB channel registers, TBCH0H–TBCH0L and TBCH1H–TBCH1L

#### 18.8.1 TIMB Status and Control Register

The TIMB status and control register:

- Enables TIMB overflow interrupts

- Flags TIMB overflows

- Stops the TIMB counter

- Resets the TIMB counter

- Prescales the TIMB counter clock

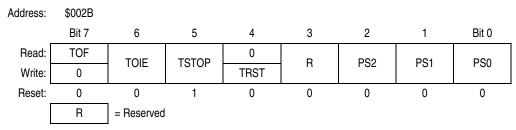

Figure 18-4. TIMB Status and Control Register (TBSC)

#### **TOF** — TIMB Overflow Flag Bit

This read/write flag is set when the TIMB counter reaches the modulo value programmed in the TIMB counter modulo registers. Clear TOF by reading the TIMB status and control register when TOF is set and then writing a 0 to TOF. If another TIMB overflow occurs before the clearing sequence is complete, then writing 0 to TOF has no effect. Therefore, a TOF interrupt request cannot be lost due to inadvertent clearing of TOF. Reset clears the TOF bit. Writing a 1 to TOF has no effect.

- 1 = TIMB counter has reached modulo value

- 0 = TIMB counter has not reached modulo value

#### **TOIE** — TIMB Overflow Interrupt Enable Bit

This read/write bit enables TIMB overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

- 1 = TIMB overflow interrupts enabled

- 0 = TIMB overflow interrupts disabled

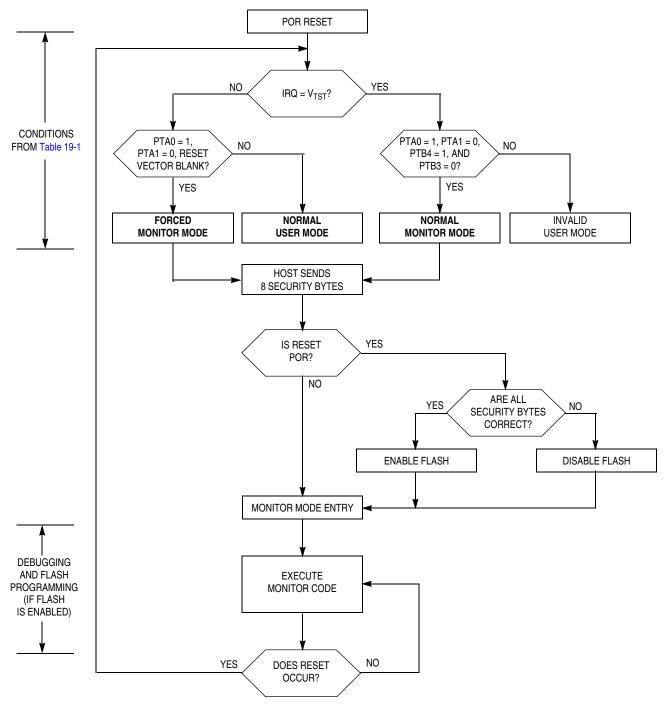

Figure 19-8. Simplified Monitor Mode Entry Flowchart

| Characteristic <sup>(1)</sup>                                                                                                                                                               | Symbol                              | Min                   | Typ <sup>(2)</sup>          | Max                        | Unit                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|-----------------------------|----------------------------|----------------------|

| V <sub>DD</sub> + V <sub>DDA</sub> supply current Run <sup>(4),(5)</sup> Wait <sup>(5), (6)</sup>                                                                                           |                                     | _<br>_                | 18<br>5.2                   | 25<br>7.0                  | mA<br>mA             |

| Stop (LVI off) @ $25^{\circ}$ C <sup>(7)</sup><br>Stop (LVI on) @ $25^{\circ}$ C<br>Stop (LVI off), $-40^{\circ}$ C to $135^{\circ}$ C<br>Stop (LVI on), $-40^{\circ}$ C to $135^{\circ}$ C | I <sub>DD</sub>                     | _<br>_<br>_<br>_      | 0.83<br>0.19<br>3.0<br>0.19 | 2.00<br>0.24<br>30<br>0.30 | μΑ<br>mA<br>μΑ<br>mA |

| I/O ports Hi-Z leakage current <sup>(8)</sup>                                                                                                                                               | I <sub>IL</sub>                     | -1                    | _                           | +1                         | μΑ                   |

| Input current – RST, OSC1                                                                                                                                                                   | I <sub>In</sub>                     | -1                    | 1                           | +1                         | μΑ                   |

| Capacitance Ports (as input or output)                                                                                                                                                      | C <sub>Out</sub><br>C <sub>In</sub> |                       |                             | 12<br>8                    | pF                   |

| POR rearm voltage <sup>(9)</sup>                                                                                                                                                            | $V_{POR}$                           | 0                     |                             | 100                        | mV                   |

| POR reset voltage <sup>(10)</sup>                                                                                                                                                           | V <sub>POR</sub>                    | 0                     | 700                         | 800                        | mV                   |

| POR rise time ramp rate                                                                                                                                                                     | R <sub>POR</sub>                    | 0.035                 | _                           | _                          | V/ms                 |

| Monitor mode entry voltage                                                                                                                                                                  | V <sub>TST</sub>                    | V <sub>DD</sub> + 3.5 |                             | V <sub>DD</sub> + 4.5      | V                    |

| Low-voltage inhibit reset, trip falling voltage <sup>(11)</sup>                                                                                                                             | V <sub>TRIPF</sub>                  | 3.90                  | 4.30                        | 4.50                       | V                    |

| Low-voltage inhibit reset, trip rising voltage <sup>(12)</sup>                                                                                                                              | V <sub>TRIPR</sub>                  | 4.00                  | 4.40                        | 4.60                       | V                    |

| Low-voltage inhibit reset/recover hysteresis <sup>(13)</sup>                                                                                                                                | V <sub>HYS</sub>                    | _                     | 0.09                        | _                          | V                    |

| Pullup resistor — PTA0–PTA6/SS <sup>(14)</sup> , IRQ, RST                                                                                                                                   | R <sub>PU</sub>                     | 24                    | _                           | 48                         | kΩ                   |

- 1.  $V_{DD}$  = 5.5 Vdc to 4.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $-40^{\circ}$ C to +135°C, unless otherwise noted 2. Typical values reflect average measurements at midpoint of voltage range, 25°C only.

- 3. Some disturbance of the ADC accuracy is possible during any injection event and is dependent on board layout and power supply decoupling.

- 4. Run (operating) I<sub>DD</sub> measured using internal oscillator at its 32-MHz rate. V<sub>DD</sub> = 5.5 Vdc. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs. Measured with all modules enabled.

- 5. All measurements taken with LVI enabled.

- 6. Wait I<sub>DD</sub> measured using internal oscillator at its 1-MHz rate. All inputs 0.2 V from rail; no dc loads; less than 100 pF on all outputs. All ports configured as inputs.

- 7. Stop I<sub>DD</sub> is measured with no port pin sourcing current; all modules are disabled. OSCSTOPEN option is not selected.

- 8. Pullups and pulldowns are disabled.

- 9. Maximum is highest voltage that power-on reset (POR) is guaranteed.

- 10. Maximum is highest voltage that POR is possible.

- 11. These values assume the LVI is operating in 5-V mode (i.e. LVI5OR3 bit is set to 1). For 3-V mode (LVI5OR3 = 0), values become Min: 2.45, Typ: 2.60, Max: 2.80

- 12. These values assume the LVI is operating in 5-V mode (i.e. LVI5OR3 bit is set to 1). For 3-V mode (LVI5OR3 = 0), values become Min: 2.55, Typ: 2.66, Max: 2.80

- 13. These values assume the LVI is operating in 5-V mode (i.e. LVI5OR3 bit is set to 1). For 3-V mode (LVI5OR3 = 0), values become Typ: 60

- 14. PTA0-PTA4 pullup resistors are for interrupts only and are only enabled when the keyboard is in use.

| \$0000       |                                                              | \$FE08                                                         | FLASH Control Register (FLCR)                         |  |  |

|--------------|--------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|--|--|

| $\downarrow$ | I/O Registers<br>64 Bytes                                    | \$FE09                                                         | Break Address Register High (BRKH)                    |  |  |

| \$003F       | S. Syllo                                                     | \$FE0A                                                         | Break Address Register Low (BRKL)                     |  |  |

| \$0040       |                                                              | \$FE0B                                                         | Break Status and Control Register (BRKSCR)            |  |  |

| $\downarrow$ | RAM<br>384 Bytes                                             | \$FE0C                                                         | LVI Status Register (LVISR)                           |  |  |

| \$01BF       | 33.27.63                                                     | \$FE0D                                                         |                                                       |  |  |

| \$01C00      |                                                              | <b>\</b>                                                       | Reserved<br>3 Bytes                                   |  |  |

| $\downarrow$ | Unimplemented<br>3648 Bytes                                  | \$FE0F                                                         | o Bytes                                               |  |  |

| \$0FFF       | 0040 Bytes                                                   | \$FE10                                                         | Reserved                                              |  |  |

| \$1000       |                                                              | $\downarrow$                                                   | 16 Bytes Reserved for Compatibility with Monitor Code |  |  |

| $\downarrow$ | Reserved for Integrated FLASH Burn-in Routines<br>1024 Bytes | \$FE1F                                                         | for A-Family Parts                                    |  |  |

| \$13FF       | 1024 Bytes                                                   | \$FE20                                                         |                                                       |  |  |

| \$1400       |                                                              | <b>↓</b>                                                       | Monitor ROM 310 Bytes                                 |  |  |

| $\downarrow$ | Unimplemented<br>53,334 Bytes                                | FF55                                                           |                                                       |  |  |

| \$DFFF       | 30,004 Dytes                                                 | FF56                                                           |                                                       |  |  |

| \$E000       |                                                              | $\downarrow$                                                   | Unimplemented<br>40 Bytes                             |  |  |

| $\downarrow$ | FLASH Memory<br>7680 Bytes                                   | FF7D                                                           | 40 Dytes                                              |  |  |

| \$FDFF       | 7000 Bytes                                                   | \$FF7E                                                         | FLASH Block Protect Register (FLBPR)                  |  |  |

| \$FE00       | SIM Break Status Register (SBSR)                             | \$FF7F                                                         |                                                       |  |  |

| \$FE01       | SIM Reset Status Register (SRSR)                             | <b>1</b>                                                       | Unimplemented<br>93 Bytes                             |  |  |

| \$FE02       | Reserved                                                     | \$FFDB                                                         | 30 Dytes                                              |  |  |

| \$FE03       | SIM Break Flag Control Register (SBFCR)                      | \$FFDC                                                         |                                                       |  |  |

| \$FE04       | RESERVED                                                     | $\downarrow$                                                   | FLASH Vectors<br>36 Bytes                             |  |  |

| \$FE05       | RESERVED                                                     | \$FFFF                                                         | 30 Dytes                                              |  |  |

| \$FE06       | RESERVED                                                     | Note:                                                          |                                                       |  |  |

| \$FE07       | Reserved for FLASH Test Control Register (FLTCR)             | Locations \$FFF6-\$FFFD are reserved for eight security bytes. |                                                       |  |  |

|              |                                                              | I                                                              |                                                       |  |  |

Figure A-2. MC68HC908EY8 Memory Map