#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

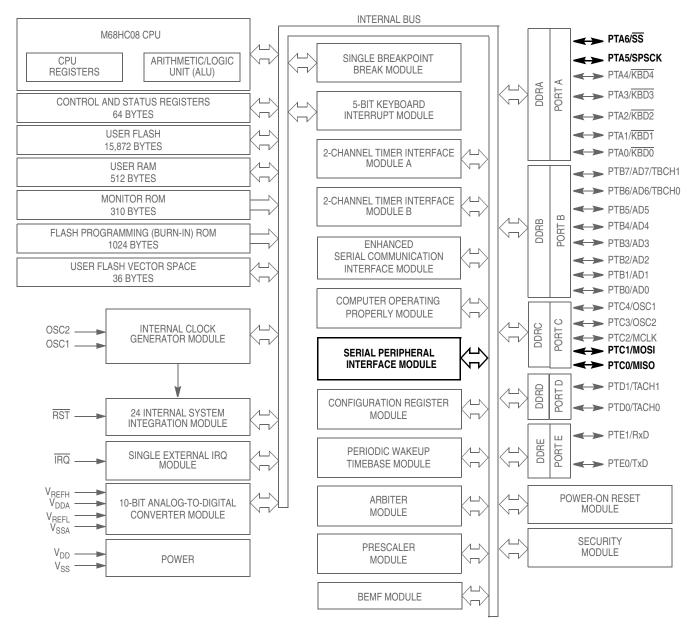

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | LINbus, SCI, SPI                                                      |

| Peripherals                | POR, PWM                                                              |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908ey8mfaer |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 14.6   | Low-Power Modes                 | 164 |

|--------|---------------------------------|-----|

| 14.6.1 | Wait Mode                       | 164 |

| 14.6.2 | Stop Mode                       | 165 |

| 14.7   | SIM Registers                   | 166 |

|        | SIM Break Status Register       |     |

| 14.7.2 | SIM Reset Status Register       | 167 |

| 14.7.3 | SIM Break Flag Control Register | 168 |

# Chapter 15 Serial Peripheral Interface (SPI) Module

| 15.1    | Introduction                           | 169 |

|---------|----------------------------------------|-----|

| 15.2    | Features                               | 169 |

| 15.3    | Pin Name and Register Name Conventions | 169 |

| 15.4    | Functional Description                 | 171 |

| 15.4.1  | Master Mode                            | 172 |

| 15.4.2  | Slave Mode                             | 172 |

| 15.5    | Transmission Formats                   | 173 |

| 15.5.1  | Clock Phase and Polarity Controls.     | 173 |

| 15.5.2  | Transmission Format When CPHA = 0      | 174 |

| 15.5.3  | Transmission Format When CPHA = 1      | 174 |

| 15.5.4  | Transmission Initiation Latency        | 175 |

| 15.6    | Error Conditions                       | 176 |

| 15.6.1  | Overflow Error                         | 177 |

| 15.6.2  | Mode Fault Error                       | 178 |

| 15.7    | Interrupts                             | 180 |

| 15.8    | Queuing Transmission Data              | 180 |

| 15.9    | Resetting the SPI                      | 181 |

| 15.10   | Low-Power Modes                        | 182 |

| 15.10.1 | 1 Wait Mode                            | 182 |

| 15.10.2 | 2 Stop Mode                            | 182 |

| 15.11   | SPI During Break Interrupts            | 182 |

| 15.12   | I/O Signals                            | 182 |

| 15.12.1 | 1 MISO (Master In/Slave Out)           | 183 |

| 15.12.2 | 2 MOSI (Master Out/Slave In)           | 183 |

| 15.12.3 | 3 SPSCK (Serial Clock)                 | 183 |

| 15.12.4 | 4 SS (Slave Select)                    | 183 |

| 15.12.5 | 5 V <sub>SS</sub> (Clock Ground)       | 184 |

| 15.13   | I/O Registers                          | 184 |

| 15.13.1 |                                        |     |

| 15.13.2 | 2 SPI Status and Control Register      | 186 |

| 15.13.3 | 3 SPI Data Register                    | 188 |

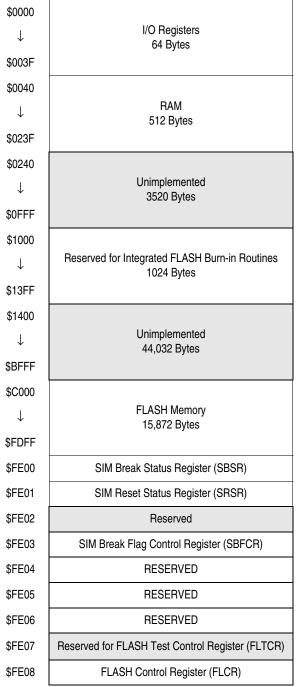

| \$FE09       | Break Address Register High (BRKH)                       |  |  |  |

|--------------|----------------------------------------------------------|--|--|--|

| \$FE0A       | Break Address Register Low (BRKL)                        |  |  |  |

| \$FE0B       | Break Status and Control Register (BRKSCR)               |  |  |  |

| \$FE0C       | LVI Status Register (LVISR)                              |  |  |  |

| \$FE0D       |                                                          |  |  |  |

| $\downarrow$ | Reserved<br>3 Bytes                                      |  |  |  |

| \$FE0F       | 0 5900                                                   |  |  |  |

| \$FE10       | Reserved                                                 |  |  |  |

| $\downarrow$ | 16 Bytes<br>Reserved for Compatibility with Monitor Code |  |  |  |

| \$FE1F       | for A-Family Parts                                       |  |  |  |

| \$FE20       |                                                          |  |  |  |

| $\downarrow$ | Monitor ROM 310 Bytes                                    |  |  |  |

| FF55         |                                                          |  |  |  |

| FF56         |                                                          |  |  |  |

| $\downarrow$ | Unimplemented<br>40 Bytes                                |  |  |  |

| FF7D         | -10 Dyie3                                                |  |  |  |

| \$FF7E       | FLASH Block Protect Register (FLBPR)                     |  |  |  |

| \$FF80       | ICG Trim Value (Optional) (ICGT)                         |  |  |  |

| \$FF7F       |                                                          |  |  |  |

| $\downarrow$ | Unimplemented<br>93 Bytes                                |  |  |  |

| \$FFDB       | 00 59100                                                 |  |  |  |

| \$FFDC       |                                                          |  |  |  |

| $\downarrow$ | FLASH Vectors                                            |  |  |  |

| \$FFFF       | 36 Bytes                                                 |  |  |  |

|              |                                                          |  |  |  |

Note:

Locations \$FFF6–\$FFFD are reserved for eight security bytes.

# Figure 2-1. Memory Map

# 2.6.2 FLASH Page Erase Operation

Use this step-by-step procedure to erase a page (64 bytes) of FLASH memory to read as logic 1:

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub> (minimum 1 ms or 4 ms).

- 7. Clear the ERASE bit.

- 8. Wait for a time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. After time,  $t_{BCV}$  (typical 1 µs), the memory can be accessed in read mode again.

#### NOTE

While these operations must be performed in the order shown, other unrelated operations may occur between the steps.

#### NOTE

Due to the security feature (see 19.3 Monitor Module (MON)) the last page of the FLASH (0xFFDC–0xFFFF), which contains the security bytes, cannot be erased by Page Erase Operation. It can only be erased with the Mass Erase Operation.

In applications that require more than 1000 program/erase cycles, use the 4 ms page erase specification to get improved long-term reliability. Any application can use this 4 ms page erase specification. However, in applications where a FLASH location will be erased and reprogrammed less than 1000 times, and speed is important, use the 1 ms page erase specification to get a shorter cycle time.

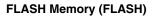

#### Configuration Registers (CONFIG1 and CONFIG2)

1. The LVI5OR3 bit is cleared only by a power-on reset (POR).

#### Figure 5-2. Configuration Register 1 (CONFIG1)

#### ESCIBDSRC — ESCI Baud Rate Clock Source Bit

ESCIBDSRC controls the clock source used for the ESCI. The setting of the bit affects the frequency at which the ESCI operates.

1 = Internal data bus clock used as clock source for ESCI

0 = CGMXCLK used as clock source for ESCI

#### **EXTXTALEN** — External Crystal Enable Bit

EXTXTALEN enables the external oscillator circuits to be configured for a crystal configuration where the PTC4/OSC1 and PTC3/OSC2 pins are the connections for an external crystal.

#### NOTE

This bit does not function without setting the EXTCLKEN bit also.

Clearing the EXTXTALEN bit (default setting) allows the PTC3/OSC2 pin to function as a general-purpose I/O pin. Refer to Table 5-1 for configuration options for the external source. See Chapter 8 Internal Clock Generator (ICG) Module for a more detailed description of the external clock operation.

| External Clock<br>Configuration Bits |           | Pin Function |           | Description                                                                                                                                            |  |

|--------------------------------------|-----------|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EXTCLKEN                             | EXTXTALEN | PTC4/OSC1    | PTC3/OSC2 |                                                                                                                                                        |  |

| 0                                    | 0         | PTC4         | PTC3      | Default setting — external oscillator disabled                                                                                                         |  |

| 0                                    | 1         | PTC4         | PTC3      | External oscillator disabled since EXTCLKEN not set                                                                                                    |  |

| 1                                    | 0         | OSC1         | PTC3      | External oscillator configured for an external clock source input (square wave) on OSC1                                                                |  |

| 1                                    | 1         | OSC1         | OSC2      | External oscillator configured for an external crystal configuration on OSC1 and OSC2. System will also operate with square-wave clock source in OSC1. |  |

Table 5-1. External Clock Option Settings

EXTXTALEN, when set, also configures the clock monitor to expect an external clock source in the valid range of crystals (30 kHz to 100 kHz or 1 MHz to 8 MHz). When EXTXTALEN is clear, the clock monitor will expect an external clock source in the valid range for externally generated clocks when using the clock monitor (60 Hz to 32 MHz).

EXTXTALEN, when set, also configures the external clock stabilization divider in the clock monitor for a 4096-cycle timeout to allow the proper stabilization time for a crystal. When EXTXTALEN is clear, the stabilization divider is configured to 16 cycles since an external clock source does not need a startup time.

1 = Allows PTC3/OSC2 to be an external crystal connection.

0 = PTC3/OSC2 functions as an I/O port pin (default).

#### Configuration Registers (CONFIG1 and CONFIG2)

### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI) Module.

1 = LVI module resets disabled

0 = LVI module resets enabled

## LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI) Module.

1 = LVI module power disabled

0 = LVI module power enabled

## LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

LVI5OR3 selects the voltage operating mode of the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI) Module. The voltage mode selected for the LVI will typically be 5 V. However, users may choose to operate the LVI in 3-V mode if desired. See Chapter 20 Electrical Specifications for the LVI's voltage trip points for each of the modes.

1 = LVI operates in 5-V mode.

0 = LVI operates in 3-V mode.

#### NOTE

The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 CGMXCLK cycles instead of a 4096-CGMXCLK cycle delay.

1 = Stop mode recovery after 32 CGMXCLK cycles

0 = Stop mode recovery after 4096 CGMXCLCK cycles

## NOTE

#### Exiting stop mode by an LVI reset will result in the long stop recovery.

If the system clock source selected is the internal oscillator or the external crystal and the OSCENINSTOP configuration bit is not set, the oscillator will be disabled during stop mode. The short stop recovery does not provide enough time for oscillator stabilization and thus the SSREC bit should not be set.

When using the LVI during normal operation but disabling during stop mode, the LVI will have an enable time of t<sub>EN</sub>. The system stabilization time for power-on reset and long stop recovery (both 4096 CGMXCLK cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32-CGMXCLK delay must be greater than the LVI's turn on time to avoid a period in startup where the LVI is not protecting the MCU.

# STOP — STOP Instruction Enable Bit

- STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

## COPD — COP Disable Bit

COPD disables the COP module. See Chapter 6 Computer Operating Properly (COP) Module.

- 1 = COP module disabled

- 0 = COP module enabled

External Interrupt (IRQ)

# 9.5 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ interrupt latch can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear the latches during the break state.

To allow software to clear the IRQ latch during a break interrupt, write a 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ latch.

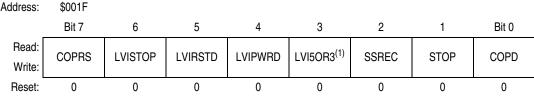

# 9.6 IRQ Status and Control Register

The IRQ status and control register (ISCR) controls and monitors operation of the IRQ module. The ISCR has these functions:

- Shows the state of the IRQ interrupt flag

- Clears the IRQ interrupt latch

- Masks IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

# Figure 9-3. IRQ Status and Control Register (ISCR)

## IRQF — IRQ Flag Bit

This read-only status bit is high when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- $0 = \overline{IRQ}$  interrupt not pending

## ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0. Reset clears ACK.

## IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables IRQ interrupt requests. Reset clears IMASK.

- 1 = IRQ interrupt requests disabled

- 0 = IRQ interrupt requests enabled

## MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin. Reset clears MODE.

- $1 = \overline{IRQ}$  interrupt requests on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt requests on falling edges only

#### PTE[1:0] — Port E Data Bits

These read/write bits are software programmable. Data direction of each port E pin is under the control of the corresponding bit in data direction register E. Reset has no effect on PTE[1:0].

#### **RxD** — SCI Receive Data Input Bit

The PTE1/RxD pin is the receive data input for the SCI module. When the enable SCI bit, ENSCI, is clear, the SCI module is disabled, and the PTE1/RxD pin is available for general-purpose I/O. See 13.8.1 ESCI Control Register 1.

### TxD — SCI Transmit Data Output

The PTE0/TxD pin is the transmit data output for the SCI module. When the enable SCI bit, ENSCI, is clear, the SCI module is disabled, and the PTE0/TxD pin is available for general-purpose I/O. See 13.8.1 ESCI Control Register 1.

#### NOTE

Data direction register E (DDRE) does not affect the data direction of port E pins that are being used by the ESCI. However, the DDRE bits always determine whether reading port E returns the states of the latches or the states of the pins. See Table 12-5.

## 12.6.2 Data Direction Register E

Data direction register E determines whether each port E pin is an input or an output. Writing a 1 to a DDRE bit enables the output buffer for the corresponding port E pin; a 0 disables the output buffer.

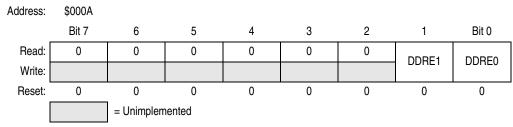

Figure 12-14. Data Direction Register E (DDRE)

#### DDRE[1:0] — Data Direction Register E Bits

These read/write bits control port E data direction. Reset clears DDRE[1:0], configuring all port E pins as inputs.

1 = Corresponding port E pin configured as output

0 = Corresponding port E pin configured as input

#### NOTE

Avoid glitches on port E pins by writing to the port E data register before changing data direction register E bits from 0 to 1.

# 13.4.3 Receiver

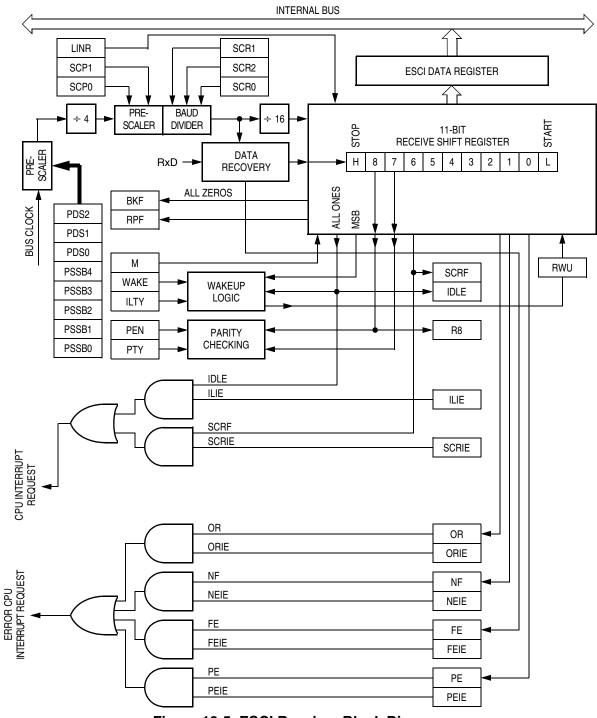

Figure 13-5 shows the structure of the ESCI receiver.

Figure 13-5. ESCI Receiver Block Diagram

#### TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 consecutive 1s from the transmit shift register to the TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the TxD returns to the idle condition (1). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted. Reset clears the TE bit.

1 = Transmitter enabled

0 = Transmitter disabled

#### NOTE

Writing to the TE bit is not allowed when the enable ESCI bit (ENSCI) is clear. ENSCI is in ESCI control register 1.

#### RE — Receiver Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver but does not affect receiver interrupt flag bits. Reset clears the RE bit.

1 = Receiver enabled

0 = Receiver disabled

#### NOTE

Writing to the RE bit is not allowed when the enable ESCI bit (ENSCI) is clear. ENSCI is in ESCI control register 1.

#### RWU — Receiver Wakeup Bit

This read/write bit puts the receiver in a standby state during which receiver interrupts are disabled. The WAKE bit in SCC1 determines whether an idle input or an address mark brings the receiver out of the standby state and clears the RWU bit. Reset clears the RWU bit.

1 = Standby state

0 = Normal operation

#### SBK — Send Break Bit

Setting and then clearing this read/write bit transmits a break character followed by a 1. The 1 after the break character guarantees recognition of a valid start bit. If SBK remains set, the transmitter continuously transmits break characters with no 1s between them. Reset clears the SBK bit.

1 = Transmit break characters

0 = No break characters being transmitted

## NOTE

Do not toggle the SBK bit immediately after setting the SCTE bit. Toggling SBK before the preamble begins causes the ESCI to send a break character instead of a preamble.

#### I/O Registers

| PSSB[4:3:2:1:0] | Prescaler Divisor Fine Adjust (PDFA) |

|-----------------|--------------------------------------|

| 0 0 0 0 0       | 0/32 = 0                             |

| 00001           | 1/32 = 0.03125                       |

| 00010           | 2/32 = 0.0625                        |

| 00011           | 3/32 = 0.09375                       |

| 00100           | 4/32 = 0.125                         |

| 00101           | 5/32 = 0.15625                       |

| 00110           | 6/32 = 0.1875                        |

| 00111           | 7/32 = 0.21875                       |

| 01000           | 8/32 = 0.25                          |

| 01001           | 9/32 = 0.28125                       |

| 01010           | 10/32 = 0.3125                       |

| 01011           | 11/32 = 0.34375                      |

| 01100           | 12/32 = 0.375                        |

| 01101           | 13/32 = 0.40625                      |

| 01110           | 14/32 = 0.4375                       |

| 01111           | 15/32 = 0.46875                      |

| 10000           | 16/32 = 0.5                          |

| 10001           | 17/32 = 0.53125                      |

| 10010           | 18/32 = 0.5625                       |

| 10011           | 19/32 = 0.59375                      |

| 10100           | 20/32 = 0.625                        |

| 10101           | 21/32 = 0.65625                      |

| 10110           | 22/32 = 0.6875                       |

| 10111           | 23/32 = 0.71875                      |

| 1 1 0 0 0       | 24/32 = 0.75                         |

| 1 1 0 0 1       | 25/32 = 0.78125                      |

| 1 1 0 1 0       | 26/32 = 0.8125                       |

| 1 1 0 1 1       | 27/32 = 0.84375                      |

| 1 1 1 0 0       | 28/32 = 0.875                        |

| 1 1 1 0 1       | 29/32 = 0.90625                      |

| 1 1 1 1 0       | 30/32 = 0.9375                       |

| 11111           | 31/32 = 0.96875                      |

# Table 13-10. ESCI Prescaler Divisor Fine Adjust

#### Serial Peripheral Interface (SPI) Module

## Figure 15-1. Block Diagram Highlighting SPI Block and Pins

The generic names of the SPI I/O registers are:

- SPI control register (SPCR)

- SPI status and control register (SPSCR)

- SPI data register (SPDR)

Table 15-2 shows the names and the addresses of the SPI I/O registers.

In a master SPI with the mode fault enable bit (MODFEN) set, the mode fault flag (MODF) is set if  $\overline{SS}$  goes to logic 0. A mode fault in a master SPI causes the following events to occur:

- If ERRIE = 1, the SPI generates an SPI receiver/error CPU interrupt request.

- The SPE bit is cleared.

- The SPTE bit is set.

- The SPI state counter is cleared.

- The data direction register of the shared I/O port regains control of port drivers.

## NOTE

To prevent bus contention with another master SPI after a mode fault error, clear all data direction register (DDR) bits associated with the SPI shared port pins.

## NOTE

Setting the MODF flag (SPSCR) does not clear the SPMSTR bit. Reading SPMSTR when MODF = 1 will indicate a MODE fault error occurred in either master mode or slave mode.

When configured as a slave (SPMSTR = 0), the MODF flag is set if  $\overline{SS}$  goes high during a transmission. When CPHA = 0, a transmission begins when  $\overline{SS}$  goes low and ends once the incoming SPSCK returns to its idle level after the shift of the eighth data bit. When CPHA = 1, the transmission begins when the SPSCK leaves its idle level and  $\overline{SS}$  is already low. The transmission continues until the SPSCK returns to its IDLE level after the shift of the last data bit. (See 15.5 Transmission Formats.)

## NOTE

When CPHA = 0, a MODF occurs if a slave is selected ( $\overline{SS}$  is at logic 0) and later deselected ( $\overline{SS}$  is at logic 1) even if no SPSCK is sent to that slave. This happens because  $\overline{SS}$  at logic 0 indicates the start of the transmission (MISO driven out with the value of MSB) for CPHA = 0. When CPHA = 1, a slave can be selected and then later deselected with no transmission occurring. Therefore, MODF does not occur since a transmission was never begun.

In a slave SPI (MSTR = 0), the MODF bit generates an SPI receiver/error CPU interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by toggling the SPE bit of the slave.

#### NOTE

A logic 1 voltage on the SS pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if a transmission has begun.

To clear the MODF flag, read the SPSCR and then write to the SPCR register. This entire clearing procedure must occur with no MODF condition existing or else the flag will not be cleared.

# Chapter 16 Timebase Module (TBM)

# 16.1 Introduction

This section describes the timebase module (TBM). The TBM will generate periodic interrupts at user selectable rates using a counter clocked by either the internal or external clock sources. This TBM version uses 15 divider stages, eight of which are user selectable.

## NOTE

The TBM on this device differs from that of the MC68HC908KX8 in that it has an additional divide-by-128 at the front end of the divider chain.

For further information regarding timers on M68HC08 family devices, please consult the *HC08 Timer Reference Manual*, Freescale order number TIM08RM/AD.

# 16.2 Features

Features of the TBM module include:

- Software configurable periodic interrupts with divide-by-1024, 2048, 4096, 8192, 16384, 262144, 1048576, and 4194304 taps of the selected clock source

- Configurable for operation during stop mode to allow periodic wake up from stop

# **16.3 Functional Description**

This module can generate a periodic interrupt by dividing the clock source supplied from the internal clock generator module, TBMCLK. Note that this clock source is the external clock ECLK when the ECGON bit in the ICG control register (ICGCR) is set. Otherwise, TBMCLK is driven at the internally generated clock frequency (ICLK). In other words, if the external clock is enabled it will be used as the TBMCLK, even if the MCU bus clock is based on the internal clock.

The counter is initialized to all 0s when TBON bit is cleared. The counter, shown in Figure 16-1, starts counting when the TBON bit is set. When the counter overflows at the tap selected by TBR2–TBR0, the TBIF bit gets set. If the TBIE bit is set, an interrupt request is sent to the CPU. The TBIF flag is cleared by writing a 1 to the TACK bit. The first time the TBIF flag is set after enabling the timebase module, the interrupt is generated at approximately half of the overflow period. Subsequent events occur at the exact period.

The timebase module may remain active after execution of the STOP instruction if the internal clock generator has been enabled to operate during stop mode through the OSCENINSTOP bit in the configuration register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

PWM function, and TIMA channel 1 status and control register (TASC1) is unused. While the MS0B bit is set, the channel 1 pin, PTD1/TACH1, is available as a general-purpose I/O pin.

## NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

## 17.3.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use this initialization procedure:

- 1. In the TIMA status and control register (TASC):

- a. Stop the TIMA counter by setting the TIMA stop bit, TSTOP.

- b. Reset the TIMA counter prescaler by setting the TIMA reset bit, TRST.

- 2. In the TIMA counter modulo registers (TAMODH–TAMODL), write the value for the required PWM period.

- 3. In the TIMA channel x registers (TACHxH–TACHxL), write the value for the required pulse width.

- 4. In TIMA channel x status and control register (TASCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB–MSxA. See Table 17-2.

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (to clear output on compare) or 1:1 (to set output on compare) to the edge/level select bits, ELSxB–ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 17-2.

## NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIMA status control register (TASC), clear the TIMA stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIMA channel 0 registers (TACH0H–TACH0L) initially control the buffered PWM output. TIMA status control register 0 (TASC0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIMA overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 17.8.4 TIMA Channel Status and Control Registers.

#### Timer Interface A (TIMA) Module

#### **TOIE** — **TIMA** Overflow Interrupt Enable Bit

This read/write bit enables TIMA overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

1 = TIMA overflow interrupts enabled

0 = TIMA overflow interrupts disabled

## TSTOP — TIMA Stop Bit

This read/write bit stops the TIMA counter. Counting resumes when TSTOP is cleared. Reset sets the TSTOP bit, stopping the TIMA counter until software clears the TSTOP bit.

1 = TIMA counter stopped

0 = TIMA counter active

#### NOTE

Do not set the TSTOP bit before entering wait mode if the TIMA is required to exit wait mode. Also, when the TSTOP bit is set and the timer is configured for input capture operation, input captures are inhibited until TSTOP is cleared.

When using TSTOP to stop the timer counter, check for any timer flags being set. If a timer flag is set, it must be cleared by clearing TSTOP, then clearing the flag, then setting TSTOP again.

## TRST — TIMA Reset Bit

Setting this write-only bit resets the TIMA counter and the TIMA prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIMA counter is reset and always reads as 0. Reset clears the TRST bit.

1 = Prescaler and TIMA counter cleared

0 = No effect

#### NOTE

Setting the TSTOP and TRST bits simultaneously stops the TIMA counter at a value of \$0000.

#### PS[2:0] — Prescaler Select Bits

These read/write bits select one of the seven prescaler outputs as the input to the TIMA counter as Table 17-1 shows. Reset clears the PS[2:0] bits.

| PS[2:0] | TIMA Clock Source       |

|---------|-------------------------|

| 0 0 0   | Internal bus clock ÷ 1  |

| 0 0 1   | Internal bus clock ÷ 2  |

| 010     | Internal bus clock ÷ 4  |

| 0 1 1   | Internal bus clock ÷ 8  |

| 100     | Internal bus clock ÷ 16 |

| 101     | Internal bus clock ÷ 32 |

| 1 1 0   | Internal bus clock ÷ 64 |

| 111     | Unused                  |

#### Table 17-1. Prescaler Selection

#### Timer Interface B (TIMB) Module

## 18.3.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 18.3.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the value currently in the TIMB channel registers.

An unsynchronized write to the TIMB channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIMB overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIMB may pass the new value before it is written to the TIMB channel registers.

Use these methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- When changing to a longer pulse width, enable TIMB overflow interrupts and write the new value in the TIMB overflow interrupt routine. The TIMB overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

#### 18.3.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the PTB6/TBCH0 pin. The TIMB channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIMB channel 0 status and control register (TBSC0) links channel 0 and channel 1. The TIMB channel 0 registers initially control the pulse width on the PTB6/TBCH0 pin. Writing to the TIMB channel 1 registers enables the TIMB channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIMB channel registers (0 or 1) that control the pulse width are the ones written to last. TBSC0 controls and monitors the buffered PWM function, and TIMB channel 1 status and control register (TBSC1) is unused. While the MS0B bit is set, the channel 1 pin, PTB7/TBCH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

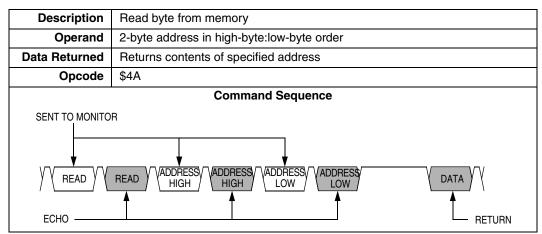

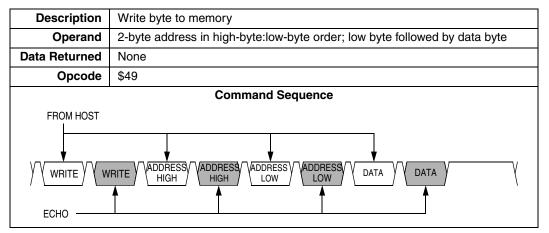

A brief description of each monitor mode command is given in Table 19-3 through Table 19-8.

# Table 19-3. READ (Read Memory) Command

#### Table 19-5. IREAD (Indexed Read) Command

| Description      | Read next 2 bytes in memory from last address accessed |  |  |

|------------------|--------------------------------------------------------|--|--|

| Operand          | None                                                   |  |  |

| Data Returned    | Returns contents of next two addresses                 |  |  |

| Opcode           | \$1A                                                   |  |  |

| Command Sequence |                                                        |  |  |

|                  | FROM HOST                                              |  |  |

**Electrical Specifications**

# 20.11 SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                       | Min                                              | Мах                                   | Unit                                 |

|----------------------------------|----------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|---------------------------------------|--------------------------------------|

|                                  | Operating frequency<br>Master<br>Slave                               | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub>     | f <sub>OP</sub> /128<br>DC                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz                           |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub><br>t <sub>CYC(S)</sub>   | 2<br>1                                           | 128<br>—                              | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                         | 1                                                | —                                     | t <sub>cyc</sub>                     |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                          | 1                                                | _                                     | t <sub>cyc</sub>                     |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub><br>t <sub>SCKH(S)</sub> | t <sub>cyc</sub> –25<br>1/2 t <sub>cyc</sub> –25 | 64 t <sub>cyc</sub>                   | ns<br>ns                             |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub><br>t <sub>SCKL(S)</sub> | t <sub>cyc</sub> –25<br>1/2 t <sub>cyc</sub> –25 | 64 t <sub>cyc</sub>                   | ns<br>ns                             |

| 6                                | Data setup time (inputs)<br>Master<br>Slave                          | t <sub>SU(M)</sub><br>t <sub>SU(S)</sub>     | 30<br>30                                         |                                       | ns<br>ns                             |

| 7                                | Data hold time (inputs)<br>Master<br>Slave                           | t <sub>H(M)</sub><br>t <sub>H(S)</sub>       | 30<br>30                                         |                                       | ns<br>ns                             |

| 8                                | Access time, slave <sup>(3)</sup><br>CPHA = 0<br>CPHA = 1            | t <sub>A(CP0)</sub><br>t <sub>A(CP1)</sub>   | 0<br>0                                           | 40<br>40                              | ns<br>ns                             |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                          | —                                                | 40                                    | ns                                   |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub><br>t <sub>V(S)</sub>       |                                                  | 50<br>50                              | ns<br>ns                             |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub><br>t <sub>HO(S)</sub>     | 0<br>0                                           |                                       | ns<br>ns                             |

Numbers refer to dimensions in Figure 20-1 and Figure 20-2.

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins.

Time to data active from high-impedance state

Hold time to high-impedance state

With 100 pF on all SPI pins

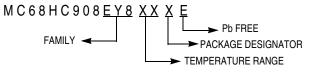

# A.4 MC Order Numbers

| MC Order Number <sup>(1)</sup> | Operating<br>Temperature Range |

|--------------------------------|--------------------------------|

| MC68HC908EY8KFA                | –40°C to +135°C                |

| MC68HC908EY8MFA                | -40°C to +125°C                |

| MC68HC908EY8VFA                | -40°C to +105°C                |

| MC68HC908EY8CFA                | -40°C to +85°C                 |

## Table A-1. MC Order Numbers

1. FA = Quad flat pack

Figure A-3. Device Numbering System