Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                   |

|--------------------------------|-------------------------------------------------------------------|

| Product Status                 | Active                                                            |

| Number of LABs/CLBs            | 5968                                                              |

| Number of Logic Elements/Cells | 53712                                                             |

| Total RAM Bits                 | 2322432                                                           |

| Number of I/O                  | 309                                                               |

| Number of Gates                | 3400000                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                     |

| Mounting Type                  | Surface Mount                                                     |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                |

| Package / Case                 | 484-FBGA, CSPBGA                                                  |

| Supplier Device Package        | 484-CSPBGA (19x19)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xillinx/xc3sd3400a-4csg484li |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                             |

|----------|---------|----------------------------------------------------------------------------------------------------------------------|

| 04/02/07 | 1.0     | Initial Xilinx release.                                                                                              |

| 05/25/07 | 1.0.1   | Minor edits.                                                                                                         |

| 06/18/07 | 1.2     | Updated for Production release.                                                                                      |

| 07/16/07 | 2.0     | Added Low-power options.                                                                                             |

| 06/02/08 | 2.1     | Added reference to SCD 4103 for 750 Mbps performance. Add dual mark clarification to Package Marking. Updated links. |

| 03/11/09 | 2.2     | Simplified ordering information. Removed reference to SCD 4103.                                                      |

| 10/04/10 | 3.0     | Updated the Notice of Disclaimer section.                                                                            |

# **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### **AUTOMOTIVE APPLICATIONS DISCLAIMER**

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

# Spartan-3A DSP FPGA Family: DC and Switching Characteristics

DS610 (v3.0) October 4, 2010

**Product Specification**

## **DC Electrical Characteristics**

In this section, specifications may be designated as Advance, Preliminary, or Production. These terms are defined as follows:

**Advance:** Initial estimates are based on simulation, early characterization, and/or extrapolation from the characteristics of other families. Values are subject to change. Use as estimates, not for production.

**Preliminary:** Based on characterization. Further changes are not expected.

**Production:** These specifications are approved once the silicon has been characterized over numerous production lots. Parameter values are considered stable with no future changes expected.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the published parameter values apply to all Spartan®-3A DSP devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades.

# **Absolute Maximum Ratings**

Stresses beyond those listed under Table 3: Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to absolute maximum conditions for extended periods of time adversely affects device reliability.

Table 3: Absolute Maximum Ratings

| Symbol             | Description                                                | Conditions                                | Min   | Max                    | Units |

|--------------------|------------------------------------------------------------|-------------------------------------------|-------|------------------------|-------|

| V <sub>CCINT</sub> | Internal supply voltage                                    |                                           | -0.5  | 1.32                   | V     |

| V <sub>CCAUX</sub> | Auxiliary supply voltage                                   |                                           | -0.5  | 3.75                   | V     |

| V <sub>CCO</sub>   | Output driver supply voltage                               |                                           | -0.5  | 3.75                   | V     |

| V <sub>REF</sub>   | Input reference voltage                                    |                                           | -0.5  | V <sub>CCO</sub> + 0.5 | V     |

| V <sub>IN</sub>    | Voltage applied to all User I/O pins and Dual-Purpose pins | Driver in a high-impedance state          | -0.95 | 4.6                    | V     |

|                    | Voltage applied to all Dedicated pins                      |                                           | -0.5  | 4.6                    | V     |

| I <sub>IK</sub>    | Input clamp current per I/O pin                            | $-0.5V < V_{IN} < (V_{CCO} + 0.5V)^{(1)}$ | _     | ±100                   | mA    |

| V <sub>ESD</sub>   | Electrostatic Discharge Voltage                            | Human body model                          | _     | ±2000                  | V     |

|                    |                                                            | Charged device model                      | _     | ±500                   | V     |

|                    |                                                            | Machine model                             | _     | ±200                   | V     |

| TJ                 | Junction temperature                                       |                                           | _     | 125                    | °C    |

| T <sub>STG</sub>   | Storage temperature                                        |                                           | -65   | 150                    | °C    |

#### Notes:

- 1. Upper clamp applies only when using PCI IOSTANDARDs.

- 2. For soldering guidelines, see <u>UG112</u>: Device Packaging and Thermal Characteristics and <u>XAPP427</u>: Implementation and Solder Reflow Guidelines for Pb-Free Packages.

© Copyright 2007–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

# **Power Supply Specifications**

Table 4: Supply Voltage Thresholds for Power-On Reset

| Symbol              | Description                                      | Min | Max | Units |

|---------------------|--------------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply      | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply      | 1.0 | 2.0 | V     |

| V <sub>CCO2T</sub>  | Threshold for the V <sub>CCO</sub> Bank 2 supply | 1.0 | 2.0 | V     |

#### Notes:

- V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA configuration source (Platform Flash, SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. Apply V<sub>CCINT</sub> last for lowest overall power consumption (see the <u>UG331</u> chapter titled "Powering Spartan-3 Generation FPGAs" for more information).

- To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

Table 5: Supply Voltage Ramp Rate

| Symbol              | Description                                                      | Min | Max | Units |

|---------------------|------------------------------------------------------------------|-----|-----|-------|

| V <sub>CCINTR</sub> | Ramp rate from GND to valid V <sub>CCINT</sub> supply level      | 0.2 | 100 | ms    |

| V <sub>CCAUXR</sub> | Ramp rate from GND to valid V <sub>CCAUX</sub> supply level      | 0.2 | 100 | ms    |

| V <sub>CCO2R</sub>  | Ramp rate from GND to valid V <sub>CCO</sub> Bank 2 supply level | 0.2 | 100 | ms    |

- V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA configuration source (Platform Flash, SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. Apply V<sub>CCINT</sub> last for lowest overall power consumption (see the <u>UG331</u> chapter titled "Powering Spartan-3 Generation FPGAs" for more information).

- To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

Table 6: Supply Voltage Levels Necessary for Preserving CMOS Configuration Latch (CCL) Contents and RAM Data

| Symbol             | Description                                                                             | Min | Units |

|--------------------|-----------------------------------------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | V <sub>CCINT</sub> level required to retain CMOS Configuration Latch (CCL) and RAM data | 1.0 | V     |

| V <sub>DRAUX</sub> | V <sub>CCAUX</sub> level required to retain CMOS Configuration Latch (CCL) and RAM data | 2.0 | V     |

## **Pin-to-Pin Setup and Hold Times**

Table 18: Pin-to-Pin Setup and Hold Times for the IOB Input Path (System Synchronous)

|                    |                                                                                                                                                                    |                                              |            | Speed Grade |       |       |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------|-------------|-------|-------|

| Symbol             | Description                                                                                                                                                        | Conditions                                   | Device     | -5          | -4    | Units |

|                    |                                                                                                                                                                    |                                              |            | Max         | Max   |       |

| Setup Times        |                                                                                                                                                                    |                                              |            |             |       |       |

| T <sub>PSDCM</sub> | When writing to the Input                                                                                                                                          | LVCMOS25 <sup>(2)</sup> ,                    | XC3SD1800A | 2.65        | 3.11  | ns    |

|                    | Flip-Flop (IFF), the time from the setup of data at the Input pin to the active transition at a Global Clock pin. The DCM is in use. No Input Delay is programmed. | IFD_DELAY_VALUE = 0, with DCM <sup>(4)</sup> | XC3SD3400A | 2.25        | 2.49  | ns    |

|                    | LVCMOS25 <sup>(2)</sup> ,                                                                                                                                          | XC3SD1800A                                   | 2.98       | 3.39        | ns    |       |

|                    | from the setup of data at the IFD_DE                                                                                                                               | IFD_DELAY_VALUE = 6, without DCM             | XC3SD3400A | 2.78        | 3.08  | ns    |

| Hold Times         |                                                                                                                                                                    |                                              |            |             |       |       |

| T <sub>PHDCM</sub> | When writing to IFF, the time                                                                                                                                      | LVCMOS25(3),                                 | XC3SD1800A | -0.38       | -0.38 | ns    |

|                    | from the active transition at the Global Clock pin to the point when data must be held at the Input pin. The DCM is in use. No Input Delay is programmed.          | IFD_DELAY_VALUE = 0, with DCM <sup>(4)</sup> | XC3SD3400A | -0.26       | -0.26 | ns    |

| T <sub>PHFD</sub>  | When writing to IFF, the time                                                                                                                                      | LVCMOS25 <sup>(3)</sup> ,                    | XC3SD1800A | -0.71       | -0.71 | ns    |

|                    | from the active transition at the Global Clock pin to the point when data must be held at the Input pin. The DCM is not in use. The Input Delay is programmed.     | IFD_DELAY_VALUE = 6, without DCM             | XC3SD3400A | -0.65       | -0.65 | ns    |

- 1. The numbers in this table are tested using the methodology presented in Table 26 and are based on the operating conditions set forth in Table 7 and Table 10.

- This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, subtract the appropriate adjustment from Table 22. If this is true of the data Input, add the appropriate Input adjustment from the same table.

- 3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, add the appropriate Input adjustment from Table 22. If this is true of the data Input, subtract the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

- 4. DCM output jitter is included in all measurements.

Table 19: Setup and Hold Times for the IOB Input Path (Cont'd)

|                      |                                                                                                                               |             |                 |            | Spe   | Speed |       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|------------|-------|-------|-------|

| Symbol               | Description                                                                                                                   | Conditions  | DELAY_<br>VALUE | Device     | -5    | -4    | Units |

|                      |                                                                                                                               |             | VALUE           |            | Min   | Min   |       |

| T <sub>IOICKPD</sub> | Time from the active transition at the                                                                                        | LVCMOS25(3) | 1               | XC3SD1800A | -1.40 | -1.40 | ns    |

|                      | ICLK input of the Input Flip-Flop (IFF) to the point where data must be held at the Input pin. The Input Delay is programmed. |             | 2               |            | -2.11 | -2.11 | ns    |

|                      |                                                                                                                               |             | 3               |            | -2.48 | -2.48 | ns    |

|                      |                                                                                                                               |             | 4               |            | -2.77 | -2.77 | ns    |

|                      |                                                                                                                               |             | 5               |            | -2.62 | -2.62 | ns    |

|                      |                                                                                                                               |             | 6               |            | -3.06 | -3.06 | ns    |

|                      |                                                                                                                               |             | 7               | XC3SD3400A | -3.42 | -3.42 | ns    |

|                      |                                                                                                                               |             | 8               |            | -3.65 | -3.65 | ns    |

|                      |                                                                                                                               |             | 1               |            | -1.31 | -1.31 | ns    |

|                      |                                                                                                                               |             | 2               |            | -1.88 | -1.88 | ns    |

|                      |                                                                                                                               |             | 3               |            | -2.44 | -2.44 | ns    |

|                      |                                                                                                                               |             | 4               |            | -2.89 | -2.89 | ns    |

|                      |                                                                                                                               |             | 5               |            | -2.83 | -2.83 | ns    |

|                      |                                                                                                                               |             | 6               |            | -3.33 | -3.33 | ns    |

|                      |                                                                                                                               |             | 7               |            | -3.63 | -3.63 | ns    |

|                      |                                                                                                                               |             | 8               |            | -3.96 | -3.96 | ns    |

| Set/Reset            | Pulse Width                                                                                                                   |             |                 |            |       |       |       |

| T <sub>RPW_IOB</sub> | Minimum pulse width to SR control input on IOB                                                                                | -           | _               | All        | 1.33  | 1.61  | ns    |

- 1. The numbers in this table are tested using the methodology presented in Table 26 and are based on the operating conditions set forth in Table 7 and Table 10.

- 2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, add the appropriate Input adjustment from Table 22.

- 3. These hold times require adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, subtract the appropriate Input adjustment from Table 22. When the hold time is negative, it is possible to change the data before the clock's active edge.

Table 20: Sample Window (Source Synchronous)

| Symbol            | Description                                        | Max                                                                                                                                                                                                                                                   | Units |

|-------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| T <sub>SAMP</sub> | Setup and hold capture window of an IOB flip-flop. | The input capture sample window value is highly specific to a particular application, device, package, I/O standard, I/O placement, DCM usage, and clock buffer. Please consult the appropriate Xilinx Answer Record for application-specific values. | ps    |

|                   |                                                    | Answer Record 30879                                                                                                                                                                                                                                   |       |

# **Three-State Output Propagation Times**

# Table 24: Timing for the IOB Three-State Path

|                                    |                                                                                                                                                  |                                                    |        | Speed | Speed Grade |       |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------|-------|-------------|-------|

| Symbol                             | Description                                                                                                                                      | Conditions                                         | Device | -5    | -4          | Units |

|                                    |                                                                                                                                                  |                                                    |        | Max   | Max         |       |

| Synchronous                        | S Output Enable/Disable Times                                                                                                                    |                                                    |        |       |             |       |

| T <sub>IOCKHZ</sub>                | Time from the active transition at the OTCLK input of the Three-state Flip-Flop (TFF) to when the Output pin enters the high-impedance state     | LVCMOS25, 12 mA<br>output drive, Fast slew<br>rate | All    | 1.13  | 1.39        | ns    |

| T <sub>IOCKON</sub> <sup>(2)</sup> | Time from the active transition at TFF's OTCLK input to when the Output pin drives valid data                                                    |                                                    | All    | 3.08  | 3.35        | ns    |

| Asynchronou                        | us Output Enable/Disable Times                                                                                                                   |                                                    |        | -     |             | *     |

| T <sub>GTS</sub>                   | Time from asserting the Global Three State (GTS) input on the STARTUP_SPARTAN3A primitive to when the Output pin enters the high-impedance state | LVCMOS25, 12 mA<br>output drive, Fast slew<br>rate | All    | 9.47  | 10.36       | ns    |

| Set/Reset Tir                      | nes                                                                                                                                              | 1                                                  |        | 1     | •           |       |

| T <sub>IOSRHZ</sub>                | Time from asserting TFF's SR input to when the Output pin enters a high-impedance state                                                          | LVCMOS25, 12 mA output drive, Fast slew            | All    | 1.61  | 1.86        | ns    |

| T <sub>IOSRON</sub> <sup>(2)</sup> | Time from asserting TFF's SR input at TFF to when the Output pin drives valid data                                                               | rate                                               | All    | 3.57  | 3.82        | ns    |

- 1. The numbers in this table are tested using the methodology presented in Table 26 and are based on the operating conditions set forth in Table 7 and Table 10.

- 2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. When this is true, *add* the appropriate Output adjustment from Table 25.

# **Configurable Logic Block (CLB) Timing**

Table 29: CLB (SLICEM) Timing

|                      |                                                                                                                                         | Speed Grade |                |      |      |       |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|------|------|-------|

| Symbol               | Description                                                                                                                             | ı           | -5             |      | -4   | Units |

|                      |                                                                                                                                         | Min         | Max            | Min  | Max  |       |

| Clock-to-Output      | Times                                                                                                                                   |             |                |      |      |       |

| T <sub>CKO</sub>     | When reading from the FFX (FFY) Flip-Flop, the time from the active transition at the CLK input to data appearing at the XQ (YQ) output | -           | 0.60           | -    | 0.68 | ns    |

| Setup Times          |                                                                                                                                         |             |                |      |      |       |

| T <sub>AS</sub>      | Time from the setup of data at the F or G input to the active transition at the CLK input of the CLB                                    | 0.18        | -              | 0.36 | _    | ns    |

| T <sub>DICK</sub>    | Time from the setup of data at the BX or BY input to the active transition at the CLK input of the CLB                                  | 1.58        | -              | 1.88 | -    | ns    |

| Hold Times           |                                                                                                                                         |             | <u>.</u>       | !    |      | •     |

| T <sub>AH</sub>      | Time from the active transition at the CLK input to the point where data is last held at the F or G input                               | 0.00        | -              | 0.00 | -    | ns    |

| T <sub>CKDI</sub>    | Time from the active transition at the CLK input to the point where data is last held at the BX or BY input                             | 0.00        | -              | 0.00 | -    | ns    |

| Clock Timing         |                                                                                                                                         |             | <del>-</del> ! | !    |      |       |

| T <sub>CH</sub>      | The High pulse width of the CLB's CLK signal                                                                                            | 0.63        | -              | 0.75 | _    | ns    |

| T <sub>CL</sub>      | The Low pulse width of the CLK signal                                                                                                   | 0.63        | _              | 0.75 | -    | ns    |

| F <sub>TOG</sub>     | Toggle frequency (for export control)                                                                                                   | 0           | 770            | 0    | 667  | MHz   |

| Propagation Tim      | nes                                                                                                                                     |             |                |      |      |       |

| T <sub>ILO</sub>     | The time it takes for data to travel from the CLB's F (G) input to the X (Y) output                                                     | -           | 0.62           | -    | 0.71 | ns    |

| Set/Reset Pulse      | Width                                                                                                                                   |             |                |      |      |       |

| T <sub>RPW_CLB</sub> | The minimum allowable pulse width, High or Low, to the CLB's SR input                                                                   | 1.33        | -              | 1.61 | -    | ns    |

<sup>1.</sup> The numbers in this table are based on the operating conditions set forth in Table 7.

Table 37: Switching Characteristics for the DLL (Cont'd)

| Symbol                        |                                                  |        | Speed Grade |     |     |     |       |

|-------------------------------|--------------------------------------------------|--------|-------------|-----|-----|-----|-------|

|                               | Description                                      | Device | -5          |     | -4  |     | Units |

|                               |                                                  |        | Min         | Max | Min | Max |       |

| Delay Lines                   |                                                  |        |             |     |     |     |       |

| DCM_DELAY_STEP <sup>(5)</sup> | Finest delay resolution, averaged over all steps | All    | 15          | 35  | 15  | 35  | ps    |

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 7 and Table 36.

- 2. Indicates the maximum amount of output jitter that the DCM adds to the jitter on the CLKIN input.

- For optimal jitter tolerance and faster lock time, use the CLKIN\_PERIOD attribute.

- 4. Some jitter and duty-cycle specifications include 1% of input clock period or 0.01 UI. For example, the data sheet specifies a maximum jitter of ±[1% of CLKIN period + 150]. Assume the CLKIN frequency is 100 MHz. The equivalent CLKIN period is 10 ns and 1% of 10 ns is 0.1 ns or 100 ps. According to the data sheet, the maximum jitter is ±[100 ps + 150 ps] = ±250 ps, averaged over all steps.

- 5. The typical delay step size is 23 ps.

## **Digital Frequency Synthesizer (DFS)**

Table 38: Recommended Operating Conditions for the DFS

|                                |                                              |                               |       | Speed              | Grade |                    |     |

|--------------------------------|----------------------------------------------|-------------------------------|-------|--------------------|-------|--------------------|-----|

| Symbol                         | Descriptio                                   | n                             | -5 -4 |                    | 4     | Units              |     |

|                                |                                              |                               | Min   | Max                | Min   | Max                | 1   |

| Input Frequency Ranges         | 2)                                           |                               |       |                    |       |                    |     |

| F <sub>CLKIN</sub> CLKIN_FREQ_ | Frequency for the CLKIN input                | Frequency for the CLKIN input |       | 333 <sup>(5)</sup> | 0.2   | 333 <sup>(5)</sup> | MHz |

| Input Clock Jitter Toleran     | ce <sup>(3)</sup>                            |                               |       |                    |       |                    |     |

| CLKIN_CYC_JITT_FX_LF           | Cycle-to-cycle jitter at the                 | F <sub>CLKFX</sub> ≤ 150 MHz  | _     | ±300               | _     | ±300               | ps  |

| CLKIN_CYC_JITT_FX_HF           | CLKIN input, based on CLKFX output frequency | F <sub>CLKFX</sub> > 150 MHz  | -     | ±150               | -     | ±150               | ps  |

| CLKIN_PER_JITT_FX              | Period jitter at the CLKIN input             |                               | -     | ±1                 | _     | ±1                 | ns  |

- 1. DFS specifications apply when either of the DFS outputs (CLKFX or CLKFX180) are used.

- 2. If both DFS and DLL outputs are used on the same DCM, follow the more restrictive CLKIN\_FREQ\_DLL specifications in Table 36.

- 3. CLKIN input jitter beyond these limits may cause the DCM to lose lock.

- 4. The DCM specifications are guaranteed when both adjacent DCMs are locked.

- To support double the maximum effective F<sub>CLKIN</sub> limit, set the CLKIN\_DIVIDE\_BY\_2 attribute to TRUE. This attribute divides the incoming clock frequency by two as it enters the DCM.

# Phase Shifter (PS)

Table 40: Recommended Operating Conditions for the PS in Variable Phase Mode

|                          |                                                       | Speed Grade -5 -4 |     |     |       |     |  |

|--------------------------|-------------------------------------------------------|-------------------|-----|-----|-------|-----|--|

| Symbol                   | Description                                           |                   |     | 4   | Units |     |  |

|                          |                                                       | Min Max Min Max   | Max |     |       |     |  |

| Operating Frequency      | Ranges                                                |                   |     |     |       |     |  |

| PSCLK_FREQ<br>(FPSCLK)   | Frequency for the PSCLK input                         | 1                 | 167 | 1   | 167   | MHz |  |

| Input Pulse Requirements |                                                       |                   |     |     |       |     |  |

| PSCLK_PULSE              | PSCLK pulse width as a percentage of the PSCLK period | 40%               | 60% | 40% | 60%   | _   |  |

Table 41: Switching Characteristics for the PS in Variable Phase Mode

| Symbol               | Description                                                                                                                                                    |                | Phase Shift Amount                           | Units |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------|-------|

| Phase Shifting Range |                                                                                                                                                                |                |                                              |       |

| MAX_STEPS(2,3)       | Maximum allowed number of                                                                                                                                      | CLKIN < 60 MHz | ±[INTEGER(10 • (T <sub>CLKIN</sub> − 3 ns))] | steps |

|                      | DCM_DELAY_STEP steps for a given CLKIN clock period, where T = CLKIN clock period in ns. If using CLKIN_DIVIDE_BY_2 = TRUE, double the effective clock period. | CLKIN ≥ 60 MHz | ±[INTEGER(15 • (T <sub>CLKIN</sub> − 3 ns))] |       |

| FINE_SHIFT_RANGE_MIN | Minimum guaranteed delay for variable p                                                                                                                        | phase shifting | ±[MAX_STEPS ●<br>DCM_DELAY_STEP_MIN]         | ns    |

| FINE_SHIFT_RANGE_MAX | Maximum guaranteed delay for variable                                                                                                                          | phase shifting | ±[MAX_STEPS •<br>DCM_DELAY_STEP_MAX]         | ns    |

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 7 and Table 40.

- The maximum variable phase shift range, MAX\_STEPS, is only valid when the DCM is has no initial fixed phase shifting, that is, the PHASE\_SHIFT attribute is set to 0.

- The DCM\_DELAY\_STEP values are provided at the bottom of Table 37.

# **Miscellaneous DCM Timing**

Table 42: Miscellaneous DCM Timing

| Symbol         | Description                           | Min | Max | Units           |

|----------------|---------------------------------------|-----|-----|-----------------|

| DCM_RST_PW_MIN | Minimum duration of a RST pulse width | 3   | -   | CLKIN<br>cycles |

# **DNA Port Timing**

Table 43: DNA\_PORT Interface Timing

| Symbol               | Description                                            | Min | Max      | Units |

|----------------------|--------------------------------------------------------|-----|----------|-------|

| T <sub>DNASSU</sub>  | Setup time on SHIFT before the rising edge of CLK      | 1.0 | -        | ns    |

| T <sub>DNASH</sub>   | Hold time on SHIFT after the rising edge of CLK        | 0.5 | _        | ns    |

| T <sub>DNADSU</sub>  | Setup time on DIN before the rising edge of CLK        | 1.0 | -        | ns    |

| T <sub>DNADH</sub>   | Hold time on DIN after the rising edge of CLK          | 0.5 | -        | ns    |

| T <sub>DNARSU</sub>  | Setup time on READ before the rising edge of CLK       | 5.0 | 10,000   | ns    |

| T <sub>DNARH</sub>   | Hold time on READ after the rising edge of CLK         | 0.0 | _        | ns    |

| T <sub>DNADCKO</sub> | Clock-to-output delay on DOUT after rising edge of CLK | 0.5 | 1.5      | ns    |

| T <sub>DNACLKF</sub> | CLK frequency                                          | 0.0 | 100      | MHz   |

| T <sub>DNACLKH</sub> | CLK High time                                          | 1.0 | $\infty$ | ns    |

| T <sub>DNACLKL</sub> | CLK Low time                                           | 1.0 | $\infty$ | ns    |

#### Notes:

1. The minimum READ pulse width is 5 ns, and the maximum READ pulse width is 10  $\mu$ s.

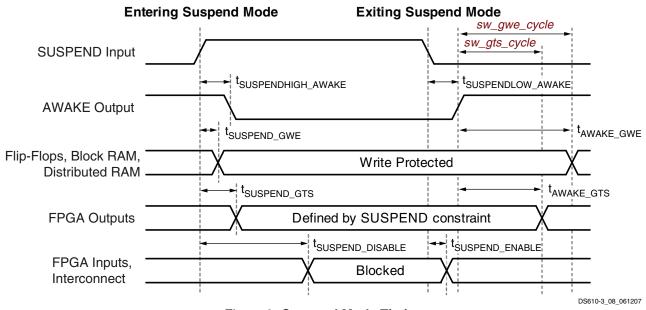

# **Suspend Mode Timing**

Figure 9: Suspend Mode Timing

Table 44: Suspend Mode Timing Parameters

| Symbol                         | Description                                                                                                                                                          | Min  | Тур        | Max  | Units |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------|-------|

| Entering Suspend Mo            | ode                                                                                                                                                                  |      |            |      |       |

| T <sub>SUSPENDHIGH_AWAKE</sub> | Rising edge of SUSPEND pin to falling edge of AWAKE pin without glitch filter ( <i>suspend_filter:No</i> )                                                           | _    | 7          | _    | ns    |

| T <sub>SUSPENDFILTER</sub>     | Adjustment to SUSPEND pin rising edge parameters when glitch filter enabled (suspend_filter:Yes)                                                                     | +160 | +300       | +600 | ns    |

| T <sub>SUSPEND_GTS</sub>       | Rising edge of SUSPEND pin until FPGA output pins drive their defined SUSPEND constraint behavior                                                                    | -    | 10         | -    | ns    |

| T <sub>SUSPEND_GWE</sub>       | Rising edge of SUSPEND pin to write-protect lock on all writable clocked elements                                                                                    | -    | <5         | -    | ns    |

| T <sub>SUSPEND_DISABLE</sub>   | Rising edge of the SUSPEND pin to FPGA input pins and interconnect disabled                                                                                          | -    | 340        | -    | ns    |

| Exiting Suspend Mod            | de                                                                                                                                                                   | •    |            |      |       |

| T <sub>SUSPENDLOW_AWAKE</sub>  | Falling edge of the SUSPEND pin to rising edge of the AWAKE pin. Does not include DCM lock time.                                                                     | _    | 4 to 108   | _    | μS    |

| T <sub>SUSPEND_ENABLE</sub>    | Falling edge of the SUSPEND pin to FPGA input pins and interconnect re-enabled                                                                                       | -    | 3.7 to 109 | -    | μS    |

| T <sub>AWAKE_GWE1</sub>        | Rising edge of the AWAKE pin until write-protect lock released on all writable clocked elements, using <b>sw_clk:InternalClock</b> and <b>sw_gwe_cycle:1</b> .       | -    | 67         | -    | ns    |

| T <sub>AWAKE_GWE512</sub>      | Rising edge of the AWAKE pin until write-protect lock released on all writable clocked elements, using <b>sw_clk:InternalClock</b> and <b>sw_gwe_cycle:512</b> .     | -    | 14         | -    | μs    |

| T <sub>AWAKE_GTS1</sub>        | Rising edge of the AWAKE pin until outputs return to the behavior described in the FPGA application, using <b>sw_clk:InternalClock</b> and <b>sw_gts_cycle:1</b> .   | -    | 57         | 1    | ns    |

| T <sub>AWAKE_GTS512</sub>      | Rising edge of the AWAKE pin until outputs return to the behavior described in the FPGA application, using <b>sw_clk:InternalClock</b> and <b>sw_gts_cycle:512</b> . | -    | 14         | -    | μs    |

- 1. These parameters based on characterization.

- 2. For information on using the Spartan-3A DSP Suspend feature, see XAPP480: Using Suspend Mode in Spartan-3 Generation FPGAs.

# Configuration and JTAG Timing

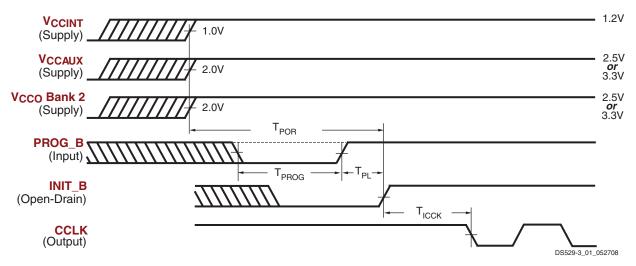

## **General Configuration Power-On/Reconfigure Timing**

#### Notes:

- 1. The  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  supplies can be applied in any order.

- 2. The Low-going pulse on PROG\_B is optional after power-on but necessary for reconfiguration without a power cycle.

- 3. The rising edge of INIT\_B samples the voltage levels applied to the mode pins (M0 M2).

Figure 10: Waveforms for Power-On and the Beginning of Configuration

Table 45: Power-On Timing and the Beginning of Configuration

| Cumbal                          | Description                                                                                                                                                               | Dovice | All Speed Grades |     | Units |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|-----|-------|

| Symbol                          | Description                                                                                                                                                               | Device | Min              | Max | Units |

| T <sub>POR</sub> <sup>(2)</sup> | The time from the application of $V_{CCINT}$ , $V_{CCAUX}$ , and $V_{CCO}$ Bank 2 supply voltage ramps (whichever occurs last) to the rising transition of the INIT_B pin | All    | -                | 18  | ms    |

| T <sub>PROG</sub>               | The width of the low-going pulse on the PROG_B pin                                                                                                                        | All    | 0.5              | -   | μs    |

| T <sub>PL</sub> <sup>(2)</sup>  | The time from the rising edge of the PROG_B pin to the rising transition on the INIT_B pin                                                                                | All    | -                | 2   | ms    |

| T <sub>INIT</sub>               | Minimum Low pulse width on INIT_B output                                                                                                                                  | All    | 300              | _   | ns    |

| T <sub>ICCK</sub> (3)           | The time from the rising edge of the INIT_B pin to the generation of the configuration clock signal at the CCLK output pin                                                | All    | 0.5              | 4   | μs    |

- The numbers in this table are based on the operating conditions set forth in Table 7. This means power must be applied to all V<sub>CCINT</sub>, V<sub>CCO</sub>, and V<sub>CCAUX</sub> lines.

- 2. Power-on reset and the clearing of configuration memory occurs during this period.

- 3. This specification applies only to the Master Serial, SPI, and BPI modes.

- 4. For details on configuration, see UG332 Spartan-3 Generation Configuration User Guide.

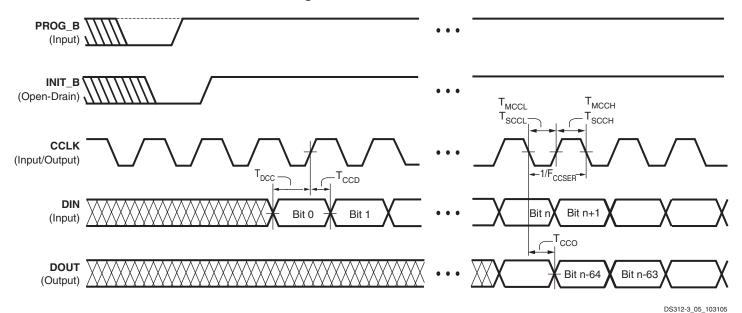

# **Master Serial and Slave Serial Mode Timing**

Figure 11: Waveforms for Master Serial and Slave Serial Configuration

Table 50: Timing for the Master Serial and Slave Serial Configuration Modes

| Cumbal             | Danavi                                                                                                 |                                         | Slave/ | All Speed Grades |             | l lmita |  |

|--------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------|--------|------------------|-------------|---------|--|

| Symbol             | Descri                                                                                                 | ption                                   | Master | Min              | Max         | Units   |  |

| Clock-to-O         | utput Times                                                                                            |                                         |        |                  |             |         |  |

| T <sub>CCO</sub>   | The time from the falling transition on the CCLK pin to data appearing at the DOUT pin                 |                                         |        | 1.5              | 10          | ns      |  |

| Setup Time         | es                                                                                                     |                                         |        | 11               |             | 1       |  |

| T <sub>DCC</sub>   | The time from the setup of data at the CCLK pin                                                        | DIN pin to the rising transition at the | Both   | 7                | _           | ns      |  |

| Hold Times         | 5                                                                                                      |                                         |        | 11               | 1           |         |  |

| T <sub>CCD</sub>   | The time from the rising transition at the CCLK pin to the point when data is last held at the DIN pin |                                         | Master | 0.0              | _           | ns      |  |

|                    |                                                                                                        |                                         | Slave  | 1.0              | _           | ns      |  |

| Clock Timi         | ng                                                                                                     |                                         |        | 11               | '           |         |  |

| T <sub>CCH</sub>   | High pulse width at the CCLK input pi                                                                  | n                                       | Master | S                | ee Table 48 |         |  |

|                    |                                                                                                        |                                         | Slave  | S                | ee Table 49 |         |  |

| T <sub>CCL</sub>   | Low pulse width at the CCLK input pin                                                                  |                                         | Master | S                | ee Table 48 |         |  |

|                    |                                                                                                        |                                         | Slave  | S                | ee Table 49 |         |  |

| F <sub>CCSER</sub> | Frequency of the clock signal at the                                                                   | No bitstream compression                | Slave  | 0                | 100         | MHz     |  |

|                    | CCLK input pin <sup>(2)</sup>                                                                          | With bitstream compression              |        | 0                | 100         | MHz     |  |

- 1. The numbers in this table are based on the operating conditions set forth in Table 7.

- 2. For serial configuration with a daisy-chain of multiple FPGAs, the maximum limit is 25 MHz.

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/02/07 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 05/25/07 | 1.0.1   | Minor edits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 06/18/07 | 1.2     | Updated for v1.29 production speed files. Noted banking rules in Table 11 and Table 12. Added DIFF_HSTL_III to Table 12, Table 13, and Table 26. Updated TMDS DC characteristics in Table 13. Updated I/O Test Method values in Table 26. Added Simultaneously Switching Output limits in Table 28. Updated DSP48A timing symbols, descriptions, and values in Table 34. Added power-on timing in Table 45. Added CCLK specifications for Commercial in Table 46 through Table 48. Updated Slave Parallel timing in Table 51. Updated JTAG specifications in Table 56.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 07/16/07 | 2.0     | Added Low-power options and updated typical values for quiescent current in Table 9. Updated DSP48A timing in Table 34 and Table 35.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 06/02/08 | 2.1     | Improved V <sub>CCAUXT</sub> and V <sub>CCO2T</sub> POR minimum in Table 4 and updated V <sub>CCO</sub> POR levels in Figure 10. Added V <sub>IN</sub> to Recommended Operating Conditions in Table 7 and added reference to XAPP459, "Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins." Reduced typical I <sub>CCINTQ</sub> and I <sub>CCAUXQ</sub> quiescent current values by 20%-44% in Table 9. Increased V <sub>IL</sub> max to 0.4V for LVCMOS12/15/18 and improved V <sub>IH</sub> min to 0.7V for LVCMOS12 in Table 10. Changed V <sub>OL</sub> max to 0.4V and V <sub>OH</sub> min to V <sub>CCO</sub> -0.4V for LVCMOS15/18 in Table 11. Added reference to V <sub>CCAUX</sub> in Simultaneously Switching Output Guidelines. Removed DNA_RETENTION limit of 10 years in Table 14 since number of Read cycles is the only unique limit. Updated speed files to v1.31 in Table 16 and elsewhere. Updated IOB Setup and Hold times with device-specific values in Table 19. Added reference to Sample Window in Table 20. Updated IOB Propagation times with device-specific values in Table 21. Improved SSTL_18_II SSO value in Table 28. Improved F <sub>BUFG</sub> for -4 to 334 MHz in Table 32. Added references to 375 MHz performance via SCD 4103 in Table 32, Table 37, Table 38, and Table 39. Added explanatory footnotes to DSP48A Timing tables. Simplified DSP48A F <sub>MAX</sub> to value with all registers used in Table 35. Improved FBUFG in Table 32 for -4 speed grade. Updated CCLK output maximum period in Table 46 to match minimum frequency in Table 47. Replaced BPI with SPI specification descriptions in Table 52. Corrected BPI Figure 14 and Table 54 from falling edge to rising edge. Added references to Spartan-3 Generation User Guides. Updated links. |

| 03/11/09 | 2.2     | Changed typical quiescent current temperature from ambient to quiescent. Updated selected I/O standard DC characteristics. Removed PCIX IOSTANDARD due to limited PCIX interface support. Added T <sub>IOPI</sub> and T <sub>IOPID</sub> to Table 21. Updated BPI configuration waveforms in Figure 14 and updated Table 55. Removed references to SCD 4103.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10/04/10 | 3.0     | Added $I_{IK}$ to Table 3. Updated description for $V_{IN}$ in Table 7 including adding note 4. Also, added note 2 to $I_{L}$ in Table 8 to note potential leakage between pins of a differential pair. Added note 6 to Table 10. Updated notes 5 and 6 in Table 12. Corrected symbols for $T_{SUSPEND\_GTS}$ and $T_{SUSPEND\_GWE}$ in Table 44.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

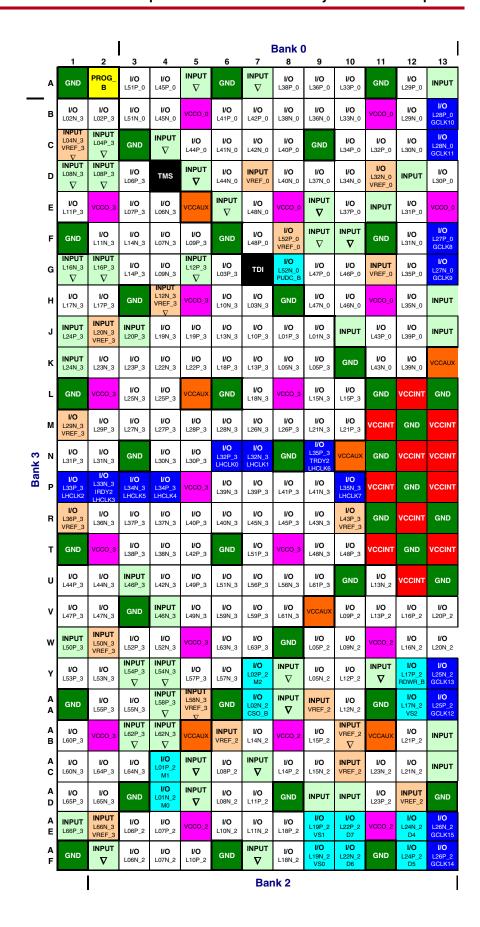

# Spartan-3A DSP FPGA Family: Pinout Descriptions

DS610 (v3.0) October 4, 2010

**Product Specification**

# Introduction

This section describes how the various pins on a Spartan®-3A DSP FPGA connect within the supported component packages and provides device-specific thermal characteristics. For general information on the pin functions and the package characteristics, see the *Packaging* section in UG331: *Spartan-3 Generation FPGA User Guide*.

Spartan-3A DSP FPGAs are available in both standard and Pb-free, RoHS versions of each package, with the Pb-free version adding a "G" to the middle of the package code. Except for the thermal characteristics, all information for the standard package applies equally to the Pb-free package.

# **Pin Types**

Most pins on a Spartan-3A DSP FPGA are general-purpose, user-defined I/O pins. There are, however, up to 12 different functional types of pins on Spartan-3A DSP packages, as outlined in Table 57. In the package footprint drawings that follow, the individual pins are color-coded according to pin type as in the table.

Table 57: Types of Pins on Spartan-3A DSP FPGAs

| Type/Color<br>Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Name(s) in Type                                                                          |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| I/O                | Unrestricted, general-purpose user-I/O pin. Most pins can be paired together to form differential I/Os.                                                                                                                                                                                                                                                                                                                                         | IO_#<br>IO_Lxxy_#                                                                            |

| INPUT              | Unrestricted, general-purpose input-only pin. This pin does not have an output structure, differential termination resistor, or PCI clamp diode.                                                                                                                                                                                                                                                                                                | IP_#<br>IP_Lxxy_#                                                                            |

| DUAL               | Dual-purpose pin used in some configuration modes during the configuration process and then usually available as a user I/O after configuration. If the pin is not used during configuration, this pin behaves as an I/O-type pin. See <a href="UG332"><u>UG332</u></a> : Spartan-3 Generation Configuration User Guide for additional information on these signals.                                                                            | M[2:0] PUDC_B CCLK MOSI/CSI_B D[7:1] D0/DIN CSO_B RDWR_B INIT_B A[25:0] VS[2:0] LDC[2:0] HDC |

| VREF               | Dual-purpose pin that is either a user-I/O pin or Input-only pin, or, along with all other VREF pins in the same bank, provides a reference voltage input for certain I/O standards. If used for a reference voltage within a bank, all VREF pins within the bank must be connected.                                                                                                                                                            | IP/VREF_# IP_Lxxy_#/VREF_# IO/VREF_# IO_Lxxy_#/VREF_#                                        |

| CLK                | Either a user-I/O pin or an input to a specific clock buffer driver. Packages have 16 global clock inputs that optionally clock the entire device. The RHCLK inputs optionally clock the right half of the device. The LHCLK inputs optionally clock the left half of the device. See the Using Global Clock Resources chapter in <a href="UG331">UG331</a> : Spartan-3 Generation FPGA User Guide for additional information on these signals. | IO_Lxxy_#/GCLK[15:0],<br>IO_Lxxy_#/LHCLK[7:0],<br>IO_Lxxy_#/RHCLK[7:0]                       |

| CONFIG             | Dedicated configuration pin, two per device. Not available as a user-I/O pin. Every package has two dedicated configuration pins. These pins are powered by VCCAUX. See the <u>UG332</u> : Spartan-3 Generation Configuration User Guide for additional information on the DONE and PROG_B signals.                                                                                                                                             | DONE, PROG_B                                                                                 |

<sup>©</sup> Copyright 2007–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

Table 63: Spartan-3A DSP CS484 Pinout (Cont'd)

| Bank | Pin Name  | CS484<br>Ball | Туре  |

|------|-----------|---------------|-------|

| 3    | IO_L36P_3 | V4            | I/O   |

| 3    | IO_L35N_3 | W1            | I/O   |

| 3    | IO_L37N_3 | W2            | I/O   |

| 3    | IO_L37P_3 | W3            | I/O   |

| 3    | IO_L35P_3 | Y1            | I/O   |

| 3    | IP_L39P_3 | Y2            | INPUT |

| 3    | VCCO_3    | E2            | VCCO  |

| 3    | VCCO_3    | J2            | VCCO  |

| 3    | VCCO_3    | J5            | VCCO  |

| 3    | VCCO_3    | N2            | VCCO  |

| 3    | VCCO_3    | P5            | VCCO  |

| 3    | VCCO_3    | V2            | VCCO  |

| GND  | GND       | A1            | GND   |

| GND  | GND       | A22           | GND   |

| GND  | GND       | AA7           | GND   |

| GND  | GND       | AA11          | GND   |

| GND  | GND       | AA16          | GND   |

| GND  | GND       | AB1           | GND   |

| GND  | GND       | AB22          | GND   |

| GND  | GND       | B7            | GND   |

| GND  | GND       | B12           | GND   |

| GND  | GND       | B16           | GND   |