#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f248t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F248

- PIC18F258

- PIC18F448

- PIC18F458

These devices are available in 28-pin, 40-pin and 44-pin packages. They are differentiated from each other in four ways:

1. PIC18FX58 devices have twice the Flash program memory and data RAM of PIC18FX48 devices (32 Kbytes and 1536 bytes vs. 16 Kbytes and 768 bytes, respectively).

- 2. PIC18F2X8 devices implement 5 A/D channels, as opposed to 8 for PIC18F4X8 devices.

- 3. PIC18F2X8 devices implement 3 I/O ports, while PIC18F4X8 devices implement 5.

- 4. Only PIC18F4X8 devices implement the Enhanced CCP module, analog comparators and the Parallel Slave Port.

All other features for devices in the PIC18FXX8 family, including the serial communications modules, are identical. These are summarized in Table 1-1.

Block diagrams of the PIC18F2X8 and PIC18F4X8 devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2.

| Fe                                                                 | eatures                          | PIC18F248                                                                        | PIC18F258                                                                        | PIC18F448                                                                        | PIC18F458                                                                        |                                           |                                           |  |

|--------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--|

| Operating Fre                                                      | quency                           | DC – 40 MHz                                                                      |                                           |                                           |  |

| Internal                                                           | Bytes                            | 16K                                                                              | 32K                                                                              | 16K                                                                              | 32K                                                                              |                                           |                                           |  |

| Program<br>Memory                                                  | # of Single-Word<br>Instructions | 8192                                                                             | 16384                                                                            | 16384 8192                                                                       |                                                                                  |                                           |                                           |  |

| Data Memory                                                        | (Bytes)                          | 768                                                                              | 1536                                                                             | 768                                                                              | 1536                                                                             |                                           |                                           |  |

| Data EEPROM Memory (Bytes)                                         |                                  | 256                                                                              | 256                                                                              | 256                                                                              | 256                                                                              |                                           |                                           |  |

| Interrupt Sources                                                  |                                  | 17                                                                               | 17                                                                               | 21                                                                               | 21                                                                               |                                           |                                           |  |

| I/O Ports                                                          |                                  | Ports A, B, C                                                                    | Ports A, B, C                                                                    | Ports A, B, C, D, E                                                              | Ports A, B, C, D, E                                                              |                                           |                                           |  |

| Timers                                                             |                                  | 4                                                                                | 4                                                                                | 4                                                                                | 4                                                                                |                                           |                                           |  |

| Capture/Compare/PWM Modules                                        |                                  | 1                                                                                | 1                                                                                | 1                                                                                | 1                                                                                |                                           |                                           |  |

| Enhanced Capture/Compare/<br>PWM Modules                           |                                  | —                                                                                | _                                                                                | 1                                                                                | 1                                                                                |                                           |                                           |  |

| Serial Communications                                              |                                  | MSSP, CAN,<br>Addressable USART                                                  | ASSP, CAN, MSSP, CAN, essable USART Addressable USART                            |                                                                                  | MSSP, CAN,<br>Addressable USART                                                  |                                           |                                           |  |

| Parallel Communications (PSP)                                      |                                  | No                                                                               | No                                                                               | Yes                                                                              | Yes                                                                              |                                           |                                           |  |

| 10-bit Analog-t                                                    | o-Digital Converter              | 5 input channels                                                                 | 5 input channels                                                                 | 8 input channels                                                                 | 8 input channels                                                                 |                                           |                                           |  |

| Analog Compa                                                       | arators                          | No                                                                               | No                                                                               | 2                                                                                | 2                                                                                |                                           |                                           |  |

| Analog Compa                                                       | arators VREF Output              | N/A                                                                              | N/A                                                                              | Yes                                                                              | Yes                                                                              |                                           |                                           |  |

| Resets (and Delays)                                                |                                  | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) |                                           |                                           |  |

| Programmable                                                       | Low-Voltage Detect               | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |                                           |                                           |  |

| Programmable                                                       | e Brown-out Reset                | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |                                           |                                           |  |

| CAN Module                                                         |                                  | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |                                           |                                           |  |

| In-Circuit Serial Programming <sup>™</sup><br>(ICSP <sup>™</sup> ) |                                  | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |                                           |                                           |  |

| Instruction Set                                                    | t                                | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  |                                           |                                           |  |

| Packages                                                           |                                  |                                                                                  |                                                                                  | 28-pin SPDIP<br>28-pin SOIC                                                      | 28-pin SPDIP<br>28-pin SOIC                                                      | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP |  |

### TABLE 1-1: PIC18FXX8 DEVICE FEATURES

|                                                       | Pi            | n Numb | ber     |      | Pin                    | Buffer               |                                                                                                       |

|-------------------------------------------------------|---------------|--------|---------|------|------------------------|----------------------|-------------------------------------------------------------------------------------------------------|

| Pin Name                                              | PIC18F248/258 | PIC    | 18F448/ | 458  | Туре                   | Туре                 | Description                                                                                           |

|                                                       | SPDIP, SOIC   | PDIP   | TQFP    | PLCC |                        |                      |                                                                                                       |

|                                                       |               | 10     |         | 01   |                        |                      | PORTD is a bidirectional I/O por<br>These pins have TTL input buffe<br>when external memory is enable |

| RD0/PSP0/C1IN+<br>RD0<br>PSP0<br>C1IN+                | _             | 19     | 38      | 21   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 1 input.                                      |

| RD1/PSP1/C1IN-<br>RD1<br>PSP1<br>C1IN-                | _             | 20     | 39      | 22   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 1 input.                                      |

| RD2/PSP2/C2IN+<br>RD2<br>PSP2<br>C2IN+                | _             | 21     | 40      | 23   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 2 input.                                      |

| RD3/PSP3/C2IN-<br>RD3<br>PSP3<br>C2IN-                | _             | 22     | 41      | 24   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 2 input.                                      |

| RD4/PSP4/ECCP1/<br>P1A<br>RD4<br>PSP4<br>ECCP1<br>P1A | _             | 27     | 2       | 30   | I/O<br>I/O<br>I/O<br>O | ST<br>TTL<br>ST<br>— | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 capture/compare.<br>ECCP1 PWM output A.            |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                    | _             | 28     | 3       | 31   | I/O<br>I/O<br>O        | ST<br>TTL<br>—       | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output B.                                      |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                    | _             | 29     | 4       | 32   | I/O<br>I/O<br>O        | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output C.                                      |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D                    | _             | 30     | 5       | 33   | I/O<br>I/O<br>O        | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output D.                                      |

# TABLE 1-2: PIC18FXX8 PINOUT I/O DESCRIPTIONS (CONTINUED)

OD = Open-Drain (no P diode to VDD)

# 4.10 Access Bank

The Access Bank is an architectural enhancement that is very useful for C compiler code optimization. The techniques used by the C compiler are also useful for programs written in assembly.

This data memory region can be used for:

- · Intermediate computational values

- · Local variables of subroutines

- · Faster context saving/switching of variables

- · Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the upper 160 bytes in Bank 15 (SFRs) and the lower 96 bytes in Bank 0. These two sections will be referred to as Access Bank High and Access Bank Low, respectively. Figure 4-6 indicates the Access Bank areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register or in the Access Bank.

When forced in the Access Bank (a = 0), the last address in Access Bank Low is followed by the first address in Access Bank High. Access Bank High maps most of the Special Function Registers so that these registers can be accessed without any software overhead.

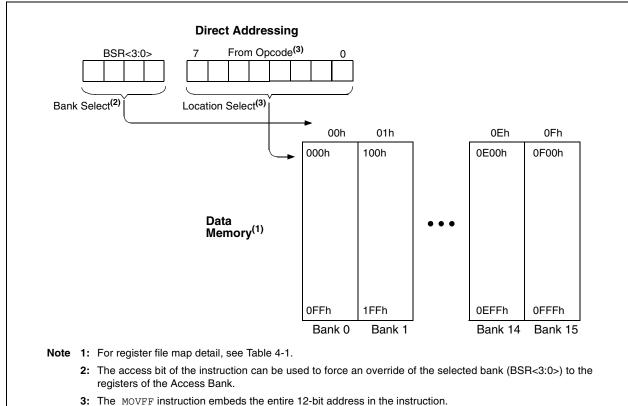

# 4.11 Bank Select Register (BSR)

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's and writes will have no effect.

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The Status register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR since the 12-bit addresses are embedded into the instruction word.

Section 4.12 "Indirect Addressing, INDF and FSR Registers" provides a description of indirect addressing, which allows linear addressing of the entire RAM space.

#### \_\_\_\_\_

FIGURE 4-7: DIRECT ADDRESSING

| <b>REGISTER 8-2:</b> | INTCON2          | NTCON2: INTERRUPT CONTROL REGISTER 2                                                                                    |                 |              |             |            |              |        |  |  |  |

|----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|-------------|------------|--------------|--------|--|--|--|

|                      | R/W-1            | R/W-1                                                                                                                   | R/W-1           | U-0          | U-0         | R/W-1      | U-0          | R/W-1  |  |  |  |

|                      | RBPU             | INTEDG0                                                                                                                 | INTEDG1         | _            | _           | TMR0IP     |              | RBIP   |  |  |  |

|                      | bit 7            |                                                                                                                         |                 |              |             |            |              | bit 0  |  |  |  |

|                      |                  |                                                                                                                         |                 |              |             |            |              |        |  |  |  |

| bit 7                | RBPU: PO         | RTB Pull-up                                                                                                             | Enable bit      |              |             |            |              |        |  |  |  |

|                      |                  | <ul> <li>All PORTB pull-ups are disabled</li> <li>PORTB pull-ups are enabled by individual port latch values</li> </ul> |                 |              |             |            |              |        |  |  |  |

| bit 6                | INTEDG0:         | TEDG0: External Interrupt 0 Edge Select bit                                                                             |                 |              |             |            |              |        |  |  |  |

|                      |                  | = Interrupt on rising edge                                                                                              |                 |              |             |            |              |        |  |  |  |

|                      |                  | = Interrupt on falling edge                                                                                             |                 |              |             |            |              |        |  |  |  |

| bit 5                |                  | External Inte                                                                                                           |                 | e Select bit |             |            |              |        |  |  |  |

|                      |                  | ot on rising e<br>ot on falling e                                                                                       | •               |              |             |            |              |        |  |  |  |

| bit 4-3              |                  | ented: Read                                                                                                             | •               |              |             |            |              |        |  |  |  |

| bit 2                | -                | MR0 Overflo                                                                                                             |                 | Priority bit |             |            |              |        |  |  |  |

|                      | 1 = High pi      |                                                                                                                         |                 |              |             |            |              |        |  |  |  |

|                      | 0 = Low pr       | •                                                                                                                       |                 |              |             |            |              |        |  |  |  |

| bit 1                | Unimplem         | ented: Read                                                                                                             | <b>d as</b> '0' |              |             |            |              |        |  |  |  |

| bit 0                | RBIP: RB         | Port Change                                                                                                             | Interrupt Pr    | iority bit   |             |            |              |        |  |  |  |

|                      | 1 = High p       | •                                                                                                                       |                 |              |             |            |              |        |  |  |  |

|                      | 0 = Low priority |                                                                                                                         |                 |              |             |            |              |        |  |  |  |

|                      |                  |                                                                                                                         |                 |              |             |            |              |        |  |  |  |

|                      | Legend:          |                                                                                                                         |                 |              |             |            |              |        |  |  |  |

|                      | R = Reada        | ble bit                                                                                                                 | W = W           | ritable bit  | U = Unin    | nplemented | bit, read as | ʻ0'    |  |  |  |

|                      | -n = Value       | at POR                                                                                                                  | '1' = B         | it is set    | '0' = Bit i | s cleared  | x = Bit is u | nknown |  |  |  |

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

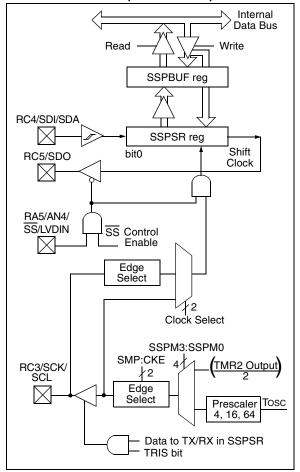

# 17.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

## 17.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

# 17.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

## 17.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/SS/LVDIN

Figure 17-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 17-1: MSSP BLOCK DIAGRAM (SPI™ MODE)

# 17.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

## REGISTER 17-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/A | Р   | S   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

|       |       |     |     |     |     |     |       |

bit 7 SMP: Sample bit SPI Master mode: 1 = Input data sampled at end of data output time 0 = Input data sampled at middle of data output time SPI Slave mode: SMP must be cleared when SPI is used in Slave mode. bit 6 CKE: SPI Clock Edge Select bit 1 = Transmit occurs on transition from active to Idle clock state 0 = Transmit occurs on transition from Idle to active clock state Note: Polarity of clock state is set by the CKP bit (SSPCON1<4>). D/A: Data/Address bit bit 5 Used in I<sup>2</sup>C mode only. bit 4 P: Stop bit Used in I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared. bit 3 S: Start bit Used in I<sup>2</sup>C mode only. bit 2 R/W: Read/Write Information bit Used in I<sup>2</sup>C mode only. UA: Update Address bit bit 1 Used in I<sup>2</sup>C mode only. bit 0 BF: Buffer Full Status bit (Receive mode only) 1 = Receive complete, SSPBUF is full 0 = Receive not complete, SSPBUF is empty Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' '1' = Bit is set '0' = Bit is cleared -n = Value at POR x = Bit is unknown

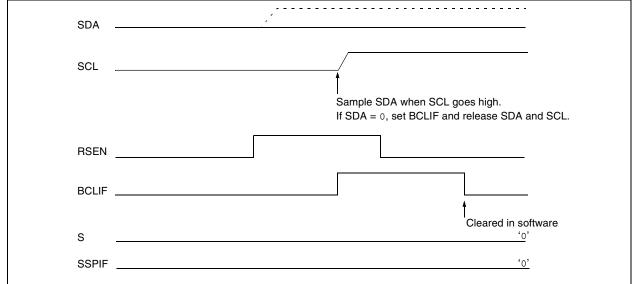

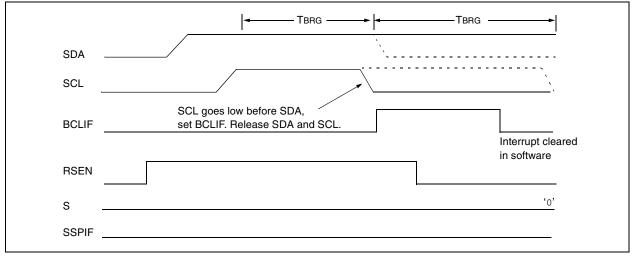

# 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins

counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 17-30).

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 17-30: BUS COLLISION DURING A REPEATED START CONDITION (CASE 2)

# 18.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in that the shift clock is supplied externally at the RC6/ TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTA register).

#### 18.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

### 18.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

#### REGISTER 19-5: TXBnSIDH: TRANSMIT BUFFER n STANDARD IDENTIFIER, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 SID10:SID3: Standard Identifier bits if EXIDE = 0 (TXBnSID Register) or Extended Identifier bits EID28:EID21 if EXIDE = 1

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 19-6: TXBnSIDL: TRANSMIT BUFFER n STANDARD IDENTIFIER, LOW BYTE REGISTERS

|   | R/W-x |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | SID2  | SID1  | SID0  | —     | EXIDE | _     | EID17 | EID16 |

| - | bit 7 |       |       |       |       |       |       | bit 0 |

- bit 7-5 SID2:SID0: Standard Identifier bits if EXIDE = 0 or Extended Identifier bits EID20:EID18 if EXIDE = 1

- bit 4 Unimplemented: Read as '0'

- bit 3 **EXIDE:** Extended Identifier enable bit

- 1 = Message will transmit extended ID, SID10:SID0 becomes EID28:EID18

- 0 = Message will transmit standard ID, EID17:EID0 are ignored

- bit 2 Unimplemented: Read as '0'

- bit 1-0 EID17:EID16: Extended Identifier bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 19-7: TXBnEIDH: TRANSMIT BUFFER n EXTENDED IDENTIFIER, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 EID15:EID8: Extended Identifier bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 20.4 A/D Conversions

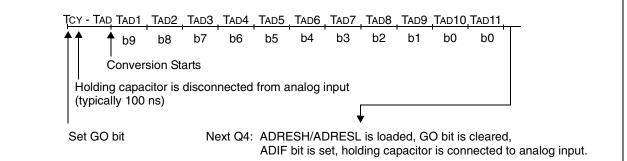

Figure 20-4 shows the operation of the A/D converter after the GO bit has been set. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will not be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, acquisition on the selected channel is automatically started.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

# 20.4.1 A/D RESULT REGISTERS

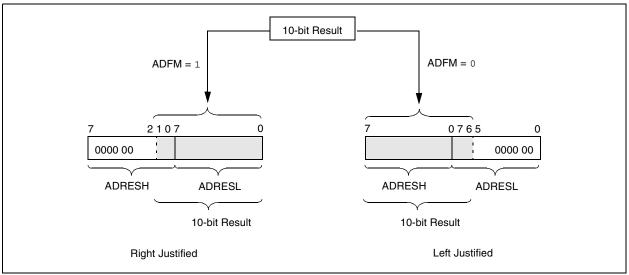

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16 bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 20-3 shows the operation of the A/D result justification. The extra bits are loaded with '0's. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

FIGURE 20-3: A/D RESULT JUSTIFICATION

# 20.5 Use of the ECCP Trigger

An A/D conversion can be started by the "special event trigger" of the ECCP module. This requires that the ECCP1M3:ECCP1M0 bits (ECCP1CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/ DONE bit will be set, starting the A/D conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH/ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the "special event trigger" will be ignored by the A/D module but will still reset the Timer1 (or Timer3) counter.

# FIGURE 20-4: A/D CONVERSION TAD CYCLES

#### TABLE 20-3: SUMMARY OF A/D REGISTERS

| Name   | Bit 7                | Bit 6               | Bit 5       | Bit 4    | Bit 3 | Bit 2   | Bit 1         | Bit 0                  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------|---------------------|-------------|----------|-------|---------|---------------|------------------------|----------------------|---------------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL           | TMR0IE      | INT0IE   | RBIE  | TMR0IF  | <b>INT0IF</b> | RBIF                   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF                | RCIF        | TXIF     | SSPIF | CCP1IF  | TMR2IF        | TMR1IF                 | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE                | RCIE        | TXIE     | SSPIE | CCP1IE  | TMR2IE        | TMR1IE                 | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP                | RCIP        | TXIP     | SSPIP | CCP1IP  | TMR2IP        | TMR1IP                 | 1111 1111            | 1111 1111                       |

| PIR2   | _                    | CMIF <sup>(1)</sup> | _           | EEIF     | BCLIF | LVDIF   | TMR3IF        | ECCP1IF <sup>(1)</sup> | -0-0 0000            | -0-0 0000                       |

| PIE2   | _                    | CMIE <sup>(1)</sup> | _           | EEIE     | BCLIE | LVDIE   | TMR3IE        | ECCP1IE <sup>(1)</sup> | -0-0 0000            | -0-0 0000                       |

| IPR2   | _                    | CMIP <sup>(1)</sup> | _           | EEIP     | BCLIP | LVDIP   | TMR3IP        | ECCP1IP <sup>(1)</sup> | -1-1 1111            | -1-1 1111                       |

| ADRESH | A/D Resul            | t Register          |             |          |       |         |               |                        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL | A/D Resul            | t Register          |             |          |       |         |               |                        | xxxx xxxx            | uuuu uuuu                       |

| ADCON0 | ADCS1                | ADCS0               | CHS2        | CHS1     | CHS0  | GO/DONE | _             | ADON                   | 0000 00-0            | 0000 00-0                       |

| ADCON1 | ADFM                 | ADCS2               | _           | _        | PCFG3 | PCFG2   | PCFG1         | PCFG0                  | 00 0000              | 00 0000                         |

| PORTA  | _                    | RA6                 | RA5         | RA4      | RA3   | RA2     | RA1           | RA0                    | -x0x 0000            | -u0u 0000                       |

| TRISA  |                      | PORTA Data          | a Direction | Register |       |         |               |                        | -111 1111            | -111 1111                       |

| PORTE  | _                    | —                   | _           | _        | _     | RE2     | RE1           | RE0                    | xxx                  | 000                             |

| LATE   | _                    | —                   | _           | _        |       | LATE2   | LATE1         | LATE0                  | xxx                  | uuu                             |

| TRISE  | IBF                  | OBF                 | IBOV        | PSPMODE  |       | TRISE2  | TRISE1        | TRISE0                 | 0000 -111            | 0000 -111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These bits are reserved on PIC18F2X8 devices; always maintain these bits clear.

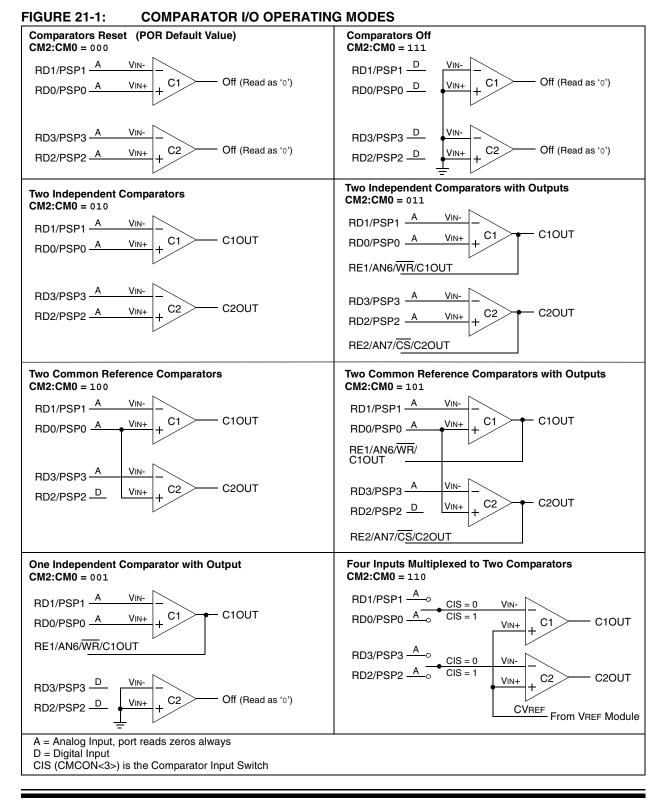

# 21.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select these modes. Figure 21-1 shows the eight possible modes. The TRISD register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Section 27.0 "Electrical Characteristics".

Note: Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

### TABLE 25-2: PIC18FXXX INSTRUCTION SET

| Mnemo                                  | onic,                           | Description                           | Cycles     | Cycles 16-Bit Ir |              |      | /ord | Status          | Natas      |

|----------------------------------------|---------------------------------|---------------------------------------|------------|------------------|--------------|------|------|-----------------|------------|

| Opera                                  | nds                             | Description                           | Cycles     | MSb              |              |      | LSb  | Affected        | Notes      |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |                                 |                                       |            |                  |              |      |      |                 |            |

| ADDWF                                  | f, d, a                         | Add WREG and f                        | 1          | 0010             | 01da         | ffff | ffff | C, DC, Z, OV, N |            |

| ADDWFC                                 | f, d, a                         | Add WREG and Carry bit to f           | 1          | 0010             | 00da         | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF                                  | f, d, a                         | AND WREG with f                       | 1          | 0001             | 01da         | ffff | ffff | Z, N            | 1,2        |

| CLRF                                   | f, a                            | Clear f                               | 1          | 0110             | 101a         | ffff | ffff | Z               | 2          |

| COMF                                   | f, d, a                         | Complement f                          | 1          | 0001             | 11da         | ffff | ffff | Z, N            | 1, 2       |

| CPFSEQ                                 | f, a                            | Compare f with WREG, skip =           | 1 (2 or 3) | 0110             | 001a         | ffff | ffff | None            | 4          |

| CPFSGT                                 | f, a                            | Compare f with WREG, skip >           | 1 (2 or 3) | 0110             | 010a         | ffff | ffff | None            | 4          |

| CPFSLT                                 | f, a                            | Compare f with WREG, skip <           | 1 (2 or 3) | 0110             | 000a         | ffff | ffff | None            | 1, 2       |

| DECF                                   | f, d, a                         | Decrement f                           | 1          | 0000             | 01da         | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                                 | f, d, a                         | Decrement f, Skip if 0                | 1 (2 or 3) | 0010             | 11da         | ffff | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ                                 | f, d, a                         | Decrement f, Skip if Not 0            | 1 (2 or 3) |                  | 11da         | ffff | ffff | None            | 1, 2       |

| INCF                                   | f, d, a                         | Increment f                           | 1 ΄        | 0010             | 10da         | ffff | ffff | C, DC, Z, OV, N | 1.2.3.4    |

| INCFSZ                                 |                                 | Increment f, Skip if 0                | 1 (2 or 3) |                  | 11da         | ffff | ffff | None            | 4          |

| INFSNZ                                 | f, d, a                         | Increment f, Skip if Not 0            | 1 (2 or 3) |                  | 10da         | ffff | ffff | None            | 1, 2       |

| IORWF                                  | f, d, a                         | Inclusive OR WREG with f              | 1          |                  | 00da         | ffff | ffff |                 | 1, 2       |

| MOVF                                   | f, d, a                         | Move f                                | 1          |                  | 00da         | ffff |      | Z, N            | 1          |

| MOVFF                                  | f <sub>s</sub> , f <sub>d</sub> |                                       | 2          |                  | ffff         | ffff |      | None            |            |

| movi i                                 | 's, 'a                          | f <sub>d</sub> (destination) 2nd word | -          |                  | ffff         | ffff | ffff |                 |            |

| MOVWF                                  | f, a                            | Move WREG to f                        | 1          |                  | 111a         | ffff | ffff | None            |            |

| MULWF                                  | f, a                            | Multiply WREG with f                  | 1          |                  | 001a         | ffff |      | None            |            |

| NEGF                                   | f, a                            | Negate f                              | 1          |                  | 110a         | ffff | ffff | C, DC, Z, OV, N | 1 2        |

| RLCF                                   | f, d, a                         | Rotate Left f through Carry           | 1          |                  | 01da         | ffff | ffff | C, Z, N         | 1, 2       |

| RLNCF                                  |                                 | Rotate Left f (No Carry)              | 1          |                  | 01da<br>01da | ffff | ffff |                 | 1, 2       |

| RRCF                                   | f, d, a                         | Rotate Right f through Carry          | 1          |                  | 01da<br>00da | ffff | ffff | C, Z, N         | 1, 2       |

| -                                      | f, d, a                         | Rotate Right f (No Carry)             | -          |                  |              |      | ffff |                 |            |

| RRNCF                                  |                                 |                                       | 1          |                  | 00da         | ffff |      |                 |            |

| SETF                                   | f, a                            | Set f                                 | -          |                  | 100a         | ffff |      | None            | 1 0        |

| SUBFWB                                 | f, d, a                         | Subtract f from WREG with<br>borrow   | 1          | 0101             | 01da         | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWF                                  | f, d, a                         | Subtract WREG from f                  | 1          | 0101             | 11da         | ffff | ffff | C, DC, Z, OV, N |            |

|                                        | f, d, a                         | Subtract WREG from f with             | 1          |                  | 10da         | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

|                                        |                                 | borrow                                |            |                  |              |      |      |                 |            |

| SWAPF                                  | f, d, a                         | Swap nibbles in f                     | 1          | 0011             | 10da         | ffff | ffff | None            | 4          |

| TSTFSZ                                 | f, a                            | Test f, skip if 0                     | 1 (2 or 3) | 0110             | 011a         | ffff | ffff | None            | 1, 2       |

| XORWF                                  | f, d, a                         | Exclusive OR WREG with f              | 1          | 0001             | 10da         | ffff | ffff | Z, N            |            |

| BIT-ORIEN                              | NTED FI                         | LE REGISTER OPERATIONS                | ļ          |                  |              |      |      | ł               |            |

| BCF                                    | f, b, a                         | Bit Clear f                           | 1          | 1001             | bbba         | ffff | ffff | None            | 1, 2       |

| BSF                                    | f, b, a                         | Bit Set f                             | 1          | 1000             | bbba         | ffff | ffff | None            | 1, 2       |

| BTFSC                                  | f, b, a                         | Bit Test f, Skip if Clear             | 1 (2 or 3) | 1011             | bbba         | ffff | ffff | None            | 3, 4       |

| BTFSS                                  |                                 | Bit Test f, Skip if Set               | 1 (2 or 3) |                  | bbba         | ffff | ffff | None            | 3, 4       |

| BTG                                    |                                 | Bit Toggle f                          | 1          |                  | bbba         | ffff |      | None            | 1, 2       |

|                                        |                                 | Dert register is modified as a fur    | -          |                  |              |      |      |                 |            |

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

### TABLE 25-2: PIC18FXXX INSTRUCTION SET (CONTINUED)

| Mnem     | onic,  | Description                     | Qualas | 16-Bit Instruction Word |      |      |      | Status          |       |

|----------|--------|---------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

| Operands |        | Description                     | Cycles | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL  |        |                                 |        |                         |      |      |      |                 |       |

| ADDLW    | k      | Add literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW    | k      | AND literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW    | k      | Inclusive OR literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR     | f, k   | Move literal (12-bit)2nd word   | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|          |        | to FSRx 1st word                |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB    | k      | Move literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW    | k      | Move literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW    | k      | Multiply literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW    | k      | Return with literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW    | k      | Subtract WREG from literal      | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW    | k      | Exclusive OR literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA ME  | MORY ← | PROGRAM MEMORY OPERA            | TIONS  |                         |      |      |      |                 |       |

| TBLRD*   |        | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+  |        | Table Read with post-increment  |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-  |        | Table Read with post-decrement  |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*  |        | Table Read with pre-increment   |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*   |        | Table Write                     | 2 (5)  | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+  |        | Table Write with post-increment |        | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-  |        | Table Write with post-decrement |        | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*  |        | Table Write with pre-increment  |        | 0000                    | 0000 | 0000 | 1111 | None            |       |

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| XORWF                                                  | Exclusive                                                                                                                   | Exclusive OR W with f                                                               |                                                                   |                                              |                                                |  |  |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------|------------------------------------------------|--|--|--|

| Syntax:                                                | [label] >                                                                                                                   | KORWF                                                                               | f [,d                                                             | [,a]]                                        |                                                |  |  |  |

| Operands:                                              | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                         | d ∈ [0,1]                                                                           |                                                                   |                                              |                                                |  |  |  |

| Operation:                                             | (W) .XOR.                                                                                                                   | (f) $\rightarrow$ des                                                               | st                                                                |                                              |                                                |  |  |  |

| Status Affected:                                       | N, Z                                                                                                                        |                                                                                     |                                                                   |                                              |                                                |  |  |  |

| Encoding:                                              | 0001                                                                                                                        | 10da                                                                                | fff                                                               | f                                            | ffff                                           |  |  |  |

| Description:                                           | Exclusive C<br>register 'f'.<br>in W. If 'd' is<br>in register '<br>Access Bar<br>overriding t<br>then the ba<br>the BSR va | If 'd' is 'o'<br>s '1', the r<br>f' (defaul<br>hk will be<br>he BSR v<br>nk will be | , the result<br>result<br>t). If 'a<br>selec<br>value.<br>e selec | esult<br>is sto<br>a' is '<br>ted,<br>If 'a' | is stored<br>bred back<br>0', the<br>' is '1', |  |  |  |

| Words:                                                 | 1                                                                                                                           |                                                                                     |                                                                   |                                              |                                                |  |  |  |

| Cycles:                                                | 1                                                                                                                           |                                                                                     |                                                                   |                                              |                                                |  |  |  |

| Q Cycle Activity:                                      |                                                                                                                             |                                                                                     |                                                                   |                                              |                                                |  |  |  |

| Q1                                                     | Q2                                                                                                                          | Q3                                                                                  |                                                                   | Q4                                           |                                                |  |  |  |

| Decode                                                 | Read<br>register 'f'                                                                                                        | Process<br>Data                                                                     |                                                                   | Write to<br>destination                      |                                                |  |  |  |

| Example:                                               | XORWF                                                                                                                       | REG                                                                                 | ~                                                                 |                                              |                                                |  |  |  |

| Before Instruct<br>REG<br>W<br>After Instructio<br>REG | = 0xAF<br>= 0xB5<br>on<br>= 0x1A                                                                                            |                                                                                     |                                                                   |                                              |                                                |  |  |  |

| W                                                      | = 0xB5                                                                                                                      |                                                                                     |                                                                   |                                              |                                                |  |  |  |

# TABLE 27-3: COMPARATOR SPECIFICATIONS

| Param<br>No. | Sym    | Characteristics                           | Min  | Тур          | Max          | Units    | Comments                |

|--------------|--------|-------------------------------------------|------|--------------|--------------|----------|-------------------------|

| D300         | VIOFF  | Input Offset Voltage                      | —    | ±5.0         | ±10          | mV       |                         |

| D301         | VICM   | Input Common Mode Voltage                 | 0    | _            | Vdd - 1.5    | V        |                         |

| D302         | CMRR   | CMRR                                      | +55* |              |              | db       |                         |

| D300         | TRESP  | Response Time <sup>(1)</sup>              | —    | 300*<br>350* | 400*<br>600* | ns<br>ns | PIC18FXX8<br>PIC18LFXX8 |

| D301         | TMC20V | Comparator Mode Change to<br>Output Valid | —    | —            | 10*          | μs       |                         |

These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

# TABLE 27-4: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> VDD range as described in <b>Section 27.1 "DC Characteristics"</b> , $-40^{\circ}C < TA < +125^{\circ}C$ |      |                              |        |     |        |       |          |  |

|---------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|--------|-----|--------|-------|----------|--|

| Param No.                                                                                                                             | Sym  | Characteristics              | Min    | Тур | Max    | Units | Comments |  |

| D310                                                                                                                                  | VRES | Resolution                   | VDD/24 |     | VDD/32 | LSB   |          |  |

| D311                                                                                                                                  | VRAA | Absolute Accuracy            |        | Ι   | 0.5    | LSB   |          |  |

| D312                                                                                                                                  | Vrur | Unit Resistor Value (R)      | _      | 2K* |        | Ω     |          |  |

| D310                                                                                                                                  | TSET | Settling Time <sup>(1)</sup> | _      |     | 10*    | μs    |          |  |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from 0000 to 1111.

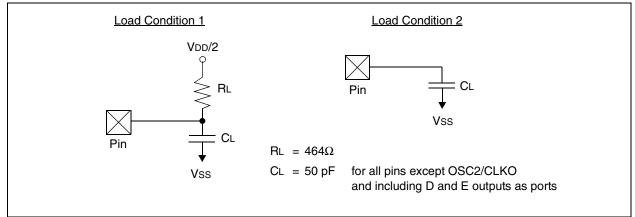

## 27.3.2 TIMING CONDITIONS

The temperature and voltages specified in Table 27-5 apply to all timing specifications unless otherwise noted. Figure 27-5 specifies the load conditions for the timing specifications.

### TABLE 27-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

| AC CHARACTERISTICS | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Operating voltage VDD range as described in DC specification,<br>Section 27.1 "DC Characteristics".<br>LF parts operate for industrial temperatures only.                                      |

### FIGURE 27-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

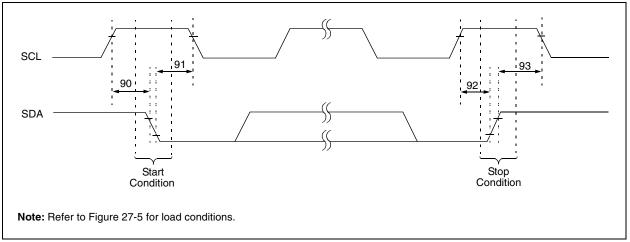

| TABLE 27-17: | I <sup>2</sup> C <sup>™</sup> BUS START/STOP BITS REQUIREMENTS (SLAVE MODE | E) |

|--------------|----------------------------------------------------------------------------|----|

|--------------|----------------------------------------------------------------------------|----|

| Param<br>No. | Symbol  | Characte        | ristic       | Min  | Max | Units | Conditions                   |  |

|--------------|---------|-----------------|--------------|------|-----|-------|------------------------------|--|

| 90           | TSU:STA | Start Condition | 100 kHz mode | 4700 |     | ns    | Only relevant for Repeated   |  |

|              |         | Setup Time      | 400 kHz mode | 600  | _   |       | Start condition              |  |

| 91           | THD:STA | Start Condition | 100 kHz mode | 4000 |     | ns    | After this period, the first |  |

|              |         | Hold Time       | 400 kHz mode | 600  | -   |       | clock pulse is generated     |  |

| 92           | TSU:STO | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                              |  |

|              |         | Setup Time      | 400 kHz mode | 600  | _   |       |                              |  |

| 93           | THD:STO | Stop Condition  | 100 kHz mode | 4000 | -   | ns    |                              |  |

|              |         | Hold Time       | 400 kHz mode | 600  | _   |       |                              |  |

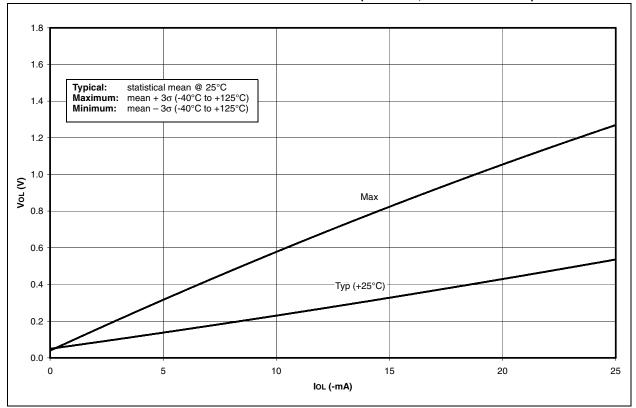

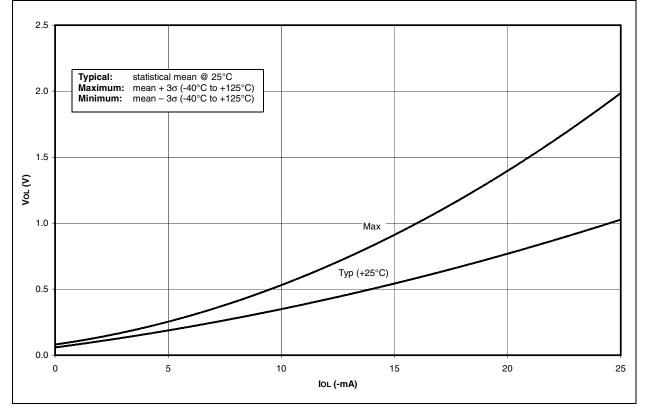

# FIGURE 28-23: TYPICAL AND MAXIMUM Vol vs. lol (VDD = 5V, -40°C TO +125°C)

NOTES: