#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f258-e-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>REGISTER 8-3:</b> | INTCON3:                                                                                                                                          | INTERRU                                      |                                 | ROL REGI     | STER 3       |             |              |        |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------|--------------|--------------|-------------|--------------|--------|--|

|                      | R/W-1                                                                                                                                             | R/W-1                                        | U-0                             | R/W-0        | R/W-0        | U-0         | R/W-0        | R/W-0  |  |

|                      | INT2IP                                                                                                                                            | INT1IP                                       | —                               | INT2IE       | INT1IE       |             | INT2IF       | INT1IF |  |

|                      | bit 7                                                                                                                                             |                                              |                                 |              |              |             | ·            | bit 0  |  |

| bit 7                | INT2IP: IN                                                                                                                                        | Γ2 External                                  | Interrupt Pri                   | ority bit    |              |             |              |        |  |

|                      | 5 1                                                                                                                                               | 1 = High priority<br>0 = Low priority        |                                 |              |              |             |              |        |  |

| bit 6                | INT1IP: IN                                                                                                                                        | INT1IP: INT1 External Interrupt Priority bit |                                 |              |              |             |              |        |  |

|                      | 5 1                                                                                                                                               | 1 = High priority<br>0 = Low priority        |                                 |              |              |             |              |        |  |

| bit 5                | Unimplem                                                                                                                                          | ented: Read                                  | <b>d as</b> '0'                 |              |              |             |              |        |  |

| bit 4                | INT2IE: IN                                                                                                                                        | T2 External                                  | Interrupt En                    | able bit     |              |             |              |        |  |

|                      |                                                                                                                                                   |                                              | external inter<br>external inte |              |              |             |              |        |  |

| bit 3                | INT1IE: IN                                                                                                                                        | T1 External                                  | Interrupt En                    | able bit     |              |             |              |        |  |

|                      |                                                                                                                                                   |                                              | external inter<br>external inte |              |              |             |              |        |  |

| bit 2                | Unimplem                                                                                                                                          | ented: Read                                  | <b>d as</b> '0'                 |              |              |             |              |        |  |

| bit 1                | INT2IF: INT                                                                                                                                       | 2 External                                   | Interrupt Fla                   | g bit        |              |             |              |        |  |

|                      |                                                                                                                                                   |                                              | interrupt occ<br>interrupt did  |              | be cleared i | n software) |              |        |  |

| bit 0                | INT1IF: INT                                                                                                                                       | 1 External                                   | Interrupt Fla                   | g bit        |              |             |              |        |  |

|                      | <ul> <li>1 = The INT1 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT1 external interrupt did not occur</li> </ul> |                                              |                                 |              |              |             |              |        |  |

|                      | Legend:                                                                                                                                           |                                              |                                 |              |              |             |              |        |  |

|                      | R = Readal                                                                                                                                        | ole bit                                      | W = W                           | /ritable bit | U = Unin     | nplemented  | bit, read as | '0'    |  |

|                      | -n = Value a                                                                                                                                      | at POR                                       | '1' = B                         | it is set    | '0' = Bit i  | s cleared   | x = Bit is u | nknown |  |

| Note: | Interrupt flag bits are set when an interrupt condition occurs regardless of the state |

|-------|----------------------------------------------------------------------------------------|

|       | of its corresponding enable bit or the global interrupt enable bit. User software      |

|       | should ensure the appropriate interrupt flag bits are clear prior to enabling an       |

|       | interrupt. This feature allows software polling.                                       |

© 2006 Microchip Technology Inc.

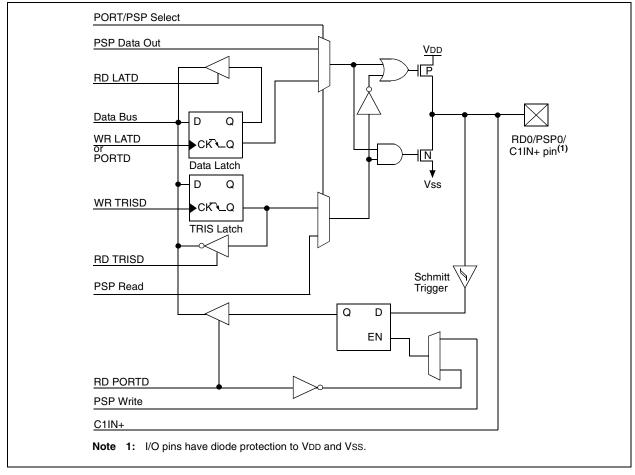

# 9.4 PORTD, TRISD and LATD Registers

| Note: | This | port  | is  | only | available | on | the |

|-------|------|-------|-----|------|-----------|----|-----|

|       | PIC1 | 8F448 | and | PIC1 | 8F458.    |    |     |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register for the port is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

PORTD uses Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTD can be configured as an 8-bit wide, microprocessor port (Parallel Slave Port or PSP) by setting the control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 10.0 "Parallel Slave Port"** for additional information.

PORTD is also multiplexed with the analog comparator module and the ECCP module.

| EXAMF | PLE 9-4: | INITIALIZING PORTD      |

|-------|----------|-------------------------|

| CLRF  | PORTD    | ; Initialize PORTD by   |

|       |          | ; clearing output       |

|       |          | ; data latches          |

| CLRF  | LATD     | ; Alternate method      |

|       |          | ; to clear output       |

|       |          | ; data latches          |

| MOVLW | 07h      | ; comparator off        |

| MOVWF | CMCON    |                         |

| MOVLW | 0CFh     | ; Value used to         |

|       |          | ; initialize data       |

|       |          | ; direction             |

| MOVWF | TRISD    | ; Set RD3:RD0 as inputs |

|       |          | ; RD5:RD4 as outputs    |

|       |          | ; RD7:RD6 as inputs     |

# FIGURE 9-9: PORTD BLOCK DIAGRAM IN I/O PORT MODE

| Name    | Bit 7                                                                       | Bit 6          | Bit 5         | Bit 4         | Bit 3         | Bit 2      | Bit 1  | Bit 0   |         | e on<br>BOR | allo    | e on<br>other<br>sets |

|---------|-----------------------------------------------------------------------------|----------------|---------------|---------------|---------------|------------|--------|---------|---------|-------------|---------|-----------------------|

| INTCON  | GIE/<br>GIEH                                                                | PEIE/<br>GIEL  | TMR0IE        | INTOIE        | RBIE          | TMR0IF     | INTOIF | RBIF    | 0000    | 000x        | 0000    | 000u                  |

| PIR1    | PSPIF <sup>(1)</sup>                                                        | ADIF           | RCIF          | TXIF          | SSPIF         | CCP1IF     | TMR2IF | TMR1IF  | 0000    | 0000        | 0000    | 0000                  |

| PIE1    | PSPIE <sup>(1)</sup>                                                        | ADIE           | RCIE          | TXIE          | SSPIE         | CCP1IE     | TMR2IE | TMR1IE  | 0000    | 0000        | 0000    | 0000                  |

| IPR1    | PSPIP <sup>(1)</sup>                                                        | ADIP           | RCIP          | TXIP          | SSPIP         | CCP1IP     | TMR2IP | TMR1IP  | 1111    | 1111        | 1111    | 1111                  |

| TRISD   | PORTD Da                                                                    | ata Direction  | Register      |               |               |            |        |         | 1111    | 1111        | 1111    | 1111                  |

| TMR1L   | Holding Re                                                                  | gister for the | e Least Sigr  | nificant Byte | of the 16-bi  | t TMR1 Reg | gister |         | xxxx    | xxxx        | uuuu    | uuuu                  |

| TMR1H   | Holding Re                                                                  | gister for the | e Most Sign   | ificant Byte  | of the 16-bit | TMR1 Reg   | ister  |         | xxxx    | xxxx        | uuuu    | uuuu                  |

| T1CON   | RD16                                                                        | _              | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS | TMR10N  | 0-00    | 0000        | u-uu    | uuuu                  |

| CCPR1L  | Capture/Co                                                                  | ompare/PWN     | /I Register 1 | (LSB)         |               | •          | •      |         | xxxx    | xxxx        | uuuu    | uuuu                  |

| CCPR1H  | Capture/Co                                                                  | ompare/PWN     | /I Register 1 | (MSB)         |               |            |        |         | xxxx    | xxxx        | uuuu    | uuuu                  |

| CCP1CON | _                                                                           | _              | DC1B1         | DC1B0         | CCP1M3        | CCP1M2     | CCP1M1 | CCP1M0  | 00      | 0000        | 00      | 0000                  |

| PIR2    |                                                                             | CMIF           | _             | EEIF          | BCLIF         | LVDIF      | TMR3IF | ECCP1IF | - 0 - 0 | 0000        | - 0 - 0 | 0000                  |

| PIE2    |                                                                             | CMIE           | _             | EEIE          | BCLIE         | LVDIE      | TMR3IE | ECCP1IE | - 0 - 0 | 0000        | - 0 - 0 | 0000                  |

| IPR2    |                                                                             | CMIP           | _             | EEIP          | BCLIP         | LVDIP      | TMR3IP | ECCP1IP | -1-1    | 1111        | -1-1    | 1111                  |

| TMR3L   | Holding Register for the Least Significant Byte of the 16-bit TMR3 Register |                |               |               |               |            |        |         | xxxx    | xxxx        | uuuu    | uuuu                  |

| TMR3H   | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register  |                |               |               |               |            |        |         | xxxx    | xxxx        | uuuu    | uuuu                  |

| T3CON   | RD16                                                                        | T3ECCP1        | T3CKPS1       | T3CKPS0       | T3CCP1        | T3SYNC     | TMR3CS | TMR3ON  | 0000    | 0000        | uuuu    | uuuu                  |

# TABLE 15-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: These registers or register bits are not implemented on the PIC18F248 and PIC18F258 and read as '0's.

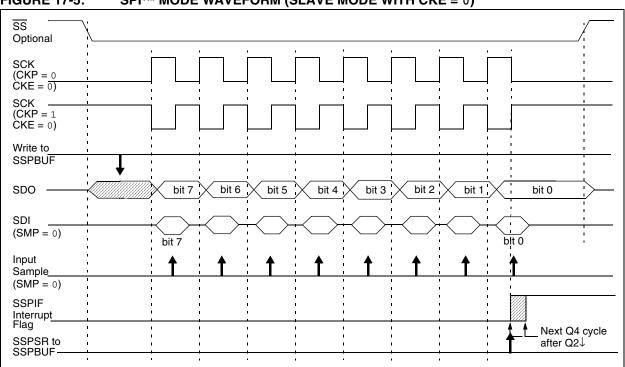

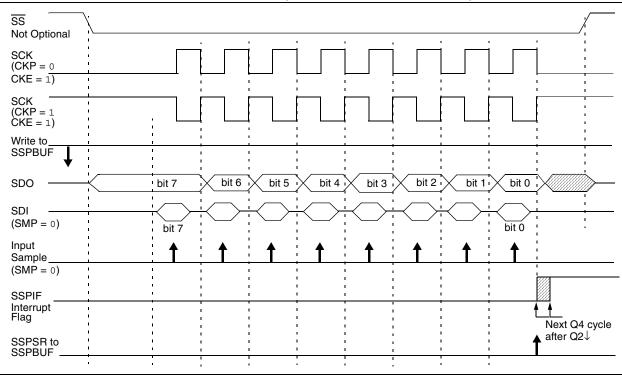

# FIGURE 17-6: SPI™ MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

© 2006 Microchip Technology Inc.

# 19.2.3.1 Message Acceptance Filters and Masks

This subsection describes the message acceptance filters and masks for the CAN receive buffers.

# REGISTER 19-21: RXFnSIDH: RECEIVE ACCEPTANCE FILTER n STANDARD IDENTIFIER FILTER, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 SID10:SID3: Standard Identifier Filter bits if EXIDEN = 0 or Extended Identifier Filter bits EID28:EID21 if EXIDEN = 1

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 19-22: RXFnSIDL: RECEIVE ACCEPTANCE FILTER n STANDARD IDENTIFIER FILTER, LOW BYTE REGISTERS

|         | R/W-x                      | R/W-x       | R/W-x           | U-0                              | R/W-x  | U-0 | R/W-x | R/W-x |

|---------|----------------------------|-------------|-----------------|----------------------------------|--------|-----|-------|-------|

|         | SID2                       | SID1        | SID0            | _                                | EXIDEN | _   | EID17 | EID16 |

|         | bit 7                      |             |                 |                                  |        |     |       | bit 0 |

| bit 7-5 |                            |             |                 | er bits if EXII<br>0:EID18 if EX |        |     |       |       |

| bit 4   | Unimplemented: Read as '0' |             |                 |                                  |        |     |       |       |

| bit 3   | EXIDEN: E                  | xtended Ide | ntifier Filter  | Enable bit                       |        |     |       |       |

|         |                            | •           | •               | ID message<br>ID message         |        |     |       |       |

| bit 2   | Unimplem                   | ented: Read | <b>d as</b> '0' |                                  |        |     |       |       |

| bit 1-0 | EID17:EID                  | 16: Extende | d Identifier I  | Filter bits                      |        |     |       |       |

|         |                            |             |                 |                                  |        |     |       |       |

|         | Legend:                    |             |                 |                                  |        |     |       |       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

### 19.2.5 CAN MODULE I/O CONTROL REGISTER

bit bit

bit

bit

This register controls the operation of the CAN module's I/O pins in relation to the rest of the microcontroller.

# REGISTER 19-32: CIOCON: CAN I/O CONTROL REGISTER

|       | U-0                                                                                        | U-0         | R/W-0         | R/W-0                         | U-0          | U-0       | U-0          | U-0    |

|-------|--------------------------------------------------------------------------------------------|-------------|---------------|-------------------------------|--------------|-----------|--------------|--------|

|       | —                                                                                          | _           | ENDRHI        | CANCAP                        | —            |           | _            | —      |

|       | bit 7                                                                                      |             |               |                               |              |           |              | bit 0  |

| t 7-6 | Unimplemented: Read as '0'                                                                 |             |               |                               |              |           |              |        |

| t 5   | ENDRHI: E                                                                                  | nable Drive | High bit      |                               |              |           |              |        |

|       | 1 = CANTX pin will drive VDD when recessive<br>0 = CANTX pin will tri-state when recessive |             |               |                               |              |           |              |        |

| t 4   | CANCAP:                                                                                    | CAN Messa   | ge Receive    | Capture Ena                   | able bit     |           |              |        |

|       |                                                                                            |             |               | ssage receiv<br>P1 input to 0 |              |           | on RC2/CCF   | 91     |

| t 3-0 | Unimpleme                                                                                  | ented: Read | <b>as</b> '0' |                               |              |           |              |        |

|       |                                                                                            |             |               |                               |              |           |              |        |

|       | Legend:                                                                                    |             |               |                               |              |           |              |        |

|       | R = Readal                                                                                 | ole bit     | W = Writa     | ble bit                       | U = Unim     | plemented | bit, read as | ʻ0'    |

|       | -n = Value a                                                                               | at POR      | '1' = Bit is  | set                           | '0' = Bit is | s cleared | x = Bit is u | nknown |

# 19.3 CAN Modes of Operation

The PIC18FXX8 has six main modes of operation:

- Configuration mode

- Disable mode

- Normal Operation mode

- · Listen Only mode

- · Loopback mode

- Error Recognition mode

All modes, except Error Recognition, are requested by setting the REQOP bits (CANCON<7:5>); Error Recognition is requested through the RXM bits of the Receive Buffer register(s). Entry into a mode is Acknowledged by monitoring the OPMODE bits.

When changing modes, the mode will not actually change until all pending message transmissions are complete. Because of this, the user must verify that the device has actually changed into the requested mode before fUrther Operations Are Executed.

### 19.3.1 CONFIGURATION MODE

The CAN module has to be initialized before the activation. This is only possible if the module is in the Configuration mode. The Configuration mode is requested by setting the REQOP2 bit. Only when the OPMODE2 status bit has a high level can the initialization be performed. Afterwards, the Configuration registers, the Acceptance Mask registers and the Acceptance Filter registers can be written. The module is activated by setting the REQOP control bits to zero.

The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module can not be modified while the module is online. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The CONFIG bit serves as a lock to protect the following registers.

- Configuration registers

- Bus Timing registers

- Identifier Acceptance Filter registers

- Identifier Acceptance Mask registers

In the Configuration mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes.

### 19.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If REQOP<2:0> is set to '001', the module will enter the Module Disable mode. This mode is similar to disabling other peripheral modules by turning off the module enables. This causes the module internal clock to stop unless the module is active (i.e., receiving or transmitting a message). If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an IDLE bus, then accept the module disable command. OPMODE<2:0> = 001 indicates whether the module successfully went into Module Disable mode.

The WAKIF interrupt is the only module interrupt that is still active in the Module Disable mode. If the WAKIE is set, the processor will receive an interrupt whenever the CAN bus detects a dominant state, as occurs with a SOF. If the processor receives an interrupt while it is sleeping, more than one message may get lost. User firmware must anticipate this condition and request retransmission. If the processor is running while it receives an interrupt, only the first message may get lost.

The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

# 19.3.3 NORMAL MODE

This is the standard operating mode of the PIC18FXX8. In this mode, the device actively monitors all bus messages and generates Acknowledge bits, error frames, etc. This is also the only mode in which the PIC18FXX8 will transmit messages over the CAN bus.

# 19.3.4 LISTEN ONLY MODE

Listen Only mode provides a means for the PIC18FXX8 to receive all messages, including messages with errors. This mode can be used for bus monitor applications or for detecting the baud rate in 'hot plugging' situations. For auto-baud detection, it is necessary that there are at least two other nodes which are communicating with each other. The baud rate can be detected empirically by testing different values until valid messages are received. The Listen Only mode is a silent mode, meaning no messages will be transmitted while in this state, including error flags or Acknowledge signals. The filters and masks can be used to allow only particular messages to be loaded into the receive registers, or the filter masks can be set to all zeros to allow a message with any identifier to pass. The error counters are reset and deactivated in this state. The Listen Only mode is activated by setting the mode request bits in the CANCON register.

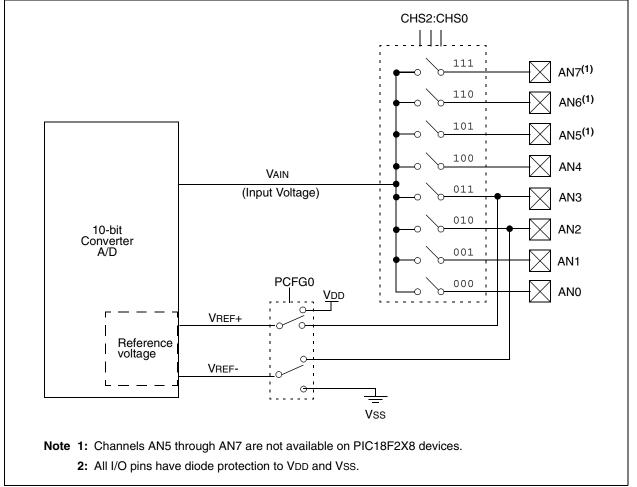

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and VSS) or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF- pin.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter which generates the result via successive approximation.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference) or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 20-1.

### FIGURE 20-1: A/D BLOCK DIAGRAM

To calculate the minimum acquisition time, Equation 20-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 20-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following application system assumptions:

| • | CHOLD | = | 120 pF |

|---|-------|---|--------|

|   |       |   |        |

• Rs =  $2.5 \text{ k}\Omega$

• Conversion Error  $\leq$  1/2 LSb

• VDD =  $5V \rightarrow Rss = 7 k\Omega$

- Temperature =  $50^{\circ}$ C (system max.)

- VHOLD = 0V @ time = 0

### EQUATION 20-1: ACQUISITION TIME

| TACQ | = | Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient |

|------|---|-------------------------------------------------------------------------------------|

|      | = | TAMP + TC + TCOFF                                                                   |

### EQUATION 20-2: A/D MINIMUM CHARGING TIME

| VHOLD | = | $(\text{VREF} - (\text{VREF}/2048)) \bullet (1 - e^{(-\text{Tc/CHOLD}(\text{Ric} + \text{Rss} + \text{Rs}))})$ |

|-------|---|----------------------------------------------------------------------------------------------------------------|

| or    |   |                                                                                                                |

| Тс    | = | $-(120 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/2047)$                                    |

# EXAMPLE 20-1: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ   | =     | TAMP + TC + TCOFF                                                                                                                                                                                           |

|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temper | ature | coefficient is only required for temperatures $> 25^{\circ}$ C.                                                                                                                                             |

| TACQ   | =     | $2 \ \mu s + Tc + [(Temp - 25^{\circ}C)(0.05 \ \mu s/^{\circ}C)]$                                                                                                                                           |

| ТС     | =     | -CHOLD (RIC + RSS + RS) $\ln(1/2047)$<br>-120 pF (1 k $\Omega$ + 7 k $\Omega$ + 2.5 k $\Omega$ ) $\ln(0.0004885)$<br>-120 pF (10.5 k $\Omega$ ) $\ln(0.0004885)$<br>-1.26 $\mu$ s (-7.6241)<br>9.61 $\mu$ s |

| TACQ   | =     | 2 μs + 9.61 μs + [(50°C – 25°C)(0.05 μs/°C)]<br>11.61 μs + 1.25 μs<br>12.86 μs                                                                                                                              |

**Note:** When using external voltage references with the A/D converter, the source impedance of the external voltage references must be less than  $20\Omega$  to obtain the specified A/D resolution. Higher reference source impedances will increase both offset and gain errors. Resistive voltage dividers will not provide a sufficiently low source impedance.

To maintain the best possible performance in A/D conversions, external VREF inputs should be buffered with an operational amplifier or other low output impedance circuit.

### 20.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 12 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. The seven possible options for TAD are:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC oscillator.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 20-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

# 20.3 Configuring Analog Port Pins

The ADCON1, TRISA and TRISE registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins) may cause the input buffer to consume current that is out of the device's specification.

# TABLE 20-1: TAD VS. DEVICE OPERATING FREQUENCIES

| AD Clock  | Source (TAD) |                       | Device F              | requency               |                       |

|-----------|--------------|-----------------------|-----------------------|------------------------|-----------------------|

| Operation | ADCS2:ADCS0  | 20 MHz                | 5 MHz                 | 1.25 MHz               | 333.33 kHz            |

| 2 Tosc    | 000          | 100 ns <sup>(2)</sup> | 400 ns <sup>(2)</sup> | 1.6 μs                 | 6 µs                  |

| 4 Tosc    | 100          | 200 ns <sup>(2)</sup> | 800 ns <sup>(2)</sup> | 3.2 μs                 | 12 μs                 |

| 8 Tosc    | 001          | 400 ns <sup>(2)</sup> | 1.6 μs                | 6.4 μs                 | 24 μs <sup>(3)</sup>  |

| 16 Tosc   | 101          | 800 ns <sup>(2)</sup> | 3.2 μs                | 12.8 μs                | 48 μs <sup>(3)</sup>  |

| 32 Tosc   | 010          | 1.6 μs                | 6.4 μs                | 25.6 μs <sup>(3)</sup> | 96 μs <sup>(3)</sup>  |

| 64 Tosc   | 110          | 3.2 μs                | 12.8 μs               | 51.2 μs <sup>(3)</sup> | 192 μs <sup>(3)</sup> |

| RC        | 011          | 2-6 μs <sup>(1)</sup> | 2-6 μs <sup>(1)</sup> | 2-6 μs <sup>(1)</sup>  | 2-6 μs <sup>(1)</sup> |

Legend: Shaded cells are outside of recommended range.

**2:** These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

#### TABLE 20-2: TAD vs. DEVICE OPERATING FREQUENCIES (FOR EXTENDED, LF DEVICES)

| AD Clock  | Source (TAD) |                       | Device F              | requency               |                       |

|-----------|--------------|-----------------------|-----------------------|------------------------|-----------------------|

| Operation | ADCS2:ADCS0  | 4 MHz                 | 2 MHz                 | 1.25 MHz               | 333.33 kHz            |

| 2 Tosc    | 000          | 500 ns <sup>(2)</sup> | 1.0 μs <sup>(2)</sup> | 1.6 μs <sup>(2)</sup>  | 6 µs                  |

| 4 Tosc    | 100          | 1.0 μs <sup>(2)</sup> | 2.0 μs <sup>(2)</sup> | 3.2 μs <sup>(2)</sup>  | 12 µs                 |

| 8 Tosc    | 001          | 2.0 μs <sup>(2)</sup> | 4.0 μs                | 6.4 μs                 | 24 μs <sup>(3)</sup>  |

| 16 Tosc   | 101          | 4.0 μs <sup>(2)</sup> | 8.0 μs                | 12.8 μs                | 48 μs <sup>(3)</sup>  |

| 32 Tosc   | 010          | 8.0 μs                | 16.0 μs               | 25.6 μs <sup>(3)</sup> | 96 μs <sup>(3)</sup>  |

| 64 Tosc   | 110          | 16.0 μs               | 32.0 μs               | 51.2 μs <sup>(3)</sup> | 192 μs <sup>(3)</sup> |

| RC        | 011          | 3-9 μs <sup>(1)</sup> | 3-9 μs <sup>(1)</sup> | 3-9 μs <sup>(1)</sup>  | 3-9 μs <sup>(1)</sup> |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 6 µs.

- **2:** These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

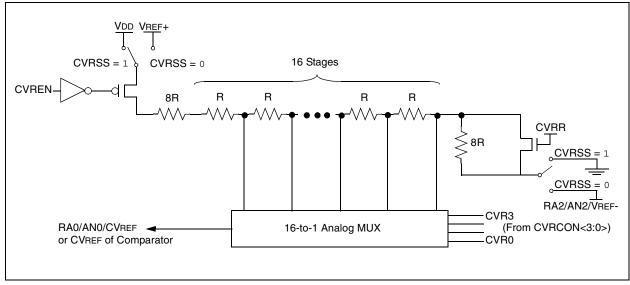

# 22.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 22-1) keep VREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the VREF output changes with fluctuations in that source. The absolute accuracy of the voltage reference can be found in **Section 27.0 "Electrical Characteristics"**.

# 22.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 22.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit CVREN (CVRCON register). This Reset also disconnects the reference from the RA2 pin by clearing bit CVROE (CVRCON register) and selects the high-voltage range by clearing bit CVRR (CVRCON register). The CVRSS value select bits, CVRCON<3:0>, are also cleared.

# 22.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA0/AN0 pin if the TRISA<0> bit is set and the CVROE bit (CVRCON<6>) is set. Enabling the voltage reference output onto the RA0/AN0 pin, with an input signal present, will increase current consumption. Connecting RA0/AN0 as a digital output, with CVRSS enabled, will also increase current consumption.

The RA0/AN0 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 22-2 shows an example buffering technique.

|         |              |               |               |                |                |             | -000000      | 5111)   |

|---------|--------------|---------------|---------------|----------------|----------------|-------------|--------------|---------|

|         | U-0          | U-0           | R/P-1         | U-0            | U-0            | R/P-1       | R/P-1        | R/P-1   |

|         |              | _             | OSCSEN        | _              | _              | FOSC2       | FOSC1        | FOSC0   |

|         | bit 7        |               |               |                |                |             |              | bit 0   |

|         |              |               |               |                |                |             |              |         |

| bit 7-6 | Unimplem     | ented: Read   | <b>as</b> '0' |                |                |             |              |         |

| bit 5   | OSCSEN:      | Oscillator Sy | stem Clock S  | witch Enable   | bit            |             |              |         |

|         |              |               | ock switch op |                |                |             |              |         |

|         | 0 = Oscillat | or system cl  | ock switch op | tion is enable | ed (oscillator | switching   | is enabled)  |         |

| bit 4-3 | Unimplem     | ented: Read   | <b>as</b> '0' |                |                |             |              |         |

| bit 2-0 | FOSC2:FO     | SC0: Oscilla  | tor Selection | bits           |                |             |              |         |

|         |              |               | SC2 configu   |                |                |             |              |         |

|         |              |               | PLL enabled   |                | ency = (4 x F  | OSC)        |              |         |

|         |              |               | SC2 configui  |                | -by-4 clock o  | utout       |              |         |

|         | 011 = RC c   |               |               |                | by + clock o   | uipui       |              |         |

|         | 010 = HS c   | oscillator    |               |                |                |             |              |         |

|         | 001 = XT c   |               |               |                |                |             |              |         |

|         | 000 = LP o   | scillator     |               |                |                |             |              |         |

|         | <b></b>      |               |               |                |                |             |              |         |

|         | Legend:      |               |               |                |                |             |              |         |

|         | R = Readal   | ole bit       | P = Program   | nmable bit     | U = Unimple    | emented bit | t, read as ' | 0'      |

|         | -n = Value v | when device   | is unprogram  | imed           | u = Unchang    | ged from p  | rogramme     | d state |

|         |              |               |               |                |                |             |              |         |

REGISTER 24-1: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

# REGISTER 24-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

|         |                   |               |               |             |           |            |              | · · /    |

|---------|-------------------|---------------|---------------|-------------|-----------|------------|--------------|----------|

|         | U-0               | U-0           | U-0           | U-0         | R/P-1     | R/P-1      | R/P-1        | R/P-1    |

|         | —                 | _             | —             | —           | BORV1     | BORV0      | BOREN        | PWRTEN   |

|         | bit 7             |               |               |             |           |            |              | bit 0    |

| bit 7-4 | -                 | ented: Read   |               |             |           |            |              |          |

| bit 3-2 | BORV1:BC          | DRV0: Brown   | -out Reset V  | oltage bits |           |            |              |          |

|         | 11 = VBOR         | set to 2.0V   |               |             |           |            |              |          |

|         | 10 = VBOR         | set to 2.7V   |               |             |           |            |              |          |

|         | 01 = VBOR         | set to 4.2V   |               |             |           |            |              |          |

|         | 00 = <b>V</b> BOR | set to 4.5V   |               |             |           |            |              |          |

| bit 1   | BOREN: B          | rown-out Res  | set Enable bi | it          |           |            |              |          |

|         | 1 = Brown-        | out Reset en  | abled         |             |           |            |              |          |

|         | 0 = Brown         | out Reset dis | sabled        |             |           |            |              |          |

| bit 0   | <b>PWRTEN:</b>    | Power-up Tir  | mer Enable b  | bit         |           |            |              |          |

|         | 1 = PWRT          | disabled      |               |             |           |            |              |          |

|         | 0 = PWRT          | enabled       |               |             |           |            |              |          |

|         |                   |               |               |             |           |            |              |          |

|         | Legend:           |               |               |             |           |            |              |          |

|         | R = Readal        | ole bit       | P = Program   | mmable bit  | U = Unim  | plemented  | bit, read as | s 'O'    |

|         | -n = Value v      | when device   | is unprogram  | nmed        | u = Uncha | anged from | programm     | ed state |

|         |                   |               |               |             |           |            |              | ,        |

#### REGISTER 24-11: DEVID1: DEVICE ID REGISTER 1 FOR PIC18FXX8 DEVICES (BYTE ADDRESS 3FFFFEh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-5 **DEV2:DEV0:** Device ID bits These bits are used with the DEV<10:3> bits in the Device ID Register 2 to identify the part number.

000 = PIC18F248

001 = PIC18F448

010 = PIC18F258

011 = PIC18F458

bit 4-0 REV4:REV0: Revision ID bits

These bits are used to indicate the device revision.

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

# REGISTER 24-12: DEVID2: DEVICE ID REGISTER 2 FOR PIC18FXX8 DEVICES (BYTE ADDRESS 3FFFFFh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 DEV10:DEV3: Device ID bits

These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.

00001000 = PIC18FXX8

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

#### **GENERAL FORMAT FOR INSTRUCTIONS** FIGURE 25-1: Byte-oriented file register operations **Example Instruction** 10 9 8 7 15 0 OPCODE f (FILE #) ADDWF MYREG, W, B d а d = 0 for result destination to be WREG register d = 1 for result destination to be file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Byte to Byte move operations (2-word) 15 12 11 0 OPCODE f (Source FILE #) MOVFF MYREG1, MYREG2 15 12 11 0 f (Destination FILE #) 1111 f = 12-bit file register address Bit-oriented file register operations 15 12 11 987 0 OPCODE b (BIT #) f (FILE #) а BSF MYREG, bit, B b = 3-bit position of bit in file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Literal operations 15 8 7 0 OPCODE k (literal) MOVLW 0x7F k = 8-bit immediate value **Control** operations CALL, GOTO and Branch operations 15 8 7 0 OPCODE n<7:0> (literal) GOTO Label 15 12 11 0 1111 n<19:8> (literal) n = 20-bit immediate value 15 8 7 0 CALL MYFUNC OPCODE S n<7:0> (literal) 15 12 11 0 n<19:8> (literal) S = Fast bit 15 11 10 0 OPCODE BRA MYFUNC n<10:0> (literal) 15 8 7 0 OPCODE n<7:0> (literal) BC MYFUNC

| GOTO                                       |       | Unconditi                    | onal Bra                           | nch                       |                                                         |   |

|--------------------------------------------|-------|------------------------------|------------------------------------|---------------------------|---------------------------------------------------------|---|

| Syntax:                                    |       | [label] C                    | GOTO k                             |                           |                                                         |   |

| Operands:                                  |       | $0 \le k \le 104$            | 8575                               |                           |                                                         |   |

| Operation:                                 |       | $k \rightarrow PC < 20$      | 0:1>                               |                           |                                                         |   |

| Status Affecte                             | d:    | None                         |                                    |                           |                                                         |   |

| Encoding:<br>1st word (k<7<br>2nd word(k<1 | ,     | 1110<br>1111                 | 1111<br>k <sub>19</sub> kkk        | k <sub>7</sub> kk<br>kkkk | -                                                       |   |

| Description:                               |       | range. The                   | within ent<br>20-bit va<br>GOTO is | ire 2-Mi<br>Iue 'k' is    | nal branch<br>byte memor<br>s loaded int<br>a two-cycle | 0 |

| Words:                                     |       | 2                            |                                    |                           |                                                         |   |

| Cycles:                                    |       | 2                            |                                    |                           |                                                         |   |

| Q Cycle Activ                              | /ity: |                              |                                    |                           |                                                         |   |

| Q1                                         |       | Q2                           | Q                                  | 3                         | Q4                                                      |   |

| Decoc                                      | le    | Read literal<br>'k'<7:0>     | No<br>opera                        | tion                      | Read litera<br>'k'<19:8>,<br>Write to PC                | - |

| No                                         |       | No                           | No                                 |                           | No                                                      |   |

| operati                                    | on    | operation                    | opera                              | tion                      | operation                                               |   |

| Example:<br>After Inst<br>PC               |       | GOTO THI<br>on<br>Address (1 |                                    |                           |                                                         |   |

| INCF                                                    |       | Incremen                                                                                                      | t f                                                                                  |                                                                        |                                                           |                                     |  |  |  |

|---------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------|--|--|--|

| Syntax:                                                 |       | [ label ]                                                                                                     | [ <i>label</i> ] INCF f [,d [,a]]                                                    |                                                                        |                                                           |                                     |  |  |  |

| Operands:                                               |       | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                         | $0 \le f \le 255$<br>$d \in [0,1]$                                                   |                                                                        |                                                           |                                     |  |  |  |

| Operation:                                              |       | (f) + 1 $\rightarrow$ c                                                                                       | lest                                                                                 |                                                                        |                                                           |                                     |  |  |  |

| Status Affecte                                          | ed:   | C, DC, N,                                                                                                     | OV, Z                                                                                |                                                                        |                                                           |                                     |  |  |  |

| Encoding:                                               |       | 0010                                                                                                          | 10da                                                                                 | fff                                                                    | f f                                                       | fff                                 |  |  |  |

| Description:                                            |       | The conte<br>increment<br>placed in V<br>placed bac<br>is '0', the V<br>overriding<br>the bank v<br>BSR value | ed. If 'd' is<br>W. If 'd' is<br>ck in regis<br>Access Ba<br>the BSR<br>vill be sele | s '0', th<br>'1', the<br>ter 'f' (<br>ank will<br>value. I<br>value. l | e result<br>e result<br>default)<br>be sele<br>If 'a' = 1 | is<br>). If 'a'<br>ected,<br>, then |  |  |  |

| Words:                                                  |       | 1                                                                                                             |                                                                                      |                                                                        |                                                           |                                     |  |  |  |

| Cycles:                                                 |       | 1                                                                                                             |                                                                                      |                                                                        |                                                           |                                     |  |  |  |

| Q Cycle Acti                                            | vity: |                                                                                                               |                                                                                      |                                                                        |                                                           |                                     |  |  |  |

| Q1                                                      |       | Q2                                                                                                            | Q                                                                                    | 3                                                                      | Q4                                                        |                                     |  |  |  |

| Deco                                                    | de    | Read<br>register 'f'                                                                                          | Proce<br>Dat                                                                         |                                                                        | Write<br>destina                                          |                                     |  |  |  |

| Example:                                                |       | INCF                                                                                                          | CNT,                                                                                 |                                                                        |                                                           |                                     |  |  |  |

| Before II<br>CN<br>Z<br>C<br>DC<br>After Ins<br>CN<br>Z | T     | = 0xFF<br>= 0<br>= ?<br>= ?                                                                                   |                                                                                      |                                                                        |                                                           |                                     |  |  |  |

| IORL     | w                                       | Inclusive                        | OR Litera                | al with W | 1                          |  |  |  |

|----------|-----------------------------------------|----------------------------------|--------------------------|-----------|----------------------------|--|--|--|

| Synta    | ax:                                     | [ label ]                        | [ <i>label</i> ] IORLW k |           |                            |  |  |  |

| Opera    | ands:                                   | $0 \le k \le 25$                 | 5                        |           |                            |  |  |  |

| Opera    | ation:                                  | (W) .OR. I                       | $x \to W$                |           |                            |  |  |  |

| Statu    | s Affected:                             | N, Z                             |                          |           |                            |  |  |  |

| Enco     | ding:                                   | 0000                             | 1001                     | kkkk      | kkkk                       |  |  |  |

| Desc     | ription:                                | The conte<br>eight-bit lit<br>W. |                          |           | l with the<br>is placed in |  |  |  |

| Word     | s:                                      | 1                                |                          |           |                            |  |  |  |

| Cycle    | es:                                     | 1                                |                          |           |                            |  |  |  |

| QC       | ycle Activity:                          |                                  |                          |           |                            |  |  |  |

| -        | Q1                                      | Q2                               | Q                        | 3         | Q4                         |  |  |  |

|          | Decode                                  | Read<br>literal 'k'              | Proce<br>Dat             |           | Write to W                 |  |  |  |

| Example: |                                         | IORLW                            | 0x35                     |           |                            |  |  |  |

|          | Before Instruc<br>W<br>After Instructic | = 0x9A                           |                          |           |                            |  |  |  |

|          | W                                       | = 0xBF                           |                          |           |                            |  |  |  |

| IORWF                         | Inclusive O                                         | R W with f                                                                               |                         |

|-------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------|

| Syntax:                       | [label] IC                                          | RWF f[,d[                                                                                | ,a]]                    |

| Operands:                     | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ |                                                                                          |                         |

| Operation:                    | (W) .OR. (f)                                        | $\rightarrow$ dest                                                                       |                         |

| Status Affected:              | N, Z                                                |                                                                                          |                         |

| Encoding:                     | 0001                                                | 00da ff:                                                                                 | ff ffff                 |

|                               | (default). If '<br>will be selec<br>value. If 'a'   | placed back i<br>a' is '0', the A<br>sted, overridin<br>= 1, then the b<br>per the BSR y | ccess Bank<br>g the BSR |

| Words:                        | 1                                                   |                                                                                          |                         |

| Cycles:                       | 1                                                   |                                                                                          |                         |

| Q Cycle Activity:             |                                                     |                                                                                          |                         |

| Q1                            | Q2                                                  | Q3                                                                                       | Q4                      |

| Decode                        | Read<br>register 'f'                                | Process<br>Data                                                                          | Write to destination    |

| Example:                      | IORWF RE                                            | SULT, W                                                                                  |                         |

| Before Instruc<br>RESULT<br>W |                                                     |                                                                                          |                         |

0x13 0x93

After Instruction RESULT = W =

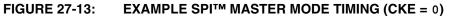

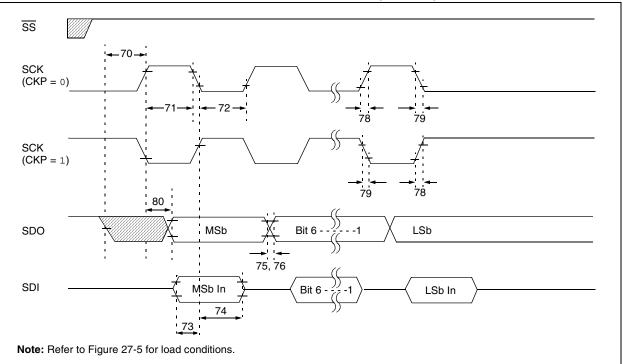

| TABLE 27-13: | EXAMPLE SPI™ MODE REQUIREMENTS (MASTER MODE, CKE = 0) |  |

|--------------|-------------------------------------------------------|--|

|              |                                                       |  |

| Param<br>No. | Symbol                | Characteristi                                                          | c           | Min           | Max | Units | Conditions |

|--------------|-----------------------|------------------------------------------------------------------------|-------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input |             | Тсү           | -   | ns    |            |

| 71           | TscH                  | SCK Input High Time                                                    | Continuous  | 1.25 Tcy + 30 | _   | ns    |            |

| 71A          |                       | (Slave mode)                                                           | Single Byte | 40            | —   | ns    | (Note 1)   |

| 72           | TscL                  | SCK Input Low Time                                                     | Continuous  | 1.25 Tcy + 30 | _   | ns    |            |

| 72A          |                       | (Slave mode)                                                           | Single Byte | 40            | —   | ns    | (Note 1)   |

| 73           | TdiV2scH,<br>TdiV2scL | Setup Time of SDI Data Input to SCK Edge                               |             | 100           | _   | ns    |            |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the 1st Clock Edge of Byte 2              |             | 1.5 TCY + 40  |     | ns    | (Note 2)   |

| 74           | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edge                                |             | 100           | _   | ns    |            |

| 75           | TdoR                  | SDO Data Output Rise Time                                              | PIC18FXX8   |               | 25  | ns    |            |

|              |                       |                                                                        | PIC18LFXX8  | —             | 45  | ns    |            |

| 76           | TdoF                  | SDO Data Output Fall Time                                              |             |               | 25  | ns    |            |

| 78           | TscR                  | SCK Output Rise Time                                                   | PIC18FXX8   | —             | 25  | ns    |            |

|              |                       | (Master mode)                                                          | PIC18LFXX8  | —             | 45  | ns    |            |

| 79           | TscF                  | SCK Output Fall Time (Master                                           | mode)       | —             | 25  | ns    |            |

| 80           | TscH2doV,             | SDO Data Output Valid after                                            | PIC18FXX8   | —             | 50  | ns    |            |

|              | TscL2doV              | SCK Edge                                                               | PIC18LFXX8  | —             | 100 | ns    | ]          |

**Note 1:** Requires the use of parameter #73A.

2: Only if parameter #71A and #72A are used.

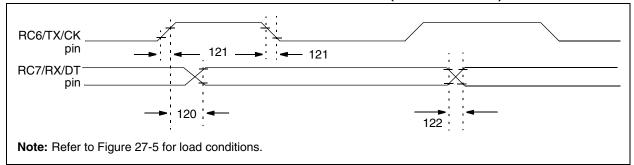

# FIGURE 27-21: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 27-21: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol        | Characteristic                    |            | Min | Мах | Units | Conditions |

|--------------|---------------|-----------------------------------|------------|-----|-----|-------|------------|

| 120          | TckH2dtV      | SYNC XMIT (Master & Slave)        |            |     |     |       |            |

|              |               | Clock High to Data-Out Valid      | PIC18FXX8  |     | 50  | ns    |            |

|              |               |                                   | PIC18LFXX8 |     | 150 | ns    |            |

| 121          | Tckrf         | Clock Out Rise Time and Fall Time | PIC18FXX8  |     | 25  | ns    |            |

|              | (Master mode) | PIC18LFXX8                        | —          | 60  | ns  |       |            |

| 122          | Tdtrf         | Data-Out Rise Time and Fall Time  | PIC18FXX8  |     | 25  | ns    |            |

|              |               |                                   | PIC18LFXX8 |     | 60  | ns    |            |

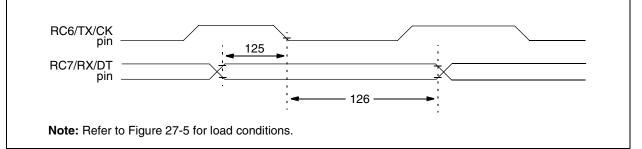

### FIGURE 27-22: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 27-22: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                                                               | Min | Max | Units | Conditions |

|--------------|----------|------------------------------------------------------------------------------|-----|-----|-------|------------|

| 125          | TdtV2ckl | SYNC RCV (Master & Slave)<br>Data-Hold before $CK \downarrow$ (DT hold time) | 10  |     | ns    |            |

| 126          | TckL2dtl | Data-Hold after CK $\downarrow$ (DT hold time)                               | 15  | —   | ns    |            |

| Transition from OSC1 to                             |

|-----------------------------------------------------|

| Timer1 Oscillator21                                 |

| USART Asynchronous Reception 192                    |

| USART Asynchronous Transmission                     |

| USART Asynchronous Transmission                     |

| (Back to Back)190                                   |

| USART Synchronous Receive                           |

| (Master/Slave)                                      |

| USART Synchronous Reception                         |

| (Master Mode, SREN)                                 |

| USART Synchronous Transmission                      |

| USART Synchronous Transmission                      |

| (Master/Slave)                                      |

| USART Synchronous Transmission                      |

|                                                     |

| (Through TXEN)                                      |

| Wake-up from Sleep via Interrupt                    |

| Timing Diagrams and Specifications                  |

| A/D Conversion Requirements                         |

| A/D Converter Characteristics                       |

| Capture/Compare/PWM Requirements                    |

| (CCP1 and ECCP1)                                    |

| CLKO and I/O Timing                                 |

| Requirements344                                     |

| Example SPI Mode Requirements                       |

| (Master Mode, CKE = 0)349                           |

| Example SPI Mode Requirements                       |

| (Master Mode, CKE = 1)                              |

| Example SPI Mode Requirements                       |

| (Slave Mode, CKE = 0)                               |

| Example SPI Slave Mode                              |

| Requirements (CKE = 1)                              |

| External Clock Timing Requirements                  |

| I <sup>2</sup> C Bus Data Requirements              |

| (Slave Mode)                                        |

| I <sup>2</sup> C Bus Start/Stop Bits Requirements   |

| (Slave Mode)353                                     |

| Master SSP I <sup>2</sup> C Bus Data                |

| Requirements                                        |

| Master SSP I <sup>2</sup> C Bus Start/Stop Bits     |

| Requirements                                        |

| Parallel Slave Port Requirements                    |

| (PIC18F248 and PIC18F458)                           |

| PLL Clock                                           |

| Reset, Watchdog Timer, Oscillator                   |

| Start-up Timer, Power-up Timer,                     |

|                                                     |

| Brown-out Reset and Low-Voltage Detect Requirements |

| •                                                   |

| Timer0 and Timer1 External                          |

| Clock Requirements                                  |

| USART Synchronous Receive                           |

| Requirements                                        |

| USART Synchronous Transmission                      |

| Requirements                                        |

| TSTFSZ                                              |

| TXSTA Register                                      |

| BRGH Bit185                                         |

|                                                     |

# U

| USART                                |

|--------------------------------------|

| Asynchronous Mode189                 |

| Reception                            |

| Setting Up 9-Bit Mode with           |

| Address Detect 191                   |

| Transmission189                      |

| Asynchronous Reception192            |

| Asynchronous Transmission            |

| Associated Registers 190             |

| Baud Rate Generator (BRG) 185        |

| Associated Registers                 |

| Baud Rate Error, Calculating 185     |

| Baud Rate Formula 185                |

| Baud Rates for Asynchronous Mode     |

| (BRGH = 0)                           |

| Baud Rates for Asynchronous Mode     |

| (BRGH = 1)                           |

| Baud Rates for Synchronous Mode 186  |

| High Baud Rate Select (BRGH Bit) 185 |

| Sampling 185                         |

| Serial Port Enable (SPEN) Bit 183    |

| Synchronous Master Mode 193          |

| Reception 195                        |

| Transmission 193                     |

| Synchronous Master Reception         |

| Associated Registers 195             |

| Synchronous Master Transmission      |

| Associated Registers 193             |

| Synchronous Slave Mode 196           |

| Reception 196                        |

| Transmission 196                     |

| Synchronous Slave Reception 197      |

| Synchronous Slave Transmission       |

| Associated Registers 197             |

| V                                    |

| Voltage Reference Specifications     |

| W                                    |

| Wake-up from Sleep                   |

| Using Interrupts                     |

| Watchdog Timer (WDT)                 |

| Associated Registers       | 273                  |

|----------------------------|----------------------|

| Control Register           |                      |

| Postscaler                 | 273                  |

| Programming Considerations | 272                  |

| RC Oscillator              |                      |

| Time-out Period            |                      |

| WCOL                       | . 171, 172, 173, 176 |

| WCOL Status Flag           | . 171, 172, 173, 176 |

| WDT. See Watchdog Timer.   |                      |

| WWW, On-Line Support       | 5                    |

| x                          |                      |

|                            |                      |

|                            | 201                  |

| XORLW | 321 |

|-------|-----|

| XORWF | 322 |