Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

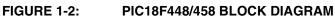

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f258-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 3-3:             |            |           | IONS FOR ALL RE                    | GISTERS (CONTINUI                                            |                                 |

|------------------------|------------|-----------|------------------------------------|--------------------------------------------------------------|---------------------------------|

| Register               | Applicable | e Devices | Power-on Reset,<br>Brown-out Reset | MCLR Reset<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |

| TRISE                  | PIC18F2X8  | PIC18F4X8 | 0000 -111                          | 0000 -111                                                    | uuuu -uuu                       |

| TRISD                  | PIC18F2X8  | PIC18F4X8 | 1111 1111                          | 1111 1111                                                    | uuuu uuuu                       |

| TRISC                  | PIC18F2X8  | PIC18F4X8 | 1111 1111                          | 1111 1111                                                    | uuuu uuuu                       |

| TRISB                  | PIC18F2X8  | PIC18F4X8 | 1111 1111                          | 1111 1111                                                    | uuuu uuuu                       |

| TRISA <sup>(5)</sup>   | PIC18F2X8  | PIC18F4X8 | -111 1111 <b>(5)</b>               | -111 1111 <sup>(5)</sup>                                     | -uuu uuuu <b>(5)</b>            |

| LATE                   | PIC18F2X8  | PIC18F4X8 | xxx                                | uuu                                                          | uuu                             |

| LATD                   | PIC18F2X8  | PIC18F4X8 | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |

| LATC                   | PIC18F2X8  | PIC18F4X8 | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |

| LATB                   | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| LATA <sup>(5)</sup>    | PIC18F2X8  | PIC18F4X8 | -xxx xxxx(5)                       | -uuu uuuu <sup>(5)</sup>                                     | -uuu uuuu <b>(5)</b>            |

| PORTE                  | PIC18F2X8  | PIC18F4X8 | xxx                                | 000                                                          | uuu                             |

| PORTD                  | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| PORTC                  | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| PORTB                  | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| PORTA <sup>(5)</sup>   | PIC18F2X8  | PIC18F4X8 | -x0x 0000 <sup>(5)</sup>           | -u0u 0000 <b>(5)</b>                                         | -uuu uuuu <b>(5)</b>            |

| TXERRCNT               | PIC18F2X8  | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |

| RXERRCNT               | PIC18F2X8  | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |

| COMSTAT                | PIC18F2X8  | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |

| CIOCON                 | PIC18F2X8  | PIC18F4X8 | 00                                 | 00                                                           | uu                              |

| BRGCON3                | PIC18F2X8  | PIC18F4X8 | -0000                              | -0000                                                        | -uuuu                           |

| BRGCON2                | PIC18F2X8  | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |

| BRGCON1                | PIC18F2X8  | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |

| CANCON                 | PIC18F2X8  | PIC18F4X8 | xxxx xxx-                          | uuuu uuu-                                                    | uuuu uuu-                       |

| CANSTAT <sup>(6)</sup> | PIC18F2X8  | PIC18F4X8 | xxx- xxx-                          | uuu- uuu-                                                    | uuu- uuu-                       |

| RXB0D7                 | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| RXB0D6                 | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| RXB0D5                 | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| RXB0D4                 | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| RXB0D3                 | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| RXB0D2                 | PIC18F2X8  | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |

| RXB0D1                 | PIC18F2X8  | PIC18F4X8 | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |

| RXB0D0                 | PIC18F2X8  | PIC18F4X8 | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |

## TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for Reset value for specific condition.

5: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

6: Values for CANSTAT also apply to its other instances (CANSTATRO1 through CANSTATRO4).

| TABLE 4-2  | : REG         | ISTER FIL     | E SUMM        | ARY (CON      | TINUED  | )       | -             |         |                      | -                   |

|------------|---------------|---------------|---------------|---------------|---------|---------|---------------|---------|----------------------|---------------------|

| File Name  | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3   | Bit 2   | Bit 1         | Bit 0   | Value on<br>POR, BOR | Details on<br>Page: |

| CANSTATRO4 | OPMODE2       | OPMODE1       | OPMODE0       | _             | ICODE2  | ICODE1  | ICODE0        | _       | xxx- xxx-            | 33, 202             |

| TXB2D7     | TXB2D77       | TXB2D76       | TXB2D75       | TXB2D74       | TXB2D73 | TXB2D72 | TXB2D71       | TXB2D70 | XXXX XXXX            | 35, 208             |

| TXB2D6     | TXB2D67       | TXB2D66       | TXB2D65       | TXB2D64       | TXB2D63 | TXB2D62 | TXB2D61       | TXB2D60 | XXXX XXXX            | 35, 208             |

| TXB2D5     | TXB2D57       | TXB2D56       | TXB2D55       | TXB2D54       | TXB2D53 | TXB2D52 | TXB2D51       | TXB2D50 | XXXX XXXX            | 35, 208             |

| TXB2D4     | TXB2D47       | TXB2D46       | TXB2D45       | TXB2D44       | TXB2D43 | TXB2D42 | TXB2D41       | TXB2D40 | xxxx xxxx            | 35, 208             |

| TXB2D3     | TXB2D37       | TXB2D36       | TXB2D35       | TXB2D34       | TXB2D33 | TXB2D32 | TXB2D31       | TXB2D30 | xxxx xxxx            | 35, 208             |

| TXB2D2     | TXB2D27       | TXB2D26       | TXB2D25       | TXB2D24       | TXB2D23 | TXB2D22 | TXB2D21       | TXB2D20 | xxxx xxxx            | 35, 208             |

| TXB2D1     | TXB2D17       | TXB2D16       | TXB2D15       | TXB2D14       | TXB2D13 | TXB2D12 | TXB2D11       | TXB2D10 | xxxx xxxx            | 35, 208             |

| TXB2D0     | TXB2D07       | TXB2D06       | TXB2D05       | TXB2D04       | TXB2D03 | TXB2D02 | TXB2D01       | TXB2D00 | xxxx xxxx            | 35, 208             |

| TXB2DLC    | _             | TXRTR         | —             | -             | DLC3    | DLC2    | DLC1          | DLC0    | -x xxxx              | 35, 209             |

| TXB2EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | xxxx xxxx            | 35, 208             |

| TXB2EIDH   | EID15         | EID14         | EID13         | EID12         | EID11   | EID10   | EID9          | EID8    | XXXX XXXX            | 35, 207             |

| TXB2SIDL   | SID2          | SID1          | SID0          | _             | EXIDE   | _       | EID17         | EID16   | xxx- x-xx            | 35, 207             |

| TXB2SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | XXXX XXXX            | 35, 207             |

| TXB2CON    | _             | TXABT         | TXLARB        | TXERR         | TXREQ   | _       | TXPRI1        | TXPRI0  | -000 0-00            | 35, 206             |

| RXM1EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | xxxx xxxx            | 35, 217             |

| RXM1EIDH   | EID15         | EID14         | EID13         | EID12         | EID11   | EID10   | EID9          | EID8    | xxxx xxxx            | 35, 217             |

| RXM1SIDL   | SID2          | SID1          | SID0          | _             | _       | _       | EID17         | EID16   | xxxxx                | 36, 217             |

| RXM1SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | xxxx xxxx            | 36, 216             |

| RXM0EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | xxxx xxxx            | 36, 217             |

| RXM0EIDH   | EID15         | EID14         | EID13         | EID12         | EID11   | EID10   | EID9          | EID8    | xxxx xxxx            | 36, 217             |

| RXM0SIDL   | SID2          | SID1          | SID0          | _             | _       | _       | EID17         | EID16   | xxxxx                | 36, 217             |

| RXM0SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | xxxx xxxx            | 36, 216             |

| RXF5EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | xxxx xxxx            | 36, 216             |

| RXF5EIDH   | EID15         | EID14         | EID13         | EID12         | EID11   | EID10   | EID9          | EID8    | xxxx xxxx            | 36, 216             |

| RXF5SIDL   | SID2          | SID1          | SID0          | _             | EXIDEN  | _       | EID17         | EID16   | xxx- x-xx            | 36, 215             |

| RXF5SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | xxxx xxxx            | 36, 215             |

| RXF4EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | xxxx xxxx            | 36, 216             |

| RXF4EIDH   | EID15         | EID14         | EID13         | EID12         | EID11   | EID10   | EID9          | EID8    | xxxx xxxx            | 36, 216             |

| RXF4SIDL   | SID2          | SID1          | SID0          | _             | EXIDEN  | _       | EID17         | EID16   | xxx- x-xx            | 36, 215             |

| RXF4SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | xxxx xxxx            | 36, 215             |

| RXF3EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | xxxx xxxx            | 36, 216             |

| RXF3EIDH   | EID15         | EID14         | EID13         | EID12         | EID11   | EID10   | EID9          | EID8    | xxxx xxxx            | 36, 216             |

| RXF3SIDL   | SID2          | SID1          | SID0          | _             | EXIDEN  | _       | EID17         | EID16   | xxx- x-xx            | 36, 215             |

| RXF3SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | xxxx xxxx            | 36, 215             |

| RXF2EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | xxxx xxxx            | 36, 216             |

| RXF2EIDH   | EID15         | EID14         | EID13         | EID12         | EID11   | EID10   | EID9          | EID8    | xxxx xxxx            | 36, 216             |

| RXF2SIDL   | SID2          | SID1          | SID0          | _             | EXIDEN  | _       | EID17         | EID16   | xxx- x-xx            | 36, 215             |

| RXF2SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | xxxx xxxx            | 36, 215             |

| RXF1EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | XXXX XXXX            | 36, 216             |

| RXF1EIDH   | EID15         | EID0<br>EID14 | EID13         | EID12         | EID0    | EID10   | EID9          | EID8    | XXXX XXXX            | 36, 216             |

| RXF1SIDL   | SID2          | SID14         | SIDO          |               | EXIDEN  |         | EID3          | EID16   | xxx- x-xx            | 36, 215             |

| RXF1SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | XXXX XXXX            | 36, 215             |

| RXF0EIDL   | EID7          | EID6          | EID5          | EID4          | EID3    | EID2    | EID1          | EID0    | XXXX XXXX            | 36, 216             |

| RXF0EIDH   | EID7<br>EID15 | EID14         | EID3<br>EID13 | EID4<br>EID12 | EID3    | EID10   | EID9          | EID8    | XXXX XXXX            | 36, 216             |

| RXF0SIDL   | SID2          | SID14         | SIDO          |               | EXIDEN  |         | EID9<br>EID17 | EID8    |                      | 36, 216             |

|            |               |               |               |               |         | SIDE    |               |         | xxx- x-xx            |                     |

| RXF0SIDH   | SID10         | SID9          | SID8          | SID7          | SID6    | SID5    | SID4          | SID3    | XXXX XXXX            | 36, 215             |

.....

Legend:  $\mathbf{x}$  = unknown,  $\mathbf{u}$  = unchanged, - = unimplemented,  $\mathbf{q}$  = value depends on condition Note

1: These registers or register bits are not implemented on the PIC18F248 and PIC18F258 and read as '0's.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator mode only and read '0' in all other oscillator modes. 3:

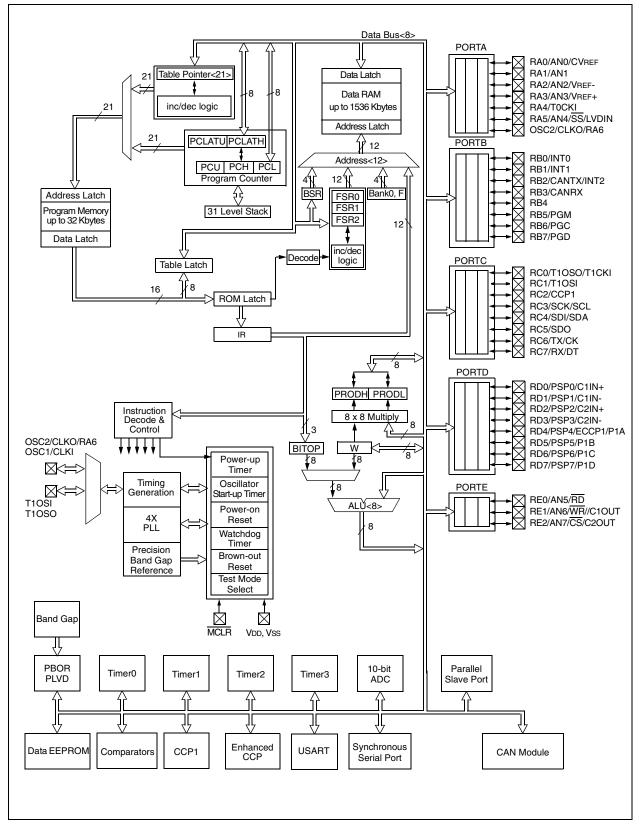

## 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

## FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

## EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW            | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE ADDR LOW |   | Load TBLPTR with the base<br>address of the word                                         |

|-----------|------------------------------------------------------|--------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------|

| READ WORD | MOVWF                                                | TBLPTRL                                                                  |   |                                                                                          |

| _         | TBLRD*-<br>MOVF<br>MOVWF<br>TBLRD*-<br>MOVF<br>MOVWF | TABLAT, W<br>WORD_LSB                                                    | ; | read into TABLAT and increment<br>get data<br>read into TABLAT and increment<br>get data |

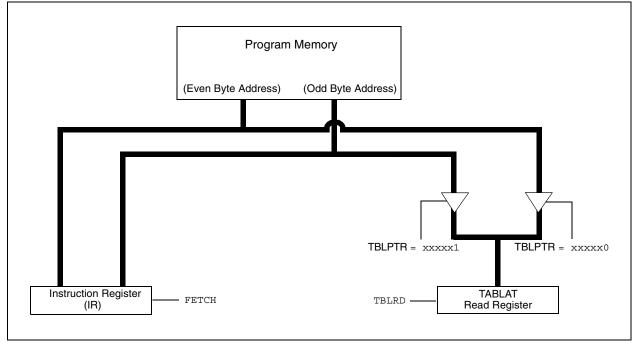

## 17.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2 < 1 >) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

## 17.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 17-20: REPEATED START CONDITION WAVEFORM

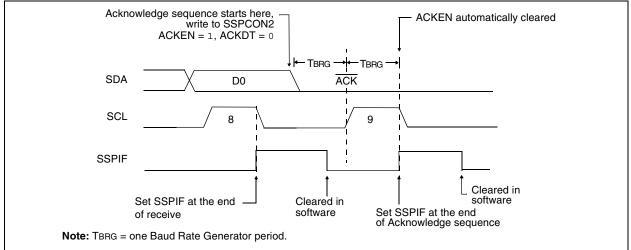

#### 17.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 17-23).

#### 17.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

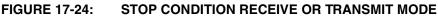

### 17.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 17-24).

## 17.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 17-23: ACKNOWLEDGE SEQUENCE WAVEFORM

## PIC18FXX8

| TER 18-2: | RCSTA: R                         | ECEIVE S                                            | TATUS AN       | ID CONTR       | OL REGIS      | TER          |                               |            |

|-----------|----------------------------------|-----------------------------------------------------|----------------|----------------|---------------|--------------|-------------------------------|------------|

|           | R/W-0                            | R/W-0                                               | R/W-0          | R/W-0          | R/W-0         | R-0          | R-0                           | R-x        |

|           | SPEN                             | RX9                                                 | SREN           | CREN           | ADDEN         | FERR         | OERR                          | RX9D       |

|           | bit 7                            |                                                     |                |                |               |              |                               | bit 0      |

| bit 7     | SPEN: Seri                       | ial Port Ena                                        | ole bit        |                |               |              |                               |            |

|           |                                  | ort enabled                                         |                | RX/DT and      | TX/CK pins    | as serial po | rt pins)                      |            |

| bit 6     | <b>RX9</b> : 9-bit F             | Receive Ena                                         | uble bit       |                |               |              |                               |            |

|           |                                  | 9-bit recept<br>8-bit recept                        |                |                |               |              |                               |            |

| bit 5     | SREN: Sing                       | gle Receive                                         | Enable bit     |                |               |              |                               |            |

|           | <u>Asynchronc</u><br>Don't care. | ous mode:                                           |                |                |               |              |                               |            |

|           | 1 = Enables                      | <u>us mode – N</u><br>s single rece<br>s single rec | eive           | is cleared a   | fter receptio | n is comple  | te)                           |            |

|           | <u>Synchronou</u><br>Unused in t | <u>us mode – S</u><br>his mode.                     | <u>lave:</u>   |                |               |              |                               |            |

| bit 4     | CREN: Cor                        | ntinuous Re                                         | ceive Enable   | e bit          |               |              |                               |            |

|           |                                  | <u>ous mode:</u><br>s continuou:<br>s continuou     |                |                |               |              |                               |            |

|           |                                  |                                                     |                | til enable bit | CREN is cle   | eared (CRE   | N overrides S                 | SREN)      |

| bit 3     | ADDEN: Ad                        | ddress Dete                                         | ct Enable bi   | t              |               |              |                               |            |

|           | Asynchrono                       | ous mode 9-                                         | bit (RX9 = 1   | <u>.):</u>     |               |              |                               |            |

|           | is set                           |                                                     |                |                | -             |              | ve buffer whe<br>n be used as |            |

| bit 2     |                                  | ning Error b                                        |                | bytes are n    |               |              |                               | parity bit |

| DIL Z     |                                  | g error (can                                        |                | by reading l   | RCREG regi    | ster and rec | eive next va                  | lid byte)  |

| bit 1     |                                  | errun Error b                                       | oit            |                |               |              |                               |            |

| bit i     |                                  | n error (can                                        | be cleared t   | by clearing b  | it CREN)      |              |                               |            |

| bit 0     |                                  | bit of Receiv                                       | ved Data       |                |               |              |                               |            |

| 2         |                                  |                                                     | it or a parity | bit.           |               |              |                               |            |

|           | Legend:                          |                                                     |                |                |               |              |                               |            |

|           | R = Reada                        | ble bit                                             | W = W          | /ritable bit   | U = Unin      | nplemented   | bit, read as                  | '0'        |

|           | 1                                |                                                     |                |                |               |              |                               |            |

'1' = Bit is set

## REGISTER 18-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

-n = Value at POR

'0' = Bit is cleared x = Bit is unknown

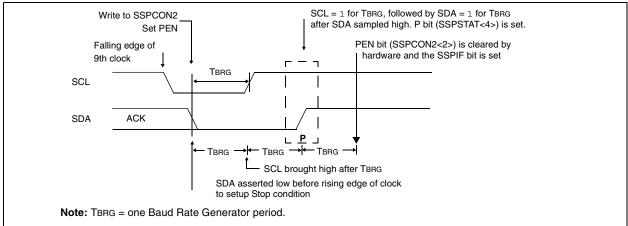

## 19.9 Programming Time Segments

Some requirements for programming of the time segments:

- Prop Seg + Phase Seg 1 ≥ Phase Seg 2

- Phase Seg 2 ≥ Sync Jump Width

For example, assume that a 125 kHz CAN baud rate is desired using 20 MHz for Fosc. With a Tosc of 50 ns, a baud rate prescaler value of 04h gives a TQ of 500 ns. To obtain a nominal bit rate of 125 kHz, the nominal bit time must be 8  $\mu$ s or 16 TQ.

Using 1 TQ for the Sync Segment, 2 TQ for the Propagation Segment and 7 TQ for Phase Segment 1 would place the sample point at 10 TQ after the transition. This leaves 6 TQ for Phase Segment 2.

By the rules above, the Sync Jump Width could be the maximum of 4 Tq. However, normally a large SJW is only necessary when the clock generation of the different nodes is inaccurate or unstable, such as using ceramic resonators. Typically, an SJW of 1 is enough.

## 19.10 Oscillator Tolerance

As a rule of thumb, the bit timing requirements allow ceramic resonators to be used in applications with transmission rates of up to 125 Kbit/sec. For the full bus speed range of the CAN protocol, a quartz oscillator is required. A maximum node-to-node oscillator variation of 1.7% is allowed.

## 19.11 Bit Timing Configuration Registers

The Configuration registers (BRGCON1, BRGCON2, BRGCON3) control the bit timing for the CAN bus interface. These registers can only be modified when the PIC18FXX8 is in Configuration mode.

## 19.11.1 BRGCON1

The BRP bits control the baud rate prescaler. The SJW < 1:0 > bits select the synchronization jump width in terms of multiples of Tq.

#### 19.11.2 BRGCON2

The PRSEG bits set the length of the Propagation Segment in terms of TQ. The SEG1PH bits set the length of Phase Segment 1 in TQ. The SAM bit controls how many times the RXCAN pin is sampled. Setting this bit to a '1' causes the bus to be sampled three times; twice at TQ/2 before the sample point and once at the normal sample point (which is at the end of Phase Segment 1). The value of the bus is determined to be the value read during at least two of the samples. If the SAM bit is set to a '0', then the RXCAN pin is sampled only once at the sample point. The SEG2PHTS bit controls how the length of Phase Segment 2 is determined. If this bit is set to a '1', then the length of Phase Segment 2 is determined by the SEG2PH bits of BRGCON3. If the SEG2PHTS bit is set to a '0', then the length of Phase Segment 2 is the greater of Phase Segment 1 and the information processing time (which is fixed at 2 TQ for the PIC18FXX8).

## 19.11.3 BRGCON3

The PHSEG2<2:0> bits set the length (in TQ) of Phase Segment 2 if the SEG2PHTS bit is set to a '1'. If the SEG2PHTS bit is set to a '0', then the PHSEG2<2:0> bits have no effect.

## 20.5 Use of the ECCP Trigger

An A/D conversion can be started by the "special event trigger" of the ECCP module. This requires that the ECCP1M3:ECCP1M0 bits (ECCP1CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/ DONE bit will be set, starting the A/D conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH/ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the "special event trigger" will be ignored by the A/D module but will still reset the Timer1 (or Timer3) counter.

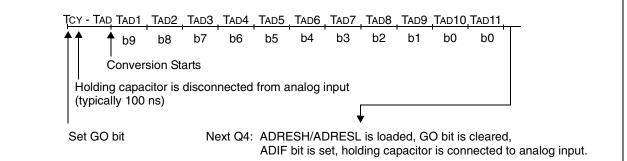

## FIGURE 20-4: A/D CONVERSION TAD CYCLES

#### TABLE 20-3: SUMMARY OF A/D REGISTERS

| Name   | Bit 7                | Bit 6               | Bit 5       | Bit 4    | Bit 3 | Bit 2   | Bit 1         | Bit 0                  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------|---------------------|-------------|----------|-------|---------|---------------|------------------------|----------------------|---------------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL           | TMR0IE      | INT0IE   | RBIE  | TMR0IF  | <b>INT0IF</b> | RBIF                   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF                | RCIF        | TXIF     | SSPIF | CCP1IF  | TMR2IF        | TMR1IF                 | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE                | RCIE        | TXIE     | SSPIE | CCP1IE  | TMR2IE        | TMR1IE                 | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP                | RCIP        | TXIP     | SSPIP | CCP1IP  | TMR2IP        | TMR1IP                 | 1111 1111            | 1111 1111                       |

| PIR2   | _                    | CMIF <sup>(1)</sup> | _           | EEIF     | BCLIF | LVDIF   | TMR3IF        | ECCP1IF <sup>(1)</sup> | -0-0 0000            | -0-0 0000                       |

| PIE2   | _                    | CMIE <sup>(1)</sup> | _           | EEIE     | BCLIE | LVDIE   | TMR3IE        | ECCP1IE <sup>(1)</sup> | -0-0 0000            | -0-0 0000                       |

| IPR2   | _                    | CMIP <sup>(1)</sup> | _           | EEIP     | BCLIP | LVDIP   | TMR3IP        | ECCP1IP <sup>(1)</sup> | -1-1 1111            | -1-1 1111                       |

| ADRESH | A/D Resul            | t Register          |             |          |       |         |               |                        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL | A/D Resul            | t Register          |             |          |       |         |               |                        | xxxx xxxx            | uuuu uuuu                       |

| ADCON0 | ADCS1                | ADCS0               | CHS2        | CHS1     | CHS0  | GO/DONE | _             | ADON                   | 0000 00-0            | 0000 00-0                       |

| ADCON1 | ADFM                 | ADCS2               | _           | _        | PCFG3 | PCFG2   | PCFG1         | PCFG0                  | 00 0000              | 00 0000                         |

| PORTA  | _                    | RA6                 | RA5         | RA4      | RA3   | RA2     | RA1           | RA0                    | -x0x 0000            | -u0u 0000                       |

| TRISA  |                      | PORTA Data          | a Direction | Register |       |         |               |                        | -111 1111            | -111 1111                       |

| PORTE  | _                    | —                   | _           | _        | _     | RE2     | RE1           | RE0                    | xxx                  | 000                             |

| LATE   | _                    | —                   | _           | _        |       | LATE2   | LATE1         | LATE0                  | xxx                  | uuu                             |

| TRISE  | IBF                  | OBF                 | IBOV        | PSPMODE  |       | TRISE2  | TRISE1        | TRISE0                 | 0000 -111            | 0000 -111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These bits are reserved on PIC18F2X8 devices; always maintain these bits clear.

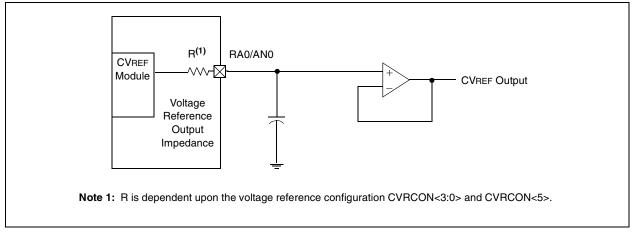

#### FIGURE 22-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 22-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value<br>all ot<br>Rese | her  |

|--------|-------|--------|--------|--------|--------|--------|--------|--------|-----------------|-------------------------|------|

| CVRCON | CVREN | CVROE  | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 0000 0000       | 0000                    | 0000 |

| CMCON  | C2OUT | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000                    | 0000 |

| TRISA  | _     | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | -111 1111       | -111 3                  | 1111 |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

# PIC18FXX8

NOTES:

#### REGISTER 24-3: CONFIG2H: CONFIGURATION REGISTER 2 HIGH (BYTE ADDRESS 300003h)

| U-0   | U-0 | U-0 | U-0 | R/P-1  | R/P-1  | R/P-1  | R/P-1 |

|-------|-----|-----|-----|--------|--------|--------|-------|

|       | —   | —   | —   | WDTPS2 | WDTPS1 | WDTPS0 | WDTEN |

| bit 7 |     |     |     |        |        |        | bit 0 |

bit 7-4 Unimplemented: Read as '0'

#### bit 3-1 WDTPS2:WDTPS0: Watchdog Timer Postscale Select bits

- 111 **= 1:128**

- 110 **= 1:64**

- 101 **= 1:32**

- 100 = 1:16

- 011 **= 1:8**

- 010 = **1**:4

- 001 = 1:2

- 000 = 1:1

- **Note:** The Watchdog Timer postscale select bits configuration used in the PIC18FXXX devices has changed from the configuration used in the PIC18CXXX devices.

#### bit 0 WDTEN: Watchdog Timer Enable bit

- 1 = WDT enabled

- 0 = WDT disabled (control is placed on the SWDTEN bit)

| Legend:              |                      |                                     |

|----------------------|----------------------|-------------------------------------|

| R = Readable bit     | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when devi | ce is unprogrammed   | u = Unchanged from programmed state |

#### REGISTER 24-4: CONFIGUL: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

-n = Value when device is unprogrammed

|         | R/P-1                                                                                                                                                                                                                    | U-0                              | U-0           | U-0          | U-0      | R/P-1      | U-0            | R/P-1  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------|--------------|----------|------------|----------------|--------|--|

|         | DEBUG                                                                                                                                                                                                                    | _                                | _             | _            | _        | LVP        | _              | STVREN |  |

|         | bit 7                                                                                                                                                                                                                    |                                  |               |              |          |            |                | bit 0  |  |

| bit 7   | <b>DEBUG:</b> Background Debugger Enable bit<br>1 = Background Debugger disabled. RB6 and RB7 configured as general purpose I/O pins.<br>0 = Background Debugger enabled. RB6 and RB7 are dedicated to In-Circuit Debug. |                                  |               |              |          |            |                |        |  |

| bit 6-3 | Unimplemented: Read as '0'                                                                                                                                                                                               |                                  |               |              |          |            |                |        |  |

| bit 2   | LVP: Low-                                                                                                                                                                                                                | LVP: Low-Voltage ICSP Enable bit |               |              |          |            |                |        |  |

|         |                                                                                                                                                                                                                          | oltage ICSP e<br>oltage ICSP o   |               |              |          |            |                |        |  |

| bit 1   | Unimplem                                                                                                                                                                                                                 | ented: Read                      | <b>as</b> '0' |              |          |            |                |        |  |

| bit 0   | STVREN:                                                                                                                                                                                                                  | Stack Full/Un                    | derflow Re    | set Enable b | oit      |            |                |        |  |

|         | <ul><li>1 = Stack Full/Underflow will cause Reset</li><li>0 = Stack Full/Underflow will not cause Reset</li></ul>                                                                                                        |                                  |               |              |          |            |                |        |  |

|         | <b></b>                                                                                                                                                                                                                  |                                  |               |              |          |            |                |        |  |

|         | Legend:                                                                                                                                                                                                                  |                                  |               |              |          |            |                |        |  |

|         | R = Reada                                                                                                                                                                                                                | ble bit                          | C = Cleara    | able bit     | U = Unin | nplemented | d bit, read as | '0'    |  |

u = Unchanged from programmed state

# PIC18FXX8

NOTES:

#### TABLE 25-2: PIC18FXXX INSTRUCTION SET (CONTINUED)

| Mnem    | onic,  | Description                     | Qualas | 16-1 | Bit Inst | ruction | Word | Status          | Natas |

|---------|--------|---------------------------------|--------|------|----------|---------|------|-----------------|-------|

| Opera   | nds    | Description                     | Cycles | MSb  |          |         | LSb  | Affected        | Notes |

| LITERAL | OPERAT | TIONS                           |        |      |          |         |      |                 |       |

| ADDLW   | k      | Add literal and WREG            | 1      | 0000 | 1111     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| ANDLW   | k      | AND literal with WREG           | 1      | 0000 | 1011     | kkkk    | kkkk | Z, N            |       |

| IORLW   | k      | Inclusive OR literal with WREG  | 1      | 0000 | 1001     | kkkk    | kkkk | Z, N            |       |

| LFSR    | f, k   | Move literal (12-bit)2nd word   | 2      | 1110 | 1110     | 00ff    | kkkk | None            |       |

|         |        | to FSRx 1st word                |        | 1111 | 0000     | kkkk    | kkkk |                 |       |

| MOVLB   | k      | Move literal to BSR<3:0>        | 1      | 0000 | 0001     | 0000    | kkkk | None            |       |

| MOVLW   | k      | Move literal to WREG            | 1      | 0000 | 1110     | kkkk    | kkkk | None            |       |

| MULLW   | k      | Multiply literal with WREG      | 1      | 0000 | 1101     | kkkk    | kkkk | None            |       |

| RETLW   | k      | Return with literal in WREG     | 2      | 0000 | 1100     | kkkk    | kkkk | None            |       |

| SUBLW   | k      | Subtract WREG from literal      | 1      | 0000 | 1000     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| XORLW   | k      | Exclusive OR literal with WREG  | 1      | 0000 | 1010     | kkkk    | kkkk | Z, N            |       |

| DATA ME | MORY ← | PROGRAM MEMORY OPERA            | TIONS  |      |          |         |      |                 |       |

| TBLRD*  |        | Table Read                      | 2      | 0000 | 0000     | 0000    | 1000 | None            |       |

| TBLRD*+ |        | Table Read with post-increment  |        | 0000 | 0000     | 0000    | 1001 | None            |       |

| TBLRD*- |        | Table Read with post-decrement  |        | 0000 | 0000     | 0000    | 1010 | None            |       |

| TBLRD+* |        | Table Read with pre-increment   |        | 0000 | 0000     | 0000    | 1011 | None            |       |

| TBLWT*  |        | Table Write                     | 2 (5)  | 0000 | 0000     | 0000    | 1100 | None            |       |

| TBLWT*+ |        | Table Write with post-increment |        | 0000 | 0000     | 0000    | 1101 | None            |       |

| TBLWT*- |        | Table Write with post-decrement |        | 0000 | 0000     | 0000    | 1110 | None            |       |

| TBLWT+* |        | Table Write with pre-increment  |        | 0000 | 0000     | 0000    | 1111 | None            |       |

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

## 26.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 26.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 26.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, timekeeping and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high-level source debugging with the MPLAB IDE.

# 26.6 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

## 26.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

## 26.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high-speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

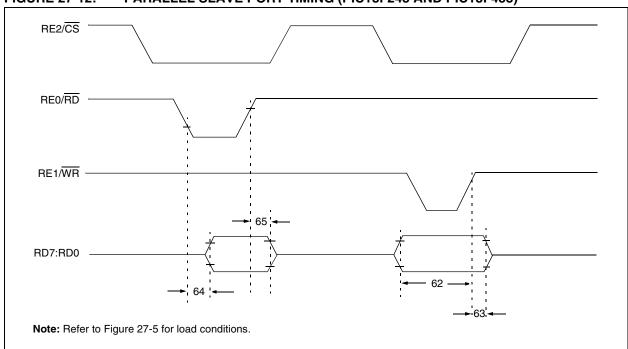

| FIGURE 27-12: | PARALLEL SLAVE PORT | TIMING (PIC18F248 AND PIC18F458) |

|---------------|---------------------|----------------------------------|

|               | FANALLL SLAVE FUNI  |                                  |

| TABLE 27-12: PARALLEL SLAVE PORT REQUIREMENTS (PIC18F248 AND PIC18F458) |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

| Param<br>No. | Symbol   | Characteristic                                                                                                                          |                     |    | Max      | Units    | Conditions           |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|----|----------|----------|----------------------|

| 62           | TdtV2wrH | Data-In Valid before $\overline{WR} \uparrow$ or $\overline{CS} \uparrow$ (setup time)                                                  |                     |    |          | ns<br>ns | Extended Temp. range |

| 63           | TwrH2dtl | $\overline{\text{WR}} \uparrow \text{ or } \overline{\text{CS}} \uparrow \text{ to Data-In Invalid} $ P (hold time)                     | PIC18FXX8           | 20 | _        | ns       |                      |

|              |          |                                                                                                                                         | PIC18 <b>LF</b> XX8 | 35 | _        | ns       |                      |

| 64           | TrdL2dtV | $\overline{\mathrm{RD}}\downarrow\mathrm{and}\overline{\mathrm{CS}}\downarrow\mathrm{to}\mathrm{Data}	ext{-}\mathrm{Out}\mathrm{Valid}$ |                     |    | 80<br>90 | ns<br>ns | Extended Temp. range |

| 65           | TrdH2dtl | $\overline{RD}$ $\uparrow$ or $\overline{CS}$ $\downarrow$ to Data-Out Invali                                                           | 10                  | 30 | ns       |          |                      |

| 66           | TibfINH  | Inhibit the IBF flag bit being cleared from $\overline{\rm WR}\uparrow$ or $\overline{\rm CS}\uparrow$                                  |                     | _  | 3 TCY    | ns       |                      |

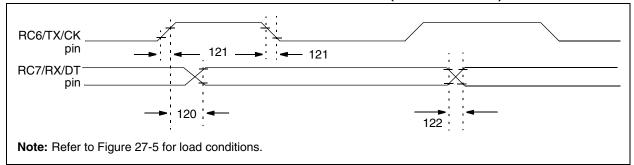

## FIGURE 27-21: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 27-21: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                    | Characteristic |   |     | Units | Conditions |

|--------------|----------|-----------------------------------|----------------|---|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (Master & Slave)        |                |   |     |       |            |

|              |          | Clock High to Data-Out Valid      | PIC18FXX8      |   | 50  | ns    |            |

|              |          |                                   | PIC18LFXX8     |   | 150 | ns    |            |

| 121          | Tckrf    | Clock Out Rise Time and Fall Time | PIC18FXX8      |   | 25  | ns    |            |

|              |          | (Master mode)                     | PIC18LFXX8     | — | 60  | ns    |            |

| 122          | Tdtrf    | Data-Out Rise Time and Fall Time  | PIC18FXX8      |   | 25  | ns    |            |

|              |          |                                   | PIC18LFXX8     |   | 60  | ns    |            |

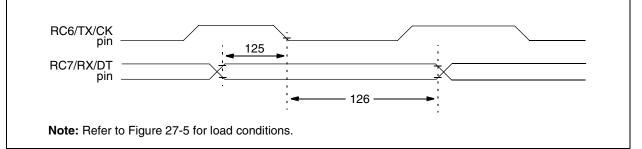

#### FIGURE 27-22: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 27-22: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                                                               | Min | Max | Units | Conditions |

|--------------|----------|------------------------------------------------------------------------------|-----|-----|-------|------------|

| 125          | TdtV2ckl | SYNC RCV (Master & Slave)<br>Data-Hold before $CK \downarrow$ (DT hold time) | 10  |     | ns    |            |

| 126          | TckL2dtl | Data-Hold after CK $\downarrow$ (DT hold time)                               | 15  | —   | ns    |            |

| Param<br>No. | Symbol                           | Characteristic Min                                |                 | Min                               | Тур | Max         | Units                                                                                                                         | Conditions                                    |

|--------------|----------------------------------|---------------------------------------------------|-----------------|-----------------------------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| A01          | NR                               | Resolution                                        |                 | _                                 | _   | 10          | bit                                                                                                                           | $VREF = VDD \ge 3.0V$                         |

| A03          | EIL                              | Integral Linearity Error                          |                 | _                                 | _   | <±1         | LSb                                                                                                                           | $VREF=VDD \geq 3.0V$                          |

| A04          | Edl                              | Differential Linearity Error                      |                 | _                                 | _   | <±1         | LSb                                                                                                                           | $VREF = VDD \ge 3.0V$                         |

| A05          | Efs                              | Full Scale Error                                  |                 | _                                 | _   | <±1         | LSb                                                                                                                           | $VREF = VDD \ge 3.0V$                         |

| A06          | EOFF                             | Offset Error                                      |                 | _                                 | _   | <±1.5       | LSb                                                                                                                           | $VREF = VDD \ge 3.0V$                         |

| A10          | _                                | Monotonicity <sup>(3)</sup>                       |                 | guaranteed                        |     | —           | $VSS \le VAIN \le VREF$                                                                                                       |                                               |

| A20          | VREF                             | Reference Voltage                                 |                 | 0V                                |     | _           | V                                                                                                                             |                                               |

| A20A         |                                  | (VREFH – VREFL)                                   |                 | 3V                                | _   | —           | V                                                                                                                             | For 10-bit resolution                         |

| A21          | VREFH                            | Reference Voltage High                            |                 | Vss                               |     | VDD + 0.3V  | V                                                                                                                             |                                               |

| A22          | VREFL                            | Reference Voltage Low                             |                 | Vss - 0.3V                        | _   | Vdd         | V                                                                                                                             |                                               |

| A25          | VAIN                             | Analog Input Voltage                              |                 | Vss - 0.3V                        | _   | VREF + 0.3V | V                                                                                                                             |                                               |

| A30          | ZAIN                             | Recommended Impedance of<br>Analog Voltage Source |                 | —                                 | _   | 10.0        | kΩ                                                                                                                            |                                               |

| A40          | IAD                              | A/D Conversion                                    | PIC18FXX8       | _                                 | 180 | —           | μA                                                                                                                            | Average current                               |

|              |                                  | Current (VDD)                                     | D) PIC18LFXX8 — | nt (VDD) PIC18 <b>LF</b> XX8 — 90 | 90  | —           | μA                                                                                                                            | consumption when<br>A/D is on <b>(Note 1)</b> |

| A50          | IREF VREF Input Current (Note 2) |                                                   | 0               | _                                 | 5   | μΑ<br>μΑ    | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN. To<br>charge CHOLD.<br>During A/D conversion<br>cycle. |                                               |

# TABLE 27-23: A/D CONVERTER CHARACTERISTICS: PIC18FXX8 (INDUSTRIAL, EXTENDED) PIC18LFXX8 (INDUSTRIAL)

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current specification includes any such leakage from the A/D module. VREF current is from RA2/AN2/VREF- and RA3/AN3/VREF+ pins or VDD and VSS pins, whichever is selected as reference input.

**2:** VSS  $\leq$  VAIN  $\leq$  VREF

**3:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

## 29.1 Package Marking Information (Continued)

44-Lead PLCC

44-Lead TQFP

Example

Example

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com