Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f258t-i-sog |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.7 Effects of Sleep Mode on the On-Chip Oscillator

When the device executes a SLEEP instruction, the on-chip clocks and oscillator are turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor switching currents have been removed, Sleep mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The user can wake from Sleep through external Reset, Watchdog Timer Reset or through an interrupt.

# 2.8 Power-up Delays

Power-up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply and clock are stable. For additional information on Reset operation, see **Section 3.0 "Reset"**.

The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of TPWRT (parameter #D033) on power-up only (POR and BOR). The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable.

With the PLL enabled (HS4 Oscillator mode), the timeout sequence following a Power-on Reset is different from other oscillator modes. The time-out sequence is as follows: the PWRT time-out is invoked after a POR time delay has expired, then the Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies. The PWRT timer is used to provide an additional fixed 2 ms (nominal) to allow the PLL ample time to lock to the incoming clock frequency.

TABLE 2-3: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode      | OSC1 Pin                                              | OSC2 Pin                                              |

|---------------|-------------------------------------------------------|-------------------------------------------------------|

| RC            | Floating, external resistor should pull high          | At logic low                                          |

| RCIO          | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |

| ECIO          | Floating                                              | Configured as PORTA, bit 6                            |

| EC            | Floating                                              | At logic low                                          |

| LP, XT and HS | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

Note: See Table 3-1 in Section 3.0 "Reset" for time-outs due to Sleep and MCLR Reset.

### 8.3 PIE Registers

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

The Peripheral Interrupt Enable (PIE) registers contain the individual enable bits for the peripheral interrupts (Register 8-7 through Register 8-9). Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2, PIE3). When IPEN is clear, the PEIE bit must be set to enable any of these peripheral interrupts.

| REGISTER 8-7: | PIE1. PERIPHERAL | INTERRUPT ENABLE REGISTER 1 |

|---------------|------------------|-----------------------------|

|               | FIEL. FENIFIENAL |                             |

|   | R/W-0                          | R/W-0                       | R/W-0         | R/W-0                       | R/W-0         | R/W-0        | R/W-0      | R/W-0         |  |  |  |  |

|---|--------------------------------|-----------------------------|---------------|-----------------------------|---------------|--------------|------------|---------------|--|--|--|--|

|   | PSPIE <sup>(1)</sup>           | ADIE                        | RCIE          | TXIE                        | SSPIE         | CCP1IE       | TMR2IE     | TMR1IE        |  |  |  |  |

|   | bit 7                          |                             |               |                             |               |              |            | bit 0         |  |  |  |  |

|   |                                |                             |               |                             |               |              |            |               |  |  |  |  |

|   |                                |                             |               | -                           | ot Enable bit | (1)          |            |               |  |  |  |  |

|   |                                | s the PSP re<br>s the PSP r |               |                             |               |              |            |               |  |  |  |  |

|   | ADIE: A/D                      | Converter Ir                | nterrupt Ena  | ble bit                     |               |              |            |               |  |  |  |  |

|   | 1 = Enables the A/D interrupt  |                             |               |                             |               |              |            |               |  |  |  |  |

|   | 0 = Disables the A/D interrupt |                             |               |                             |               |              |            |               |  |  |  |  |

|   |                                | RT Receive                  | -             |                             |               |              |            |               |  |  |  |  |

|   |                                | s the USAR<br>s the USAR    |               | •                           |               |              |            |               |  |  |  |  |

|   | TXIE: USA                      | RT Transmi                  | t Interrupt E | nable bit                   |               |              |            |               |  |  |  |  |

|   |                                | s the USAR                  |               |                             |               |              |            |               |  |  |  |  |

|   | 0 = Disable                    | es the USAR                 | T transmit i  | nterrupt                    |               |              |            |               |  |  |  |  |

|   |                                | -                           |               | l Port Interru              | pt Enable b   | it           |            |               |  |  |  |  |

|   |                                | s the MSSP<br>es the MSSF   | •             |                             |               |              |            |               |  |  |  |  |

|   |                                | CP1 Interru                 | •             | t                           |               |              |            |               |  |  |  |  |

|   |                                | s the CCP1                  |               |                             |               |              |            |               |  |  |  |  |

|   | 0 = Disable                    | es the CCP1                 | interrupt     |                             |               |              |            |               |  |  |  |  |

|   |                                | MR2 to PR2                  |               | •                           | bit           |              |            |               |  |  |  |  |

|   |                                | s the TMR2<br>s the TMR2    |               |                             |               |              |            |               |  |  |  |  |

| ) | TMR1IE: T                      | MR1 Overflo                 | ow Interrupt  | Enable bit                  |               |              |            |               |  |  |  |  |

|   |                                | s the TMR1                  |               |                             |               |              |            |               |  |  |  |  |

|   | 0 = Disable                    | es the TMR1                 | overflow in   | terrupt                     |               |              |            |               |  |  |  |  |

|   | Note 1:                        |                             | •             | e on PIC18<br>reads as '0'. | F4X8 device   | es. For PIC1 | 8F2X8 devi | ces, this bit |  |  |  |  |

|   |                                |                             |               |                             |               |              |            |               |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| <b>REGISTER 8-8:</b> | REGISTER 8-8: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 |                              |                 |                      |       |       |        |                        |  |  |  |

|----------------------|------------------------------------------------------------|------------------------------|-----------------|----------------------|-------|-------|--------|------------------------|--|--|--|

|                      | U-0                                                        | R/W-0                        | U-0             | R/W-0                | R/W-0 | R/W-0 | R/W-0  | R/W-0                  |  |  |  |

|                      | —                                                          | CMIE <sup>(1)</sup>          | _               | EEIE                 | BCLIE | LVDIE | TMR3IE | ECCP1IE <sup>(1)</sup> |  |  |  |

|                      | bit 7                                                      |                              |                 |                      |       |       |        | bit 0                  |  |  |  |

|                      |                                                            |                              |                 |                      |       |       |        |                        |  |  |  |

| bit 7                | •                                                          | ented: Rea                   |                 | (1)                  |       |       |        |                        |  |  |  |

| bit 6                |                                                            | nparator Inte                | •               |                      |       |       |        |                        |  |  |  |

|                      |                                                            | es the compa<br>es the compa |                 | -                    |       |       |        |                        |  |  |  |

| bit 5                | Unimplem                                                   | ented: Rea                   | <b>d as</b> '0' |                      |       |       |        |                        |  |  |  |

| bit 4                | EEIE: EEP                                                  | ROM Write                    | Interrupt Er    | able bit             |       |       |        |                        |  |  |  |

|                      | 1 = Enable<br>0 = Disable                                  |                              |                 |                      |       |       |        |                        |  |  |  |

| bit 3                | BCLIE: Bu                                                  | s Collision I                | nterrupt Ena    | able bit             |       |       |        |                        |  |  |  |

|                      | 1 = Enable<br>0 = Disable                                  |                              |                 |                      |       |       |        |                        |  |  |  |

| bit 2                | LVDIE: LO                                                  | w-Voltage D                  | etect Interru   | ipt Enable b         | it    |       |        |                        |  |  |  |

|                      | 1 = Enable                                                 | d                            |                 | -                    |       |       |        |                        |  |  |  |

|                      | 0 = Disable                                                | ed                           |                 |                      |       |       |        |                        |  |  |  |

| bit 1                | TMR3IE: T                                                  | MR3 Overfle                  | ow Interrupt    | Enable bit           |       |       |        |                        |  |  |  |

|                      | 1 = Enable                                                 | s the TMR3                   | overflow in     | terrupt              |       |       |        |                        |  |  |  |

|                      | 0 = Disable                                                | es the TMR3                  | overflow ir     | iterrupt             |       |       |        |                        |  |  |  |

| bit 0                | ECCP1IE:                                                   | ECCP1 Inte                   | rrupt Enabl     | e bit <sup>(1)</sup> |       |       |        |                        |  |  |  |

|                      | 1 = Enable                                                 | s the ECCP                   | 1 interrupt     |                      |       |       |        |                        |  |  |  |

|                      | 0 = Disable                                                | es the ECCF                  | 1 interrupt     |                      |       |       |        |                        |  |  |  |

|                      |                                                            |                              |                 |                      |       |       |        |                        |  |  |  |

# Note 1: This bit is only available on PIC18F4X8 devices. For PIC18F2X8 devices, this bit is unimplemented and reads as '0'.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| ER 8-12: | IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3   |                                                  |                |                 |           |            |                |        |  |  |  |  |

|----------|--------------------------------------------------|--------------------------------------------------|----------------|-----------------|-----------|------------|----------------|--------|--|--|--|--|

|          | R/W-1                                            | R/W-1                                            | R/W-1          | R/W-1           | R/W-1     | R/W-1      | R/W-1          | R/W-1  |  |  |  |  |

|          | IRXIP                                            | WAKIP                                            | ERRIP          | TXB2IP          | TXB1IP    | TXB0IP     | RXB1IP         | RXB0IP |  |  |  |  |

|          | bit 7                                            |                                                  |                |                 |           |            |                | bit 0  |  |  |  |  |

|          |                                                  |                                                  |                |                 |           |            |                |        |  |  |  |  |

| bit 7    |                                                  | •                                                | e Received     | Interrupt Pric  | ority bit |            |                |        |  |  |  |  |

|          | 1 = High pr<br>0 = Low pri                       | ,                                                |                |                 |           |            |                |        |  |  |  |  |

| bit 6    | WAKIP: Bu                                        | is Activity W                                    | lake-up Inte   | rrupt Priority  | bit       |            |                |        |  |  |  |  |

|          |                                                  | 1 = High priority<br>0 = Low priority            |                |                 |           |            |                |        |  |  |  |  |

| bit 5    | ERRIP: CA                                        | N bus Erro                                       | r Interrupt Pi | riority bit     |           |            |                |        |  |  |  |  |

|          | 1 = High pr<br>0 = Low pri                       |                                                  |                |                 |           |            |                |        |  |  |  |  |

| bit 4    | TXB2IP: Tr                                       | ansmit Buff                                      | er 2 Interrup  | ot Priority bit |           |            |                |        |  |  |  |  |

|          | 1 = High pr<br>0 = Low pri                       | ,                                                |                |                 |           |            |                |        |  |  |  |  |

| bit 3    | TXB1IP: Tr                                       | TXB1IP: Transmit Buffer 1 Interrupt Priority bit |                |                 |           |            |                |        |  |  |  |  |

|          | 1 = High pr<br>0 = Low pri                       | ,                                                |                |                 |           |            |                |        |  |  |  |  |

| bit 2    | TXB0IP: Transmit Buffer 0 Interrupt Priority bit |                                                  |                |                 |           |            |                |        |  |  |  |  |

|          | 1 = High pr<br>0 = Low pri                       | •                                                |                |                 |           |            |                |        |  |  |  |  |

| bit 1    | <b>RXB1IP:</b> R                                 | eceive Buff                                      | er 1 Interrup  | t Priority bit  |           |            |                |        |  |  |  |  |

|          | 1 = High pr<br>0 = Low pri                       | ,                                                |                |                 |           |            |                |        |  |  |  |  |

| bit 0    | RXB0IP: Receive Buffer 0 Interrupt Priority bit  |                                                  |                |                 |           |            |                |        |  |  |  |  |

|          | 1 = High pr<br>0 = Low pri                       |                                                  |                |                 |           |            |                |        |  |  |  |  |

|          | Legend:                                          |                                                  |                |                 |           |            |                | ]      |  |  |  |  |

|          | R = Reada                                        | ble bit                                          | W = W          | /ritable bit    | U = Unim  | nplemented | bit, read as ' | 0'     |  |  |  |  |

# REGISTER 8-12: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

| Legena:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 10.0 PARALLEL SLAVE PORT

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | PIC18F4X8 devices.                           |

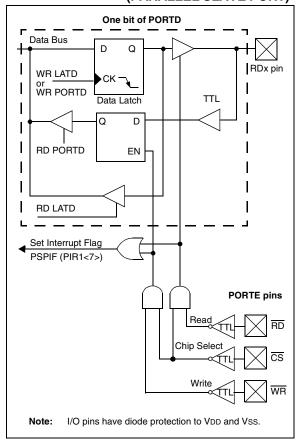

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 9-1). Setting control bit PSPMODE (TRISE<4>) enables PSP operation. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit PSPMODE enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set).

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The timing for the control signals in Write and Read modes is shown in Figure 10-2 and Figure 10-3, respectively.

FIGURE 10-1:

### PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

#

### FIGURE 10-2: PARALLEL SLAVE PORT WRITE WAVEFORMS

| Name   | Bit 7                   | Bit 6        | Bit 5  | Bit 4         | Bit 3 | Bit 2  | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------|--------------|--------|---------------|-------|--------|---------------|--------|----------------------|---------------------------------|

| INTCON | GIE/GIEH                | PEIE/GIEL    | TMR0IE | <b>INTOIE</b> | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>    | ADIF         | RCIF   | TXIF          | SSPIF | CCP1IF | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>    | ADIE         | RCIE   | TXIE          | SSPIE | CCP1IE | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>    | ADIP         | RCIP   | TXIP          | SSPIP | CCP1IP | TMR2IP        | TMR1IP | 1111 1111            | 1111 1111                       |

| RCSTA  | SPEN                    | RX9          | SREN   | CREN          | ADDEN | FERR   | OERR          | RX9D   | 0000 000x            | 0000 000u                       |

| TXREG  | USART Transmit Register |              |        |               |       |        |               |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                    | TX9          | TXEN   | SYNC          |       | BRGH   | TRMT          | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate (             | Generator Re | gister |               |       |        |               |        | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: These registers or register bits are not implemented on the PIC18F248 and PIC18F258 and read as '0's.

TABLE 18-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Name   | Bit 7                | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------|---------------|--------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL     | TMR0IE | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF          | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE          | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP          | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 1111 1111            | 1111 1111                       |

| RCSTA  | SPEN                 | RX9           | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000u                       |

| RCREG  | USART Red            | ceive Registe | r      |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                 | TX9           | TXEN   | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate            | Generator Re  | gister |        |       |        |        |        | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: These registers or register bits are not implemented on the PIC18F248 and PIC18F258 and read as '0's.

### 19.5 Message Reception

### 19.5.1 RECEIVE MESSAGE BUFFERING

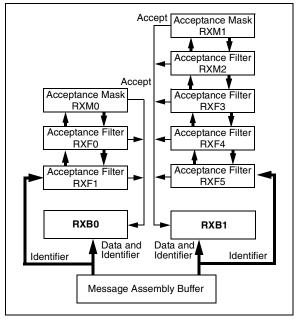

The PIC18FXX8 includes two full receive buffers with multiple acceptance filters for each. There is also a separate Message Assembly Buffer (MAB) which acts as a third receive buffer (see Figure 19-4).

### 19.5.2 RECEIVE BUFFERS

Of the three receive buffers, the MAB is always committed to receiving the next message from the bus. The remaining two receive buffers are called RXB0 and RXB1 and can receive a complete message from the protocol engine. The MCU can access one buffer while the other buffer is available for message reception or holding a previously received message.

The MAB assembles all messages received. These messages will be transferred to the RXBn buffers only if the acceptance filter criteria are met.

Note: The entire contents of the MAB are moved into the receive buffer once a message is accepted. This means that regardless of the type of identifier (standard or extended) and the number of data bytes received, the entire receive buffer is overwritten with the MAB contents. Therefore, the contents of all registers in the buffer must be assumed to have been modified when any message is received.

When a message is moved into either of the receive buffers, the appropriate RXBnIF bit is set. This bit must be cleared by the MCU when it has completed processing the message in the buffer in order to allow a new message to be received into the buffer. This bit provides a positive lockout to ensure that the MCU has finished with the message before the PIC18FXX8 attempts to load a new message into the receive buffer. If the RXBnIE bit is set, an interrupt will be generated to indicate that a valid message has been received.

### 19.5.3 RECEIVE PRIORITY

RXB0 is the higher priority buffer and has two message acceptance filters associated with it. RXB1 is the lower priority buffer and has four acceptance filters associated with it. The lower number of acceptance filters makes the match on RXB0 more restrictive and implies a higher priority for that buffer. Additionally, the RXB0CON register can be configured such if RXB0 contains a valid message and another valid message is received, an overflow error will not occur and the new message will be moved into RXB1 regardless of the acceptance criteria of RXB1. There are also two programmable acceptance filter masks available, one for each receive buffer (see Section 19.6 "Message Acceptance Filters and Masks").

When a message is received, bits <3:0> of the RXBnCON register will indicate the acceptance filter number that enabled reception and whether the received message is a remote transfer request.

The RXM bits set special Receive modes. Normally, these bits are set to '00' to enable reception of all valid messages as determined by the appropriate acceptance filters. In this case, the determination of whether or not to receive standard or extended messages is determined by the EXIDE bit in the Acceptance Filter register. If the RXM bits are set to '01' or '10', the receiver will accept only messages with standard or extended identifiers, respectively. If an acceptance filter has the EXIDE bit set, such that it does not correspond with the RXM mode, that acceptance filter is rendered useless. These two modes of RXM bits can be used in systems where it is known that only standard or extended messages will be on the bus. If the RXM bits are set to '11', the buffer will receive all messages regardless of the values of the acceptance filters. Also, if a message has an error before the end of frame, that portion of the message assembled in the MAB before the error frame will be loaded into the buffer. This mode has some value in debugging a CAN system and would not be used in an actual system environment.

### 19.5.4 TIME-STAMPING

The CAN module can be programmed to generate a time-stamp for every message that is received. When enabled, the module generates a capture signal for CCP1 which in turns captures the value of either Timer1 or Timer3. This value can be used as the message time-stamp.

To use the time-stamp capability, the CANCAP bit (CIOCAN<4>) must be set. This replaces the capture input for CCP1 with the signal generated from the CAN module. In addition, CCP1CON<3:0> must be set to '0011' to enable the CCP special event trigger for CAN events.

#### RECEIVE BUFFER BLOCK DIAGRAM

### 23.2.1 REFERENCE VOLTAGE SET POINT

The internal reference voltage of the LVD module may be used by other internal circuitry (the Programmable Brown-out Reset). If these circuits are disabled (lower current consumption), the reference voltage circuit requires a time to become stable before a low-voltage condition can be reliably detected. This time is invariant of system clock speed. This start-up time is specified in electrical specification parameter #36. The low-voltage interrupt flag will not be enabled until a stable reference voltage is reached. Refer to the waveform in Figure 23-4.

### 23.2.2 CURRENT CONSUMPTION

When the module is enabled, the LVD comparator and voltage divider are enabled and will consume static current. The voltage divider can be tapped from multiple places in the resistor array. Total current consumption, when enabled, is specified in electrical specification parameter #D022B.

### 23.3 Operation During Sleep

When enabled, the LVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

### 23.4 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the LVD module to be turned off.

| RLNCF             | Rotate Left                                           | f (no ca                                                          | arry)                                                         |                                                  |

|-------------------|-------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------|

| Syntax:           | [ label ]                                             | RLNCF                                                             | f [,d [,                                                      | .a]]                                             |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$   |                                                                   |                                                               |                                                  |

| Operation:        | $(f{<}n{>})  ightarrow de$ $(f{<}7{>})  ightarrow de$ |                                                                   | >,                                                            |                                                  |

| Status Affected:  | N, Z                                                  |                                                                   |                                                               |                                                  |

| Encoding:         | 0100                                                  | 01da                                                              | ffff                                                          | ffff                                             |

|                   | placed in W<br>stored back                            | /. If 'd' is<br>t in regisi<br>ccess Ba<br>he BSR '<br>nk will be | '1', the<br>ter 'f' (d<br>ank will ∣<br>value. If<br>e select | efault). If 'a'<br>be selected,<br>f 'a' is '1', |

|                   | _                                                     | regi                                                              | ister f                                                       |                                                  |

| Words:            | 1                                                     |                                                                   |                                                               |                                                  |

| Cycles:           | 1                                                     |                                                                   |                                                               |                                                  |

| Q Cycle Activity: |                                                       |                                                                   |                                                               |                                                  |

| Q1                | Q2                                                    | Q3                                                                | }                                                             | Q4                                               |

|                   |                                                       |                                                                   |                                                               |                                                  |

| Decode            | Read                                                  | Proce                                                             | SS                                                            | Write to                                         |

| Decode            | Read<br>register 'f'                                  | Proce<br>Data                                                     |                                                               | Write to destination                             |

| Example:          | register 'f'                                          |                                                                   |                                                               |                                                  |

|                   | register 'f'<br>RLNCF                                 | Data                                                              |                                                               |                                                  |

| RRCF                                                                              | Rotate Rig                                                                          | ht f throu                            | igh Carry                                 | /                   |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------|---------------------|

| Syntax:                                                                           | [label] R                                                                           | RCF f[                                | ,d [,a]]                                  |                     |

| Operands:                                                                         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                 |                                       |                                           |                     |

| Operation:                                                                        | $(f < n >) \rightarrow de$<br>$(f < 0 >) \rightarrow C$<br>$(C) \rightarrow dest$   | ,                                     | >,                                        |                     |

| Status Affected:                                                                  | C, N, Z                                                                             |                                       |                                           |                     |

| Encoding:                                                                         | 0011                                                                                | 00da                                  | ffff                                      | ffff                |

|                                                                                   | If 'd' is '1', t<br>register 'f' (<br>Access Bar<br>overriding t<br>then the ba     | default). I<br>nk will be<br>he BSR v | f 'a' is 'o',<br>selected,<br>alue. If 'a | , the<br>.' is '1', |

|                                                                                   | the BSR va                                                                          | ,<br>                                 | ,                                         | 7                   |

|                                                                                   |                                                                                     | ,<br>                                 | ult).<br>ster f                           | ]                   |

| Words:                                                                            |                                                                                     | ,<br>                                 | ,                                         | ]-•                 |

| Words:<br>Cycles:                                                                 |                                                                                     | ,<br>                                 | ,                                         | ]                   |

|                                                                                   |                                                                                     | ,<br>                                 | ,                                         | ]                   |

| Cycles:                                                                           |                                                                                     | ,<br>                                 | ,                                         | <br>                |

| Cycles:<br>Q Cycle Activity:                                                      | C<br>1<br>1<br>Q2<br>Read                                                           | ► regi<br>Q3<br>Proces                | ster f                                    | Q4<br>Vrite to      |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                | 1<br>1<br>Q2                                                                        | - regi                                | ster f                                    | <br>Q4              |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                | C<br>1<br>1<br>Q2<br>Read<br>register 'f'                                           | ► regi<br>Q3<br>Proces                | ster f                                    | Q4<br>Vrite to      |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                                      | C<br>1<br>1<br>Q2<br>Read<br>register 'f'                                           | Q3<br>Proces<br>Data                  | ster f                                    | Q4<br>Vrite to      |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruc<br>REG | C<br>1<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>RRCF F                            | Q3<br>Proces<br>Data                  | ster f                                    | Q4<br>Vrite to      |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct       | C<br>1<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>RRCF H<br>tion<br>= 1110 (<br>= 0 | Q3<br>Proces<br>Data                  | ster f                                    | Q4<br>Vrite to      |

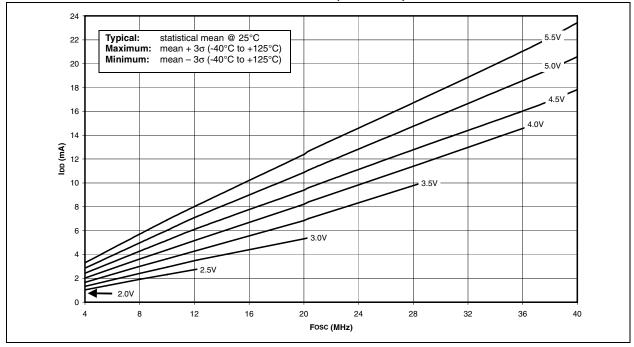

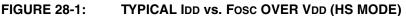

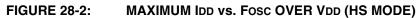

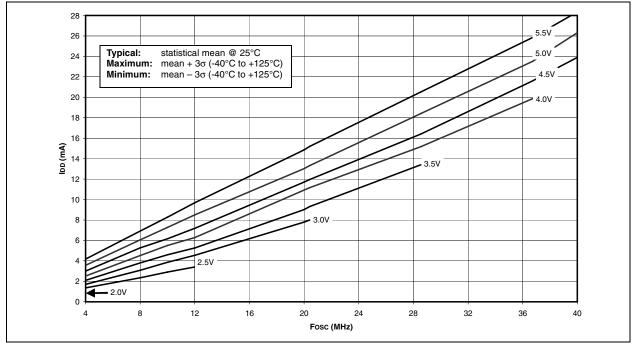

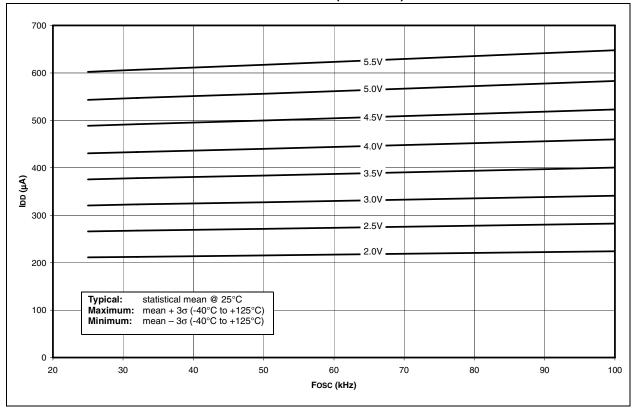

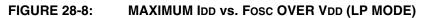

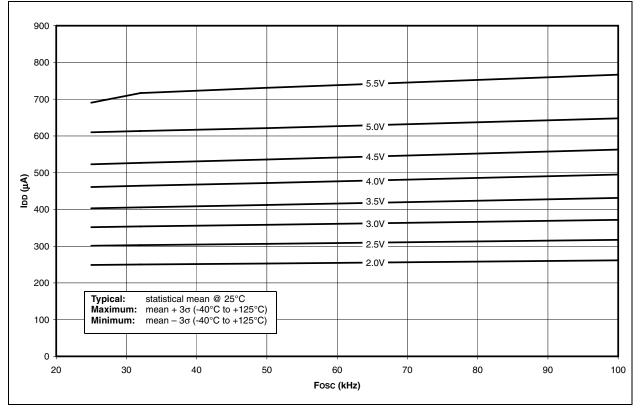

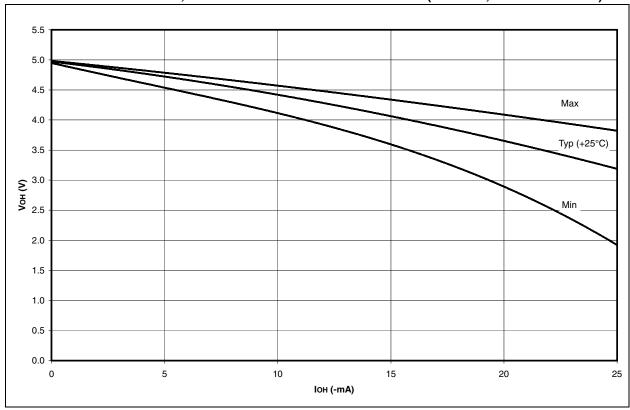

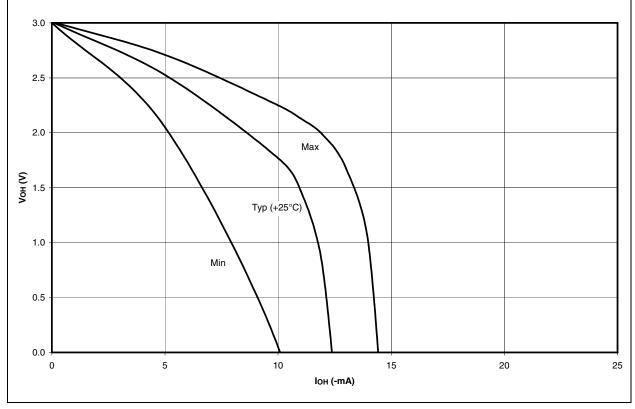

# 28.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

### FIGURE 28-7: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

FIGURE 28-21: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO +125°C)

© 2006 Microchip Technology Inc.

# 29.0 PACKAGING INFORMATION

# 29.1 Package Marking Information

#### 28-Lead SPDIP

28-Lead SOIC

### 40-Lead PDIP

Example

### Example

### Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |

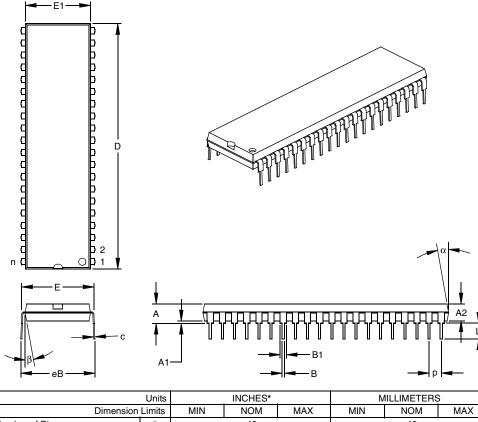

# 40-Lead Plastic Dual In-line (P) – 600 mil Body (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Dimensior                  | Limits | MIN   | NOM   | MAX   | MIN   | NOM   | MAX   |

|----------------------------|--------|-------|-------|-------|-------|-------|-------|

| Number of Pins             | n      |       | 40    |       |       | 40    |       |

| Pitch                      | р      |       | .100  |       |       | 2.54  |       |

| Top to Seating Plane       | А      | .160  | .175  | .190  | 4.06  | 4.45  | 4.83  |

| Molded Package Thickness   | A2     | .140  | .150  | .160  | 3.56  | 3.81  | 4.06  |

| Base to Seating Plane      | A1     | .015  |       |       | 0.38  |       |       |

| Shoulder to Shoulder Width | Е      | .595  | .600  | .625  | 15.11 | 15.24 | 15.88 |

| Molded Package Width       | E1     | .530  | .545  | .560  | 13.46 | 13.84 | 14.22 |

| Overall Length             | D      | 2.045 | 2.058 | 2.065 | 51.94 | 52.26 | 52.45 |

| Tip to Seating Plane       | L      | .120  | .130  | .135  | 3.05  | 3.30  | 3.43  |

| Lead Thickness             | С      | .008  | .012  | .015  | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1     | .030  | .050  | .070  | 0.76  | 1.27  | 1.78  |

| Lower Lead Width           | В      | .014  | .018  | .022  | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing §      | eB     | .620  | .650  | .680  | 15.75 | 16.51 | 17.27 |

| Mold Draft Angle Top       | α      | 5     | 10    | 15    | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β      | 5     | 10    | 15    | 5     | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

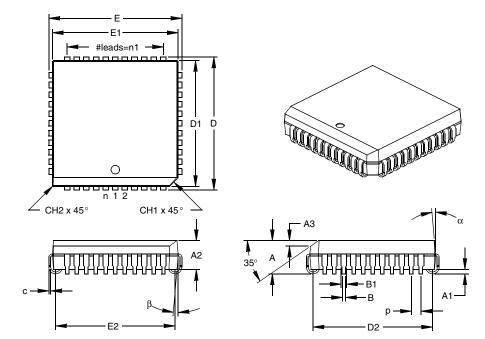

# 44-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |      | INCHES* |      | N     | MILLIMETERS |       |

|--------------------------|----------|------|---------|------|-------|-------------|-------|

| Dimensio                 | n Limits | MIN  | NOM     | MAX  | MIN   | NOM         | MAX   |

| Number of Pins           | n        |      | 44      |      |       | 44          |       |

| Pitch                    | р        |      | .050    |      |       | 1.27        |       |

| Pins per Side            | n1       |      | 11      |      |       | 11          |       |

| Overall Height           | Α        | .165 | .173    | .180 | 4.19  | 4.39        | 4.57  |

| Molded Package Thickness | A2       | .145 | .153    | .160 | 3.68  | 3.87        | 4.06  |

| Standoff §               | A1       | .020 | .028    | .035 | 0.51  | 0.71        | 0.89  |

| Side 1 Chamfer Height    | A3       | .024 | .029    | .034 | 0.61  | 0.74        | 0.86  |

| Corner Chamfer 1         | CH1      | .040 | .045    | .050 | 1.02  | 1.14        | 1.27  |

| Corner Chamfer (others)  | CH2      | .000 | .005    | .010 | 0.00  | 0.13        | 0.25  |

| Overall Width            | Е        | .685 | .690    | .695 | 17.40 | 17.53       | 17.65 |

| Overall Length           | D        | .685 | .690    | .695 | 17.40 | 17.53       | 17.65 |

| Molded Package Width     | E1       | .650 | .653    | .656 | 16.51 | 16.59       | 16.66 |

| Molded Package Length    | D1       | .650 | .653    | .656 | 16.51 | 16.59       | 16.66 |

| Footprint Width          | E2       | .590 | .620    | .630 | 14.99 | 15.75       | 16.00 |

| Footprint Length         | D2       | .590 | .620    | .630 | 14.99 | 15.75       | 16.00 |

| Lead Thickness           | С        | .008 | .011    | .013 | 0.20  | 0.27        | 0.33  |

| Upper Lead Width         | B1       | .026 | .029    | .032 | 0.66  | 0.74        | 0.81  |

| Lower Lead Width         | В        | .013 | .020    | .021 | 0.33  | 0.51        | 0.53  |

| Mold Draft Angle Top     | α        | 0    | 5       | 10   | 0     | 5           | 10    |

| Mold Draft Angle Bottom  | β        | 0    | 5       | 10   | 0     | 5           | 10    |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-047

Drawing No. C04-048

# APPENDIX A: DATA SHEET REVISION HISTORY

### Revision A (June 2001)

Original data sheet for the PIC18FXX8 family.

## Revision B (May 2002)

Updated information on CAN module, device memory and register maps, I/O ports and Enhanced CCP.

### **Revision C (January 2003)**

This revision includes the DC and AC Characteristics Graphs and Tables (see Section 28.0 "DC and AC Characteristics Graphs and Tables"), Section 27.0 "Electrical Characteristics" have been updated and CAN certification information has been added.

### **Revision D (September 2004)**

Data Sheet Errata (DS80134 and DS80161) issues have been addressed and corrected along with minor corrections to the data sheet text.

### **Revision E (October 2006)**

Packaging diagrams updated.

### TABLE B-1: DEVICE DIFFERENCES

|                       | Features                         | PIC18F248                   | PIC18F258                   | PIC18F448                                 | PIC18F458                                 |

|-----------------------|----------------------------------|-----------------------------|-----------------------------|-------------------------------------------|-------------------------------------------|

| Internal              | Bytes                            | 16K                         | 32K                         | 16K                                       | 32K                                       |

| Program<br>Memory     | # of Single-Word<br>Instructions | 8192                        | 16384                       | 8192                                      | 16384                                     |

| Data Memor            | y (Bytes)                        | 768                         | 1536                        | 768                                       | 1536                                      |

| I/O Ports             |                                  | Ports A, B, C               | Ports A, B, C               | Ports A, B, C, D, E                       | Ports A, B, C, D, E                       |

| Enhanced C<br>Modules | apture/Compare/PWM               | -                           | _                           | 1                                         | 1                                         |

| Parallel Slav         | e Port                           | No                          | No                          | Yes                                       | Yes                                       |

| 10-bit Analog         | g-to-Digital Converter           | 5 input channels            | 5 input channels            | 8 input channels                          | 8 input channels                          |

| Analog Com            | parators                         | No                          | No                          | 2                                         | 2                                         |

| Analog Com            | parators VREF Output             | N/A                         | N/A                         | Yes                                       | Yes                                       |

| Packages              |                                  | 28-pin SPDIP<br>28-pin SOIC | 28-pin SPDIP<br>28-pin SOIC | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP |

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1.

| Prescaler, Timer2128                   |

|----------------------------------------|

| PRO MATE II Universal Device           |

| Programmer                             |

| Program Counter                        |

| PCL Register                           |

| •                                      |

| PCLATH Register 40                     |

| PCLATU Register 40                     |

| Program Memory                         |

| Fast Register Stack                    |

| Instructions                           |

|                                        |

| Two-Word43                             |

| Map and Stack for PIC18F248/448        |

| Map and Stack for PIC18F258/458        |

| PUSH and POP Instructions              |

| Return Address Stack                   |

|                                        |

| Return Stack Pointer (STKPTR)          |

| Stack Full/Underflow Resets            |

| Top-of-Stack Access                    |

| Program Verification and               |

| Code Protection                        |

|                                        |

| Associated Registers Summary 276       |

| Configuration Register Protection      |

| Data EEPROM Code Protection            |

| Program Memory Code Protection         |

|                                        |

| Programming, Device Instructions       |

| PUSH                                   |

| PWM (CCP Module) 128                   |

| CCPR1H:CCPR1L Registers 128            |

| Duty Cycle                             |

|                                        |

| Example Frequencies/Resolutions        |

| Period128                              |

| Registers Associated with              |

| PWM and Timer2129                      |

| Setup for PWM Operation 129            |

|                                        |

| TMR2 to PR2 Match 117, 128             |

| PWM (ECCP Module) 134                  |

| Full-Bridge Application Example 138    |

| Full-Bridge Mode137                    |

| Direction Change 138                   |

| Half-Bridge Mode                       |

|                                        |

| Half-Bridge Output Mode                |

| Applications Example136                |

| Output Configurations134               |

| Output Polarity Configuration          |

| Output Relationships Diagram           |

|                                        |

| Programmable Dead-Band Delay           |

| Registers Associated with Enhanced PWM |

| and Timer2141                          |

| Setup for PWM Operation 141            |

| Standard Mode                          |

| Start-up Considerations                |

|                                        |

| System Implementation140               |

| Q                                      |

| Q                                      |

| Q Clock                                |

|                                        |

| R                                      |

| PAM See Data Momony                    |

| RAM. See Data Memory.                  |

| RCALL                                  |

| RCON Register                          |

| RCALL                           |  |

|---------------------------------|--|

| RCON Register                   |  |

| Significance of Status Bits vs. |  |

| Initialization Condition        |  |

| RCSTA Register                  |  |

| SPEN Bit                        |  |

| Receiver Warning                |  |

| Register File                   |  |

|                                 |  |

| Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCON0 (A/D Control 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                 |

| ADCON1 (A/D Control 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                 |

| BRGCON1 (Baud Rate Control 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                 |

| BRGCON2 (Baud Rate Control 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 219                                                                                                                                                                             |

| BRGCON3 (Baud Rate Control 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 220                                                                                                                                                                             |

| CANCON (CAN Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 201                                                                                                                                                                             |

| CANSTAT (CAN Status)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                 |

| CCP1CON (CCP1 Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                 |

| CIOCON (CAN I/O Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                 |

| CMCON (Comparator Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                 |

| COMSTAT (CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                 |

| Communication Status)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 205                                                                                                                                                                             |

| CONFIG1H (Configuration 1 High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                 |

| CONFIG2H (Configuration 2 High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                 |

| CONFIG2L (Configuration 2 Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                 |

| CONFIG4L (Configuration 4 Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                 |