Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

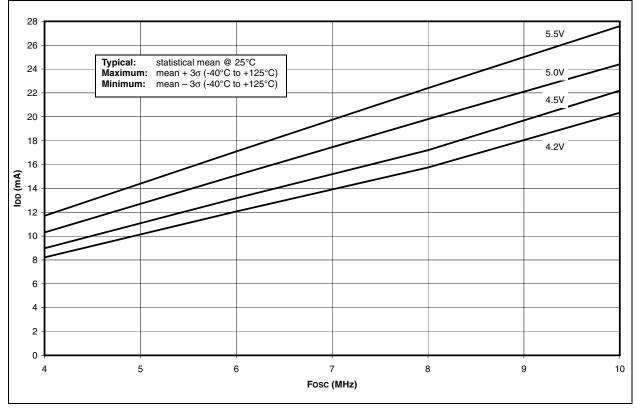

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f448-e-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                       | Pin Number    |               |      |      | Pin                    | Buffer               |                                                                                                       |

|-------------------------------------------------------|---------------|---------------|------|------|------------------------|----------------------|-------------------------------------------------------------------------------------------------------|

| Pin Name                                              | PIC18F248/258 | PIC18F448/458 |      | Туре | Туре                   | Description          |                                                                                                       |

|                                                       | SPDIP, SOIC   | PDIP          | TQFP | PLCC |                        |                      |                                                                                                       |

|                                                       |               | 10            |      | 01   |                        |                      | PORTD is a bidirectional I/O por<br>These pins have TTL input buffe<br>when external memory is enable |

| RD0/PSP0/C1IN+<br>RD0<br>PSP0<br>C1IN+                | _             | 19            | 38   | 21   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 1 input.                                      |

| RD1/PSP1/C1IN-<br>RD1<br>PSP1<br>C1IN-                | _             | 20            | 39   | 22   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 1 input.                                      |

| RD2/PSP2/C2IN+<br>RD2<br>PSP2<br>C2IN+                | _             | 21            | 40   | 23   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 2 input.                                      |

| RD3/PSP3/C2IN-<br>RD3<br>PSP3<br>C2IN-                | _             | 22            | 41   | 24   | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 2 input.                                      |

| RD4/PSP4/ECCP1/<br>P1A<br>RD4<br>PSP4<br>ECCP1<br>P1A | _             | 27            | 2    | 30   | I/O<br>I/O<br>I/O<br>O | ST<br>TTL<br>ST<br>— | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 capture/compare.<br>ECCP1 PWM output A.            |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                    | _             | 28            | 3    | 31   | I/O<br>I/O<br>O        | ST<br>TTL<br>—       | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output B.                                      |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                    | _             | 29            | 4    | 32   | I/O<br>I/O<br>O        | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output C.                                      |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D                    | _             | 30            | 5    | 33   | I/O<br>I/O<br>O        | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output D.                                      |

## TABLE 1-2: PIC18FXX8 PINOUT I/O DESCRIPTIONS (CONTINUED)

OD = Open-Drain (no P diode to VDD)

| TABLE 3-3: | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

| Register | Applicable Devices |           | Power-on Reset,<br>Brown-out Reset | MCLR Reset<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

|----------|--------------------|-----------|------------------------------------|--------------------------------------------------------------|---------------------------------|--|

| TOSU     | PIC18F2X8          | PIC18F4X8 | 0 0000                             | 0 0000                                                       | 0 uuuu <b>(3)</b>               |  |

| TOSH     | PIC18F2X8          | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu <b>(3)</b>            |  |

| TOSL     | PIC18F2X8          | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu <sup>(3)</sup>        |  |

| STKPTR   | PIC18F2X8          | PIC18F4X8 | 00-0 0000                          | uu-0 0000                                                    | uu-u uuuu <b>(3)</b>            |  |

| PCLATU   | PIC18F2X8          | PIC18F4X8 | 0 0000                             | 0 0000                                                       | u uuuu                          |  |

| PCLATH   | PIC18F2X8          | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |  |

| PCL      | PIC18F2X8          | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU  | PIC18F2X8          | PIC18F4X8 | 00 0000                            | 00 0000                                                      | uu uuuu                         |  |

| TBLPTRH  | PIC18F2X8          | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |  |

| TBLPTRL  | PIC18F2X8          | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |  |

| TABLAT   | PIC18F2X8          | PIC18F4X8 | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |  |

| PRODH    | PIC18F2X8          | PIC18F4X8 | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |  |

| PRODL    | PIC18F2X8          | PIC18F4X8 | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |  |

| INTCON   | PIC18F2X8          | PIC18F4X8 | 0000 000x                          | 0000 000u                                                    | սսսս սսսս <b>(1)</b>            |  |

| INTCON2  | PIC18F2X8          | PIC18F4X8 | 1111-1                             | 1111-1                                                       | uuuu-u <b>(1)</b>               |  |

| INTCON3  | PIC18F2X8          | PIC18F4X8 | 11-0 0-00                          | 11-0 0-00                                                    | uu-u u-uu <b>(1)</b>            |  |

| INDF0    | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| POSTINC0 | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| POSTDEC0 | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| PREINC0  | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| PLUSW0   | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| FSR0H    | PIC18F2X8          | PIC18F4X8 | xxxx                               | uuuu                                                         | uuuu                            |  |

| FSR0L    | PIC18F2X8          | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |  |

| WREG     | PIC18F2X8          | PIC18F4X8 | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |  |

| INDF1    | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| POSTINC1 | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| POSTDEC1 | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| PREINC1  | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

| PLUSW1   | PIC18F2X8          | PIC18F4X8 | N/A                                | N/A                                                          | N/A                             |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for Reset value for specific condition.

- 5: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

- 6: Values for CANSTAT also apply to its other instances (CANSTATRO1 through CANSTATRO4).

## 5.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

Generally, a write failure will be a bit which was written as a '1', but reads back as a '0' (due to leakage off the cell).

## 5.6 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together reduce the probability of an accidental write during brown-out, power glitch or software malfunction.

## 5.7 Operation During Code-Protect

Data EEPROM memory has its own code-protect mechanism. External read and write operations are disabled if either of these mechanisms are enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect configuration bit. Refer to **Section 24.0 "Special Features of the CPU"** for additional information.

## 5.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than specification D124 or D124A. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory. A simple data EEPROM refresh routine is shown in Example 5-3.

**Note:** If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification D124 or D124A.

| Loop | CLRF<br>BCF<br>BCF<br>BCF<br>BSF<br>BSF | EEADR<br>EECON1, CFGS<br>EECON1, EEPGD<br>INTCON, GIE<br>EECON1, WREN<br>EECON1, RD | <pre>; Start at address 0 ; Set for memory ; Set for Data EEPROM ; Disable interrupts ; Enable writes ; Loop to refresh array ; Read current address</pre> |

|------|-----------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | MOVLW                                   | 55h                                                                                 | , reau cuitent auuress                                                                                                                                     |

|      | MOVLW                                   | EECON2                                                                              | ;<br>; Write 55h                                                                                                                                           |

|      |                                         | 0AAh                                                                                |                                                                                                                                                            |

|      |                                         | EECON2                                                                              | ;<br>: Write AAh                                                                                                                                           |

|      | BSF                                     |                                                                                     | ; Set WR bit to begin write                                                                                                                                |

|      |                                         | EECON1, WR<br>EECON1, WR                                                            | ; Wait for write to complete                                                                                                                               |

|      | BRA                                     | \$-2                                                                                | , maie for write to comprete                                                                                                                               |

|      | Didi                                    | Y 2                                                                                 |                                                                                                                                                            |

|      | INCFSZ                                  | EEADR, F                                                                            | ; Increment address                                                                                                                                        |

|      | BRA                                     | Loop                                                                                | ; Not zero, do it again                                                                                                                                    |

|      |                                         |                                                                                     |                                                                                                                                                            |

|      | BCF                                     | EECON1, WREN                                                                        | ; Disable writes                                                                                                                                           |

|      | BSF                                     | INTCON, GIE                                                                         | ; Enable interrupts                                                                                                                                        |

|      |                                         |                                                                                     |                                                                                                                                                            |

|      |                                         |                                                                                     |                                                                                                                                                            |

### EXAMPLE 5-3: DATA EEPROM REFRESH ROUTINE

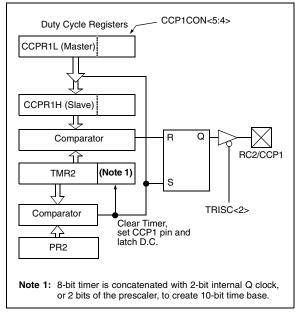

## 15.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 15-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 15.4.3** "Setup for PWM Operation".

#### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

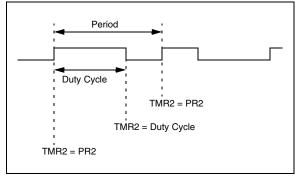

A PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 15-4: PWM OUTPUT

## 15.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula.

#### EQUATION 15-1:

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

## 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time.

#### **EQUATION 15-2:**

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

## FIGURE 16-2: PWM OUTPUT RELATIONSHIPS

| ECCP1C<br><7:6> | ON SIGNAL                                                                                                                                                                                                                                                         | 0          | Cyc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | y<br>le ─►<br>Per | PR2 + |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|

| 00              | P1A Modulated, Active-High                                                                                                                                                                                                                                        |            | ;<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |       |

|                 | P1A Modulated, Active-Low                                                                                                                                                                                                                                         |            | i<br>i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br>              |       |

| 10              | P1A Modulated, Active-Low<br>P1B Modulated, Active-High<br>P1B Modulated, Active-Low                                                                                                                                                                              | - —<br>- — |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pelay             | Delay |

| 01              | P1A Active, Active-High         P1A Active, Active-Low         P1B Inactive, Active-High         P1B Inactive, Active-Low         P1C Inactive, Active-High         P1C Inactive, Active-Low         P1D Modulated, Active-High         P1D Modulated, Active-Low |            | I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I <t< td=""><td></td><td></td></t<> |                   |       |

| 11              | P1A Inactive, Active-High         P1A Inactive, Active-Low         P1B Modulated, Active-High         P1B Modulated, Active-Low         P1C Active, Active-High         P1C Active, Active-Low         P1D Inactive, Active-High         P1D Inactive, Active-Low |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |       |

#### **Relationships:**

- Period = 4 \* Tosc \* (PR2 + 1) \* (TMR2 Prescale Value)

- Duty Cycle = Tosc \* (CCPR1L<7:0>:CCP1CON<5:4>) \* (TMR2 Prescale Value)

- Delay = 4 \* Tosc \* ECCP1DEL

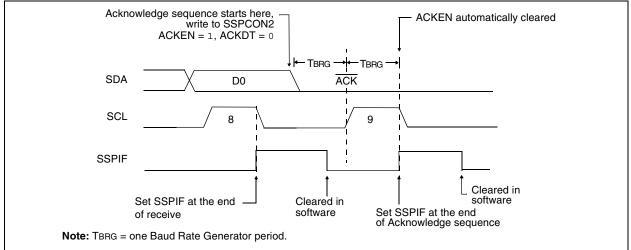

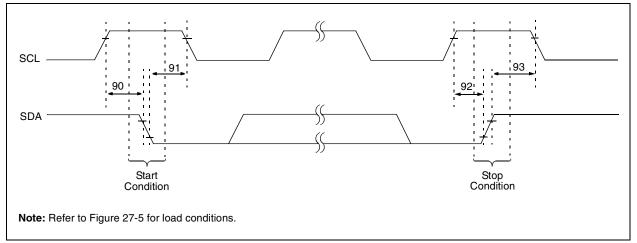

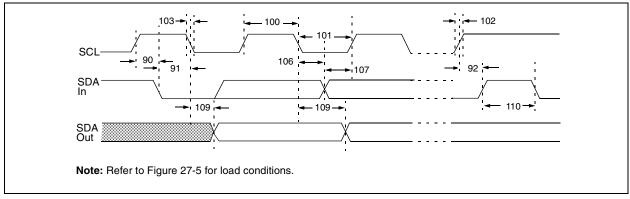

#### 17.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 17-23).

#### 17.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

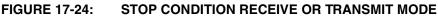

### 17.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 17-24).

## 17.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 17-23: ACKNOWLEDGE SEQUENCE WAVEFORM

| IABLE          | ABLE 18-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1) |            |                    |         |            |                    |                   |             |                    |        |            |                    |

|----------------|--------------------------------------------------------|------------|--------------------|---------|------------|--------------------|-------------------|-------------|--------------------|--------|------------|--------------------|

| BAUD<br>RATE   | Fosc =                                                 | 40 MHz     | SPBRG<br>value     | 33      | MHz        | SPBRG<br>value     | 25                | MHz         | SPBRG<br>value     |        |            | SPBRG              |

| (Kbps)         | KBAUD                                                  | %<br>ERROR | (decimal)          | KBAUD   | %<br>ERROR | (decimal)          | KBAUD             | %<br>ERROR  | (decimal)          | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA                                                     | -          | -                  | NA      | -          | -                  | NA                | -           | -                  | NA     | -          | -                  |

| 1.2            | NA                                                     | -          | -                  | NA      | -          | -                  | NA                | -           | -                  | NA     | -          | -                  |

| 2.4            | NA                                                     | -          | -                  | NA      | -          | -                  | NA                | -           | -                  | NA     | -          | -                  |

| 9.6            | NA                                                     | -          | -                  | 9.60    | -0.07      | 214                | 9.59              | -0.15       | 162                | 9.62   | +0.16      | 129                |

| 19.2           | 19.23                                                  | +0.16      | 129                | 19.28   | +0.39      | 106                | 19.30             | +0.47       | 80                 | 19.23  | +0.16      | 64                 |

| 76.8           | 75.76                                                  | -1.36      | 32                 | 76.39   | -0.54      | 26                 | 78.13             | +1.73       | 19                 | 78.13  | +1.73      | 15                 |

| 96             | 96.15                                                  | +0.16      | 25                 | 98.21   | +2.31      | 20                 | 97.66             | +1.73       | 15                 | 96.15  | +0.16      | 12                 |

| 300            | 312.50                                                 | +4.17      | 7                  | 294.64  | -1.79      | 6                  | 312.50            | +4.17       | 4                  | 312.50 | +4.17      | 3                  |

| 500            | 500                                                    | 0          | 4                  | 515.63  | +3.13      | 3                  | 520.83            | +4.17       | 2                  | 416.67 | -16.67     | 2                  |

| HIGH           | 2500                                                   | -          | 0                  | 2062.50 | -          | 0                  | 1562.50           | -           | 0                  | 1250   | -          | 0                  |

| LOW            | 9.77                                                   | -          | 255                | 8,06    | -          | 255                | 6.10              | -           | 255                | 4.88   | -          | 255                |

|                |                                                        |            |                    |         |            |                    |                   |             |                    |        |            |                    |

| BAUD           | Fosc =                                                 | 16 MHz     | SPBRG              | 10 1    | NHz        | SPBRG              | 7.15909 MHz SPBRG |             |                    | 5.068  | SPBRG      |                    |

| RATE<br>(Kbps) | KBAUD                                                  | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD             | %<br>ERROR  | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA                                                     | -          | -                  | NA      | -          | -                  | NA                | -           | -                  | NA     | -          | -                  |

| 1.2            | NA                                                     | -          | -                  | NA      | -          | -                  | NA                | -           | -                  | NA     | -          | -                  |

| 2.4            | NA                                                     | -          | -                  | NA      | -          | -                  | 2.41              | +0.23       | 185                | 2.40   | 0          | 131                |

| 9.6            | 9.62                                                   | +0.16      | 103                | 9.62    | +0.16      | 64                 | 9.52              | -0.83       | 46                 | 9.60   | 0          | 32                 |

| 19.2           | 19.23                                                  | +0.16      | 51                 | 18.94   | -1.36      | 32                 | 19.45             | +1.32       | 22                 | 18.64  | -2.94      | 16                 |

| 76.8           | 76.92                                                  | +0.16      | 12                 | 78.13   | +1.73      | 7                  | 74.57             | -2.90       | 5                  | 79.20  | +3.13      | 3                  |

| 96             | 100                                                    | +4.17      | 9                  | 89.29   | -6.99      | 6                  | 89.49             | -6.78       | 4                  | 105.60 | +10.00     | 2                  |

| 300            | 333.33                                                 | +11.11     | 2                  | 312.50  | +4.17      | 1                  | 447.44            | +49.15      | 0                  | 316.80 | +5.60      | 0                  |

| 500            | 500                                                    | 0          | 1                  | 625     | +25.00     | 0                  | 447.44            | -10.51      | 0                  | NA     | -          | -                  |

| HIGH           | 1000                                                   | -          | 0                  | 625     | -          | 0                  | 447.44            | -           | 0                  | 316.80 | -          | 0                  |

| LOW            | 3.91                                                   | -          | 255                | 2.44    | -          | 255                | 1.75              | -           | 255                | 1.24   | -          | 255                |

|                |                                                        |            |                    |         |            |                    |                   |             |                    |        |            |                    |

| BAUD           | Fosc =                                                 | 4 MHz      | SPBRG              | 3.5795  | 45 MHz     | SPBRG              | 1 N               | 1 MHz SPBRG |                    |        | 32.768 kHz |                    |

| RATE<br>(Kbps) | KBAUD                                                  | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD             | %<br>ERROR  | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA                                                     | -          | -                  | NA      | -          | -                  | 0.30              | +0.16       | 207                | 0.29   | -2.48      | 6                  |

| 1.2            | 1.20                                                   | +0.16      | 207                | 1.20    | +0.23      | 185                | 1.20              | +0.16       | 51                 | 1.02   | -14.67     | 1                  |

| 2.4            | 2.40                                                   | +0.16      | 103                | 2.41    | +0.23      | 92                 | 2.40              | +0.16       | 25                 | 2.05   | -14.67     | 0                  |

| 9.6            | 9.62                                                   | +0.16      | 25                 | 9.73    | +1.32      | 22                 | 8.93              | -6.99       | 6                  | NA     | -          | -                  |

| 19.2           | 19.23                                                  | +0.16      | 12                 | 18.64   | -2.90      | 11                 | 20.83             | +8.51       | 2                  | NA     | -          | -                  |

| 76.8           | NA                                                     | -          | -                  | 74.57   | -2.90      | 2                  | 62.50             | -18.62      | 0                  | NA     | -          | -                  |

|                |                                                        |            |                    |         |            |                    |                   |             |                    |        |            |                    |

## TABLE 18-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

96

300

500

HIGH

LOW

NA

NA

NA

250

0.98

-

-

-

-

-

-

-

-

0

255

111.86

223.72

NA

55.93

0.22

+16.52

-25.43

-

-

-

1

0

-

0

255

NA

NA

NA

62.50

0.24

-

-

-

-

-

-

-

-

0

255

NA

NA

NA

2.05

0.008

-

-

-

-

-

-

-

-

0

255

| STER 19-13: | RXB1CO                                                                                              | N: RECEIV              | E BUFFE                   | R 1 CONTI                | ROL REGIS                        | TER        |               |         |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------|------------------------|---------------------------|--------------------------|----------------------------------|------------|---------------|---------|--|--|--|

|             | R/C-0                                                                                               | R/W-0                  | R/W-0                     | U-0                      | R-0                              | R-0        | R-0           | R-0     |  |  |  |

|             | RXFUL <sup>(1)</sup>                                                                                | RXM1 <sup>(1)</sup>    | RXM0 <sup>(1)</sup>       | _                        | RXRTRRO                          | FILHIT2    | FILHIT1       | FILHIT0 |  |  |  |

|             | bit 7                                                                                               |                        |                           |                          |                                  |            |               | bit 0   |  |  |  |

|             |                                                                                                     |                        |                           |                          |                                  |            |               |         |  |  |  |

| bit 7       | RXFUL: Re                                                                                           | eceive Full S          | Status bit <sup>(1)</sup> |                          |                                  |            |               |         |  |  |  |

|             |                                                                                                     |                        |                           | ived messa<br>ve a new m | •                                |            |               |         |  |  |  |

|             | Note: This bit is set by the CAN module and should be cleared by software after the buffer is read. |                        |                           |                          |                                  |            |               |         |  |  |  |

| bit 6-5     | RXM1:RXM                                                                                            | <b>IO:</b> Receive     | Buffer Mod                | e bits <sup>(1)</sup>    |                                  |            |               |         |  |  |  |

|             |                                                                                                     |                        | •                         | ling those w             | ,                                |            |               |         |  |  |  |

|             |                                                                                                     |                        |                           |                          | led identifier<br>ard identifier |            |               |         |  |  |  |

|             |                                                                                                     | ive all valid i        | •                         | with Stanua              |                                  |            |               |         |  |  |  |

| bit 4       | Unimplem                                                                                            | ented: Rea             | d as '0'                  |                          |                                  |            |               |         |  |  |  |

| bit 3       | RXRTRRO                                                                                             | : Receive F            | lemote Tran               | sfer Reques              | st bit (read-on                  | ly)        |               |         |  |  |  |

|             |                                                                                                     | e transfer re          |                           |                          |                                  |            |               |         |  |  |  |

|             |                                                                                                     | note transfer          |                           |                          |                                  |            |               |         |  |  |  |

| bit 2-0     |                                                                                                     | LHITO: Filte           |                           | <b>(</b> 11              |                                  |            |               | Dession |  |  |  |

|             | Buffer 1.                                                                                           | indicate whi           | ich acceptar              | ice filter ena           | abled the last                   | message re | eception into | Receive |  |  |  |

|             | 111 = Res                                                                                           |                        |                           |                          |                                  |            |               |         |  |  |  |

|             | 110 = Res                                                                                           | erved<br>eptance Filte | r 5 (BYE5)                |                          |                                  |            |               |         |  |  |  |

|             |                                                                                                     | eptance Filte          |                           |                          |                                  |            |               |         |  |  |  |

|             | 011 = Acce                                                                                          | eptance Filte          | er 3 (RXF3)               |                          |                                  |            |               |         |  |  |  |

|             |                                                                                                     | eptance Filte          | . ,                       | anh maaaih               | la when DVD                      |            | ia aat        |         |  |  |  |

|             |                                                                                                     | •                      | • •                       | • •                      | le when RXB<br>le when RXB       |            |               |         |  |  |  |

|             |                                                                                                     | •                      |                           |                          | RXB1CON are                      |            |               | CON.    |  |  |  |

|             |                                                                                                     |                        |                           |                          |                                  |            |               |         |  |  |  |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | C = Clearable bit    | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

## REGISTER 19-13: RXB1CON: RECEIVE BUFFER 1 CONTROL REGISTER

#### REGISTER 19-23: RXFnEIDH: RECEIVE ACCEPTANCE FILTER n EXTENDED IDENTIFIER, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0

EID15:EID8: Extended Identifier Filter bits

| Legend:           |                  |                      |                                    |  |  |  |

|-------------------|------------------|----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

## REGISTER 19-24: RXFnEIDL: RECEIVE ACCEPTANCE FILTER n EXTENDED IDENTIFIER, LOW BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 EID7:EID0: Extended Identifier Filter bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 19-25: RXMnSIDH: RECEIVE ACCEPTANCE MASK n STANDARD IDENTIFIER MASK, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 SID10:SID3: Standard Identifier Mask bits or Extended Identifier Mask bits EID28:EID21

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| IER 19-35: | IPRJ: PEF                | IPHERAL      | INTERRU       | PT PRIOR       | II Y REGIS      | IER 3     |              |        |  |

|------------|--------------------------|--------------|---------------|----------------|-----------------|-----------|--------------|--------|--|

|            | R/W-1                    | R/W-1        | R/W-1         | R/W-1          | R/W-1           | R/W-1     | R/W-1        | R/W-1  |  |

|            | IRXIP                    | WAKIP        | ERRIP         | TXB2IP         | TXB1IP          | TXB0IP    | RXB1IP       | RXB0IP |  |

|            | bit 7                    |              | •             |                | •               |           | •            | bit 0  |  |

|            |                          |              |               |                |                 |           |              |        |  |

| bit 7      | IRXIP: CA                | N Invalid Re | ceived Mes    | sage Interru   | ot Priority bit | t         |              |        |  |

|            | 1 = High p<br>0 = Low pr |              |               |                |                 |           |              |        |  |

| bit 6      | WAKIP: C                 | AN bus Activ | vity Wake-u   | o Interrupt P  | riority bit     |           |              |        |  |

|            | 1 = High p<br>0 = Low pr |              |               |                |                 |           |              |        |  |

| bit 5      | ERRIP: CA                | AN bus Erro  | r Interrupt P | riority bit    |                 |           |              |        |  |

|            | 1 = High priority        |              |               |                |                 |           |              |        |  |

|            | 0 = Low pr               | iority       |               |                |                 |           |              |        |  |

| bit 4      | TXB2IP: C                | AN Transmi   | t Buffer 2 In | terrupt Priori | ity bit         |           |              |        |  |

|            | 1 = High p               | •            |               |                |                 |           |              |        |  |

|            | 0 = Low pr               | iority       |               |                |                 |           |              |        |  |

| bit 3      | TXB1IP: C                | AN Transmi   | t Buffer 1 In | terrupt Priori | ity bit         |           |              |        |  |

|            | 1 = High p               | •            |               |                |                 |           |              |        |  |

|            | 0 = Low pr               | •            |               |                |                 |           |              |        |  |

| bit 2      |                          |              | t Buffer 0 In | terrupt Priori | ity bit         |           |              |        |  |

|            | 1 = High p               | •            |               |                |                 |           |              |        |  |

| L. 1       | 0 = Low pr               | •            |               |                | a I. 1a         |           |              |        |  |

| bit 1      |                          |              | Butter I In   | terrupt Priori | ty Dit          |           |              |        |  |

|            | 1 = High p<br>0 = Low pr |              |               |                |                 |           |              |        |  |

| bit 0      |                          | •            | e Buffer 0 In | terrupt Priori | tv bit          |           |              |        |  |

| 2          | 1 = High p               |              |               |                | .,              |           |              |        |  |

|            | 0 = Low pr               | •            |               |                |                 |           |              |        |  |

|            | Legend:                  |              |               |                |                 |           |              |        |  |

|            | R = Reada                | ble bit      | W = Writa     | ble bit        | U = Unim        | plemented | bit, read as | 0'     |  |

## REGISTER 19-35: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |      |

|-------------------|------------------|------------------------------------|------|

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unk | nown |

## **19.12 Error Detection**

The CAN protocol provides sophisticated error detection mechanisms. The following errors can be detected.

#### 19.12.1 CRC ERROR

With the Cyclic Redundancy Check (CRC), the transmitter calculates special check bits for the bit sequence, from the start of a frame until the end of the data field. This CRC sequence is transmitted in the CRC field. The receiving node also calculates the CRC sequence using the same formula and performs a comparison to the received sequence. If a mismatch is detected, a CRC error has occurred and an error frame is generated. The message is repeated.

#### 19.12.2 ACKNOWLEDGE ERROR

In the Acknowledge field of a message, the transmitter checks if the Acknowledge slot (which was sent out as a recessive bit) contains a dominant bit. If not, no other node has received the frame correctly. An Acknowledge Error has occurred; an error frame is generated and the message will have to be repeated.

#### 19.12.3 FORM ERROR

If a node detects a dominant bit in one of the four segments, including end of frame, interframe space, Acknowledge delimiter or CRC delimiter, then a Form Error has occurred and an error frame is generated. The message is repeated.

#### 19.12.4 BIT ERROR

A Bit Error occurs if a transmitter sends a dominant bit and detects a recessive bit, or if it sends a recessive bit and detects a dominant bit, when monitoring the actual bus level and comparing it to the just transmitted bit. In the case where the transmitter sends a recessive bit and a dominant bit is detected during the arbitration field and the Acknowledge slot, no Bit Error is generated because normal arbitration is occurring.

## 19.12.5 STUFF BIT ERROR

If, between the start of frame and the CRC delimiter, six consecutive bits with the same polarity are detected, the bit stuffing rule has been violated. A Stuff Bit Error occurs and an error frame is generated. The message is repeated.

#### 19.12.6 ERROR STATES

Detected errors are made public to all other nodes via error frames. The transmission of the erroneous message is aborted and the frame is repeated as soon as possible. Furthermore, each CAN node is in one of the three error states "error-active", "error-passive" or "bus-off" according to the value of the internal error counters. The error-active state is the usual state, where the bus node can transmit messages and activate error frames (made of dominant bits) without any restrictions. In the error-passive state, messages and passive error frames (made of recessive bits) may be transmitted. The bus-off state makes it temporarily impossible for the station to participate in the bus communication. During this state, messages can neither be received nor transmitted.

#### 19.12.7 ERROR MODES AND ERROR COUNTERS

The PIC18FXX8 contains two error counters: the Receive Error Counter (RXERRCNT) and the Transmit Error Counter (TXERRCNT). The values of both counters can be read by the MCU. These counters are incremented or decremented in accordance with the CAN bus specification.

The PIC18FXX8 is error-active if both error counters are below the error-passive limit of 128. It is errorpassive if at least one of the error counters equals or exceeds 128. It goes to bus-off if the transmit error counter equals or exceeds the bus-off limit of 256. The device remains in this state until the bus-off recovery sequence is received. The bus-off recovery sequence consists of 128 occurrences of 11 consecutive recessive bits (see Figure 19-10). Note that the CAN module, after going bus-off, will recover back to erroractive without any intervention by the MCU if the bus remains Idle for 128 x 11 bit times. If this is not desired, the error Interrupt Service Routine should address this. The current error mode of the CAN module can be read by the MCU via the COMSTAT register.

Additionally, there is an Error State Warning flag bit, EWARN, which is set if at least one of the error counters equals or exceeds the error warning limit of 96. EWARN is reset if both error counters are less than the error warning limit.

## REGISTER 24-7: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| 11 27-7. |              |                              |                    |               | 01011               |                     |       |       |

|----------|--------------|------------------------------|--------------------|---------------|---------------------|---------------------|-------|-------|

|          | U-0          | U-0                          | U-0                | U-0           | R/P-1               | R/P-1               | R/P-1 | R/P-1 |

|          | —            | —                            | —                  | _             | WRT3 <sup>(1)</sup> | WRT2 <sup>(1)</sup> | WRT1  | WRT0  |

|          | bit 7        |                              |                    |               |                     |                     |       | bit 0 |

|          |              |                              |                    |               |                     |                     |       |       |

| bit 7-4  | Unimplem     | ented: Read                  | <b>as</b> '0'      |               |                     |                     |       |       |

| bit 3    | WRT3: Wri    | ite Protection               | bit <sup>(1)</sup> |               |                     |                     |       |       |

|          |              | 3 (006000-00<br>3 (006000-00 | ,                  |               | ed                  |                     |       |       |

| h 11 O   |              | ite Protection               | ,                  | protootou     |                     |                     |       |       |

| bit 2    |              |                              |                    |               |                     |                     |       |       |

|          |              | 2 (004000-00                 | ,                  | •             | ed                  |                     |       |       |

|          | 0 = Block  2 | 2 (004000-00                 | 5FFFh) write       | e-protected   |                     |                     |       |       |

| bit 1    | WRT1: Wri    | ite Protection               | bit                |               |                     |                     |       |       |

|          | 1 = Block 1  | (002000-00                   | 3FFFh) not v       | write-protect | ed                  |                     |       |       |

|          | 0 = Block 1  | (002000-00                   | 3FFFh) write       | e-protected   |                     |                     |       |       |

| bit 0    | WRT0: Wri    | ite Protection               | bit                |               |                     |                     |       |       |

|          | 1 = Block 0  | ) (000200-00                 | 1FFFh) not v       | write-protect | ed                  |                     |       |       |

|          | 0 = Block  0 | ) (000200-00                 | 1FFFh) write       | e-protected   |                     |                     |       |       |

|          | Note 1:      | Unimpleme                    | nted in PIC1       | 8FX48 devic   | es; maintair        | n this bit set      |       |       |

|          |              |                              |                    |               |                     |                     |       |       |

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

### REGISTER 24-8: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| 1 24-0. |            |               |                 | ILCIOIL       |               |            |     |       |

|---------|------------|---------------|-----------------|---------------|---------------|------------|-----|-------|

|         | R/P-1      | R/P-1         | R-1             | U-0           | U-0           | U-0        | U-0 | U-0   |

|         | WRTD       | WRTB          | WRTC            | —             | —             | —          | —   | —     |

|         | bit 7      |               |                 |               |               |            |     | bit 0 |

|         |            |               |                 |               |               |            |     |       |

| bit 7   | WRTD: Da   | ata EEPRON    | / Write Prot    | ection bit    |               |            |     |       |

|         | 1 = Data E | EPROM no      | t write-prote   | cted          |               |            |     |       |

|         | 0 = Data E | EPROM wr      | te-protected    | ł             |               |            |     |       |

| bit 6   | WRTB: Bo   | ot Block Wr   | ite Protectio   | n bit         |               |            |     |       |

|         | 1 = Boot B | lock (00000   | 0-0001FFh)      | not write-pr  | otected       |            |     |       |

|         | 0 = Boot B | lock (00000   | 0-0001FFh)      | write-protect | cted          |            |     |       |

| bit 5   | WRTC: Co   | onfiguration  | Register Wr     | ite Protectio | n bit         |            |     |       |

|         | 1 = Config | uration regis | sters (30000    | 0-3000FFh)    | not write-pr  | otected    |     |       |

|         | 0 = Config | uration regis | sters (30000    | 0-3000FFh)    | write-protect | ted        |     |       |

|         | Note:      | This bit is r | ead-only ar     | nd cannot be  | changed in    | user mode. |     |       |

| bit 4-0 | Unimplem   | ented: Rea    | <b>d as</b> '0' |               |               |            |     |       |

|         | •          |               |                 |               |               |            |     |       |

|         |            |               |                 |               |               |            |     |       |

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Readable bit       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

#### TABLE 25-2: PIC18FXXX INSTRUCTION SET (CONTINUED)

| Mnem    | onic,  | Description                     | Qualas | 16-1 | Bit Inst | ruction | Word | Status          | Natas |

|---------|--------|---------------------------------|--------|------|----------|---------|------|-----------------|-------|

| Opera   | nds    | Description                     | Cycles | MSb  |          |         | LSb  | Affected        | Notes |

| LITERAL | OPERAT | TIONS                           |        |      |          |         |      |                 |       |

| ADDLW   | k      | Add literal and WREG            | 1      | 0000 | 1111     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| ANDLW   | k      | AND literal with WREG           | 1      | 0000 | 1011     | kkkk    | kkkk | Z, N            |       |

| IORLW   | k      | Inclusive OR literal with WREG  | 1      | 0000 | 1001     | kkkk    | kkkk | Z, N            |       |

| LFSR    | f, k   | Move literal (12-bit)2nd word   | 2      | 1110 | 1110     | 00ff    | kkkk | None            |       |

|         |        | to FSRx 1st word                |        | 1111 | 0000     | kkkk    | kkkk |                 |       |

| MOVLB   | k      | Move literal to BSR<3:0>        | 1      | 0000 | 0001     | 0000    | kkkk | None            |       |

| MOVLW   | k      | Move literal to WREG            | 1      | 0000 | 1110     | kkkk    | kkkk | None            |       |

| MULLW   | k      | Multiply literal with WREG      | 1      | 0000 | 1101     | kkkk    | kkkk | None            |       |

| RETLW   | k      | Return with literal in WREG     | 2      | 0000 | 1100     | kkkk    | kkkk | None            |       |

| SUBLW   | k      | Subtract WREG from literal      | 1      | 0000 | 1000     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| XORLW   | k      | Exclusive OR literal with WREG  | 1      | 0000 | 1010     | kkkk    | kkkk | Z, N            |       |

| DATA ME | MORY ← | PROGRAM MEMORY OPERA            | TIONS  |      |          |         |      |                 |       |

| TBLRD*  |        | Table Read                      | 2      | 0000 | 0000     | 0000    | 1000 | None            |       |

| TBLRD*+ |        | Table Read with post-increment  |        | 0000 | 0000     | 0000    | 1001 | None            |       |

| TBLRD*- |        | Table Read with post-decrement  |        | 0000 | 0000     | 0000    | 1010 | None            |       |

| TBLRD+* |        | Table Read with pre-increment   |        | 0000 | 0000     | 0000    | 1011 | None            |       |

| TBLWT*  |        | Table Write                     | 2 (5)  | 0000 | 0000     | 0000    | 1100 | None            |       |

| TBLWT*+ |        | Table Write with post-increment |        | 0000 | 0000     | 0000    | 1101 | None            |       |

| TBLWT*- |        | Table Write with post-decrement |        | 0000 | 0000     | 0000    | 1110 | None            |       |

| TBLWT+* |        | Table Write with pre-increment  |        | 0000 | 0000     | 0000    | 1111 | None            |       |

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| CLRF                                                   | Clear f                                                                                |                                         |                              |                    |                                   |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------|------------------------------|--------------------|-----------------------------------|--|

| Syntax:                                                | [ <i>label</i> ] CLF                                                                   | RF f[,a                                 | ]                            |                    |                                   |  |

| Operands:                                              | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in \ [0,1] \end{array}$                      |                                         |                              |                    |                                   |  |

| Operation:                                             | $\begin{array}{l} 000h \rightarrow f \\ 1 \rightarrow Z \end{array}$                   |                                         |                              |                    |                                   |  |

| Status Affected:                                       | Z                                                                                      |                                         |                              |                    |                                   |  |

| Encoding:                                              | 0110                                                                                   | 101a                                    | fff                          | f                  | ffff                              |  |

| Description:<br>Words:<br>Cycles:                      | Clears the c<br>register. If 'a<br>be selected<br>If 'a' = 1, the<br>as per the E<br>1 | ı' is '0', tl<br>, overrid<br>en the ba | he Acc<br>ing the<br>ank wil | ess<br>BS<br>II be | Bank will<br>R value.<br>selected |  |

| Q Cycle Activity:                                      |                                                                                        |                                         |                              |                    |                                   |  |

| Q1                                                     | Q2                                                                                     | Q                                       | 3                            | Q4                 |                                   |  |

| Decode                                                 | Read<br>register 'f'                                                                   | Proce<br>Data                           |                              |                    | Write<br>jister 'f'               |  |

| Example:                                               | CLRF                                                                                   | CLRF FLAG_REG                           |                              |                    |                                   |  |

| Before Instruc<br>FLAG_R<br>After Instructio<br>FLAG_R | EG = 0x<br>on                                                                          | 5A<br>00                                |                              |                    |                                   |  |

| CLRWDT                                                                             | Clear Wate                                                                                                                                                                                        | chdog Ti                   | mer  |          |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|----------|

| Syntax:                                                                            | [label] CLRWDT                                                                                                                                                                                    |                            |      |          |

| Operands:                                                                          | None                                                                                                                                                                                              |                            |      |          |

| Operation:                                                                         | $\begin{array}{l} \text{000h} \rightarrow \text{WDT,} \\ \text{000h} \rightarrow \text{WDT postscaler,} \\ 1 \rightarrow \overline{\text{TO,}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |                            |      |          |

| Status Affected:                                                                   | TO, PD                                                                                                                                                                                            |                            |      |          |

| Encoding:                                                                          | 0000                                                                                                                                                                                              | 0000                       | 0000 | 0100     |

| Words:                                                                             | Watchdog<br>postscaler<br>and PD are                                                                                                                                                              | of the WI                  |      |          |