Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

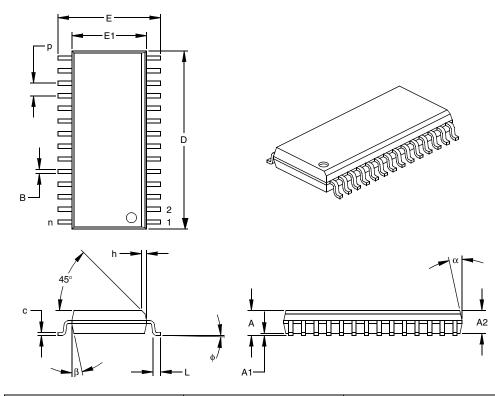

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f448-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TER 5-1:                                                                                                                                                                                                   | EECON1:                                                                                                                                                                                                                                           | EEPROM                       | CONTROL                     | . REGISTE    | R 1           |              |              |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------|--------------|---------------|--------------|--------------|-------------|

|                                                                                                                                                                                                            | R/W-x                                                                                                                                                                                                                                             | R/W-x                        | U-0                         | R/W-0        | R/W-x         | R/W-0        | R/S-0        | R/S-0       |

|                                                                                                                                                                                                            | EEPGD                                                                                                                                                                                                                                             | CFGS                         | —                           | FREE         | WRERR         | WREN         | WR           | RD          |

|                                                                                                                                                                                                            | bit 7                                                                                                                                                                                                                                             |                              |                             |              |               |              |              | bit 0       |

| bit 7                                                                                                                                                                                                      |                                                                                                                                                                                                                                                   | -                            |                             |              | mory Select   | bit          |              |             |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                   |                              | ash memory<br>OM memory     |              |               |              |              |             |

| bit 6                                                                                                                                                                                                      | CFGS: Fla:                                                                                                                                                                                                                                        | sh Program/                  | Data EE or                  | Configuratio | on Select bit |              |              |             |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                   | •                            | on registers<br>ash or data |              | nemory        |              |              |             |

| bit 5                                                                                                                                                                                                      | Unimplem                                                                                                                                                                                                                                          | ented: Read                  | <b>d as</b> '0'             |              |               |              |              |             |

| bit 4                                                                                                                                                                                                      | FREE: Flas                                                                                                                                                                                                                                        | sh Row Eras                  | e Enable bi                 | t            |               |              |              |             |

|                                                                                                                                                                                                            | (reset b                                                                                                                                                                                                                                          | y hardware                   | •                           | v addressed  | by TBLPTR     | on the next  | WR comm      | and         |

| bit 3                                                                                                                                                                                                      | 0 = Perforn                                                                                                                                                                                                                                       | Vrite Error F                | log bit                     |              |               |              |              |             |

| DIL 3                                                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                              | prematurel                  | v torminator | 4             |              |              |             |

|                                                                                                                                                                                                            | (any M                                                                                                                                                                                                                                            |                              | WDT Reset                   |              | timed progra  | mming in no  | ormal operat | tion)       |

|                                                                                                                                                                                                            | Note:                                                                                                                                                                                                                                             | When a W                     | •                           |              | GD or FRE     | E bits are n | ot cleared.  | This allows |

| bit 2                                                                                                                                                                                                      | WREN: Wr                                                                                                                                                                                                                                          | ite Enable b                 | it                          |              |               |              |              |             |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                   | write cycles<br>write to the | EEPROM o                    | or Flash mer | nory          |              |              |             |

| bit 1                                                                                                                                                                                                      | WR: Write                                                                                                                                                                                                                                         | Control bit                  |                             |              |               |              |              |             |

|                                                                                                                                                                                                            | 1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle<br>(The operation is self-timed and the bit is cleared by hardware once write is complete. The<br>WR bit can only be set (not cleared) in software.) |                              |                             |              |               |              |              |             |

|                                                                                                                                                                                                            | 0 = Write c                                                                                                                                                                                                                                       | ycle is comp                 | olete                       |              |               |              |              |             |

| bit 0                                                                                                                                                                                                      | RD: Read                                                                                                                                                                                                                                          |                              |                             |              |               |              |              |             |

| <ul> <li>1 = Initiates an EEPROM read         (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared in software. RD bit cannot be set when EEPGD = 1.)     </li> </ul> |                                                                                                                                                                                                                                                   |                              |                             |              |               |              | not cleared) |             |

|                                                                                                                                                                                                            | 0 = Does n                                                                                                                                                                                                                                        | ot initiate ar               | EEPROM                      | read         |               |              |              |             |

|                                                                                                                                                                                                            | Logond                                                                                                                                                                                                                                            |                              |                             |              |               |              |              | ]           |

|                                                                                                                                                                                                            | Legend:                                                                                                                                                                                                                                           |                              |                             |              |               |              |              |             |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | S = Settable bit     | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

# REGISTER 5-1: EECON1: EEPROM CONTROL REGISTER 1

#### 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

#### 6.1 **Table Reads and Table Writes**

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 6-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in Section 6.5 "Writing to Flash Program Memory". Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

# Instruction: TBLRD\* Program Memory Table Pointer<sup>(1)</sup> Table Latch (8-bit) TBLPTRH TBLPTRU TBLPTRL TABLAT Program Memory (TBLPTR) Note 1: Table Pointer points to a byte in program memory.

#### FIGURE 6-1: **TABLE READ OPERATION**

# 12.2 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON register). The oscillator is a low-power oscillator rated up to 50 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 12-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

#### TABLE 12-1: CAPACITOR SELECTION FOR THE ALTERNATE OSCILLATOR

| OUDILLATOIT                          |        |                    |                    |  |  |  |

|--------------------------------------|--------|--------------------|--------------------|--|--|--|

| Osc Type                             | Freq   | C1                 | C2                 |  |  |  |

| LP                                   | 32 kHz | TBD <sup>(1)</sup> | TBD <sup>(1)</sup> |  |  |  |

| Crystal to be Tested:                |        |                    |                    |  |  |  |

| 32.768 kHz Epson C-001R32.768K-A ±20 |        |                    | ±20 PPM            |  |  |  |

- Note 1: Microchip suggests 33 pF as a starting point in validating the oscillator circuit.

- Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

# 12.3 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR registers). This interrupt can be enabled/disabled by setting/clearing TMR1 Interrupt Enable bit, TMR1IE (PIE registers).

## 12.4 Resetting Timer1 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event triggers f | from the CCP1   |  |  |  |  |

|-------|------------------------------|-----------------|--|--|--|--|

|       | module will not set inte     | rrupt flag bit, |  |  |  |  |

|       | TMR1IF (PIR registers).      |                 |  |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

# 12.5 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON register) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

# 16.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

| Note: | The ECCP (Enhanced Capture/Compare/ |        |    |      |           |    |

|-------|-------------------------------------|--------|----|------|-----------|----|

|       | PWM)                                | module | is | only | available | on |

|       | PIC18F448 and PIC18F458 devices.    |        |    |      |           |    |

This module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. The operation of the ECCP module differs from the CCP (discussed in detail in **Section 15.0 "Capture/Compare/PWM (CCP) Modules**") with the addition of an Enhanced PWM module which allows for up to 4 output channels and user selectable polarity. These features are discussed in detail in **Section 16.5** "**Enhanced PWM Mode**". The module can also be programmed for automatic shutdown in response to various analog or digital events.

The control register for ECCP1 is shown in Register 16-1.

# REGISTER 16-1: ECCP1CON: ECCP1 CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0   |  |

|---------|---------|--------|--------|---------|---------|---------|---------|--|

| EPWM1M1 | EPWM1M0 | EDC1B1 | EDC1B0 | ECCP1M3 | ECCP1M2 | ECCP1M1 | ECCP1M0 |  |

| bit 7   |         |        |        |         |         |         | bit 0   |  |

bit 7-6 **EPWM1M<1:0>:** PWM Output Configuration bits

I<u>f ECCP1M<3:2> = 00, 01, 10:</u>

xx = P1A assigned as Capture/Compare input; P1B, P1C, P1D assigned as port pins If ECCP1M<3:2> = 11:

- 00 = Single output; P1A modulated; P1B, P1C, P1D assigned as port pins

- 01 = Full-bridge output forward; P1D modulated; P1A active; P1B, P1C inactive

- 10 = Half-bridge output; P1A, P1B modulated with deadband control; P1C, P1D assigned as port pins

- 11 = Full-bridge output reverse; P1B modulated; P1C active; P1A, P1D inactive

- bit 5-4 EDC1B<1:0>: PWM Duty Cycle Least Significant bits

<u>Capture mode:</u> Unused.

Compare mode:

Unused.

PWM mode:

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in ECCPR1L.

# bit 3-0 ECCP1M<3:0>: ECCP1 Mode Select bits

- 0000 = Capture/Compare/PWM off (resets ECCP module)

- 0001 = Unused (reserved)

- 0010 = Compare mode, toggle output on match (ECCP1IF bit is set)

- 0011 = Unused (reserved)

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, set output on match (ECCP1IF bit is set)

- 1001 = Compare mode, clear output on match (ECCP1IF bit is set)

- 1010 = Compare mode, ECCP1 pin is unaffected (ECCP1IF bit is set)

- 1011 = Compare mode, trigger special event (ECCP1IF bit is set; ECCP resets TMR1or TMR3 and starts an A/D conversion if the A/D module is enabled)

- 1100 = PWM mode; P1A, P1C active-high; P1B, P1D active-high

- 1101 = PWM mode; P1A, P1C active-high; P1B, P1D active-low

- 1110 = PWM mode; P1A, P1C active-low; P1B, P1D active-high

- 1111 = PWM mode; P1A, P1C active-low; P1B, P1D active-low

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### 17.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

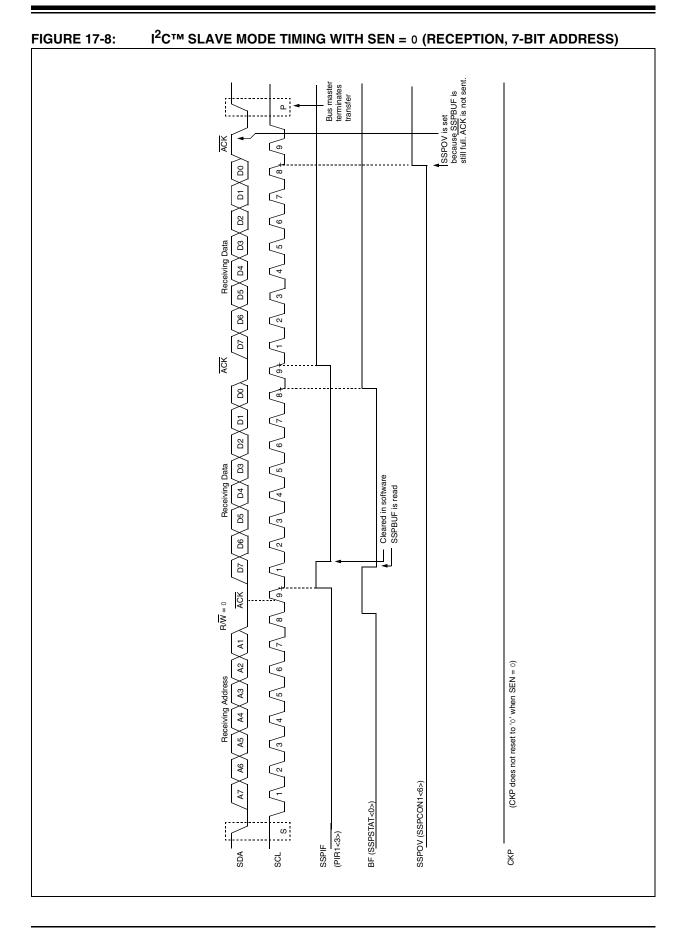

#### 17.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

#### 17.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit BF is set.

- 3. An ACK pulse is generated.

- MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

### 18.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in that the shift clock is supplied externally at the RC6/ TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTA register).

#### 18.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### 18.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

#### **19.12 Error Detection**

The CAN protocol provides sophisticated error detection mechanisms. The following errors can be detected.

#### 19.12.1 CRC ERROR

With the Cyclic Redundancy Check (CRC), the transmitter calculates special check bits for the bit sequence, from the start of a frame until the end of the data field. This CRC sequence is transmitted in the CRC field. The receiving node also calculates the CRC sequence using the same formula and performs a comparison to the received sequence. If a mismatch is detected, a CRC error has occurred and an error frame is generated. The message is repeated.

#### 19.12.2 ACKNOWLEDGE ERROR

In the Acknowledge field of a message, the transmitter checks if the Acknowledge slot (which was sent out as a recessive bit) contains a dominant bit. If not, no other node has received the frame correctly. An Acknowledge Error has occurred; an error frame is generated and the message will have to be repeated.

#### 19.12.3 FORM ERROR

If a node detects a dominant bit in one of the four segments, including end of frame, interframe space, Acknowledge delimiter or CRC delimiter, then a Form Error has occurred and an error frame is generated. The message is repeated.

#### 19.12.4 BIT ERROR

A Bit Error occurs if a transmitter sends a dominant bit and detects a recessive bit, or if it sends a recessive bit and detects a dominant bit, when monitoring the actual bus level and comparing it to the just transmitted bit. In the case where the transmitter sends a recessive bit and a dominant bit is detected during the arbitration field and the Acknowledge slot, no Bit Error is generated because normal arbitration is occurring.

#### 19.12.5 STUFF BIT ERROR

If, between the start of frame and the CRC delimiter, six consecutive bits with the same polarity are detected, the bit stuffing rule has been violated. A Stuff Bit Error occurs and an error frame is generated. The message is repeated.

#### 19.12.6 ERROR STATES

Detected errors are made public to all other nodes via error frames. The transmission of the erroneous message is aborted and the frame is repeated as soon as possible. Furthermore, each CAN node is in one of the three error states "error-active", "error-passive" or "bus-off" according to the value of the internal error counters. The error-active state is the usual state, where the bus node can transmit messages and activate error frames (made of dominant bits) without any restrictions. In the error-passive state, messages and passive error frames (made of recessive bits) may be transmitted. The bus-off state makes it temporarily impossible for the station to participate in the bus communication. During this state, messages can neither be received nor transmitted.

#### 19.12.7 ERROR MODES AND ERROR COUNTERS

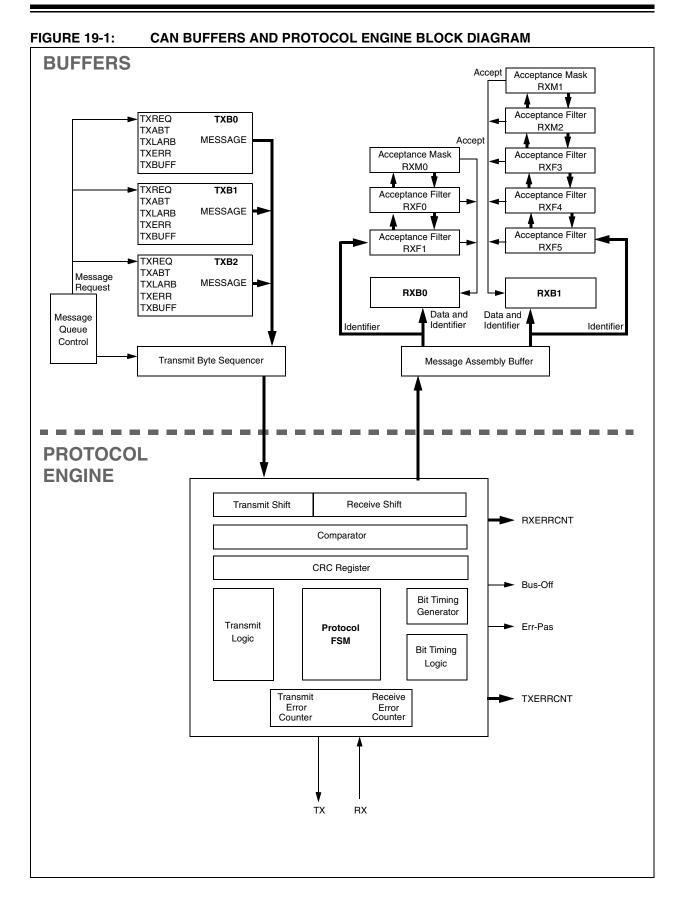

The PIC18FXX8 contains two error counters: the Receive Error Counter (RXERRCNT) and the Transmit Error Counter (TXERRCNT). The values of both counters can be read by the MCU. These counters are incremented or decremented in accordance with the CAN bus specification.

The PIC18FXX8 is error-active if both error counters are below the error-passive limit of 128. It is errorpassive if at least one of the error counters equals or exceeds 128. It goes to bus-off if the transmit error counter equals or exceeds the bus-off limit of 256. The device remains in this state until the bus-off recovery sequence is received. The bus-off recovery sequence consists of 128 occurrences of 11 consecutive recessive bits (see Figure 19-10). Note that the CAN module, after going bus-off, will recover back to erroractive without any intervention by the MCU if the bus remains Idle for 128 x 11 bit times. If this is not desired, the error Interrupt Service Routine should address this. The current error mode of the CAN module can be read by the MCU via the COMSTAT register.

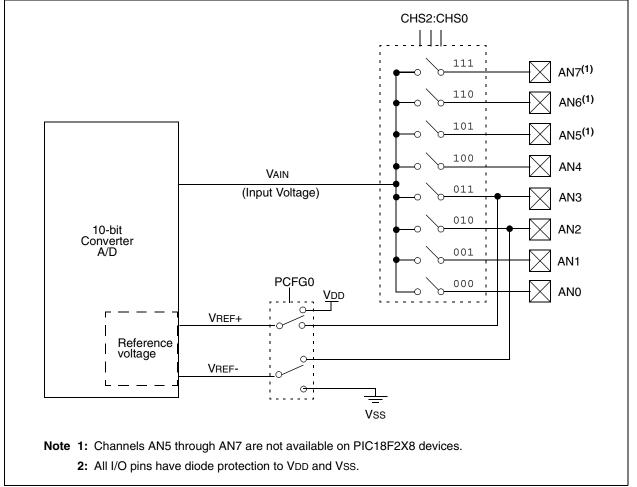

Additionally, there is an Error State Warning flag bit, EWARN, which is set if at least one of the error counters equals or exceeds the error warning limit of 96. EWARN is reset if both error counters are less than the error warning limit. The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and VSS) or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF- pin.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter which generates the result via successive approximation.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference) or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 20-1.

#### FIGURE 20-1: A/D BLOCK DIAGRAM

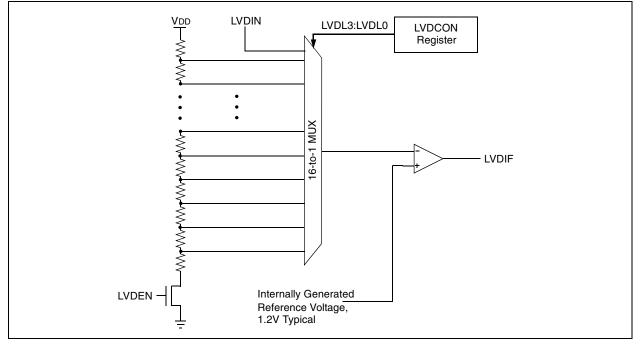

#### FIGURE 23-2: LOW-VOLTAGE DETECT (LVD) BLOCK DIAGRAM

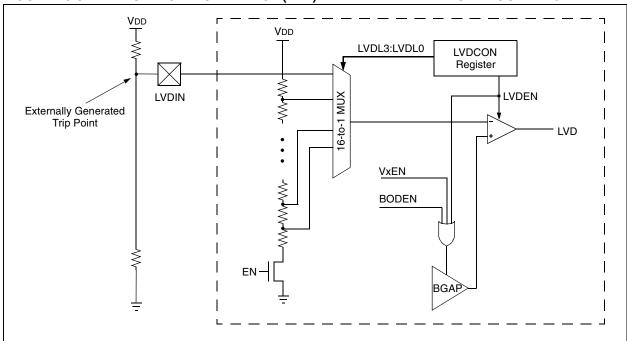

The LVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits LVDL3:LVDL0 are set to '1111'. In this state, the comparator input is multiplexed from the external input pin LVDIN to one input of the comparator (Figure 23-3). The other input is connected to the internally generated voltage reference (parameter #D423 in **Section 27.2** "**DC Characteristics**"). This gives users flexibility, because it allows them to configure the Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

FIGURE 23-3: LOW-VOLTAGE DETECT (LVD) WITH EXTERNAL INPUT BLOCK DIAGRAM

# 24.0 SPECIAL FEATURES OF THE CPU

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming

All PIC18FXX8 devices have a Watchdog Timer which is permanently enabled via the configuration bits or software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT) which provides a fixed delay on power-up only, designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very Low-Current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

# 24.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh) which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The EECON1 register WR bit starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction, with the TBLPTR pointed to the Configuration register, sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell.

| File    | Name     | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|--------|-------|--------|--------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H |       | _     | OSCSEN | _     |        | FOSC2  | FOSC1  | FOSC0  | 1111                              |

| 300002h | CONFIG2L | _     | _     | _      | _     | BORV1  | BORV0  | BOREN  | PWRTEN | 1111                              |

| 300003h | CONFIG2H |       |       | —      | -     | WDTPS2 | WDTPS1 | WDTPS0 | WDTEN  | 1111                              |

| 300006h | CONFIG4L | DEBUG | _     | _      | _     | _      | LVP    | _      | STVREN | 11-1                              |

| 300008h | CONFIG5L |       | _     | _      | _     | CP3    | CP2    | CP1    | CP0    | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   | —      | -     | -      | —      | -      | —      | 11                                |

| 30000Ah | CONFIG6L | _     | _     | —      | -     | WRT3   | WRT2   | WRT1   | WRT0   | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC   | -     | -      | —      | -      | —      | 111                               |

| 30000Ch | CONFIG7L | _     | _     | _      | _     | EBTR3  | EBTR2  | EBTR1  | EBTR0  | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB | _      | _     | _      | —      | _      | —      | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0   | REV4  | REV3   | REV2   | REV1   | REV0   | (1)                               |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8   | DEV7  | DEV6   | DEV5   | DEV4   | DEV3   | 0000 1000                         |

TABLE 24-1: CONFIGURATION BITS AND DEVICE IDS

Note 1: See Register 24-11 for DEVID1 values.

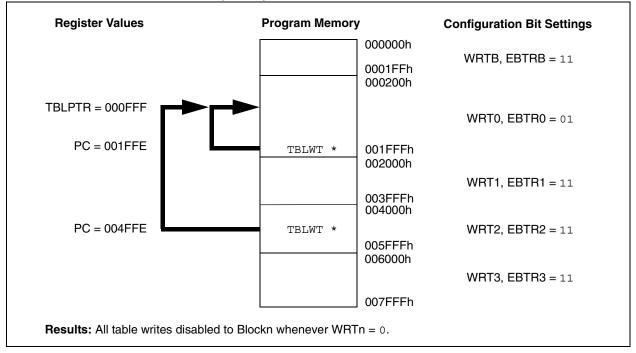

#### 24.4.1 PROGRAM MEMORY CODE PROTECTION

The user memory may be read to or written from any location using the table read and table write instructions. The device ID may be read with table reads. The Configuration registers may be read and written with the table read and table write instructions.

In user mode, the CPn bits have no direct effect. CPn bits inhibit external reads and writes. A block of user memory may be protected from table writes if the WRTn configuration bit is '0'. The EBTRn bits control table reads. For a block of user memory with the EBTRn bit set to '0', a table read instruction that executes from within that block is allowed to read. A table read instruction that executes from a location outside of that block is not allowed to read and will result in reading '0's. Figures 24-4 through 24-6 illustrate table write and table read protection.

| Note: | Code protection bits may only be written to   |

|-------|-----------------------------------------------|

|       | a '0' from a '1' state. It is not possible to |

|       | write a '1' to a bit in the '0' state. Code   |

|       | protection bits are only set to '1' by a full |

|       | chip erase or block erase function. The full  |

|       | chip erase and block erase functions can      |

|       | only be initiated via ICSP or an external     |

|       | programmer.                                   |

FIGURE 24-4: TABLE WRITE (WRTn) DISALLOWED

| DEC      | FSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Decrement                                           | f, Skip if 0                      |                      |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------|----------------------|--|--|

| Synta    | ax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | [label] DE                                          | ECFSZ f[,d                        | [,a]]                |  |  |

| Oper     | ands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ |                                   |                      |  |  |

| Oper     | ation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (f) – 1 $\rightarrow$ de skip if resul              | -                                 |                      |  |  |

| Statu    | is Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | None                                                |                                   |                      |  |  |

| Enco     | oding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0010                                                | 11da ff                           | ff ffff              |  |  |

| Desc     | cription: The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If the result is '0', the next instruction<br>which is already fetched is discarded<br>and a NOP is executed instead, making<br>it a two-cycle instruction. If 'a' is '0', the<br>Access Bank will be selected,<br>overriding the BSR value. If 'a' = 1,<br>then the bank will be selected as per<br>the BSR value (default). |                                                     |                                   |                      |  |  |

| Word     | ls:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                   | · · · ·                           |                      |  |  |

| Cycle    | es:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     | /cles if skip a<br>a 2-word insti |                      |  |  |

| QC       | ycle Activity:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |                                   |                      |  |  |

|          | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q2                                                  | Q3                                | Q4                   |  |  |

|          | Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Read<br>register 'f'                                | Process<br>Data                   | Write to destination |  |  |

| lf sl    | kip:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |                                   |                      |  |  |

|          | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q2                                                  | Q3                                | Q4                   |  |  |

|          | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | No<br>operation                                     | No<br>operation                   | No<br>operation      |  |  |

| lf sk    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | d by 2-word in                                      |                                   | operation            |  |  |

|          | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q2                                                  | Q3                                | Q4                   |  |  |

|          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | No                                                  | No                                | No                   |  |  |

|          | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | operation                                           | operation                         | operation            |  |  |

|          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | No                                                  | No                                | No                   |  |  |

|          | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | operation                                           | operation                         | operation            |  |  |

| Example: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | HERE<br>CONTINUE                                    | DECFSZ<br>GOTO                    | CNT<br>LOOP          |  |  |

|          | Before Instruc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |                                   |                      |  |  |

|          | PC<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | = Address                                           | = Address (HERE)                  |                      |  |  |

|          | CNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | = CNT - 1                                           | 1                                 |                      |  |  |

|          | If CNT<br>PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | = 0;<br>= Address                                   | s (CONTINU                        | E)                   |  |  |

|          | If CNT<br>PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ≠ 0;<br>= Address                                   | S (HERE +                         | 2)                   |  |  |

| DCFSNZ                                                      | Decremen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t f, Skip if no                                     | t 0             |  |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|--|--|--|

| Syntax:                                                     | [label] D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CFSNZ f[,d                                          | [,a]]           |  |  |  |

| Operands:                                                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d ∈ [0,1]                                           |                 |  |  |  |

| Operation:                                                  | ()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (f) – 1 → dest,<br>skip if result $\neq$ 0          |                 |  |  |  |

| Status Affected:                                            | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | None                                                |                 |  |  |  |

| Encoding:                                                   | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11da ff                                             | ff ffff         |  |  |  |

| Description:                                                | The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If the result is not '0', the next<br>instruction which is already fetched is<br>discarded and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is '0', the Access Bank<br>will be selected, overriding the BSR<br>value. If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |                                                     |                 |  |  |  |

| Words:                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |                 |  |  |  |

| Cycles:                                                     | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |                 |  |  |  |

| Q Cycle Activity:<br>Q1<br>Decode                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | cycles if skip a<br>a 2-word instr<br>Q3<br>Process |                 |  |  |  |

|                                                             | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Data                                                | destination     |  |  |  |

| lf skip:                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |                 |  |  |  |

| Q1                                                          | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q3                                                  | Q4              |  |  |  |

| No                                                          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No                                                  | No              |  |  |  |

| operation<br>If skip and followe                            | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | operation                                           | operation       |  |  |  |

| Q1                                                          | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q3                                                  | Q4              |  |  |  |

| No                                                          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No                                                  | No              |  |  |  |

| operation                                                   | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | operation                                           | operation       |  |  |  |

| No                                                          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No                                                  | No              |  |  |  |