Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f448t-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>REGISTER 8-8:</b> | PIE2: PEF                               | RIPHERAL                     | INTERRU         | PT ENABI             | E REGIS | TER 2 |        |                        |

|----------------------|-----------------------------------------|------------------------------|-----------------|----------------------|---------|-------|--------|------------------------|

|                      | U-0                                     | R/W-0                        | U-0             | R/W-0                | R/W-0   | R/W-0 | R/W-0  | R/W-0                  |

|                      | —                                       | CMIE <sup>(1)</sup>          | _               | EEIE                 | BCLIE   | LVDIE | TMR3IE | ECCP1IE <sup>(1)</sup> |

|                      | bit 7                                   |                              |                 |                      |         |       |        | bit 0                  |

|                      |                                         |                              |                 |                      |         |       |        |                        |

| bit 7                | •                                       | ented: Rea                   |                 | (1)                  |         |       |        |                        |

| bit 6                |                                         | nparator Inte                | •               |                      |         |       |        |                        |

|                      |                                         | es the compa<br>es the compa |                 | -                    |         |       |        |                        |

| bit 5                | Unimplem                                | ented: Rea                   | <b>d as</b> '0' |                      |         |       |        |                        |

| bit 4                | EEIE: EEP                               | ROM Write                    | Interrupt Er    | able bit             |         |       |        |                        |

|                      | 1 = Enable<br>0 = Disable               |                              |                 |                      |         |       |        |                        |

| bit 3                | BCLIE: Bu                               | s Collision I                | nterrupt Ena    | able bit             |         |       |        |                        |

|                      | 1 = Enable<br>0 = Disable               |                              |                 |                      |         |       |        |                        |

| bit 2                | LVDIE: LO                               | w-Voltage D                  | etect Interru   | ipt Enable b         | it      |       |        |                        |

|                      | 1 = Enable                              | d                            |                 | -                    |         |       |        |                        |

|                      | 0 = Disable                             | ed                           |                 |                      |         |       |        |                        |

| bit 1                | TMR3IE: T                               | MR3 Overfle                  | ow Interrupt    | Enable bit           |         |       |        |                        |

|                      | 1 = Enables the TMR3 overflow interrupt |                              |                 |                      |         |       |        |                        |

|                      | 0 = Disable                             | es the TMR3                  | overflow ir     | iterrupt             |         |       |        |                        |

| bit 0                | ECCP1IE:                                | ECCP1 Inte                   | rrupt Enabl     | e bit <sup>(1)</sup> |         |       |        |                        |

|                      | 1 = Enable                              | s the ECCP                   | 1 interrupt     |                      |         |       |        |                        |

|                      | 0 = Disable                             | es the ECCF                  | 1 interrupt     |                      |         |       |        |                        |

|                      |                                         |                              |                 |                      |         |       |        |                        |

### Note 1: This bit is only available on PIC18F4X8 devices. For PIC18F2X8 devices, this bit is unimplemented and reads as '0'.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.4 IPR Registers

The Interrupt Priority (IPR) registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Priority registers (IPR1, IPR2 and IPR3). The operation of the priority bits requires that the Interrupt Priority Enable bit (IPEN) be set.

#### REGISTER 8-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

|       | R/W-1                      | R/W-1        | R/W-1          | R/W-1          | R/W-1          | R/W-1        | R/W-1      | R/W-1         |

|-------|----------------------------|--------------|----------------|----------------|----------------|--------------|------------|---------------|

|       | PSPIP <sup>(1)</sup>       | ADIP         | RCIP           | TXIP           | SSPIP          | CCP1IP       | TMR2IP     | TMR1IP        |

|       | bit 7                      |              |                |                |                |              |            | bit 0         |

|       |                            |              |                |                |                |              |            |               |

| bit 7 | PSPIP: Pai                 | rallel Slave | Port Read/W    | /rite Interrup | t Priority bit | (1)          |            |               |

|       | 1 = High pr                | iority       |                |                |                |              |            |               |

|       | 0 = Low pri                | ority        |                |                |                |              |            |               |

| bit 6 |                            |              | nterrupt Prio  | rity bit       |                |              |            |               |

|       | 1 = High pr                |              |                |                |                |              |            |               |

|       | 0 = Low pri                | -            |                |                |                |              |            |               |

| bit 5 |                            |              | e Interrupt Pr | riority bit    |                |              |            |               |

|       | 1 = High pr                | -            |                |                |                |              |            |               |

|       | 0 = Low pri                | •            |                |                |                |              |            |               |

| bit 4 |                            |              | t Interrupt P  | riority bit    |                |              |            |               |

|       | 1 = High pr                | •            |                |                |                |              |            |               |

| hit 0 | 0 = Low pri                | •            | anaua Carial   | Dort Interry   | nt Driarity h  | :+           |            |               |

| bit 3 |                            | -            | onous Seria    | Port Interru   | ipt Priority D | 11           |            |               |

|       | 1 = High pr<br>0 = Low pri | ,            |                |                |                |              |            |               |

| bit 2 | •                          | -            | pt Priority bi | ł              |                |              |            |               |

|       | 1 = High pr                |              | pr:            | •              |                |              |            |               |

|       | 0 = Low pri                | •            |                |                |                |              |            |               |

| bit 1 | TMR2IP: T                  | MR2 to PR2   | 2 Match Inter  | rrupt Priority | bit            |              |            |               |

|       | 1 = High pr                | iority       |                |                |                |              |            |               |

|       | 0 = Low pri                | ority        |                |                |                |              |            |               |

| bit 0 |                            |              | ow Interrupt   | Priority bit   |                |              |            |               |

|       | 1 = High pr                | •            |                |                |                |              |            |               |

|       | 0 = Low pri                | ority        |                |                |                |              |            |               |

|       | No.4                       | This hit !   |                |                |                |              |            |               |

|       | Note 1:                    |              | only availabl  |                |                | es. For PIC1 | 8F2X8 devi | ces, this bit |

|       |                            | is unimplet  | nemeu anu      | caus as 0.     |                |              |            |               |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 12.2 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON register). The oscillator is a low-power oscillator rated up to 50 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 12-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

#### TABLE 12-1: CAPACITOR SELECTION FOR THE ALTERNATE OSCILLATOR

| OUDILLATOIT                            |        |                    |                    |  |  |  |

|----------------------------------------|--------|--------------------|--------------------|--|--|--|

| Osc Type                               | Freq   | C1                 | C2                 |  |  |  |

| LP                                     | 32 kHz | TBD <sup>(1)</sup> | TBD <sup>(1)</sup> |  |  |  |

| Crystal to be Tested:                  |        |                    |                    |  |  |  |

| 32.768 kHz Epson C-001R32.768K-A ±20 F |        |                    |                    |  |  |  |

- Note 1: Microchip suggests 33 pF as a starting point in validating the oscillator circuit.

- Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

#### 12.3 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR registers). This interrupt can be enabled/disabled by setting/clearing TMR1 Interrupt Enable bit, TMR1IE (PIE registers).

#### 12.4 Resetting Timer1 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event triggers f | from the CCP1   |  |  |  |  |  |

|-------|------------------------------|-----------------|--|--|--|--|--|

|       | module will not set inte     | rrupt flag bit, |  |  |  |  |  |

|       | TMR1IF (PIR registers).      |                 |  |  |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

#### 12.5 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON register) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

### 16.5.4 PROGRAMMABLE DEAD-BAND DELAY

In half-bridge or full-bridge applications, where all power switches are modulated at the PWM frequency at all times, the power switches normally require longer time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches will be on for a short period of time until one switch completely turns off. During this time, a very high current (*shoot-through current*) flows through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on the power switch is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 16-3 for illustration. The ECCP1DEL register (Register 16-2) sets the amount of delay.

#### 16.5.5 SYSTEM IMPLEMENTATION

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pullup and/or pull-down resistors on the PWM output pins. When the microcontroller powers up, all of the I/O pins are in the high-impedance state. The external pull-up and pull-down resistors must keep the power switch devices in the off state until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

#### 16.5.6 START-UP CONSIDERATIONS

Prior to enabling the PWM outputs, the P1A, P1B, P1C and P1D latches may not be in the proper states. Enabling the TRISD bits for output at the same time with the ECCP1 module may cause damage to the power switch devices. The ECCP1 module must be enabled in the proper output mode with the TRISD bits enabled as inputs. Once the ECCP1 completes a full PWM cycle, the P1A, P1B, P1C and P1D output latches are properly initialized. At this time, the TRISD bits can be enabled for outputs to start driving the power switch devices. The completion of a full PWM cycle is indicated by the TMR2IF bit going from a '0' to a '1'.

#### 16.5.7 OUTPUT POLARITY CONFIGURATION

The ECCP1M<1:0> bits in the ECCP1CON register allow user to choose the logic conventions (asserted high/low) for each of the outputs.

The PWM output polarities must be selected before the PWM outputs are enabled. Charging the polarity configuration while the PWM outputs are active is not recommended since it may result in unpredictable operation.

#### REGISTER 16-2: ECCP1DEL: PWM DELAY REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EPDC7 | EPDC6 | EPDC5 | EPDC4 | EPDC3 | EPDC2 | EPDC1 | EPDC0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 EPDC<7:0>: PWM Delay Count for Half-Bridge Output Mode bits

Number of Fosc/4 (Tosc \* 4) cycles between the P1A transition and the P1B transition.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 17.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 17.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

#### 17.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

#### 17.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/SS/LVDIN

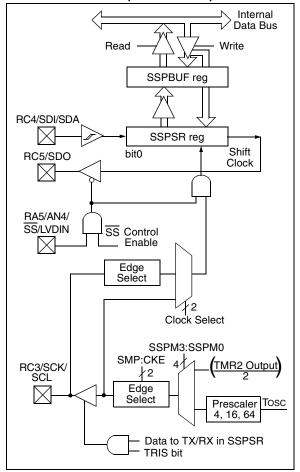

Figure 17-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 17-1: MSSP BLOCK DIAGRAM (SPI™ MODE)

#### 17.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 17-2) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode. The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in Figure 17-3, Figure 17-5 and Figure 17-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

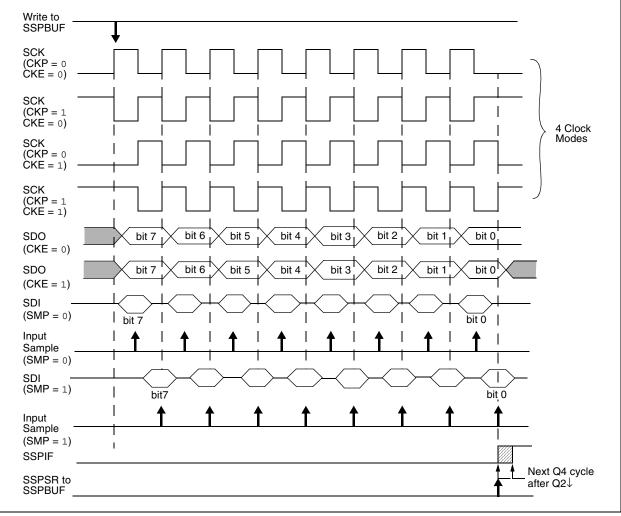

Figure 17-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 17-3: SPI™ MODE WAVEFORM (MASTER MODE)

#### 17.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep. Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit (SSPCON1<4>).

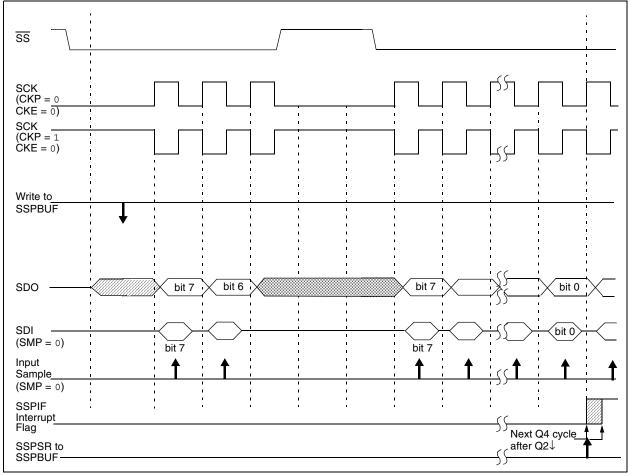

#### 17.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch

must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin      |

|---------|-------------------------------------------------------------|

|         | control enabled (SSPCON1<3:0> = 0100),                      |

|         | the SPI module will reset if the $\overline{SS}$ pin is set |

|         | to VDD.                                                     |

2: If the SPI is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

| ADDWFC                                                | ADD W and Carry bit to f                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                               | [ <i>label</i> ] ADDWFC f [,d [,a]]                                                                                                                                                                                                                                           |  |  |  |  |  |

| Operands:                                             | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                           |  |  |  |  |  |

| Operation:                                            | $(W) + (f) + (C) \to dest$                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Status Affected:                                      | N, OV, C, DC, Z                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Encoding:                                             | 0010 00da ffff ffff                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Description:                                          | Add W, the Carry flag and data memory<br>location 'f'. If 'd' is '0', the result is placed<br>in W. If 'd' is '1', the result is placed in<br>data memory location 'f'. If 'a' is '0', the<br>Access Bank will be selected. If 'a' is '1',<br>the BSR will not be overridden. |  |  |  |  |  |

| Words:                                                | 1                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Cycles:                                               | 1                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Q Cycle Activity:                                     |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Q1                                                    | Q2 Q3 Q4                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Decode                                                | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                |  |  |  |  |  |

| Example:                                              | ADDWFC REG, W                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Before Instru<br>Carry b<br>REG<br>W<br>After Instruc | it = 1<br>= 0x02<br>= 0x4D                                                                                                                                                                                                                                                    |  |  |  |  |  |

| AND          | LW                  | AND Liter                   | al with W    | /   |    |           |

|--------------|---------------------|-----------------------------|--------------|-----|----|-----------|

| Synta        | ax:                 | [label] Al                  | NDLW         | k   |    |           |

| Oper         | ands:               | $0 \le k \le 255$           | 5            |     |    |           |

| Oper         | ation:              | (W) .AND.                   | $k\toW$      |     |    |           |

| Statu        | s Affected:         | N, Z                        |              |     |    |           |

| Enco         | ding:               | 0000                        | 1011         | kkk | k  | kkkk      |

| Description: |                     | The conter<br>8-bit literal |              |     |    |           |

| Words:       |                     | 1                           |              |     |    |           |

| Cycle        | es:                 | 1                           |              |     |    |           |

| QC           | ycle Activity:      |                             |              |     |    |           |

|              | Q1                  | Q2                          | Q            | 3   |    | Q4        |

|              | Decode              | Read literal<br>'k'         | Proce<br>Dat |     | Wı | rite to W |

| <u>Exan</u>  | nple:               | ANDLW                       | 0x5F         |     |    |           |

|              | Before Instruc<br>W | tion<br>= 0xA3              |              |     |    |           |

|              | After Instruction   | on                          |              |     |    |           |

0x03

=

W

| Before Instruct  | tion |      |

|------------------|------|------|

| Carry bit        | =    | 1    |

| REG              | =    | 0x02 |

| W                | =    | 0x4D |

| After Instructio | n    |      |

| Carry bit        | =    | 0    |

| REG              | =    | 0x02 |

| W                | =    | 0x50 |

| NEGF                                             | Negate f                                                                                      |                                                                      |                                                                 |                                        |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------|

| Syntax:                                          | [label] N                                                                                     | IEGF f                                                               | [,a]                                                            |                                        |

| Operands:                                        | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in \ [0,1] \end{array}$                             |                                                                      |                                                                 |                                        |

| Operation:                                       | $(\overline{f}) + 1 \rightarrow 1$                                                            | f                                                                    |                                                                 |                                        |

| Status Affected:                                 | N, OV, C, E                                                                                   | DC, Z                                                                |                                                                 |                                        |

| Encoding:                                        | 0110                                                                                          | 110a                                                                 | ffff                                                            | ffff                                   |

| Description:                                     | Location 'f'<br>complemendata memore<br>Access Balloverriding to<br>the bank we<br>BSR value. | nt. The re<br>ory location<br>nk will be<br>the BSR v<br>ill be sele | esult is plac<br>on 'f'. If 'a'<br>e selected,<br>value. If 'a' | ced in the<br>is '0', the<br>= 1, then |

| Words:                                           | 1                                                                                             |                                                                      |                                                                 |                                        |

| Cycles:                                          | 1                                                                                             |                                                                      |                                                                 |                                        |

| Q Cycle Activity:                                |                                                                                               |                                                                      |                                                                 |                                        |

| Q1                                               | Q2                                                                                            | Q                                                                    | 3                                                               | Q4                                     |

| Decode                                           | Read<br>register 'f'                                                                          | Proce<br>Data                                                        |                                                                 | Write<br>gister 'f'                    |

| Example:                                         | NEGF                                                                                          | REG, 1                                                               |                                                                 |                                        |

| Before Instruc<br>REG<br>After Instructic<br>REG | = 0011                                                                                        | 1010 <b>[0</b><br>0110 <b>[0</b>                                     | x3A]<br>)xC6]                                                   |                                        |

| NOP                                      |                | No Operation    |              |              |    |                |  |

|------------------------------------------|----------------|-----------------|--------------|--------------|----|----------------|--|

| Synta                                    | ax:            | [label] NOP     |              |              |    |                |  |

| Oper                                     | ands:          | None            |              |              |    |                |  |

| Operation: No operation                  |                |                 |              |              |    |                |  |

| Statu                                    | s Affected:    | None            |              |              |    |                |  |

| Encoding: 0000 0000 000<br>1111 xxxx xxx |                |                 | -            | 0000<br>xxxx |    |                |  |

| Description:                             |                | No operation.   |              |              |    |                |  |

| Word                                     | ls:            | 1               |              |              |    |                |  |

| Cycle                                    | es:            | 1               |              |              |    |                |  |

| QC                                       | ycle Activity: |                 |              |              |    |                |  |

|                                          | Q1             | Q2              | Q3           | 3            |    | Q4             |  |

|                                          | Decode         | No<br>operation | No<br>operat |              | ор | No<br>peration |  |

Example:

None.

| RETFIE Return from Interrupt |                                |                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                       |                                     |  |  |

|------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|-------------------------------------|--|--|

| Synta                        | ax:                            | [label] F                                                                                                                                                                                                                                                                                                                                                                                                        | RETFIE         | [s]                   |                                     |  |  |

| Oper                         | ands:                          | $s\in  [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                    |                |                       |                                     |  |  |

| Oper                         | ation:                         | $1 \rightarrow GIE/G$<br>if s = 1<br>(WS) $\rightarrow$ W<br>(STATUSS<br>(BSRS) $\rightarrow$                                                                                                                                                                                                                                                                                                                    |                |                       |                                     |  |  |

| Statu                        | s Affected:                    | GIE/GIEH,                                                                                                                                                                                                                                                                                                                                                                                                        | PEIE/GI        | EL.                   |                                     |  |  |

| Enco                         | ding:                          | 0000                                                                                                                                                                                                                                                                                                                                                                                                             | 0000           | 0001                  | 000s                                |  |  |

| Desc                         | ription:                       | Return from interrupt. Stack is popped<br>and Top-of-Stack (TOS) is loaded into<br>the PC. Interrupts are enabled by<br>setting either the high or low priority<br>global interrupt enable bit. If 's' = 1, the<br>contents of the shadow registers WS,<br>STATUSS and BSRS are loaded into<br>their corresponding registers W, Status<br>and BSR. If 's' = 0, no update of these<br>registers occurs (default). |                |                       |                                     |  |  |

| Word                         | ls:                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                |                |                       |                                     |  |  |

| Cycle                        | es:                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                |                |                       |                                     |  |  |

| QC                           | ycle Activity:                 |                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                       |                                     |  |  |

|                              | Q1                             | Q2                                                                                                                                                                                                                                                                                                                                                                                                               | Q3             |                       | Q4                                  |  |  |

|                              | Decode                         | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                  | No<br>operatio | on s<br>Set 0         | PC from<br>stack<br>GIEH or<br>GIEL |  |  |

|                              | No                             | No                                                                                                                                                                                                                                                                                                                                                                                                               | No             |                       | No                                  |  |  |

|                              | operation                      | operation                                                                                                                                                                                                                                                                                                                                                                                                        | operatio       | on ope                | eration                             |  |  |

| <u>Exan</u>                  | After Interrupt<br>PC          | RETFIE 1                                                                                                                                                                                                                                                                                                                                                                                                         | -              | ros                   |                                     |  |  |

|                              | W<br>BSR<br>Status<br>GIE/GIEI | H, PEIE/GIEL                                                                                                                                                                                                                                                                                                                                                                                                     | = E<br>= S     | WS<br>BSRS<br>STATUSS |                                     |  |  |

| RET          | LW                          | Return Lit                                                           | eral to W                            | ,                                     |                               |  |  |  |

|--------------|-----------------------------|----------------------------------------------------------------------|--------------------------------------|---------------------------------------|-------------------------------|--|--|--|

| Synt         | ax:                         | [ <i>label</i> ] F                                                   | [ <i>label</i> ] RETLW k             |                                       |                               |  |  |  |

| Oper         | rands:                      | $0 \le k \le 255$                                                    | 5                                    |                                       |                               |  |  |  |

| Ope          | ration:                     | $k \rightarrow W$ , (TOS) $\rightarrow F$ PCLATU, F                  | ,                                    | are uncha                             | nged                          |  |  |  |

| Statu        | is Affected:                | None                                                                 |                                      |                                       |                               |  |  |  |

| Enco         | oding:                      | 0000                                                                 | 1100                                 | kkkk                                  | kkkk                          |  |  |  |

| Description: |                             | W is loade<br>The progra<br>top of the s<br>The high a<br>remains ur | am counte<br>stack (the<br>ddress la | r is loaded<br>return ad<br>tch (PCLA | d from the dress).            |  |  |  |

| Word         | ds:                         | 1                                                                    | 1                                    |                                       |                               |  |  |  |

| Cycl         | es:                         | 2                                                                    | 2                                    |                                       |                               |  |  |  |

| QC           | ycle Activity:              |                                                                      |                                      |                                       |                               |  |  |  |

|              | Q1                          | Q2                                                                   | Q3                                   |                                       | Q4                            |  |  |  |

|              | Decode                      | Read<br>literal 'k'                                                  | Proces<br>Data                       | fror                                  | op PC<br>n stack,<br>ite to W |  |  |  |

|              | No                          | No                                                                   | No                                   |                                       | No                            |  |  |  |

|              | operation                   | operation                                                            | operatio                             | on op                                 | eration                       |  |  |  |

| <u>Exar</u>  | n <b>ple:</b><br>CALL TABLE | ; W conta<br>; offset<br>; W now H<br>; table y                      | value<br>nas                         | ole                                   |                               |  |  |  |

```

:

```

```

TABLE

ADDWF PCL ; W = offset

RETLW k0 ; Begin table

RETLW k1 ;

:

:

RETLW kn ; End of table

Before Instruction

```

| W             | =    | 0x07        |

|---------------|------|-------------|

| After Instruc | tion |             |

| W             | =    | value of kn |

#### 26.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 26.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 26.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, timekeeping and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high-level source debugging with the MPLAB IDE.

### 26.6 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### 26.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

#### 26.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high-speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

#### 26.9 MPLAB ICE 2000 High-Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

#### 26.10 MPLAB ICE 4000 High-Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PICmicro microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high-speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

#### 26.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PICmicro MCUs and can be used to develop for these and other PICmicro microcontrollers. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single-stepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PICmicro devices.

#### 26.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify and program PICmicro devices without a PC connection. It can also set code protection in this mode.

#### 26.13 MPLAB PM3 Device Programmer

The MPLAB PM3 is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 device programmer can read, verify and program PICmicro devices without a PC connection. It can also set code protection in this mode. MPLAB PM3 connects to the host PC via an RS-232 or USB cable. MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

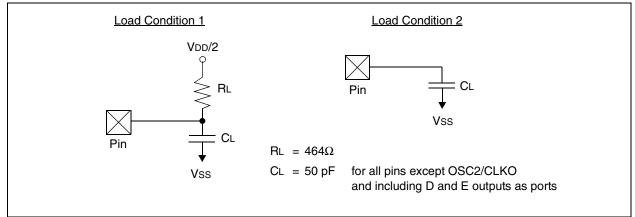

#### 27.3.2 TIMING CONDITIONS

The temperature and voltages specified in Table 27-5 apply to all timing specifications unless otherwise noted. Figure 27-5 specifies the load conditions for the timing specifications.

#### TABLE 27-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

| AC CHARACTERISTICS | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Operating voltage VDD range as described in DC specification,<br>Section 27.1 "DC Characteristics".<br>LF parts operate for industrial temperatures only.                               |

#### FIGURE 27-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

| Param<br>No. | Symbol  | Charact             | Min          | Max         | Units | Conditions |                                                |

|--------------|---------|---------------------|--------------|-------------|-------|------------|------------------------------------------------|

| 100          | Тнідн   | Clock High Time     | 100 kHz mode | 4.0         | —     | μs         | PIC18FXX8 must operate at a minimum of 1.5 MHz |

|              |         |                     | 400 kHz mode | 0.6         | _     | μs         | PIC18FXX8 must operate at a minimum of 10 MHz  |

|              |         |                     | SSP Module   | 1.5 Tcy     | —     |            |                                                |

| 101          | TLOW    | Clock Low Time      | 100 kHz mode | 4.7         | _     | μs         | PIC18FXX8 must operate at a minimum of 1.5 MHz |

|              |         |                     | 400 kHz mode | 1.3         | —     | μs         | PIC18FXX8 must operate at a minimum of 10 MHz  |

|              |         |                     | SSP module   | 1.5 Tcy     | —     | ns         |                                                |

| 102          | TR      | SDA and SCL Rise    | 100 kHz mode | —           | 1000  | ns         |                                                |

|              |         | Time                | 400 kHz mode | 20 + 0.1 Cв | 300   | ns         | CB is specified to be from<br>10 to 400 pF     |

| 103          | TF      | SDA and SCL Fall    | 100 kHz mode | —           | 300   | ns         |                                                |

|              |         | Time                | 400 kHz mode | 20 + 0.1 Cв | 300   | ns         | CB is specified to be from<br>10 to 400 pF     |

| 90           | TSU:STA | Start Condition     | 100 kHz mode | 4.7         | —     | μs         | Only relevant for Repeated                     |

|              |         | Setup Time          | 400 kHz mode | 0.6         | —     | μs         | Start condition                                |

| 91           | THD:STA | Start Condition     | 100 kHz mode | 4.0         | _     | μs         | After this period the first                    |

|              |         | Hold Time           | 400 kHz mode | 0.6         | _     | μs         | clock pulse is generated                       |

| 106          | THD:DAT | Data Input Hold     | 100 kHz mode | 0           | —     | ns         |                                                |

|              |         | Time                | 400 kHz mode | 0           | 0.9   | μs         |                                                |

| 107          | TSU:DAT | Data Input Setup    | 100 kHz mode | 250         | —     | ns         | (Note 2)                                       |

|              |         | Time                | 400 kHz mode | 100         | —     | ns         |                                                |

| 92           | Tsu:sto | Stop Condition      | 100 kHz mode | 4.7         | —     | μs         | -                                              |

|              |         | Setup Time          | 400 kHz mode | 0.6         | —     | μs         |                                                |

| 109          | ΤΑΑ     | Output Valid from   | 100 kHz mode | -           | 3500  | ns         | (Note 1)                                       |

|              |         | Clock               | 400 kHz mode |             | —     | ns         |                                                |

| 110          | TBUF    | Bus Free Time       | 100 kHz mode | 4.7         | —     | μs         | Time the bus must be free                      |

|              |         |                     | 400 kHz mode | 1.3         | —     | μs         | before a new transmission<br>can start         |

| D102         | Св      | Bus Capacitive Load | ding         |             | 400   | pF         |                                                |

#### TABLE 27-18: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS (SLAVE MODE)

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement TSU;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line.

Before the SCL line is released, TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode  $I^2C$  bus specification).

| Param<br>No. | Symbol | Characte                          | eristic             | Min        | Тур      | Max         | Units    | Conditions                                                                                                                    |

|--------------|--------|-----------------------------------|---------------------|------------|----------|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------|

| A01          | NR     | Resolution                        |                     | _          | _        | 10          | bit      | $VREF = VDD \ge 3.0V$                                                                                                         |

| A03          | EIL    | Integral Linearity                | Error               | _          | _        | <±1         | LSb      | $VREF=VDD \geq 3.0V$                                                                                                          |

| A04          | Edl    | Differential Linea                | rity Error          | _          | _        | <±1         | LSb      | $VREF = VDD \ge 3.0V$                                                                                                         |

| A05          | Efs    | Full Scale Error                  |                     | _          | _        | <±1         | LSb      | $VREF = VDD \ge 3.0V$                                                                                                         |

| A06          | EOFF   | Offset Error                      |                     | _          | _        | <±1.5       | LSb      | $VREF = VDD \ge 3.0V$                                                                                                         |

| A10          | _      | Monotonicity <sup>(3)</sup>       |                     | ç          | juarante | ed          | —        | $VSS \le VAIN \le VREF$                                                                                                       |

| A20          | VREF   | Reference Voltag                  | je                  | 0V         |          | _           | V        |                                                                                                                               |

| A20A         |        | (VREFH – VREFL)                   |                     | 3V         | _        | —           | V        | For 10-bit resolution                                                                                                         |

| A21          | VREFH  | Reference Voltag                  | je High             | Vss        |          | VDD + 0.3V  | V        |                                                                                                                               |

| A22          | VREFL  | Reference Voltag                  | je Low              | Vss - 0.3V | _        | Vdd         | V        |                                                                                                                               |

| A25          | VAIN   | Analog Input Vol                  | age                 | Vss - 0.3V | _        | VREF + 0.3V | V        |                                                                                                                               |

| A30          | ZAIN   | Recommended I<br>Analog Voltage S |                     | —          | _        | 10.0        | kΩ       |                                                                                                                               |

| A40          | IAD    | A/D Conversion                    | PIC18FXX8           | _          | 180      | —           | μA       | Average current                                                                                                               |

|              |        | Current (VDD)                     | PIC18 <b>LF</b> XX8 | —          | 90       | —           | μA       | consumption when<br>A/D is on <b>(Note 1)</b>                                                                                 |

| A50          | IREF   | VREF Input Curre                  | nt <b>(Note 2)</b>  | 0          | _        | 5           | μΑ<br>μΑ | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN. To<br>charge CHOLD.<br>During A/D conversion<br>cycle. |

### TABLE 27-23: A/D CONVERTER CHARACTERISTICS: PIC18FXX8 (INDUSTRIAL, EXTENDED) PIC18LFXX8 (INDUSTRIAL)

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current specification includes any such leakage from the A/D module. VREF current is from RA2/AN2/VREF- and RA3/AN3/VREF+ pins or VDD and VSS pins, whichever is selected as reference input.

**2:** VSS  $\leq$  VAIN  $\leq$  VREF

**3:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

NOTES:

#### 29.0 PACKAGING INFORMATION

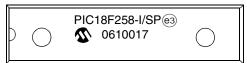

#### 29.1 Package Marking Information

#### 28-Lead SPDIP

28-Lead SOIC

#### 40-Lead PDIP

Example

#### Example

#### Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |

### INDEX

| Α                                     |

|---------------------------------------|

| A/D241                                |

| A/D Converter Flag (ADIF Bit)243      |

| A/D Converter Interrupt, Configuring  |

| Acquisition Requirements244           |

| Acquisition Time245                   |

| ADCON0 Register241                    |

| ADCON1 Register241                    |

| ADRESH Register241                    |

| ADRESH/ADRESL Registers243            |

| ADRESL Register241                    |

| Analog Port Pins, Configuring246      |

| Associated Registers Summary248       |

| Calculating the Minimum Required      |

| Acquisition Time                      |

| Configuring the Module                |

| Conversion Clock (TAD)                |

| Conversion Status (GO/DONE Bit)       |

| Conversion TAD Cycles                 |

| Conversions                           |

| Minimum Charging Time                 |

| Result Registers                      |

| Selecting the Conversion Clock        |

| Special Event Trigger (CCP)           |

| Special Event Trigger (ECCP) 133, 248 |

| TAD vs. Device Operating Frequencies  |

| (For Extended, LF Devices) (table)246 |

| TAD vs. Device Operating              |

| Frequencies (table)                   |

| Use of the ECCP Trigger               |

| Absolute Maximum Ratings              |

| AC (Timing) Characteristics           |

| Parameter Symbology                   |

| Access Bank                           |

| ACKSTAT                               |

| ACKSTAT Status Flag                   |

| ADCON0 Register                       |

|                                       |

| ADCON1 Register                       |

| ADDLW                                 |

| Receiver Transmitter, See USART.      |

| ADDWF                                 |

| ADDWF                                 |

| ADRESH Register                       |

| ADRESH ADRESL Registers               |

| ADRESL Register                       |

| Analog-to-Digital Converter. See A/D. |

| ANDLW                                 |

| ANDWF                                 |

| ANDWI                                 |

| MPASM Assembler                       |

| Associated Registers                  |

|                                       |

| В                                     |

| Bank Select Register (BSR)54          |

| Baud Rate Generator                   |

| BC                                    |

BF ...... 173